何をお探しですか?

PathWave Advanced Design System(ADS)2020 アップデート2.0製品リリース

Highlights

PathWave Advanced Design System(ADS)2020 アップデート2.0は、以下のためのソリューションおよび機能を提供します。

- 高速デジタル(HSD)デザイン

- 電磁界(EM)シミュレーション

- 回路シミュレーション

- パワー・エレクトロニクス・デザイン

- デザイン/テクノロジー管理

- デザイン編集

PathWave Advanced Design System(ADS)2020 アップデート2.0を今すぐ使用できます。

上の[トライアル&ライセンス]タブをクリックしてから、[詳細&ダウンロード]ボタンをクリックして最新ソフトウェアをダウンロードしてください。

Description

PathWave Advanced Design System(ADS)2020 アップデート2.0は、以下を含む難易度の高い高速デジタル、RF/マイクロ波デザインおよびパワー・エレクトロニクス・デザインのためのソリューションおよび機能を提供します。

PathWave Advanced Design System(ADS)2020 アップデート2.0は、以下を含む難易度の高い高速デジタル、RF/マイクロ波デザインおよびパワー・エレクトロニクス・デザインのためのソリューションおよび機能を提供します。

高速デジタルデザイン

SerDes

- データ通信および電気通信市場向けにVPIphotonicsとの電気/光/電気(E/O/E)統合ワークフローを導入。これにより、以下のようなエンドツーエンドリンク解析のデザインで光チャネル効果を考慮できるようになります。

- 電波吸収型変調器(EAM)の非線形波長依存伝達関数

- 非線形性

- 相対強度雑音(RIN)

- ファイバー減衰量

- 分散

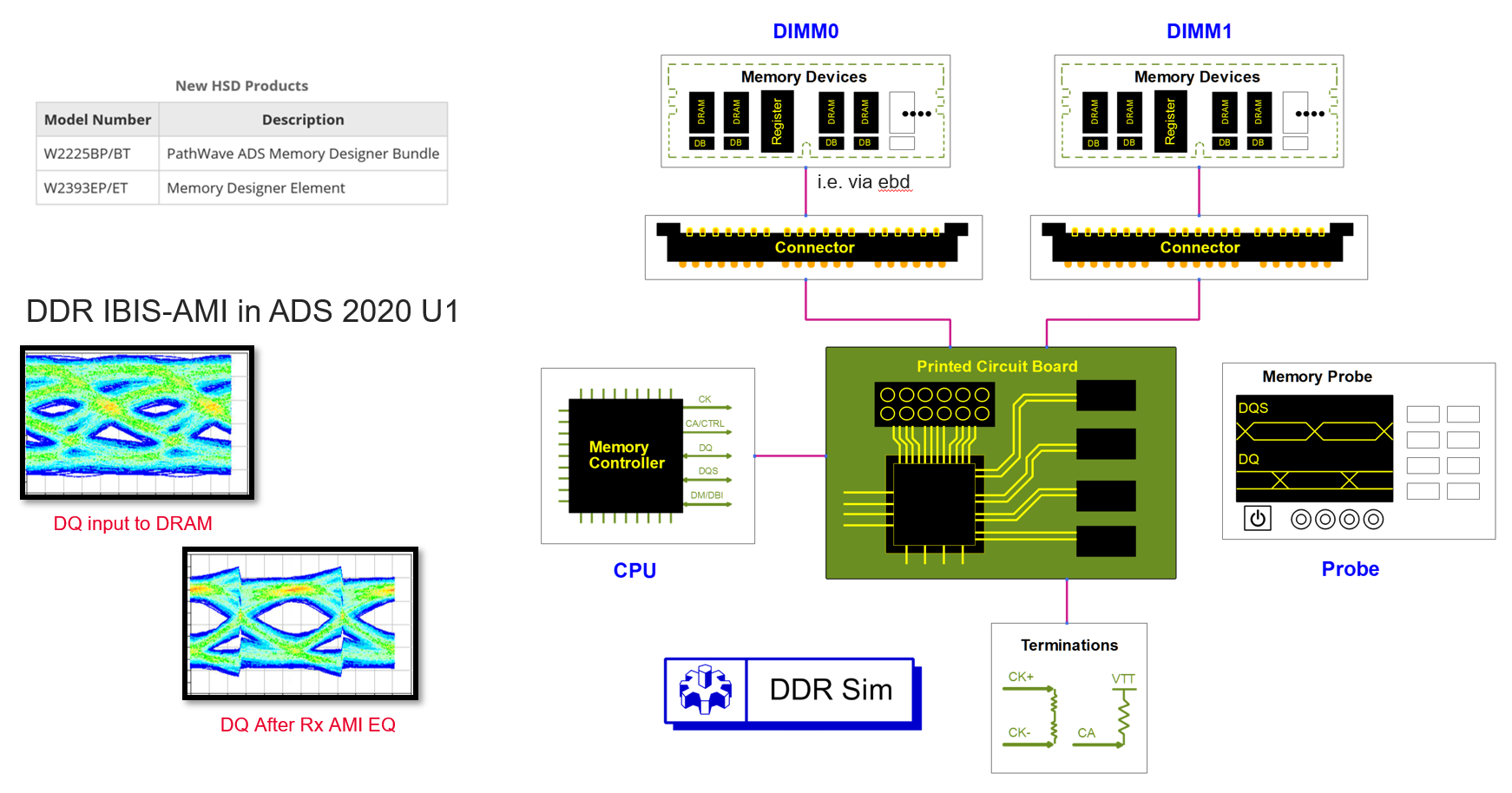

DDR/メモリ

- イコライゼーションのためのIBIS-AMIモデリングを備えた新しいDDR5およびLPDDR5ソリューション

- 内部位相補間器のトレーニングによってDFEクロック方式を最適化するためのジッタトラッキング

- シミュレートされた波形に対する自動DDR5コンプライアンステスト

- 配線を削減するためコントローラーとメモリを統合型パッケージとしてセットアップするなど、簡素化されたメモリ・デザイン・ワークフロー

- ユーザビリティー向上のための、DDR_Terminationコンポーネントに対するコントローラー、メモリ、端末GUIの改善とグループ編集

SIPro/PIPro/ビアデザイナー

- SIProでコンテキスト認識信号名マッチングアルゴリズムを採用しました

- 結果ウィンドウに遅延プロットを追加しました。

- ビアデザイナーにログ周波数プランのDC周波数(0 Hz)サポートを追加しました。

- siodumpのサンプル数を設定するオプションを追加しました。

電磁界シミュレーション

一般仕様

- 電磁界シミュレーションフローにティアドロップのサポートを追加しました

RFPro

- カスタムコンパイラーのRFProフローを実現しました

- RFProで開始およびコンポーネントのロール切り替えの速度を改善しました

回路シミュレーション

一般仕様

- カスタムルールの正規表現を変更しました

- 立ち上がり時間と立ち下がり時間を0.2 dq UIに変更しました

- プリセットに追加しなくても、指定された場合はカスタムルールを使用します

- BERのリストと[複数のBERで等高線を計算する]オプションを追加しました

- DDR_PCBテーブルのサイズ変更の問題を修正しました

- IBISモデルの選択時に完全なモデル名が表示されるようになりました

- 2つのDCD実装レポートが異なる結果を表示する問題を修正しました

- WidthAtBERは、現在、IBIS-AMIチャネルシミュレーションで密度が2UIの中心にない場合でも正しい結果を提供するようになりました

電気-熱

- ETHが、処理(クランプなど)なしで、生のTransientVars::step_reduction_factorを消費するようになりました

- 暗号化された熱テクノロジーを使用中の再利用モデル抽出に関する問題を修正しました

パワーエレクトロニクス

データシートからのモデル

- パワーMOSFETデータシートからモデルを抽出するためのテンプレートを追加しました

- パワーMOSFETデータシートからのモデル抽出を紹介するためのサンプルワークスペースを追加しました

パワー・エレクトロニクス・ライブラリに汎用パワーMOSFETコンポーネントを追加しました

IGBTサンプルワークスペース内のバグを修正しました

Power Electronics Professional (PEPro)

- PEProレイヤー表示設定パネルの表示/非表示ボタンのバグを修正しました

- 電磁界励振でデータセット選択ダイアログの情報アイコンのバグを修正しました

- 閉ループ降圧コンバーターのサンプルワークスペース内のバグを修正しました

- フィールドスケール属性のバグを修正しました

デザイン/テクノロジー管理

データディスプレイ

数式マネージャーは、すべての数式とトレース式を表形式で表示する、ドッキングウィンドウです。開いている複数のデータ・ディスプレイ・ウィンドウに、1つの数式マネージャーウィンドウで対処できるようになりました。以下に、改善点を示します。

- 参照の更新、厳選、および新たな右クリックオプションの追加を実施しました

- 従属オプションを選択すると、従属式が無効の場合、警告が表示されるようになりました

- 従属式を選択しても、デフォルトで選択にジャンプしなくなりました

デザイン編集

以下のAEL関数を追加しました。

- 選択に対するティアドロップの追加、変更、削除を実行するティアドロップAEL関数。詳細については、「ティアドロップ関数」を参照してください

- db_find_inst_term_by_name() - インスタンスオブジェクトとインスタンスターミナルの名前を指定すると、inst termを検索して返します

- db_set_edge_area_port_of_fig() - ピンフィグのエッジ/エリアポートを、渡されたタームに設定します。ターム番号0または空のターム名が渡されると、フィグのエッジ/エリアポートがクリアされます

デザインのインポート/エクスポート

- ダイオードモデルの温度係数パラメータを持つネットリストのインポートに対するサポートを追加しました

- 中括弧で囲まれたコンポーネント値を持つLTspiceネットリストのインポートに対するサポートを追加しました

デザイン・ルール・チェック(DRC)

Assura DRC

- 従属コンポーネントのアートワーク(pcell)作成時にデフォルトコンポーネントを設定するための構成を提供しました

Calibre DRC

- ルールファイルとルールフォルダーを設定するための機能を追加しました

検証テストベンチ(VTB)

シングルポートVTB(ソースのみ)シミュレーションがサポートされるようになりました。これにより、SystemVueで作成した複雑な変調ソースを、ADS Circuit Envelopeで使用することができます。

注記: SystemVue VTBのデフォルト設定では、SystemVueはシミュレーションの時間スケールを管理します。通常、VTBにシンクがある場合、シンクの設定ではシミュレーションのストップ時間が、(SystemVueワークスペース内で)要求された指標の計算に必要なデータ量の取得が可能な時間に、自動的に設定されます。VTBにシンクがない場合(入力のみのVTB)、ストップ時間はSystemVueワークスペースで明確に設定されていない可能性があります。この場合、ストップ時間が長いと、シミュレーションが長引くおそれがあります。

デフォルトでは、シミュレータはSVワークスペースのストップ時間を知らずに実行を開始するので、警告は発行されません。

ユーザーが100 n以外の値(0を除く)を設定すると、エンベロープコントローラーがマスターになります。この場合、シミュレーションは到達した最初のストップ時間(エンベロープコントローラーで設定されたストップ時間またはSystemVueワークスペースで設定されたストップ時間)で停止します。カスタムストップ時間の設定は、(タイムフレーム全体を実行する必要がない)一般的なVTBのデバッグに役立ちます。入力のみのVTBでは、現実的なストップ時間を設定するために必要になる場合があります。

注記: 100 nsに設定すると、後方互換性のため、シミュレータはそれを無視します。stop=100nは、回路図に配置したときにコントローラーに設定された値です。後方互換を保つ必要があるため、ストップ時間=100nによって、タイミングの制御は、SVワークスペースの担当に移行します。

ADS 2017以降、VTB機能に必要なファイルをインストールするには、別途VTBインストーラーをダウンロードする必要があります(Windowsのみ)。Linuxの場合、VTBインストーラーはADSインストーラーにバンドルされています。

- 互換性のあるADSインストーラーとVTBインストーラーを同じディレクトリーにダウンロードすることを推奨します。ダウンロード後、ADSインストーラーを実行します。このプロセスにより、VTB機能が自動的にインストールされます。

- ADSを既にインストールしていて、VTB機能が欠落している場合は、VTBをダウンロードしてインストールする必要があります。

- ADSのSystemVue 2018 Update 1エンジンをアップグレードしました。

- 以下のVTBを更新しました。

- 3GPP_NR_DL_Tx_Source

- 3GPP_NR_DL_Tx

- 3GPP_NR_UL_Tx_Source

- 3GPP_NR_UL_Tx

- 以下のVTBを更新しました。

- 以下に、変更を示します。

- NRダウンリンクサンプルに対して3GPP TS 38.141 V1.2.0(2018-11)で定義されたテストモデルをサポート

- NRアップリンクサンプルに対して、3GPP 38.521-1/38.521-2の表6.1-1で定義されている一般的な構成をサポート

- 測定長を1サブフレームに短縮することにより、EVM測定を高速化

- ACLR測定を追加

注記 ADS 2020 Update 1.0で使用されるSystemVueエンジンは、SystemVue 2018 Update 1.0に基づいて、いくつかの重要な問題を修正することにより進化を遂げました。そのため、上記のVTBサンプルをADS 2020 Update 1.0で実行すると正しい結果が得られますが、SystemVue 2018 Update 1.0で実行すると、エラーまたは間違った結果になる可能性があります。これらのサンプルを変更する必要がある場合は、SystemVue 2018 Update 1.0で開いて変更し、ADSに再度インポートして、ADS 2020 Update 1.0を実行して結果を確認することを推奨します。

ADS 2020 Update 1.0は、SystemVue 2018およびSystemVue 2018 Update 1.0を使用して作成されたカスタムVTB(SystemVueワークスペース)のインポートのみをサポートします。

PATHWAVE ADSの試用

PathWave ADSをご利用ください。 無料試用のお申し込み

他のADS製品のバージョンを表示できます。