尋找感興趣的產品?

PathWave 先進設計系統(ADS)2020 Update 2.0 產品發布

Highlights

PathWave 先進設計系統 (ADS) 2020 Update 2.0 針對以下應用提供各種解決方案:

- 高速數位(HSD)設計

- 電磁(EM)模擬

- 電路模擬

- 功率電子設計

- 設計與技術管理

- 設計編輯

PathWave 先進設計系統(ADS)2020 Update 1.0 現已上市!

請點擊上面的試用與授權分頁,然後點擊詳細資訊與下載按鈕,下載最新軟體。

Description

PathWave 先進系統設計(ADS)2020 Update 2.0 針對棘手的高速數位、射頻與微波,以及功率電子設計,提供諸多解決方案,這些設計包括:

PathWave 先進系統設計(ADS)2020 Update 2.0 針對棘手的高速數位、射頻與微波,以及功率電子設計,提供諸多解決方案,這些設計包括:

高速數位設計

SerDes

- 與 VPIphotonics 共同合作,針對數據通訊與電信市場,推出 E-O-E(電氣-光學-電氣)整合式工作流程,讓使用者能夠將端對端鏈路分析設計中的光通道效應納入考量,例如:

- 電吸收調變器(EAM)的非線性波長相依轉移函數

- 非線性度

- 相對強度雜訊(RIN)

- 光纖衰減

- 色散

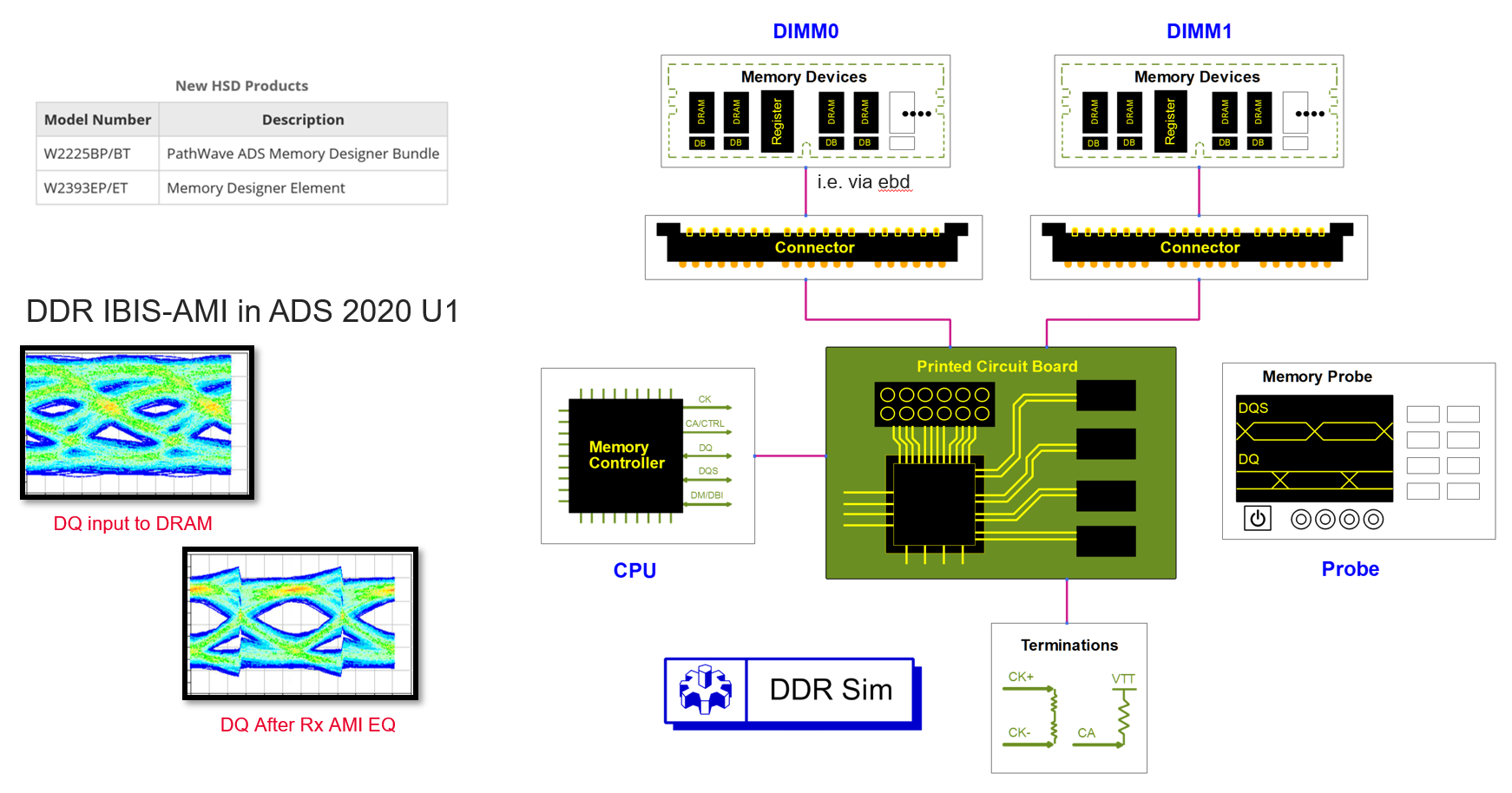

DDR/記憶體

- 全新 DDR5 與 LPDDR5 解決方案,採用 IBIS-AMI 建模來支援等化

- 透過內部相位插入器訓練來追蹤抖動,以實現最佳 DFE 時脈

- 自動對模擬波形進行 DDR5 相符性測試

- 簡化記憶體設計工作流程,例如在控制器與記憶體中整合封裝配置,以減少接線操作

- 改善控制器、記憶體和終端圖形操作介面,並提供對 DDR_Termination 元件進行群組編輯的功能,更方便使用

SIPro/PIPro/Via Designer

- 在 SIPro 中提供情境感知信號名稱匹配演算法

- 在結果視窗中新增延遲圖

- 在導孔設計程序中,使用對數頻率計畫支援直流頻率(0 Hz)

- 新增可設定 siodump 樣本數的選項

電磁模擬

一般

- 在電磁模擬流程中新增對 Teardrops 的支援

RFPro

- 針對客製編譯器啟用 RFPro 流程

- 改善 RFPro 的開啟速度與元件角色變更功能

電路模擬

一般

- 修改了自訂規則正規表達式

- 將上升與下降時間變更為 0.2 dq UI

- 可在指定規則時使用自訂的規則,不需將它添加到預設中

- 新增 BER 清單及「計算多個 BER 下的輪廓」 選項

- 修正 DDR_PCB 表格調整大小的問題

- IBIS 模型選擇設定,現在可顯示完整的模型名稱

- 修正兩個 DCD 部署報告顯示不同結果的問題

- 進行 IBIS-AMI 通道模擬時,Density(密度)不在 2UI 中心,WidthAtBER 現在可提供正確的結果

電熱

- ETH 現在支援使用原始的 TransientVars::step_reduction_factor 資料,不需進行任何處理(數據截斷等)

- 修正了使用加密熱技術時,重新使用模型萃取的問題

功率電子

透過技術資料萃取模型

- 新增樣板,可透過功率 MOSFET 技術資料萃取模型

- 新增範例工作區,用於展示如何從功率 MOSFET 技術資料萃取模型

在功率電子元件庫中添加一般功率 MOSFET 元件

修正 IGBT 範例工作區中的錯誤

Power Electronics Professional(PEPro)

- 修正 PEPro 層顯示設定面板中的顯示/隱藏按鈕錯誤

- 修正電路激發中選擇資料集對話框之資訊圖示的錯誤

- 修正閉迴路降壓轉換器範例工作區中的錯誤

- 修正場刻度屬性中的錯誤

計與技術管理

資料顯示

Expression Manager 是一種停駐視窗,可在同一表格中顯示所有方程式與軌跡方程式。現在您只需一個 Expression Manager 視窗,即可顯示多個開啟的資料顯示視窗。以下為經過增強的功能:

- 提供參考更新、選擇,並且新增單擊右鍵的選項

- 選擇相關選項後,您可看到已停用此方程式的警示

- 在預設下,選擇相關方程式不會跳轉到選擇(selection)設定

設計編輯

新增以下 AEL 功能:

- Tear drop AEL 功能,可在 selection 設定中新增、修改並移除 tear drop。如需更多資訊,請參閱 Teardrop 功能

- db_find_inst_term_by_name() - 只要提供實例物件和實例終端名稱,即可尋找並返回實例終端。

- db_set_edge_area_port_of_fig() - 將針腳圖的邊緣/區域埠,設定為傳入項。若傳入項為 0,或傳入項名稱空白,將清除圖中的邊緣/區域埠

設計匯入/匯出

- 新增對匯入網表的支援,其中包含二極體模型溫度係數參數

- 新增對匯入 LTspice 網表的支援,其中的元件參數值用大括弧括起來

設計規則檢查(DRC)

Assura DRC

- 提供的配置可設定預設元件,進而產生相關元件的圖片(pcell)

Calibre DRC

- 新增可設定規則檔案與規則資料夾的功能

驗證測試工作台(VTB)

現在支援單埠 VTB(僅限信號源)模擬。現在您可在 SystemVue 中建立複雜調變信號源,並在 ADS 電路波封中使用。

註:在 SystemVue VTB 的預設下,SystemVue 可管理模擬的時間刻度。一般而言,若 VTB 有汲入功能,此功能將在 SystemVue 工作區中被設定為,自動設定模擬停止時間,以取得計算要求的品質因素所需的資料量。若 VTB 沒有汲入功能(純輸入的 VTB),則可能無法在 SystemVue 工作區中設定精準的停止時間。在此情況下,若停止時間較長,可能會導致停止時間過長。

在預設下,這種情形不會發出警示,因為在執行前,模擬器並不清楚 SV 工作區的停止時間。

若使用者設定了 100n(不含 0)以外的數值,波封控制器將成為主機。在此情況下,模擬會停在第一個到達的停止時間(在波封控制器中設定的停止時間,或是在 SystemVue 工作區中設定的停止時間,取兩者較小值)。設定自訂的停止時間,可以讓您更有效地對一般 VTB 進行除錯(不需執行整個時間範圍);對純輸入的 VTB 進行除錯時,則一定要自訂停止時間,讓模擬能在達到一個實際的時間時停止,避免執行時間過長。

註:如果將數值設定為 100ns,為了達到向後相容,模擬器會忽略它。將它放在電路圖中時,停止時間 = 100n 便是在控制器中設定的值。為了達到向後相容,停止時間 = 100n 代表讓 SV 工作區來控制計時。

自 ADS 2017 開始,若要安裝 VTB 功能所需的檔案,必須另外下載一個 VTB 安裝程式(僅適用於 Windows 平台)。若為 Linux 平台,VTB 安裝程式會隨 ADS 安裝程式提供。

- 建議您可將 ADS 與 VTB 安裝程式下載到同一目錄中。下載後請執行 ADS 安裝程式。此程序會自動安裝 VTB 功能

- 若安裝 ADS 後找不到 VTB 功能,請另行下載並安裝 VTB

- 在 ADS 中升級 SystemVue 2018 Update 1 引擎

- 更新以下 VTB:

- 3GPP_NR_DL_Tx_Source

- 3GPP_NR_DL_Tx

- 3GPP_NR_UL_Tx_Source

- 3GPP_NR_UL_Tx

- 更新以下 VTB:

- 相關修訂如下:

- 支援 3GPP TS 38.141 V1.2.0(2018-11) 標準中,對 NR 下行鏈路範例所定義的測試模型

- 支援 3GPP 38.521-1/38.521-2 標準,表 6.1-1對 NR 上行鏈路範例所定義的一般配置

- 將量測長度縮減至 1 個子訊框,以加快 EVM 量測

- 新增 ACLR 量測

註:ADS 2020 Update 1.0 使用的 SystemVue 引擎在 SystemVue 2018 Update 1.0 基礎上進行了重要問題的修正。因此,雖然在 ADS 2020 Update 1.0 中執行上述 VTB 範例可獲得正確結果,但如果是在 SystemVue 2018 Update 1.0 中執行,可能會產生誤差或得到錯誤結果。若需修改這些範例,建議您以 SystemVue 2018 Update 1.0 開啟並進行修改,接著將其匯回 ADS 並執行 DS 2020 Update 1.0,以觀察結果。

ADS 2020 Update 1.0 僅支援匯入以 SystemVue 2018 與 SystemVue 2018 Update 1.0 建立的自訂 VTB (SystemVue 工作區)。

立即行動

準備好開始使用 PathWave ADS 了嗎?申請免費試用。

查看其他 ADS 產品版本。