O que você está procurando?

Computação de IA

Teste chips de IA e projetos digitais de alta velocidade.

Acelere o teste de semicondutores com IA e o design de HSD

Desbloqueie o futuro dos semicondutores prontos para IA e dos designs digitais de alta velocidade (HSD). Projete e teste chips de IA, solucione problemas de projetos de ponta e atenda ou supere os mais recentes padrões PCIe, DDR e CXL com ferramentas avançadas de projeto, depuração e conformidade - otimizadas para data centers de IA.

Aumente seu conhecimento em computação de IA

5 estratégias para otimizar e dimensionar os data centers de IA

A IA está transformando os setores e impulsionando a inovação. Isso significa que os arquitetos de rede devem gerenciar as crescentes demandas do data center, incluindo padrões de tráfego exclusivos, cargas de trabalho dinâmicas e pressões implacáveis de desempenho.

Leia este eBook para descobrir cinco soluções práticas para otimizar o desempenho do data center de IA para aplicativos modernos.

Aceleração da inovação em IA com engenharia de projeto simultânea

O projeto de chips de IA está ficando mais difícil devido a obstáculos técnicos e econômicos, como complexidade, custo e consumo de energia. Leia este eBook para saber como acelerar o desenvolvimento de chips de IA no design de chiplets, pesquisa 6G, fornecimento de energia e gerenciamento do ciclo de vida da engenharia.

A evolução dos padrões PCIe® e dos requisitos de teste

Os data centers enfrentam demandas crescentes para atingir velocidades mais rápidas - e a IA está acelerando a demanda. À medida que as velocidades da Ethernet ultrapassam 800GE, o PCIe® 6.0, a mais recente iteração do padrão PCIe® (Peripheral Component Interconnect Express®), está acelerando a inovação do data center.

Padrões de design digital e interconexão

Quando os sinais digitais atingem velocidades de gigabit, "o imprevisível" se torna normal. E quando se trata de padrões digitais, cada nova geração e avanço tecnológico coloca novos obstáculos em seu caminho. Explore as ferramentas de simulação, medição e conformidade para superar os desafios dos projetos digitais de gigabit.

Projetar e testar chips e semicondutores de IA

Acelere os ciclos de projeto, antecipe os desafios de conformidade, otimize o desempenho eletrônico e ofereça inovações líderes de mercado com mais rapidez.

Solucionar problemas de projetos digitais de alta velocidade otimizados para IA

Reduza as rotações do projeto, teste os semicondutores de IA e analise o desempenho da placa de circuito impresso (PCB) com instrumentos precisos e de alto desempenho.

Atender ou superar os mais recentes padrões de rede de IA

Simplifique e acelere os testes de conformidade com soluções de teste automatizadas para os principais padrões de data center de IA, incluindo PCIe®, CXL e DDR.

Teste chips de IA e depure projetos de HSD com a Keysight

Depure projetos prontos para IA com integridade de sinal inigualável

Reduza os ciclos de prototipagem, acelere o tempo de lançamento no mercado e melhore a confiabilidade da infraestrutura do data center com os osciloscópios da série UXR B da Keysight. Solucione problemas de desempenho da camada física com as mais altas medições de integridade de sinal para criar dispositivos de alta velocidade para os data centers de IA do futuro.

Garanta a conformidade com os padrões de computação de IA de última geração

Caracterize receptores e interfaces de servidor para redes de data center de IA com os testadores de taxa de erro de bits (BERTs) da Keysight. Melhore o pathfinding para 1,6T e aplicativos de ponta com integridade de sinal inflexível, suporte a NRZ / PAM4 / PAM6 / PAM8 e taxas de dados de até 120 Gbaud.

Acelere o desenvolvimento de projetos a 160 Gbaud e além

Os geradores de forma de onda arbitrária (AWGs) da Keysight oferecem velocidade, largura de banda e precisão para atender às demandas de testes de semicondutores de IA e implantações de data centers de IA. Teste comunicações de alta densidade, caracterize o desempenho do projeto e force os dispositivos até seus limites.

Obtenha uma visão clara e precisa do tráfego de links PCIe®.

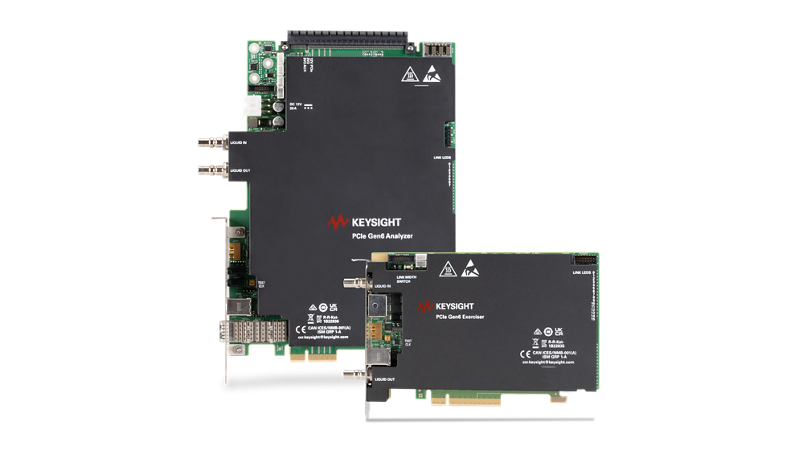

Realize análises profundas de protocolo em sistemas PCIe® com integridade de sinal incomparável. O analisador de protocolo PCIe da Keysight emula e visualiza o tráfego de dados, identificando problemas para validar hosts e endpoints para prontidão do data center de IA - tudo em um fator de forma plugável e sem cabos para calibração rápida.

Simplifique os fluxos de trabalho de projeto com produtos EDA

Simplifique os insights de vários domínios em todo o ciclo de design com os produtos de automação de design eletrônico (EDA) da Keysight. Preveja desafios de design, simule chips de IA e modelos de semicondutores e forneça produtos pioneiros no mercado com modelos de design, bibliotecas de componentes, modelagem robusta e simulações precisas.

O caminho para o PCIe® 7

Você está pronto para abraçar o futuro da transferência de dados? O PCIe® 7 e o CXL oferecem taxas de dados mais rápidas para aplicativos de alto desempenho, como IA e aprendizado de máquina. Novas tecnologias, como a sinalização PAM4 a 32 Gbaud, são um salto significativo em relação às tecnologias mais antigas baseadas em NRZ, exigindo tolerâncias rigorosas, especificações em evolução e novos modelos de componentes.

Neste webinar, você aprenderá sobre os desafios de projetar para esses padrões e explorará soluções de conformidade orientadas por simulação usando fluxos de trabalho do Método de Implementação (MOI) para certificar testes de conformidade.

Casos de uso para teste de computação de IA e validação de PCB

Analisar a integridade do sinal da placa de circuito impresso

Reduza os riscos de integridade do sinal em uma PCB digital de alta velocidade por meio da detecção e do diagnóstico de diafonia, jitter, ruído vertical e ruído de fase.

Realizar a validação do protocolo PCle® 6.0

Obter validação de protocolo nas camadas física, de link de dados e de transação.

Teste de conformidade do transmissor DDR5

Executar uma ampla gama de testes de conformidade com base nos padrões JEDEC.

Teste a conformidade do receptor PCIe® 6.0

Calibre os sinais de estresse e teste a conformidade do receptor PCIe®.

Saiba mais sobre a computação de IA

Perguntas frequentes: Computação de IA

À medida que os data centers são dimensionados para suportar o crescimento exponencial do tráfego, a infraestrutura de computação de IA da qual eles dependem - incluindo CPUs, GPUs, aceleradores e interfaces de memória - exige testes mais rigorosos. A validação agora deve abordar interfaces digitais de velocidade ultra-alta, como PCIe, CXL, DDR e HBM, que são fundamentais para o desempenho do data center moderno. Os testes de semicondutores estão evoluindo com ferramentas avançadas, como os osciloscópios de conformidade em tempo real, os analisadores de protocolo e os BERTs da Keysight, para validar a integridade e a conformidade da camada física sob condições de estresse no nível do data center. Os testes agora priorizam a integridade do sinal, o desempenho, a eficiência energética e a confiabilidade em servidores densos e implementações de silício personalizado.

Os data centers modernos são construídos com base em chipsets complexos, com margens de tempo apertadas e requisitos de taxa de transferência maciça. Ferramentas avançadas de teste de semicondutores - como os AWGs da Keysight, osciloscópios de alto desempenho e software de teste de receptor - fornecem geração e análise de sinal de precisão para garantir recursos confiáveis de alta velocidade. Essas ferramentas ajudam a detectar jitter, degradação de sinal e qualidade de sinal nos subsistemas de memória e E/S. Para os hiperescaladores que criam chips personalizados para cargas de trabalho como computação de IA, armazenamento, rede e virtualização, essas soluções de teste aceleram a qualificação e reduzem os problemas em nível de sistema após a implantação. Em última análise, a validação aprimorada significa menos falhas no campo e melhor tempo de atividade para os serviços de data center.

O desenvolvimento de chips para data centers exige ciclos rápidos e alto volume de produção. A redução do tempo e do custo dos testes depende da cobertura inteligente dos testes, do uso eficiente de equipamentos automatizados e da simulação robusta no início da fase de projeto. Os pacotes de EDA da Keysight - incluindo ferramentas como SIPro (análise de integridade de sinal) e System Design - permitem que os engenheiros simulem e validem canais de alta velocidade antes do tape-out. Na bancada, instrumentos como BERTs e osciloscópios de conformidade em tempo real simplificam a conformidade e a depuração de PCIe/CXL e interfaces de memória, reduzindo o retrabalho dispendioso e acelerando o tempo de implantação.

A validação dos sistemas de computação do data center requer uma combinação de medições da camada física, dados de conformidade de protocolo e dados de estresse ambiental. Os engenheiros de teste reúnem métricas de desempenho em tempo real, como taxas de erro de bits, diagramas oculares, TDECQ, tolerância a jitter e margining de pista de equipamentos como BERTs, osciloscópios e AWGs. Além disso, os dados de simulação de ferramentas como o PHY Designer ou o RF Circuit Simulation Professional da Keysight são usados para verificar o comportamento nas piores condições possíveis. Esses dados são essenciais para garantir que os chips de servidor, os módulos de memória e as interconexões operem de forma confiável em escala e sob as exigentes cargas de trabalho típicas de ambientes de hiperescala.

À medida que os projetos de computação de IA do data center aumentam os limites de largura de banda e reduzem as margens de energia, os engenheiros enfrentam desafios de integridade de sinal, conformidade de protocolo e estabilidade térmica. Testar chiplets, memória empilhada e caminhos de E/S personalizados - geralmente em vários domínios de tensão - requer ferramentas precisas e visibilidade profunda do protocolo. Também é difícil integrar a validação de alta velocidade nos fluxos de trabalho sem interromper o rendimento ou o tempo de colocação no mercado. Ferramentas como o Design Data e o IP Data Management da Keysight ajudam a rastrear a cobertura do teste, enquanto os analisadores de protocolo e as suítes de simulação avançada reduzem as surpresas nos estágios finais. Garantir a escalabilidade das configurações de teste em padrões de interconexão em evolução, como PCIe 6.0 e CXL 3.0, é uma preocupação constante.

As principais tendências incluem o aumento de arquiteturas compostas e desagregadas, a adoção de designs baseados em chiplets e silício personalizado para otimização de energia. As práticas recomendadas para testar a computação de IA do data center incluem começar com a simulação (usando ferramentas de EDA como o SIPro), aproveitar a automação de testes de conformidade em osciloscópios e BERTs em tempo real e correlacionar os resultados em nível de bancada com o desempenho em nível de sistema. Os hiperescaladores estão cada vez mais trazendo os testes para dentro de casa para obter maior controle e iteração mais rápida, usando plataformas de validação integradas que combinam camadas físicas, de protocolo e de gerenciamento de dados para fornecer computação de IA mais rápida e confiável em escala.

Deseja ajuda ou tem dúvidas?