¿Qué busca?

Informática AI

Pruebe chips de inteligencia artificial y diseños digitales de alta velocidad.

Acelerar las pruebas de semiconductores AI y el diseño HSD

Descubra el futuro de los semiconductores preparados para la IA y los diseños digitales de alta velocidad (HSD). Diseñe y pruebe chips de IA, solucione problemas de diseños de vanguardia y cumpla o supere los últimos estándares PCIe, DDR y CXL con herramientas avanzadas de diseño, depuración y conformidad, optimizadas para centros de datos de IA.

Aumente sus conocimientos en informática de IA

5 estrategias para optimizar y ampliar los centros de datos de IA

La IA está transformando las industrias e impulsando la innovación. Esto significa que los arquitectos de redes deben gestionar las crecientes demandas de los centros de datos, incluyendo patrones de tráfico únicos, cargas de trabajo dinámicas y presiones de rendimiento implacables.

Lea este libro electrónico para descubrir cinco soluciones prácticas para optimizar el rendimiento del centro de datos de IA para aplicaciones modernas.

Acelerar la innovación en IA con ingeniería de diseño concurrente

El diseño de chips de IA es cada vez más difícil debido a obstáculos técnicos y económicos como la complejidad, el coste y el consumo energético. Lea este eBook para saber cómo acelerar el desarrollo de chips de IA en el diseño de chips, la investigación 6G, el suministro de energía y la gestión del ciclo de vida de la ingeniería.

Evolución de las normas PCIe® y requisitos de las pruebas

Los centros de datos se enfrentan a una creciente demanda de velocidades más rápidas, y la IA está acelerando la demanda. A medida que las velocidades de Ethernet superan los 800GE, PCIe® 6.0, la última iteración del estándar Peripheral Component Interconnect Express® (PCIe®), acelera la innovación en los centros de datos.

Diseño digital y normas de interconexión

Cuando las señales digitales alcanzan velocidades de gigabit, "lo imprevisible" se convierte en normal. Y cuando se trata de estándares digitales, cada nueva generación y avance tecnológico pone nuevos obstáculos en su camino. Explore las herramientas de simulación, medición y conformidad para superar los retos de los diseños digitales gigabit.

Diseñar y probar chips y semiconductores de IA

Acelere los ciclos de diseño, anticípese a los problemas de conformidad, optimice el rendimiento electrónico y ofrezca innovaciones líderes en el mercado con mayor rapidez.

Resolución de problemas en diseños digitales de alta velocidad optimizados para IA

Reduzca las vueltas de diseño, pruebe los semiconductores AI y analice el rendimiento de las placas de circuitos impresos (PCB) con instrumentos precisos y de alto rendimiento.

Cumplen o superan las normas más recientes sobre redes de IA

Simplifique y acelere las pruebas de conformidad con soluciones de pruebas automatizadas para los principales estándares de centros de datos de IA, incluidos PCIe®, CXL y DDR.

Pruebe chips AI y depure diseños HSD con Keysight

Depuración de diseños preparados para IA con una integridad de señal inigualable

Reduzca los ciclos de creación de prototipos, acelere el tiempo de comercialización y mejore la fiabilidad de la infraestructura del centro de datos con los osciloscopios Keysight UXR Serie B. Solucione los problemas de rendimiento de la capa física con las más altas mediciones de integridad de señal para construir dispositivos de alta velocidad para los centros de datos de IA del mañana.

Garantizar el cumplimiento de las normas de computación de IA de próxima generación

Caracterice receptores e interfaces de servidor para redes de centros de datos de IA con los comprobadores de relación de bits erróneos (BERT) de Keysight. Mejore la búsqueda de rutas para 1,6T y aplicaciones de vanguardia con integridad de señal sin concesiones, compatibilidad con NRZ / PAM4 / PAM6 / PAM8 y velocidades de datos de hasta 120 Gbaud.

Acelerar el desarrollo de diseños a 160 Gbaud y más

Los generadores de forma de onda arbitraria (AWG) de Keysight ofrecen la velocidad, el ancho de banda y la precisión para satisfacer las demandas de las pruebas de semiconductores de IA y los despliegues de centros de datos de IA. Pruebe comunicaciones de alta densidad, caracterice el rendimiento del diseño y lleve los dispositivos al límite.

Obtenga una visión clara y precisa del tráfico de enlaces PCIe

Realice análisis profundos de protocolos en sistemas PCIe® con una integridad de señal inigualable. El analizador de protocolos PCIe de Keysight emula y visualiza el tráfico de datos, identificando problemas para validar hosts y puntos finales para la preparación del centro de datos de IA, todo en un factor de forma conectable y sin cables para una calibración rápida.

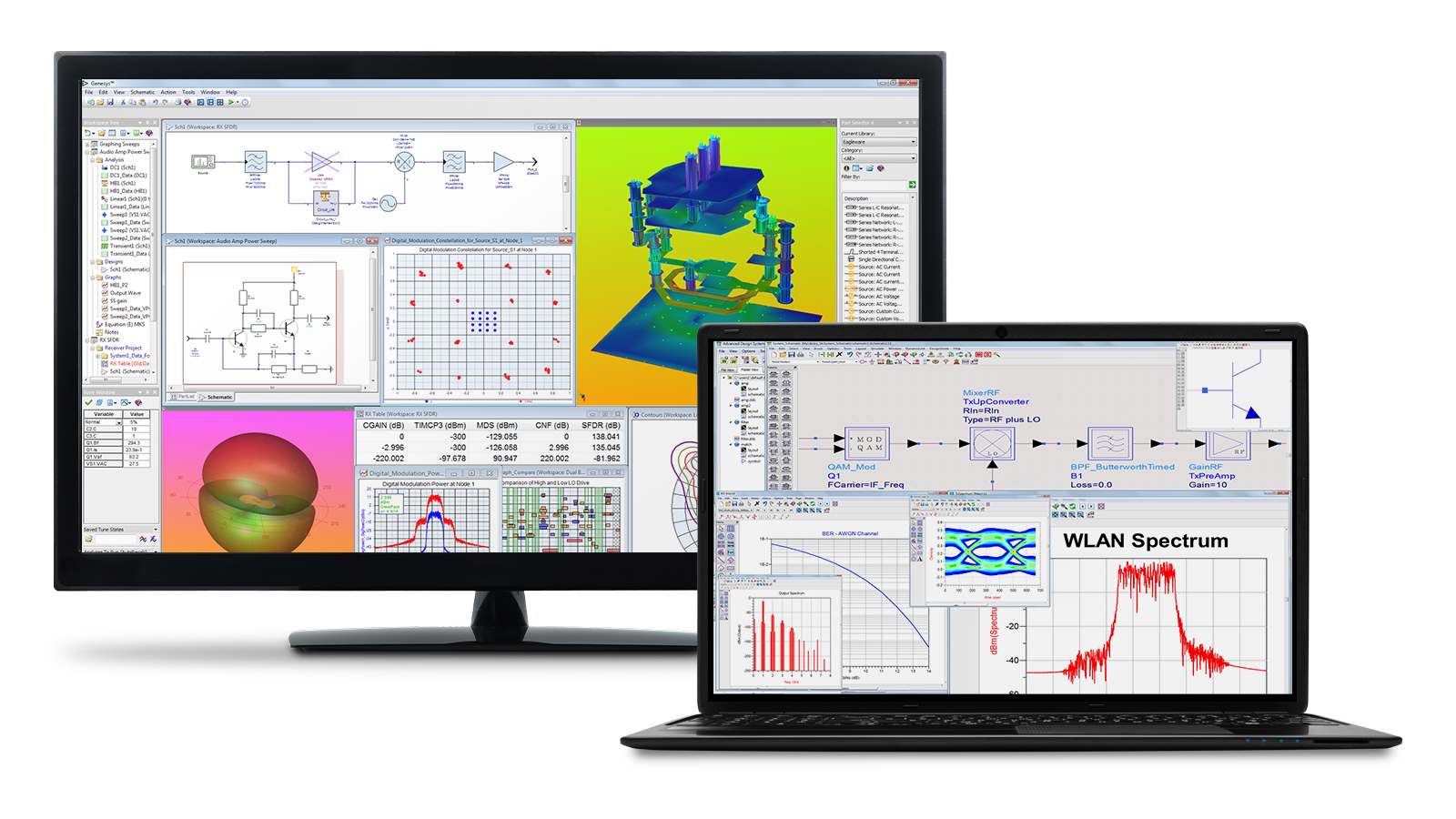

Agilice los flujos de trabajo de diseño con productos EDA

Simplifique los conocimientos multidominio a lo largo del ciclo de diseño con los productos de automatización del diseño electrónico (EDA) de Keysight. Prevea los retos de diseño, simule chips de IA y modelos de semiconductores, y ofrezca productos de primera salida al mercado con plantillas de diseño, bibliotecas de componentes, modelado robusto y simulaciones precisas.

El camino hacia PCIe® 7

¿Está preparado para adoptar el futuro de la transferencia de datos? PCIe® 7 y CXL ofrecen velocidades de datos más rápidas para aplicaciones de alto rendimiento, como la IA y el aprendizaje automático. Las nuevas tecnologías, como la señalización PAM4 a 32 Gbaudios, suponen un salto significativo con respecto a las antiguas tecnologías basadas en NRZ, lo que requiere tolerancias estrictas, especificaciones en evolución y nuevos modelos de componentes.

En este seminario web, conocerá los retos que plantea el diseño para estas normas y Explorerá soluciones de conformidad basadas en la simulación utilizando flujos de trabajo del Método de Implementación (MOI) para certificar las pruebas de conformidad.

Casos prácticos de pruebas informáticas de IA y validación de PCB

Analizar la integridad de la señal PCB

Reduzca los riesgos de integridad de la señal en una PCB digital de alta velocidad mediante la detección y el diagnóstico de diafonía, fluctuación, ruido vertical y ruido de fase.

Realice la validación del protocolo PCle® 6.0

Lograr la validación de protocolos en las capas física, de enlace de datos y de transacción.

Prueba de conformidad del transmisor DDR5

Ejecutar una amplia gama de pruebas de conformidad basadas en las normas JEDEC.

Prueba de conformidad del receptor PCIe® 6.0

Calibre las señales de tensión y compruebe la conformidad del receptor PCIe®.

Más información sobre AI Compute

Preguntas más frecuentes: AI Compute

A medida que los centros de datos se amplían para soportar un crecimiento exponencial del tráfico, la infraestructura informática de IA de la que dependen -incluidas CPU, GPU, aceleradores e interfaces de memoria- requiere pruebas más rigurosas. La validación debe abordar ahora las interfaces digitales de velocidad ultrarrápida, como PCIe, CXL, DDR y HBM, que son fundamentales para el rendimiento de los centros de datos modernos. Las pruebas de semiconductores están evolucionando con herramientas avanzadas como los osciloscopios de cumplimiento en tiempo real, los analizadores de protocolos y los BERT de Keysight para validar la integridad y el cumplimiento de la capa física en condiciones de estrés a nivel de centro de datos. Las pruebas ahora priorizan la integridad de la señal, el rendimiento, la eficiencia energética y la fiabilidad en implementaciones de servidores densos y silicio personalizado.

Los centros de datos modernos se basan en conjuntos de chips complejos con márgenes de sincronización muy ajustados y requisitos de rendimiento masivos. Las herramientas Advanced de prueba Advanced —como los generadores de ondas arbitrarias (AWG) de Keysight, los osciloscopios de alto rendimiento y el software de prueba de receptores — proporcionan una generación y un análisis de señales de precisión para garantizar capacidades fiables a alta velocidad. Estas herramientas ayudan a detectar fluctuaciones, degradación de la señal y problemas de calidad de la señal en los subsistemas de memoria y E/S. Para los hiperescaladores que desarrollan chips personalizados para cargas de trabajo como computación de IA, almacenamiento, redes y virtualización, estas soluciones de prueba aceleran la cualificación y reducen los problemas a nivel de sistema tras la implementación. En última instancia, una validación mejorada se traduce en menos fallos sobre el terreno y un mayor tiempo de actividad para los servicios de los centros de datos.

El desarrollo de chips para centros de datos exige ciclos rápidos y grandes volúmenes de producción. Reducir el tiempo y el coste de las pruebas depende de una cobertura de pruebas inteligente, un uso eficiente de los equipos automatizados y una simulación robusta en una fase temprana del diseño. Los paquetes EDA de Keysight, que incluyen herramientas como SIPro (análisis de integridad de la señal) y System Design, permiten a los ingenieros simular y validar los canales de alta velocidad antes de grabarlos. En el banco, instrumentos como los BERT y los osciloscopios de conformidad en tiempo real agilizan la conformidad y la depuración para PCIe / CXL y las interfaces de memoria, reduciendo las costosas repeticiones y acelerando el tiempo de implementación.

La validación de los sistemas informáticos de los centros de datos requiere una combinación de mediciones de la capa física, datos de cumplimiento de protocolos y datos de estrés ambiental. Los ingenieros de pruebas recopilan métricas de rendimiento en tiempo real, como tasas de error de bits, diagramas de ojo, TDECQ, tolerancia al jitter y márgenes de carril de equipos como BERT, osciloscopios y AWG. Además, se utilizan datos de simulación de herramientas como PHY Designer o RF Circuit Simulation Professional de Keysight para verificar el comportamiento en las peores condiciones. Estos datos son fundamentales para garantizar que los chips de servidor, los módulos de memoria y las interconexiones funcionen de forma fiable a escala y bajo las exigentes cargas de trabajo típicas de los entornos de hiperescala.

A medida que los diseños de computación de IA para centros de datos superan los límites de ancho de banda y reducen los márgenes de potencia, los ingenieros se enfrentan a retos de integridad de la señal, cumplimiento de protocolos y estabilidad térmica. Las pruebas de chiplets, memoria apilada y rutas de E/S personalizadas, a menudo en varios dominios de tensión, requieren herramientas precisas y una gran visibilidad de los protocolos. También es difícil integrar la validación de alta velocidad en los flujos de trabajo sin interrumpir el rendimiento o el tiempo de comercialización. Herramientas como Design Data e IP Data Management de Keysight ayudan a realizar un seguimiento de la cobertura de las pruebas, mientras que los analizadores de protocolos y las suites de simulación avanzadas reducen las sorpresas de última hora. Garantizar la escalabilidad de las configuraciones de prueba a través de estándares de interconexión en evolución como PCIe 6.0 y CXL 3.0 es una preocupación constante.

Las tendencias clave incluyen el aumento de las arquitecturas componibles y desagregadas, la adopción de diseños basados en chiplets y el silicio personalizado para la optimización de la energía. Las mejores prácticas para probar la computación de IA en centros de datos incluyen comenzar con la simulación (utilizando herramientas EDA como SIPro), aprovechar la automatización de las pruebas de conformidad en osciloscopios en tiempo real y BERT, y correlacionar los resultados a nivel de banco con el rendimiento a nivel de sistema. Los hiperescaladores cada vez realizan más pruebas internas para tener un mayor control y una iteración más rápida, utilizando plataformas de validación integradas que combinan capas físicas, de protocolo y de gestión de datos para ofrecer una informática de IA más rápida y fiable a escala.

¿Necesita ayuda o tiene alguna pregunta?