Können wir Ihnen behilflich sein?

AI-Rechner

Testen Sie AI-Chips und digitale Hochgeschwindigkeitsdesigns.

Beschleunigung von AI-Halbleitertests und HSD-Design

Erschließen Sie die Zukunft von KI-fähigen Halbleitern und High-Speed-Digital-Designs (HSD). Entwerfen und testen Sie KI-Chips, beheben Sie Fehler in modernsten Designs und erfüllen oder übertreffen Sie die neuesten PCIe-, DDR- und CXL-Standards mit fortschrittlichen Design-, Debugging- und Compliance-Tools - optimiert für KI-Rechenzentren.

Erweitern Sie Ihr Wissen im Bereich KI-Computing

5 Strategien zur Optimierung und Skalierung von KI-Rechenzentren

KI transformiert Branchen und treibt Innovationen voran. Das bedeutet, dass Netzwerkarchitekten die steigenden Anforderungen an Rechenzentren bewältigen müssen – einschließlich einzigartiger Datenverkehrsmuster, dynamischer Workloads und unerbittlichen Leistungsdrucks.

In diesem eBook finden Sie fünf praktische Lösungen zur Optimierung der KI-Rechenzentrumsleistung für moderne Anwendungen.

Beschleunigung der KI-Innovation durch gleichzeitige Entwicklung

Die Entwicklung von KI-Chips wird aufgrund technischer und wirtschaftlicher Hürden wie Komplexität, Kosten und Stromverbrauch immer schwieriger. In diesem eBook erfahren Sie, wie Sie die Entwicklung von KI-Chips in den Bereichen Chiplet-Design, 6G-Forschung, Energieversorgung und Engineering Lifecycle Management beschleunigen können.

Die Entwicklung der PCIe®-Standards und Testanforderungen

Rechenzentren müssen immer höhere Geschwindigkeiten erreichen - und KI beschleunigt die Nachfrage. Während die Ethernet-Geschwindigkeiten die 800GE-Marke überschreiten, beschleunigt PCIe® 6.0, die neueste Iteration des Peripheral Component Interconnect Express® (PCIe®)-Standards, die Innovation in Rechenzentren.

Digitaler Entwurf und Verbindungsnormen

Wenn digitale Signale Gigabit-Geschwindigkeiten erreichen, wird "das Unvorhersehbare" zur Normalität. Und wenn es um digitale Standards geht, stellt jede neue Generation und jeder technologische Fortschritt neue Hindernisse in den Weg. Entdecken Sie Tools für Simulation, Messung und Konformität, um die Herausforderungen digitaler Gigabit-Designs zu meistern.

Entwurf und Test von KI-Chips und -Halbleitern

Beschleunigen Sie die Designzyklen, antizipieren Sie Herausforderungen bei der Einhaltung von Vorschriften, optimieren Sie die elektronische Leistung, und liefern Sie schneller marktführende Innovationen.

Fehlersuche bei AI-optimierten digitalen Hochgeschwindigkeitsdesigns

Verringern Sie die Anzahl der Designspins, testen Sie AI-Halbleiter und analysieren Sie die Leistung von Leiterplatten (PCB) mit präzisen, leistungsstarken Instrumenten.

Erfüllen oder übertreffen die neuesten AI-Netzwerkstandards

Vereinfachen und beschleunigen Sie Konformitätstests mit automatisierten Testlösungen für führende KI-Rechenzentrumsstandards - einschließlich PCIe®, CXL und DDR.

Testen von AI-Chips und Debuggen von HSD-Designs mit Keysight

Debuggen von AI-fähigen Designs mit unübertroffener Signalintegrität

Verkürzen Sie die Prototyping-Zyklen, beschleunigen Sie die Markteinführung und verbessern Sie die Zuverlässigkeit der Rechenzentrumsinfrastruktur mit Keysight Oszilloskopen der UXR B-Serie. Prüfen Sie die Leistung der physikalischen Schicht mit den höchsten Signalintegritätsmessungen, um Hochgeschwindigkeitsgeräte für die KI-Rechenzentren von morgen zu entwickeln.

Stellen Sie die Einhaltung der KI-Rechenstandards der nächsten Generation sicher

Charakterisieren Sie Empfänger und Serverschnittstellen für KI-Rechenzentrumsnetzwerke mit Keysight Bit Error Ratio Testern (BERTs). Verbessern Sie die Pfadfindung für 1.6T und hochmoderne Anwendungen mit kompromissloser Signalintegrität, NRZ / PAM4 / PAM6 / PAM8-Unterstützung und Datenraten bis zu 120 Gbaud.

Beschleunigung der Designentwicklung bei 160 Gbaud und darüber hinaus

Keysight Arbitrary Waveform Generators (AWGs) bieten die Geschwindigkeit, Bandbreite und Präzision, um die Anforderungen von KI-Halbleitertests und KI-Rechenzentrumsimplementierungen zu erfüllen. Testen Sie Kommunikation mit hoher Dichte, charakterisieren Sie die Designleistung und testen Sie Geräte bis an ihre Grenzen.

Verschaffen Sie sich einen klaren und genauen Überblick über den PCIe® Link-Verkehr

Führen Sie tiefgreifende Protokollanalysen an PCIe®-Systemen mit unvergleichlicher Signalintegrität durch. Der PCIe Protocol Analyzer von Keysight emuliert und visualisiert den Datenverkehr und zeigt Probleme auf, um Hosts und Endpunkte für die Bereitschaft von AI-Rechenzentren zu validieren - alles in einem steckbaren, kabellosen Formfaktor für eine schnelle Kalibrierung.

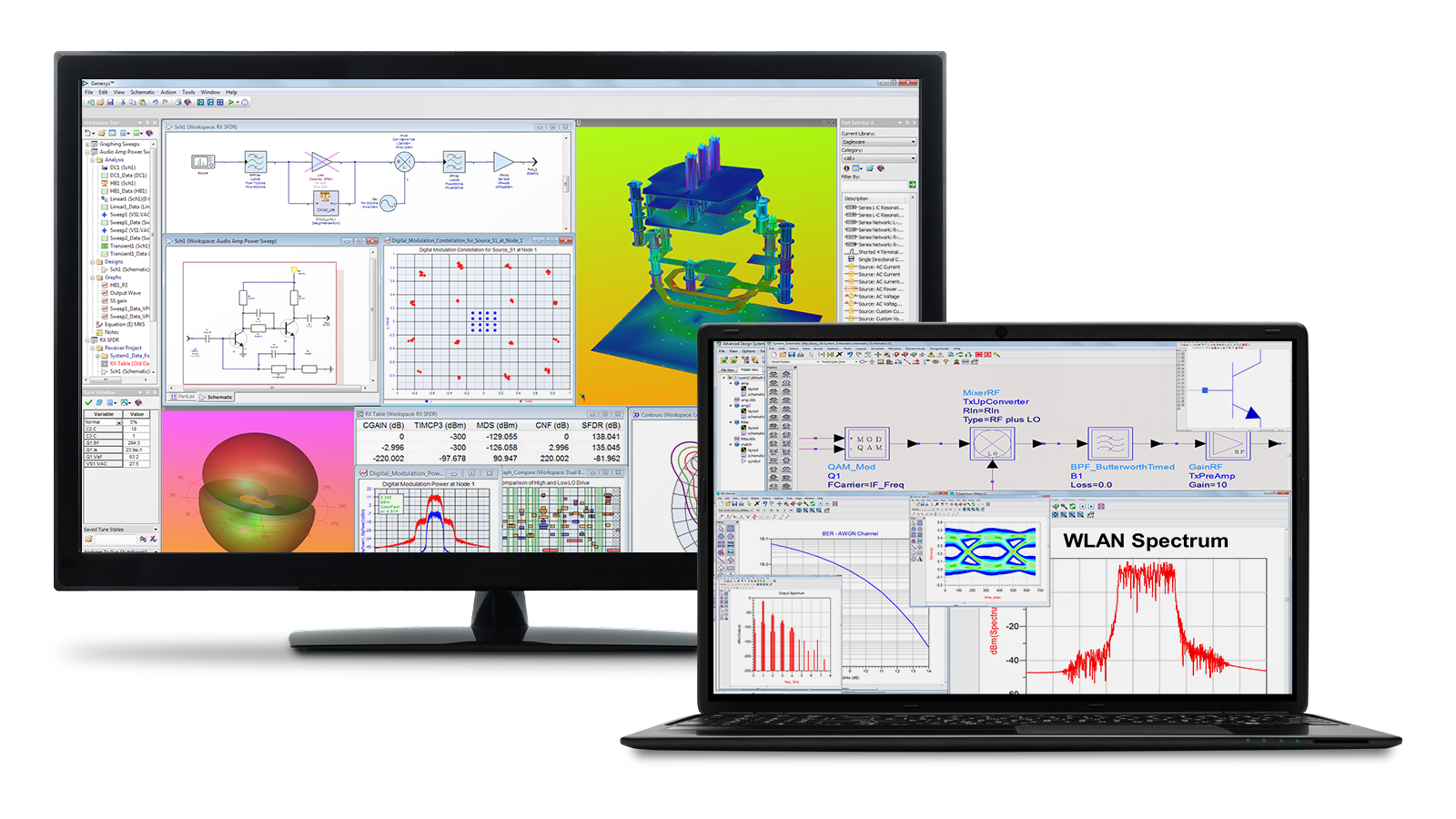

Rationalisierung von Design-Workflows mit EDA-Produkten

Vereinfachen Sie mit den EDA-Produkten (Electronic Design Automation) von Keysight den Einblick in mehrere Domänen während des gesamten Designzyklus. Prognostizieren Sie Designherausforderungen, simulieren Sie KI-Chips und Halbleitermodelle und liefern Sie mit Designvorlagen, Komponentenbibliotheken, robuster Modellierung und präzisen Simulationen Produkte, die sofort auf den Markt kommen.

Der Weg zu PCIe® 7

Sind Sie bereit, die Zukunft der Datenübertragung zu nutzen? PCIe® 7 und CXL bieten schnellere Datenraten für Hochleistungsanwendungen wie KI und maschinelles Lernen. Neue Technologien wie die PAM4-Signalübertragung mit 32 GBaud sind ein bedeutender Sprung im Vergleich zu älteren NRZ-basierten Technologien und erfordern strenge Toleranzen, sich entwickelnde Spezifikationen und neue Komponentenmodelle.

In diesem Webinar erfahren Sie mehr über die Herausforderungen bei der Entwicklung dieser Standards und lernen simulationsgestützte Konformitätslösungen kennen, die MOI-Workflows (Method of Implementation) zur Zertifizierung von Konformitätstests verwenden.

Anwendungsfälle für KI-gestütztes Testen und die Validierung von Leiterplatten

Analysieren der PCB-Signalintegrität

Reduzieren Sie die Risiken für die Signalintegrität in einer digitalen Hochgeschwindigkeitsleiterplatte durch die Erkennung und Diagnose von Übersprechen, Jitter, vertikalem Rauschen und Phasenrauschen.

PCle® 6.0 Protokoll-Validierung durchführen

Protokollvalidierung auf der physikalischen, der Datenverbindungs- und der Transaktionsschicht.

Test der DDR5-Transmitter-Konformität

Durchführung einer breiten Palette von Konformitätstests auf der Grundlage von JEDEC-Normen.

Prüfung der Konformität von PCIe® 6.0-Empfängern

Kalibrieren Sie Stresssignale und testen Sie die Konformität des PCIe®-Empfängers.

Erfahren Sie mehr über AI Compute

Häufig gestellte Fragen: AI Compute

Da Rechenzentren skaliert werden, um das exponentielle Datenverkehrswachstum zu bewältigen, erfordert die von ihnen benötigte KI-Recheninfrastruktur – einschließlich CPUs, GPUs, Beschleunigern und Speicherschnittstellen – strengere Tests. Die Validierung muss sich nun auf ultraschnelle digitale Schnittstellen wie PCIe, CXL, DDR und HBM beziehen, die für die Leistung moderner Rechenzentren grundlegend sind. Die Halbleiterprüfung entwickelt sich mit fortschrittlichen Tools wie den Echtzeit-Compliance-Oszilloskopen , Protokollanalysatoren und BERTs von Keysight weiter, um die Integrität und Compliance der physischen Schicht unter den Belastungsbedingungen eines Rechenzentrums zu validieren. Bei den Tests stehen nun Signalintegrität, Leistung, Energieeffizienz und Zuverlässigkeit bei dichten Server- und benutzerdefinierten Siliziumbereitstellungen im Vordergrund.

Moderne Rechenzentren basieren auf komplexen Chipsätzen mit engen Zeitspielräumen und enormen Durchsatzanforderungen. Advanced Halbleitertestwerkzeuge – wie die AWGs , Hochleistungsoszilloskope und Empfängertestsoftware von Keysight – ermöglichen eine präzise Signalgenerierung und -analyse, um zuverlässige Hochgeschwindigkeitsfunktionen sicherzustellen. Diese Werkzeuge helfen, Jitter, Signalverschlechterungen und Signalqualitätsprobleme in Speicher- und I/O-Subsystemen zu erkennen. Für Hyperscaler, die kundenspezifische Chips für Workloads wie KI-Computing, Speicher, Netzwerk und Virtualisierung entwickeln, beschleunigen diese Testlösungen die Qualifizierung und reduzieren Systemprobleme nach der Inbetriebnahme. Letztendlich bedeutet eine verbesserte Validierung weniger Ausfälle im Feld und eine höhere Verfügbarkeit von Rechenzentrumsdiensten.

Die Chipentwicklung in Rechenzentren erfordert schnelle Zyklen und hohen Durchsatz. Die Reduzierung von Testzeit und -kosten hängt von einer intelligenten Testabdeckung, dem effizienten Einsatz automatisierter Geräte und einer robusten Simulation in der frühen Entwicklungsphase ab. Die EDA-Pakete von Keysight – einschließlich Tools wie SIPro (Signalintegritätsanalyse) und System Design – ermöglichen Ingenieuren die Simulation und Validierung von Hochgeschwindigkeitskanälen vor dem Tape-Out. Im Labor optimieren Instrumente wie BERTs und Echtzeit-Compliance-Oszilloskope die Compliance und das Debugging für PCIe-/CXL- und Speicherschnittstellen. Dies reduziert kostspielige Nacharbeiten und beschleunigt die Bereitstellung.

Die Validierung von Rechensystemen in Rechenzentren erfordert eine Kombination aus Messungen der physikalischen Schicht, Daten zur Protokollkonformität und Daten zur Umgebungsbelastung. Testingenieure erfassen Echtzeit-Leistungsmesswerte wie Bitfehlerraten, Augendiagramme, TDECQ, Jitter-Toleranz und Lane-Margining von Geräten wie BERTs , Oszilloskopen und AWGs . Zusätzlich werden Simulationsdaten von Tools wie Keysights PHY Designer oder RF Circuit Simulation Professional verwendet, um das Verhalten unter Worst-Case-Bedingungen zu überprüfen. Diese Daten sind entscheidend, um sicherzustellen, dass Serverchips, Speichermodule und Verbindungen im großen Maßstab und unter den anspruchsvollen Arbeitslasten, die für Hyperscale-Umgebungen typisch sind, zuverlässig funktionieren.

Da KI-Rechendesigns in Rechenzentren die Bandbreitengrenzen überschreiten und die Leistungsreserven schrumpfen, stehen Ingenieure vor Herausforderungen hinsichtlich Signalintegrität, Protokollkonformität und thermischer Stabilität. Das Testen von Chiplets, gestapelten Speichern und benutzerdefinierten I/O-Pfaden – oft über mehrere Spannungsbereiche hinweg – erfordert präzise Werkzeuge und umfassende Protokolltransparenz. Die Integration der Hochgeschwindigkeitsvalidierung in Arbeitsabläufe ohne Beeinträchtigung der Ausbeute oder der Markteinführungszeit ist ebenfalls schwierig. Tools wie Keysights Design Data und IP Data Management helfen bei der Verfolgung der Testabdeckung, während Protokollanalysatoren und fortschrittliche Simulationssuiten Überraschungen in der Spätphase reduzieren. Die Sicherstellung der Skalierbarkeit von Testaufbauten über sich entwickelnde Verbindungsstandards wie PCIe 6.0 und CXL 3.0 ist ein ständiges Anliegen.

Zu den wichtigsten Trends zählen der Aufstieg von zusammensetzbaren und disaggregierten Architekturen, die Einführung chipletbasierter Designs und kundenspezifischer Siliziumchips zur Leistungsoptimierung. Best Practices zum Testen von KI-Berechnungen in Rechenzentren umfassen den Einstieg in die Simulation (mit EDA-Tools wie SIPro ), die Nutzung automatisierter Compliance-Tests auf Echtzeit-Oszilloskopen und BERTs sowie die Korrelation von Ergebnissen auf Laborebene mit der Leistung auf Systemebene. Hyperscaler holen Tests zunehmend ins eigene Haus, um mehr Kontrolle und schnellere Iterationen zu ermöglichen. Sie nutzen integrierte Validierungsplattformen, die physische, Protokoll- und Datenmanagementebenen kombinieren, um schnellere und zuverlässigere KI-Berechnungen im großen Maßstab zu ermöglichen.

Sie brauchen Hilfe oder haben Fragen?