Che cosa sta cercando?

Calcolo dell'intelligenza artificiale

Test di chip AI e progetti digitali ad alta velocità.

Accelerare i test dei semiconduttori AI e la progettazione HSD

Sbloccate il futuro dei semiconduttori AI-ready e dei progetti digitali ad alta velocità (HSD). Progettate e testate i chip AI, risolvete i problemi dei progetti all'avanguardia e soddisfate o superate i più recenti standard PCIe, DDR e CXL con strumenti avanzati di progettazione, debug e conformità, ottimizzati per i data center AI.

Elevate le vostre conoscenze in materia di calcolo dell'intelligenza artificiale

5 strategie per ottimizzare e scalare i data center AI

L'intelligenza artificiale sta trasformando i settori e guidando l'innovazione. Ciò significa che gli architetti di rete devono gestire le crescenti esigenze dei data center, tra cui modelli di traffico unici, carichi di lavoro dinamici e pressioni incessanti sulle prestazioni.

Leggete questo eBook per scoprire cinque soluzioni pratiche per ottimizzare le prestazioni dei data center AI per le applicazioni moderne.

Accelerare l'innovazione dell'intelligenza artificiale con l'ingegneria di progettazione concorrente

La progettazione di chip AI sta diventando sempre più difficile a causa di ostacoli tecnici ed economici come la complessità, il costo e il consumo di energia. Leggete questo eBook per scoprire come accelerare lo sviluppo di chip AI attraverso la progettazione di chiplet, la ricerca 6G, la fornitura di energia e la gestione del ciclo di vita dell'ingegneria.

L'evoluzione degli standard PCIe® e dei requisiti di test

I data center devono far fronte a una crescente richiesta di velocità e l'intelligenza artificiale sta accelerando la domanda. Mentre la velocità di Ethernet supera gli 800GE, PCIe® 6.0, l'ultima iterazione dello standard Peripheral Component Interconnect Express® (PCIe®), sta accelerando l'innovazione dei data center.

Progettazione digitale e standard di interconnessione

Quando i segnali digitali raggiungono velocità gigabit, "l'imprevedibile" diventa normale. E quando si tratta di standard digitali, ogni nuova generazione e progresso tecnologico pone nuovi ostacoli sul vostro cammino. Esplorate gli strumenti di simulazione, misurazione e conformità per superare le sfide dei progetti digitali gigabit.

Progettare e testare chip e semiconduttori AI

Accelerare i cicli di progettazione, anticipare le sfide di conformità, ottimizzare le prestazioni elettroniche e fornire più rapidamente innovazioni leader di mercato.

Risoluzione dei problemi dei progetti digitali ad alta velocità ottimizzati per l'AI

Riducete i giri di progettazione, testate i semiconduttori AI e analizzate le prestazioni dei circuiti stampati (PCB) con strumenti precisi e ad alte prestazioni.

Soddisfare o superare i più recenti standard di rete AI

Semplificate e accelerate i test di conformità con soluzioni di test automatizzate per i principali standard dei data center AI, tra cui PCIe®, CXL e DDR.

Test dei chip AI e debug dei progetti HSD con Keysight

Debug di progetti pronti per l'AI con un'integrità del segnale senza pari

Riducete i cicli di prototipazione, accelerate il time to market e migliorate l'affidabilità dell'infrastruttura dei data center con gli oscilloscopi Keysight serie UXR B. Risolvete i problemi delle prestazioni del livello fisico con le misure di integrità del segnale più elevate per costruire dispositivi ad alta velocità per i data center AI di domani.

Garantire la conformità agli standard di calcolo AI di nuova generazione

Caratterizzate i ricevitori e le interfacce server per le reti di data center AI con i tester Bit Error Ratio (BERT) di Keysight. Migliorano il pathfinding per applicazioni 1.6T e all'avanguardia con integrità del segnale senza compromessi, supporto NRZ / PAM4 / PAM6 / PAM8 e velocità di trasmissione dati fino a 120 Gbaud.

Accelerazione dello sviluppo di progetti a 160 Gbaud e oltre

I generatori di forme d'onda arbitrarie (AWG) di Keysight offrono la velocità, l'ampiezza di banda e la precisione necessarie per soddisfare le esigenze dei test sui semiconduttori e delle implementazioni dei data center AI. Testano comunicazioni ad alta densità, caratterizzano le prestazioni dei progetti e stressano i dispositivi fino ai loro limiti.

Ottenere una visione chiara e precisa del traffico dei collegamenti PCIe

Eseguite analisi approfondite dei protocolli sui sistemi PCIe® con un'integrità del segnale senza precedenti. L'analizzatore di protocollo PCIe di Keysight emula e visualizza il traffico di dati, individuando i problemi per convalidare gli host e gli endpoint per la preparazione dei data center AI, il tutto in un fattore di forma collegabile e senza cavi per una rapida calibrazione.

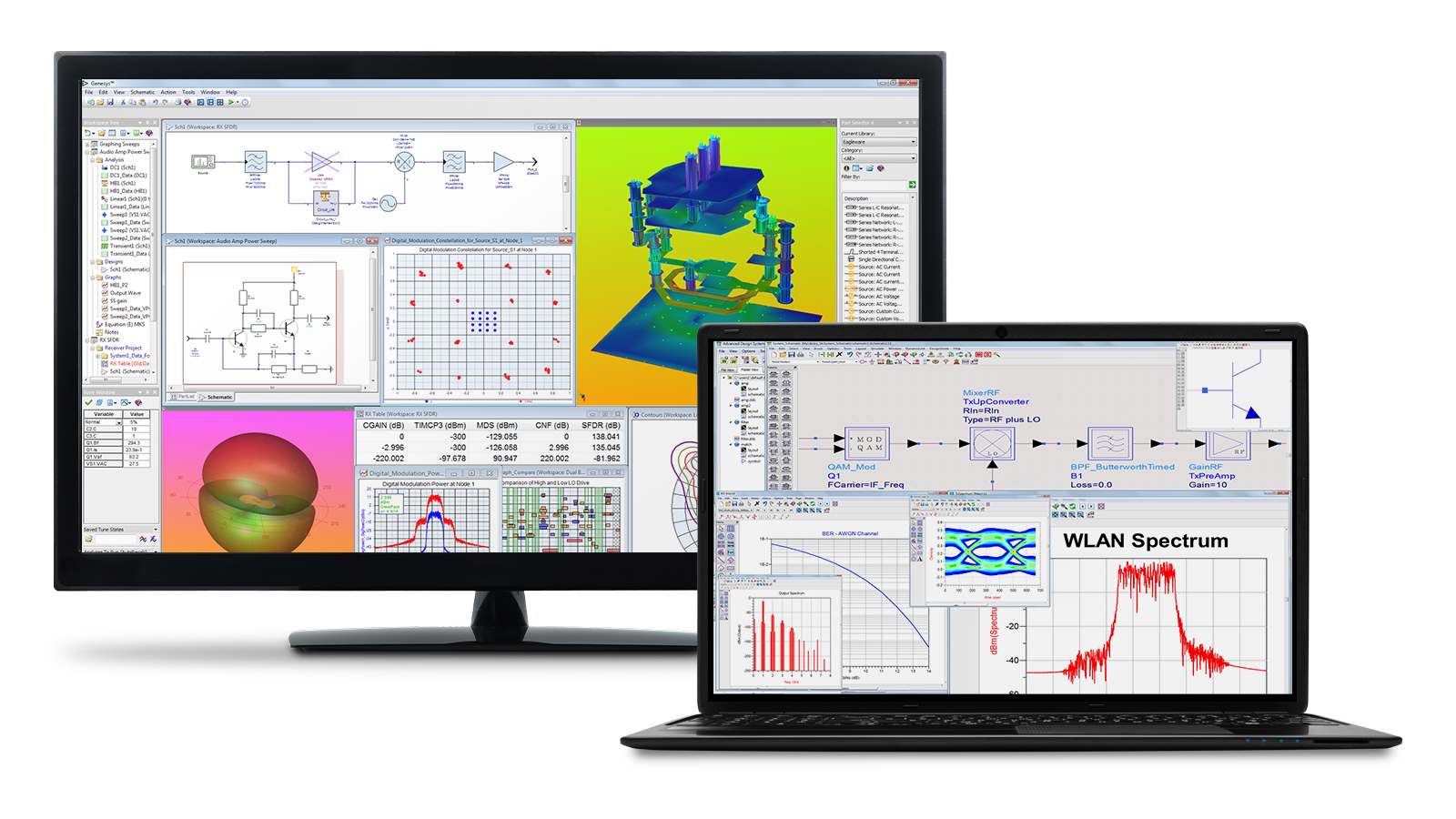

Semplificare i flussi di lavoro di progettazione con i prodotti EDA

Semplificate gli approfondimenti multidominio durante l'intero ciclo di progettazione con i prodotti di automazione della progettazione elettronica (EDA) di Keysight. Prevedete le sfide di progettazione, simulate chip AI e modelli di semiconduttori e fornite prodotti first-to-market con modelli di progettazione, librerie di componenti, modellazione robusta e simulazioni precise.

La strada verso PCIe® 7

Siete pronti ad abbracciare il futuro del trasferimento dati? PCIe® 7 e CXL offrono velocità di trasferimento dati più elevate per applicazioni ad alte prestazioni, come l'intelligenza artificiale e l'apprendimento automatico. Le nuove tecnologie, come la segnalazione PAM4 a 32 Gbaud, rappresentano un salto significativo rispetto alle vecchie tecnologie basate su NRZ e richiedono tolleranze rigorose, specifiche in evoluzione e nuovi modelli di componenti.

In questo webinar, imparerete a conoscere le sfide della progettazione per questi standard ed esplorerete le soluzioni di conformità basate sulla simulazione, utilizzando i flussi di lavoro Method of Implementation (MOI) per certificare i test di conformità.

Casi d'uso per i test di calcolo dell'intelligenza artificiale e la convalida dei PCB

Analizzare l'integrità del segnale dei PCB

Riducete i rischi di integrità del segnale in un circuito stampato digitale ad alta velocità attraverso il rilevamento e la diagnosi di diafonia, jitter, rumore verticale e rumore di fase.

Eseguire la convalida del protocollo PCle® 6.0

Ottenere la convalida del protocollo a livello fisico, di collegamento dati e di transazione.

Test di conformità del trasmettitore DDR5

Esecuzione di un'ampia gamma di test di conformità basati sugli standard JEDEC.

Verifica della conformità del ricevitore PCIe® 6.0

Calibrate i segnali di stress e verificate la conformità del ricevitore PCIe®.

Per saperne di più sull'AI Compute

Domande frequenti: Calcolo dell'intelligenza artificiale

Man mano che i data center scalano per supportare una crescita esponenziale del traffico, l'infrastruttura di calcolo dell'intelligenza artificiale su cui si basano, comprese CPU, GPU, acceleratori e interfacce di memoria, richiede test più rigorosi. La convalida deve ora riguardare le interfacce digitali ad altissima velocità come PCIe, CXL, DDR e HBM, che sono fondamentali per le prestazioni dei moderni data center. I test sui semiconduttori si stanno evolvendo con strumenti avanzati come gli oscilloscopi di conformità in tempo reale, gli analizzatori di protocollo e i BERT di Keysight per convalidare l'integrità e la conformità del livello fisico in condizioni di stress a livello di data center. I test hanno ora come priorità l'integrità del segnale, le prestazioni, l'efficienza energetica e l'affidabilità dei server densi e delle implementazioni di silicio personalizzate.

I moderni data center si basano su chipset complessi con margini temporali ristretti e requisiti di throughput elevati. Gli strumenti Advanced per il collaudo Advanced — come gli AWG, gli oscilloscopi ad alte prestazioni e il software di collaudo dei ricevitori di Keysight — garantiscono una generazione e un'analisi precise dei segnali per assicurare prestazioni affidabili ad alta velocità. Questi strumenti aiutano a rilevare il jitter, il degrado del segnale e la qualità del segnale nei sottosistemi di memoria e I/O. Per gli hyperscaler che realizzano chip personalizzati per carichi di lavoro quali elaborazione AI, archiviazione, networking e virtualizzazione, queste soluzioni di test accelerano la qualificazione e riducono i problemi a livello di sistema dopo l’implementazione. In definitiva, una validazione migliorata comporta un minor numero di guasti sul campo e un tempo di attività ottimizzato per i servizi dei data center.

Lo sviluppo di chip per data center richiede cicli rapidi e volumi elevati. La riduzione dei tempi e dei costi di test dipende da una copertura di test intelligente, dall'uso efficiente di apparecchiature automatizzate e da una simulazione robusta già nella fase di progettazione. I pacchetti EDA di Keysight, che comprendono strumenti come SIPro (analisi dell'integrità del segnale) e System Design, consentono agli ingegneri di simulare e convalidare i canali ad alta velocità prima del tape-out. Sul banco di prova, strumenti come i BERT e gli oscilloscopi di conformità in tempo reale semplificano la conformità e il debug delle interfacce PCIe/CXL e di memoria, riducendo le costose rielaborazioni e accelerando il time-to-deployment.

La convalida dei sistemi di calcolo dei data center richiede un mix di misure di livello fisico, dati di conformità del protocollo e dati di stress ambientale. Gli ingegneri addetti ai test raccolgono metriche sulle prestazioni in tempo reale, come tassi di errore di bit, diagrammi a occhio, TDECQ, tolleranza al jitter e marginazione di corsia da apparecchiature come BERT, oscilloscopi e AWG. Inoltre, i dati di simulazione provenienti da strumenti come PHY Designer o RF Circuit Simulation Professional di Keysight vengono utilizzati per verificare il comportamento nelle condizioni peggiori. Questi dati sono fondamentali per garantire che i chip dei server, i moduli di memoria e le interconnessioni funzionino in modo affidabile su scala e con i carichi di lavoro impegnativi tipici degli ambienti hyperscale.

Mentre i progetti di calcolo AI dei data center spingono i limiti di larghezza di banda e riducono i margini di potenza, gli ingegneri devono affrontare sfide di integrità del segnale, conformità del protocollo e stabilità termica. La verifica di chiplet, memorie impilate e percorsi di I/O personalizzati, spesso su più domini di tensione, richiede strumenti precisi e una profonda visibilità dei protocolli. È difficile anche integrare la convalida ad alta velocità nei flussi di lavoro senza interrompere la resa o il time-to-market. Strumenti come Design Data e IP Data Management di Keysight aiutano a monitorare la copertura dei test, mentre gli analizzatori di protocollo e le suite di simulazione avanzate riducono le sorprese dell'ultima fase. Garantire la scalabilità delle configurazioni di test per gli standard di interconnessione in evoluzione, come PCIe 6.0 e CXL 3.0, è un problema costante.

Le tendenze principali includono l'aumento delle architetture componibili e disaggregate, l'adozione di progetti basati su chiplet e il silicio personalizzato per l'ottimizzazione della potenza. Le migliori pratiche per testare l'AI compute dei data center includono l'inizio della simulazione (utilizzando strumenti EDA come SIPro), l'utilizzo dell'automazione dei test di conformità su oscilloscopi e BERT in tempo reale e la correlazione dei risultati a livello di bench con le prestazioni a livello di sistema. Gli iperscaler stanno sempre più portando i test all'interno dell'azienda per ottenere un maggiore controllo e un'iterazione più rapida, utilizzando piattaforme di convalida integrate che combinano livelli fisici, di protocollo e di gestione dei dati per offrire un calcolo AI più veloce e affidabile su scala.

Volete aiuto o avete domande?