詳細はこちら

segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communicationssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs,segmentation:business-unit/CSG,segmentation:funnel/bofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications

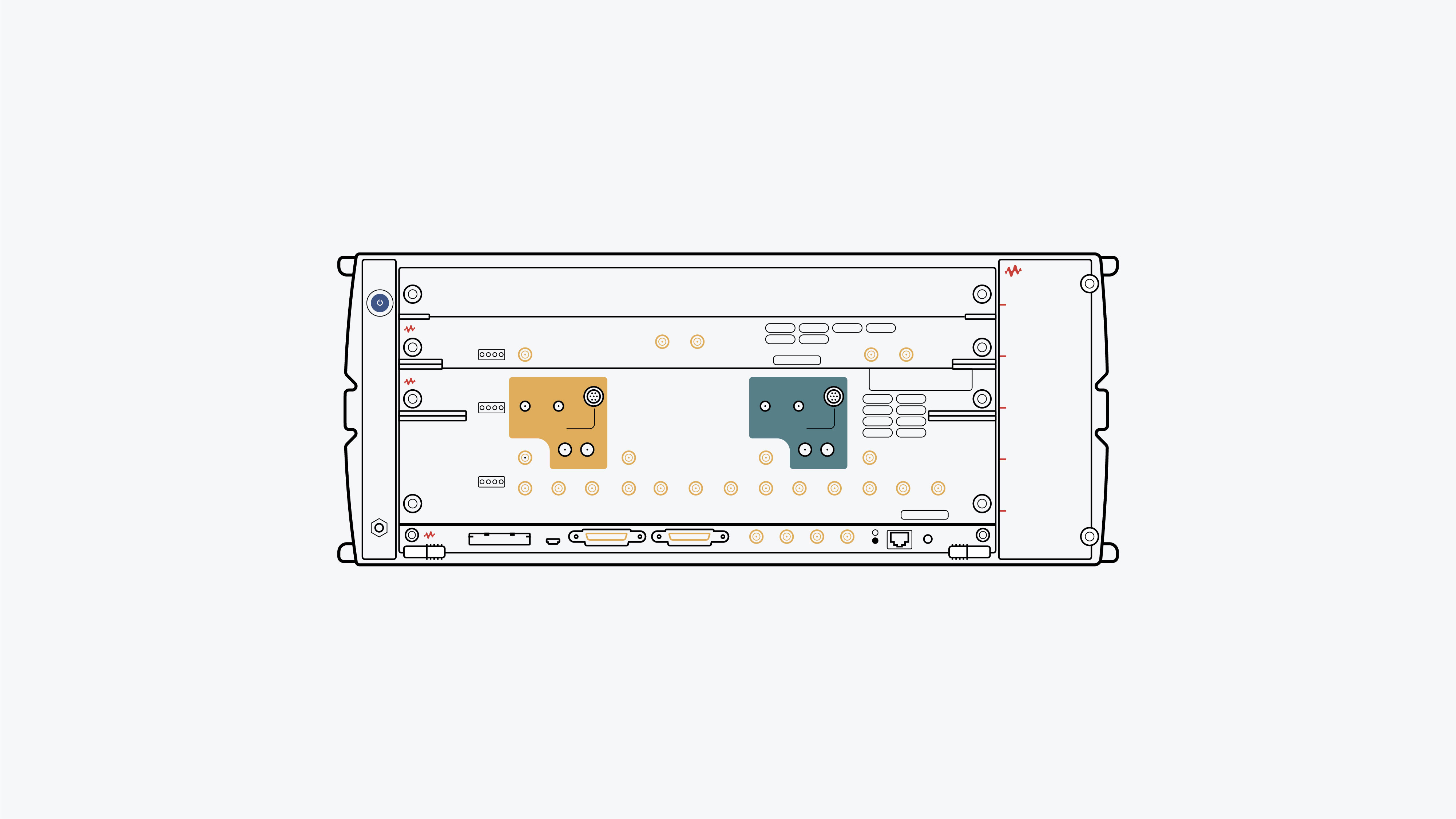

LPDDR6レシーバーのコンプライアンス試験方法

LPDDR6レシーバーのコンプライアンス試験において、BER(ビット誤り率)に基づくストレステストが、AIメモリシステムの感度、タイミングマージン、および信頼性を検証するためにどのように活用されているかをご紹介します。

詳細はこちら

.png)