何をお探しですか?

ADS 2017製品リリース

Highlights

ADS 2017は、高度な無線通信デザイン向けに以下のような3次元ソリューションとその他の機能を提供します:

- 3次元レイアウトの表示/ルーティング/編集

- マルチテクノロジー3次元電気-熱シミュレーション

- Pythonデータリンクによる3次元データのビジュアリゼーション

- FEMによる非常に高度な3次元電磁界シミュレーション

- 3次元ビアデザイナー:正確なビアモデルを使用可能

- コイルなどのPCell作成の自動化

- 新しいConfig Viewによる階層管理

- Inter Operability機能の向上

- SOA(Safe Operating Area)のサポートによる信頼性の向上

- シミュレーション性能の向上

ADS 2017は、シグナルインテグリティー(SI)/パワーインテグリティー(PI)のための新しい機能を提供します:

- PIPro – 電源分配回路(PDN)用のDC電気-熱シミュレーション

- PIPro - デカップリングキャパシタおよびインダクターの部品表オプティマイザー

- 3次元ビアデザイナー:正確なパラメータ化差動ビアモデルへのアクセスが可能

- IBISモデルのユーザビリティーの向上と新しいIBISパッケージ・モデル・コンポーネント

- バッチシミュレーションおよびポート数の多いSパラメータの使用のために、トランジェント/チャネルシミュレーションが大幅に向上

- 統計チャネルシミュレーションがアップデートされ、PAM4 IBIS-AMIモデルをサポート

- 表形式ビューでのサブストレート編集

以下のリンクをクリックして、ご覧ください:

ADS 2017 Update 1.0がダウンロード可能です (ADS Updateのリリースに関する重要な情報をご参照ください)。

上の[トライアル&ライセンス]タブをクリックしてから、[詳細&ダウンロード]ボタンをクリックしてソフトウェアをダウンロードしてください。

Description

Advanced Design System (ADS) 2017の新しいリリースでは、業界最先端のRF/マイクロ波回路シミュレーション・ソフトウェア・プラットフォームの変更によって、顧客体感(3次元ビュワー、クイック・スタート・ガイド、Pythonデータリンク)と性能(回路/FEMシミュレーション速度、複雑なレイアウトの処理、マルチテクノロジーのサポート)が向上しています。これをさらに多くの新機能と組み合わせて使用することにより、RFフロントモジュールとRFICシリコンの両方のデザインに携わるユーザーの日常的な作業が容易に実行できるようになります。

Advanced Design System (ADS) 2017の新しいリリースでは、業界最先端のRF/マイクロ波回路シミュレーション・ソフトウェア・プラットフォームの変更によって、顧客体感(3次元ビュワー、クイック・スタート・ガイド、Pythonデータリンク)と性能(回路/FEMシミュレーション速度、複雑なレイアウトの処理、マルチテクノロジーのサポート)が向上しています。これをさらに多くの新機能と組み合わせて使用することにより、RFフロントモジュールとRFICシリコンの両方のデザインに携わるユーザーの日常的な作業が容易に実行できるようになります。

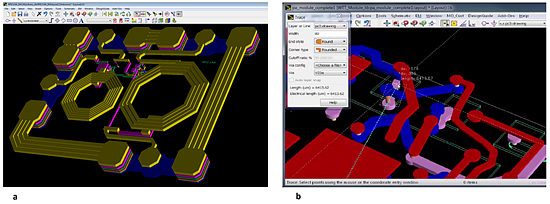

3次元レイアウトの表示/ルーティング/編集

今日の無線通信デザインは複雑さが増しているため、より優れたレイアウトの表示/編集向けのソリューションが求められています。ADS 2017の新しい3次元機能は複雑さが増しても対応が可能です。3次元の各種機能により、PCBまたはMMIC/RFICレイアウトを3次元で表示/編集できるようになります。これによってデザイナーは、デザインが要件に適合することを検証できるだけでなく、気づき難い間違いを検出することができます。ADS 2017の新しい3次元機能によって、電磁界シミュレーションのセットアップに必要な、マルチレイヤーデザインのビアによるスティッチング、高密度領域のルーティング、複雑な構造の選択も大幅に簡素化されます。

図1. ADS 2017で新たに使用できる編集可能な3次元表示。a)LNAのRFICレイアウト、b)PAモジュールのPCB

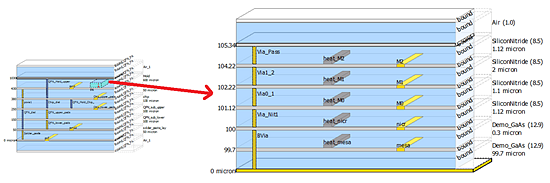

マルチテクノロジー3次元電気-熱シミュレーション

高密度のレイアウトが必要な最新のパワーアンプ(PA)モジュールのデザインや、高度な半導体プロセス(GaN、GaAsなど)の利用は、手間のかかる作業になる場合があります。コストのかかる回路修正を避けるために、デザイナーはテープアウトの前に回路の温度性能を詳細に調査する必要があります。

ADSは回路と熱の練成解析を既に提供しています。設計者はADSのレイアウト/回路設計環境と緊密に統合されたフル3D熱解析ソルバーを利用できます。ソルバーによってシステム全体やチップの温度プロファイルが計算され、そのデータが回路シミュレータにアノテートされ、温度確度の高い回路解析が可能になります。ADS 2017ではマルチテクノロジーを組み合わせて熱シミュレーションを行なうことにより、これらの機能をさらに一歩進んだものにしています。

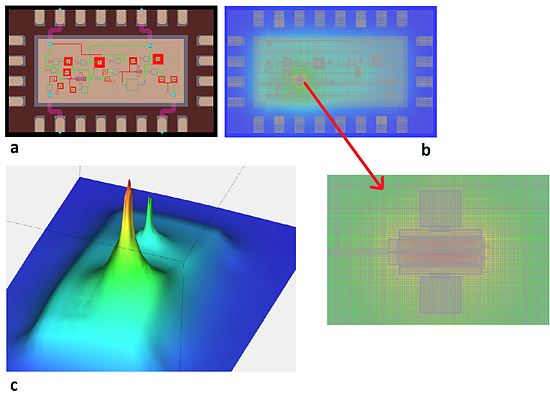

例えば、Quad Flat No-Leads(QFN)パッケージにフリップチップ実装/封止されたPAのデザインについて考えてみましょう。デザインには、ダイ、ラミネート、銅パンプ、パッケージが含まれ、大幅に変動する熱抵抗が発生します。これは、通常、解析が非常に難しいものです。図2はADS2017におけるマルチテクノロジーのサブストレートセットアップをまとめたものです。図3は、3次元チップ全体の機能ブロックの熱効果を優れた分解能/確度で示しています。熱解析にはすべてのデザインの構造が含まれています。この情報を使用してデザイナーは必要な編集を行ってから、高い信頼性でテープアウトできます。

図2. このフリップチップ実装パッケージのパワーアンプ用のサブストレートセットアップの場合、PAダイの拡大表示を含むすべての機能ブロックがADS 2017では表示が可能です。

図2. このフリップチップ実装パッケージのパワーアンプ用のサブストレートセットアップの場合、PAダイの拡大表示を含むすべての機能ブロックがADS 2017では表示が可能です。

図3. ADS 2017ではマルチテクノロジーの電気-熱シミュレーションを実行できます。上の図は、a)QFNパッケージを用いたレイアウト、b)ダイ、ラミネート、銅パンプ、QFNパッケージを含む3次元構造の2次元温度プロファイル、c)チップ全体の3次元温度プロファイルです。

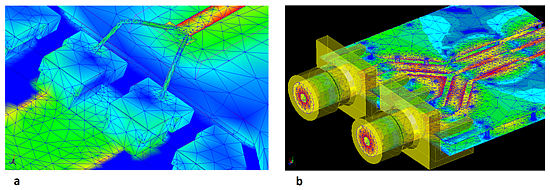

強力な3次元電磁界シミュレーション

ADSの3次元有限要素法(FEM)エンジンは高度なフルウェーブ電磁界シミュレータで、これを使用して3次元電磁界効果を周波数ドメインで解析できます。特に、高速/RFICパッケージ、ボンドワイヤー、アンテナ、オンチップ/オフチップ・エンベディッド・パッシブエレメント、PCBインターコネクトなどのコンポーネントの3次元電磁界効果をシミュレートするのに有用です。FEMエンジンは、ADSとキーサイトの3次元モデリング/シミュレーション環境であるEMProの両方に完全に統合されています。エンジンとの間のデザインのエクスポート/インポートは自動化されているので時間/費用を節約でき、サードパーティー製の電磁界シミュレータで必要なデザインの手動エクスポート/インポートと比較するとミスを最小化できます。ツール間の転送のみにかかる予測時間は1回のシミュレーション当たり約2時間です。1日に1回のシミュレーションを前提にすると、その積み重ねによって大幅な時間の節約が保証され、これは1年当たり約$50,000のコストに相当します。キーサイトのソリューションはADS/EMProにFEMを統合することにより、そのようなすべてのコストとそれに関するフラストレーションを低減します。

ADS 2017とEMPro 2017のリリースでは、FEMエンジンが今までで最も強力になっています(図5)。高性能なメッシュクリエーター、適応型メッシュ作成アルゴリズム、混合次数関数の使用、周波数ポイントの並列計算によって、ADS 2017のFEMは、従来のものよりも1.5倍~2倍(平均)高速に動作します。さらに、占有されるディスク容量が約50 %も減少しています。このような特長により、FEMエンジンは、新しい困難なデザイン要件に対応するために作業しているRF/マイクロ波デザイナーが使用しやすいものになっています。

図5. 上図はFEMによって作成された次の3次元構造の電磁界波です。a)チップパッケージおよびボンドワイヤー、b)基板インターコネクトを備えたPCB ADS 2017のFEMは、従来のものよりも1.5倍~2倍(平均)高速で、占有されるディスク容量は約50 %も減少しています。

| テストケース | FEM 2017シミュレーション時間 | FEM 2017シミュレーション速度の向上 |

|---|---|---|

| A1 | 0:15:46 | 1.7x |

| A2 | 2:04:05 | 3.8x |

| A3 | 0:00:48 | 1.8x |

| B1 | 1:12:05 | 1.4x |

| B2 | 0:57:19 | 1.8x |

| B3 | 0:32:11 | 3.2x |

| B4 | 0:55:36 | 1.8x |

| C1 | 3:24:53 | 2.6x |

| C2 | 4:51:00 | 1.4x |

| C3 | 0:58:54 | 6.6x |

| D1 | 0:36:07 | 3.8x |

| D2 | 1:46:59 | 6.8x |

| D3 | 0:04:06 | 2.6x |

| D4 | 0:01:58 | 5.8x |

3次元ビアデザイナー:正確なビアモデルを使用可能

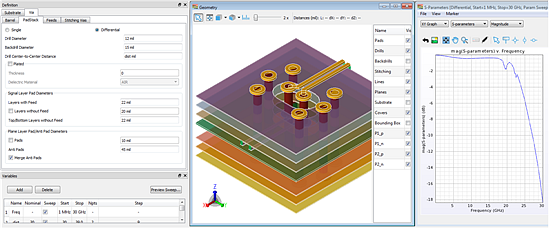

ハイスピード・デジタル・インターコネクトをシミュレートするときの重要な問題は、高周波で正確なビアモデルを使用できないことです。この問題を解決するために、ADS 2017にビアデザイナーが追加されました。PCBビア(シングルエンドまたは差動)を作成/モデリングするためのツールで、これを使用してビアの仕様全体を正しく見積ることが出来ます。(図6)。

ビアデザイナーはFEMを使用して、高周波に於いてもPCBビアの特性を抽出します。パラメータによる掃引もサポートしており、フルチャネルのシミュレーション中に回路を微調整することができます。この高度な新しいツールを使用して、ビアデザインに関する不確かさを評価できます。

図6. ADS 2017に追加されたビアデザイナーは、PCBビアを作成/モデリングするためのツールです。図にはシミュレーション結果とPCBビアの形状が一緒に表示されています。

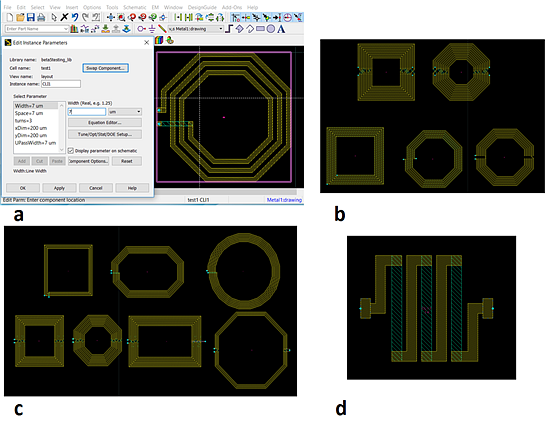

コイルなどのPCell作成の自動化

ADSは有用なオプション機能と、Keysight GoldenGateソフトウェア(RFICシミュレーションの業界標準)の統合により、シリコンRFICのデザインを最初から最後まで実行できる優れたプラットフォームを実現しています。このような機能をさらに補完するために、ADS 2017にはCoilSysが追加されています。これはアドオンユーティリティーで、スパイラルインダクター、変換回路、伝送ラインのパラメータ化セル(PCell)の作成を自動化するものです(図7)。作成されたPCellはデザイン・ルール・チェック(DRC)でクリーンな状態であり、すぐにRFICデザインに使用できます。CoilSysによってこのようなレイアウトセルを手動で作成する必要がなくなります。セルの作成は多くの場合、手間のかかる作業です。

CoilSysによって作成されたレイアウトは電磁界シミュレートしてパラメータ化することができ、これをコンポーネントシンセシスだけでなく、デザインの最適化にも使用することができます。

図7. ADS 2017に追加されたCoilSysは、PCellの作成を自動化するアドオンユーティリティーです。RFICデザイナーで、a)CoilSysを使用して、b)シングルエンドまたは差動のインダクター、c)バラン/変換回路、d)ソレノイドの、DRCクリーンなPCellを作成できます。

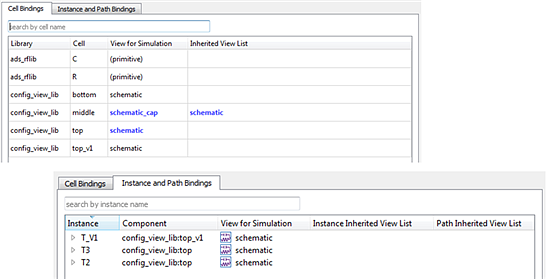

新しいConfig Viewによる階層管理

ADS 2017は、1つのグラフィカル・ユーザー・インタフェースを使用してデザイン階層の作成/変更/制御を行える新しいオプションを提供しています。オプションのConfig Viewは図8のような独自のインタフェースを備えています。ADSの古いバージョンと異なり、Config Viewでは階層管理のためにデザインを変更する必要はありません。

図8. Config Viewを使用したADS 2017内部の階層管理により、デザイン階層の作成/変更/管理が非常に簡単になります。

高度でより包括的なシミュレーションプラットフォーム

無線通信システムデザインが簡単な作業になることはありません。むしろ、今日の急速に変化する業界ではますます困難になっています。ADSが何年も蓄積してきた確固たる基礎と固定ユーザーの評価に基づいて、ADS 2017は、現代のマイクロ波/RFエンジニアが直面する既存/最新の課題に効果的に対応できる新しいオプション/機能を実現しています。非常にわずかな違いでもデザインの成功と失敗が分かれてしまう可能性がある環境で、ADS 2017の高度で包括的な新しい機能が、今日のデザイナーが成功するために必要な最適なツールになります。

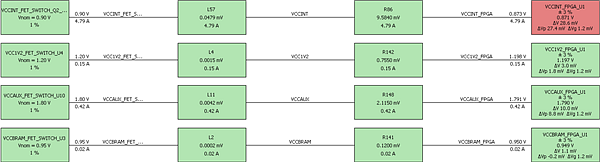

PIProのシグナル・インテグリティー/パワー・インテグリティー・デザインの新機能

図 9. パワーツリーの結果表示

ADS 2017のPIProでは、新しいパワーツリーの概要のプロット、詳細解析レポートの作成、2つのシミュレーション解析結果の差をすばやく表示できる「「~との比較」機能が含まれます。PIProには電気-熱解析用の新しいシミュレーション機能と、電源分配回路のDecap/インダクターの部品表オプティマイザーが追加されています。

DC IRドロップの電気-熱解析

完全自動化された一体型の電気-熱練成シミュレーション

既存のDC IRドロップのシミュレーションセットアップを新しい電気-熱練成シミュレーションに容易にコピー可能

プレーン、ピン、ビアの温度リストの視覚化

熱による部分的な抵抗率の変化を考慮した最も正確なDC IRドロップ結果の表示

冷却ソリューション(ヒートシンクのサイズの増加やエアフローの増加など)のテストに将来対応予定

熱のみのシミュレーションの追加により、断熱材のプランニングを実行できる機能を提供

図10. DC IRドロップの電気-熱解析 - 温度のビジュアリゼーション

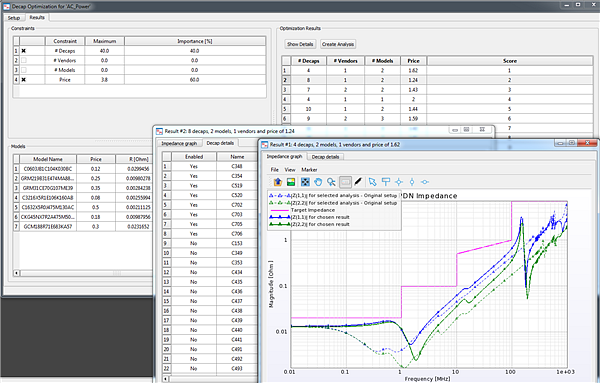

Decap/インダクターの部品表の最適化

多くのICのリファレンスデザインでは、最高の性能と信頼性を実現するためにPDNに配置する必要があるDecapの包括的なリストが提供されています。これには、デザイナーが実際のPCBに適用する特定の制限(サイズやレイヤー数)が考慮されていません。多くの場合、ICの周辺や下には十分なスペースがなく、すべてのDecapを配置することができないので、レイアウトエンジニアは残りのコンポーネントを、PDN上の取り付けられる場所に自由に配置します。PIProのDecapの最適化では、基板上に配置するときにすべてのDecapを使用できるので、必要なターゲット・インピーダンス・プロファイルに適合する最適なソリューションを探索できます。

ユーザーは、以下のような重み付けを指定して、最適なソリューションを定義できます。

- Decapの数

- 独自モデルの数

- ベンダーの数

- コスト

インテリジェントな探索アルゴリズムと、Decapモデルの変更には電磁界ソリューションの再計算が不要という特徴から、最適化は高速に行われます。最適化の結果は、ターゲットインピーダンスに適合する候補ソリューションのリストとして提供され、重み付けされた基準によってランク付けされます。各候補ソリューションに対して、ユーザーはPDNのZインピーダンス対ターゲットインピーダンスを表示して、性能とコスト削減の最適なバランスを迅速に決定することができます。

図 11. Decapの最適化の解析結果

ADSの試用

ADS 2017をご利用ください。 無料試用のお申し込みはこちらです。

他のADS製品のバージョンを表示できます。

*3次元スミスチャートは、Baylis博士をリーダーとする、ベイラー大学のチームによって開拓されました。