Choose a country or area to see content specific to your location

何をお探しですか?

-

-

WirelessPro 3GPP AIシミュレーションプラットフォーム

WirelessProは、比類のない容易さと精度で、5Gネットワーク、5G Advancedテクノロジー、および将来の6Gワイヤレスチャネルのさまざまな側面をモデル化、シミュレーション、および解析することを可能にします。

-

-

-

高度なシグナルアナライザソフトウェアで複雑さを簡素化

キーサイトのVSAソフトウェアで信号解析テストを加速します。75以上の信号規格に対応し、高精度で視覚化、復調、トラブルシューティングを行います。

-

AI強化型パケットブローカーのご紹介

追加のメモリとストレージにより、これらの強化されたNPBは、キーサイトのAIセキュリティおよびパフォーマンス監視ソフトウェアとAIスタックを実行します。

-

-

-

-

-

- ソリューション

-

キーサイト Learnは、ソリューション、ブログ、イベントなど、関心のあるトピックに関する様々なコンテンツを提供しています。

- 購入

-

頻繁にお問い合わせされるサポート関連のお役に立つ情報すばやくアクセス

お持ちの製品をサポートするための追加情報

- 概要

- すべてのモデル

- アクセサリ

- ソフトウェア

- サポート

50GEから800GEまでのイーサネット検証に対応する自動化対応システム

キーサイトのマルチレートテストシステムは、コンパクトでラボに適したフットプリントで、50GEから800GEまでの高性能かつレーン精度の高いイーサネット検証を提供します。パルス振幅変調(PAM4)BER解析、リアルタイムFEC解析、およびレイヤー1から2のトラフィック生成を組み合わせることで、これらのシステムは、再配線や手動でのレーン再マッピングなしに、複数の速度とインターフェースにわたるテストを可能にします。マルチレートプラットフォームは、研究開発および生産テストエンジニアがデバッグを加速し、シリコン、トランシーバー、ケーブル/リタイマーの性能を検証し、オシロスコープベースのコンプライアンススイートと組み合わせることで、標準規格への準拠を含むマルチレーン相互運用性を確保するのに役立ちます。必要なポート数、インターフェース速度、インターフェースタイプに応じてモデルを選択してください。人気のある構成のいずれかについて、今すぐ見積もりをご依頼ください。選択でお困りですか?以下のリソースをご覧ください。

マルチスピードポートの柔軟性

100GEから800GEまでのOSFP800、QSFP-DD、および同軸相互接続インターフェースをサポートし、再構成は不要です。

リアルタイムFEC解析

シンボルエラー密度、バースト許容度、レーンマージンを用いてRS-544 (KP4) FEC性能を監視し、弱いリンクやリタイマーの問題を迅速に特定します。

強化されたBERTデバッグ

物理的なFECハードウェアなしで、FEC対応のビットエラー分布を使用して、正確なエラー可視化とレシーバーおよびケーブルデバッグの高速化を実現します。

ラボ用計測器の統合

キーサイトのベンチトップ オシロスコープと統合することで、PAM4アイ、ジッタ解析、および共通トリガを介した同期コンプライアンス試験を実現します。

-

Ports

2 ~ 4

-

Interface speed modes

800G, 400G

-

インタフェース

QSFP-DD, OSFP800

-

Protocol support

Ethernet

人気の構成

A400GE-QDD 4ポート レイヤ1 BERT QSFP-DD テストシステム

A400GE-QDD 4ポート レイヤ1 BERT QSFP-DD テストシステム

941-0081

キーサイトA400GE-QDD 4ポート、400GE/200GE/100GE/50GE レイヤ1 BERT QSFP-QDDテストシステムには、最新バージョンのキーサイトKiOSソフトウェアを搭載した固定シャーシが含まれています。

- KiOSで問題を迅速に特定します。このアプリケーションは、すべてのレーンにわたるビットエラーレートテスト (BERT) および前方誤り訂正 (FEC) 統計のシステム全体ビューを提供します。1 x 400GE、2 x 200GE、4 x 100GE、および8 x 50GEの速度をサポートします。

- BERおよびFEC性能を数時間ではなく数分で測定します。拡張BERTオプションを使用して、すべてのイーサネット速度で新しい光トランシーバーと銅ケーブル・インターコネクトを同時に評価します。

- キーサイトのKP4 FECシンボルビットエラー分布解析を使用して、合否判定テストレポートを簡単に生成し、長時間 (時間指定) およびストレステストを実施することで、時間経過に伴うバーストエラーや熱エラーを検出できます。

- オプションのホストおよびモジュール・コンプライアンス・ボード、ケーブル、およびアダプタバンドルを使用して、A400GE-QDDとキーサイトM8040A BERTアナライザ、および開発ボードとの接続を簡素化します。

- 2世代にわたる400GE QSFP-DDテストシステムに基づいて構築された、実績のあるテクノロジーを活用します。

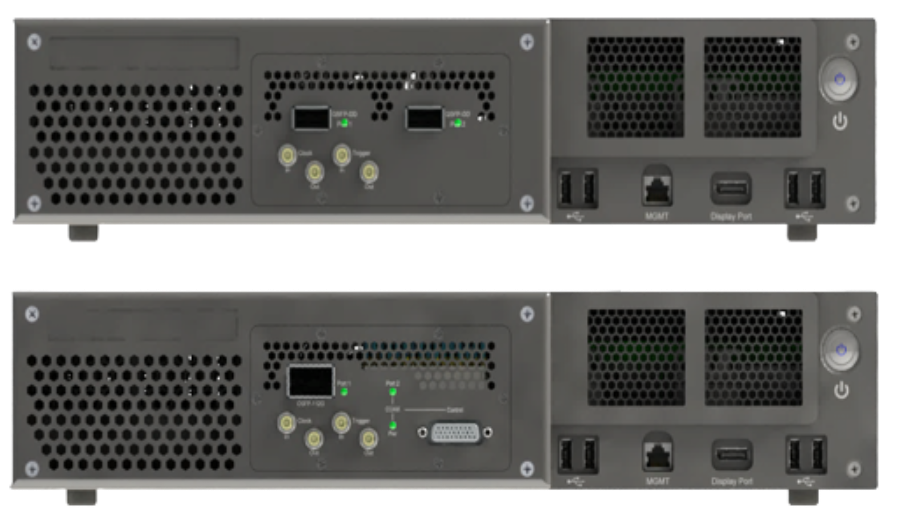

G800GE-02 2ポート OSFPテストシステム

G800GE-02 2ポート OSFPテストシステム

941-0086

キーサイト G800GE-02システムは、高度なエラー検出と訂正、包括的なレイヤー1およびレイヤー2テスト、そして合理化されたテスト管理のための直感的なインターフェースにより、信頼性の高い高速ネットワークパフォーマンスを保証します。

エンジニアは、ブラウザベースのシングルページアプリケーション (SPA) を使用して、問題を迅速に特定し、解決できます。直感的なインターフェースは、すべてのレーンまたはポートにわたるビットエラーレートテスター (BERT)、前方誤り訂正 (FEC)、およびパケット統計の包括的なシステムビューを提供します。

このソリューションは、1 x 800 (800GE)、2 x 400 (400GE)、4 x 200 (200GE)、8 x 100 (100GE)、クロック付き8 x 100 (100GE) (ck)、1 x 400 (400GE)、2 x 200 (200GE)、4 x 100 (100GE)、および8 x 50 (50GE)を含む、広範なEthernetギガビット速度をサポートしています。

この汎用性により、エンジニアはさまざまな構成でパフォーマンスを効果的にテストおよび測定でき、問題解決の迅速化とネットワーク信頼性の向上につながり、以下のことを実現するのに役立ちます。

- G800GE-02 800GE BERT、FEC、およびパケットブラストテスト機能により、光トランシーバー、アクティブおよびパッシブ銅ケーブル、シリコンデバイスのBER性能を検証します。

- すべてのEthernet速度で同時に、光トランシーバー、銅線インターコネクト、シリコンデバイスのBERを評価します。

- FECシンボルビットエラー密度分布解析を使用して、時間軸で発生するバーストエラーを特定するための長時間の時間指定ストレステストを実行します。

- IEEE802.3ckおよびOIF CEI-112GまたはCEI-56 IA仕様の高度なFEC対応物理層テストおよび検証のために、G800GE-02をキーサイトM8040A高性能BERTアナライザまたはキーサイトInfiniium UXRシリーズ・オシロスコープに接続します。

- G800GE-02電気同軸ケーブルインターフェースを使用して、モジュール適合ボードまたはデバイス評価ボードを接続します。

G800GE-01 QSFP-DD同軸テストシステム

G800GE-01 QSFP-DD同軸テストシステム

941-0089

キーサイトG800GEシステムは、高度なエラー検出と訂正、高速データテスト、および効率的なテスト管理のための直感的なインターフェースにより、ネットワークの信頼性とパフォーマンスを向上させます。

エンジニアは、ブラウザベースのシングルページアプリケーション (SPA) を使用して、問題を迅速に特定し、解決できます。直感的なインターフェースは、すべてのレーンまたはポートにわたるビットエラーレートテスター (BERT)、前方誤り訂正 (FEC)、およびパケット統計の包括的なシステムビューを提供します。

このソリューションは、1 x 800 (800GE)、2 x 400 (400GE)、4 x 200 (200GE)、8 x 100 (100GE)、クロック付き8 x 100 (100GE) (ck)、1 x 400 (400GE)、2 x 200 (200GE)、4 x 100 (100GE)、および8 x 50 (50GE)を含む、広範なEthernetギガビット速度をサポートしています。

この汎用性により、エンジニアはさまざまな構成でパフォーマンスを効果的にテストおよび測定でき、問題解決の迅速化とネットワーク信頼性の向上につながり、以下のことを実現するのに役立ちます。

- G800GE-02 800GE BERT、FEC、およびパケットブラストテスト機能により、光トランシーバー、アクティブおよびパッシブ銅ケーブル、シリコンデバイスのBER性能を検証します。

- すべてのEthernet速度で同時に、光トランシーバー、銅線インターコネクト、シリコンデバイスのBERを評価します。

- FECシンボルビットエラー密度分布解析を使用して、時間軸で発生するバーストエラーを特定するための長時間の時間指定ストレステストを実行します。

- IEEE802.3ckおよびOIF CEI-112GまたはCEI-56 IA仕様の高度なFEC対応物理層テストおよび検証のために、G800GE-02をキーサイトM8040A高性能BERTアナライザまたはキーサイトInfiniium UXRシリーズ・オシロスコープに接続します。

- G800GE-02電気同軸ケーブルインターフェースを使用して、モジュール適合ボードまたはデバイス評価ボードを接続します。

サービスとサポート

厳選されたサポートプランと、優先的な対応および迅速なターンアラウンドタイムにより、迅速なイノベーションを実現します。

予測可能なリースベースのサブスクリプションとフルライフサイクル管理ソリューションにより、ビジネス目標をより迅速に達成できます。

KeysightCareのサブスクライバーとして、コミットされた技術サポートなど、より質の高いサービスをご体験ください。

テストシステムが仕様どおりに動作し、ローカルおよびグローバルな標準に準拠していることを保証します。

社内での講師主導トレーニングやeラーニングにより、迅速に測定を実施できます。

キーサイトのソフトウェアをダウンロードするか、最新バージョンにアップデートしてください。

よくあるご質問

マルチスピードイーサネットテストプラットフォームは、エンジニアが50GE、100GE、200GE、400GE、および800GEインターフェースを単一のコンパクトなテストシステムで検証することを可能にします。この統合されたアプローチにより、複数のスタンドアロンテスターや繰り返しの再構成の必要がなくなり、セットアップ時間と設備投資の両方を削減します。PAM4シグナリングとマルチレーン相互運用性のサポートにより、これらのシステムはシリコンの立ち上げ、相互運用性テスト、およびIEEE 802.3標準への準拠を効率化します。マルチレートテストは、ハイパースケールデータセンター、AIインターコネクト、およびクラウドインフラストラクチャにおいて特に価値があります。これらの環境では、ネットワーク要素が混合展開で異なる速度で動作することがよくあります。再ケーブリングやレーンリマッピングなしでフルスピード検証を可能にすることで、マルチスピードプラットフォームは一貫したパフォーマンスを保証し、次世代イーサネット展開への準備を加速します。

リアルタイムFEC解析は、高速イーサネットテスト中にシンボルおよびレーンレベルでのエラー動作に関する継続的な洞察を提供します。シンボルエラー密度、バーストエラー耐性、レーンマージンなどのRS-544 (KP4) FECパラメータを監視することで、エンジニアは従来のBER(ビットエラーレート)テストでは見落とされがちな弱点、リタイマーの不安定性、または限界的な光パスを特定できます。リアルタイムの可視性により、発生する問題の早期検出が可能になり、より迅速な根本原因特定をサポートし、ストレス下でのFECアルゴリズムの有効性を検証します。スイッチ、ルーター、AIアクセラレータの相互接続にとって、正確なFEC診断は超低パケットエラーレートを達成し、信頼性の高い高スループット動作を確保するために不可欠です。

コードワードトリガとキャプチャ、BERT推論FECシミュレーションなどのイーサネットデバッグ機能は、物理的なFECハードウェアを必要とせずに、エンジニアがエラーイベントを分析できるようにします。コードワードベースのトリガは、過渡的または断続的な障害の正確な捕捉を可能にし、推論FECシミュレーションは、複雑なエラーシーケンスをデコードして、ライブネットワークで修正されたかどうかを判断するのに役立ちます。これらの機能は、微妙なレーン固有の障害が断続的な障害を引き起こす可能性があるシリコン検証、リタイマ特性評価、およびPHYの立ち上げにおいて特に重要です。強化されたエラー特定機能は、デバッグサイクルを短縮し、市場投入までの時間を削減し、マルチレーン高速リンクが厳格な性能仕様を満たすことを保証します。

PAM4ベースのイーサネット信号は、ノイズ、ジッタ、クロストークに非常に敏感です。マルチレート・イーサネット・テスト・プラットフォームと高性能ベンチトップ・オシロスコープを統合することで、エンジニアは詳細なPAM4アイダイアグラム解析、ジッタ分解、信号品質検証を、レイヤー1~2プロトコルおよびFECテストと並行して実行できます。計測器間の共有トリガリングにより、トラフィック生成と物理層測定が同期され、障害の原因と影響の両方を明らかにする相関デバッグワークフローが可能になります。この統合は、自動コンプライアンス・テスト、マージン解析、およびIEEEおよびOIF-CEI仕様に対する検証もサポートしており、これはハイパースケール・データセンター、AIファブリック、およびキャリアグレード・ネットワークにおける信頼性の高い性能を確保するために不可欠です。