Choose a country or area to see content specific to your location

What are you looking for?

-

-

WirelessPro 3GPP AI Simulation Platform

WirelessPro empowers you to model, simulate, and analyze various aspects of 5G networks, 5G Advanced technologies, and future 6G wireless channels with unparalleled ease and accuracy.

-

Digital Validation. Faster.

Get faster, clearer insights with our new multicore, 12-bit oscilloscope up to 33 GHz.

-

Discover Keysight AI Data Center Builder

Emulate every part of your data center infrastructure. Emulate Anything. Optimize Everything.

-

Simplify Complexity with Advanced Signal Analyzer Software

Accelerate signal analysis testing with Keysight’s VSA software. Visualize, demodulate, and troubleshoot with over 75+ signal standards with precision.

-

Introducing AI-Enhanced Packet Brokers

With extra memory and storage, these enhanced NPBs run Keysight's AI security and performance monitoring software and AI stack.

-

Precision In-Circuit Testing for Production

Achieve fast, accurate board-level testing with robust inline and offline ICT designed for modern manufacturing.

-

Accelerate Your Innovation Engine

Explore curated support plans, prioritized to keep you innovating at speed.

-

-

Stream 120 MHz I/Q Data to Your Laptop in the FieldPinpoint interference with post-processing spectrum management software in the lab.

Now You Can Run Fast, Accurate Tests up to 192 kW

Now You Can Run Fast, Accurate Tests up to 192 kWOur high-density ATE power supplies end trade-offs between test throughput and precision.

-

- Solutions

-

Explore engineer-authored content and a vast knowledge base with thousands of learning opportunities.

FeaturedKeysight Learn offers immersive content on topics of interest, including solutions, blogs, events, and more.

- Buy

-

Quick access to support related self-help tasks.

Additional content to support your product needs.

Do more with Keysight ServicesExplore services to accelerate every step of your innovation journey.

Multirate Test Systems Versatile FEC and BERT test platforms for 800GE interconnect validation

- Overview

- All Models

- Accessories

- Software

- Support

Automation-ready systems for Ethernet validation from 50GE to 800GE

Keysight multirate test systems provide high-performance, lane-accurate Ethernet validation from 50GE through 800GE in a compact, lab-friendly footprint. Combining pulse amplitude modulation (PAM4) BER analysis, real-time FEC analysis, and Layer 1 to 2 traffic generation, these systems enable testing across multiple speeds and interfaces without recabling or manual lane remapping. Multirate platforms help research and development and production test engineers accelerate debugging, validate silicon, transceiver, and cable / retimer performance, and ensure multilane interoperability, including standards compliance when combined with an oscilloscope-based compliance suite. Choose a model by the number of ports, interface speeds, and interface types you need. Request a quote for one of our popular configurations today. Need help selecting? Check out the resources below.

Multispeed port flexibility

Supports OSFP800, QSFP‑DD, and coaxial interconnect interfaces from 100GE to 800GE, no reconfiguration required.

Real-time FEC analysis

Monitor RS-544 (KP4) FEC performance with symbol error density, burst tolerance, and lane margin to quickly identify weak links and retimer issues.

Enhanced BERT debug

Use FEC-aware bit error distribution for precise error visualization and accelerated receiver and cable debugging without physical FEC hardware.

Lab instrument integration

Integrate with Keysight benchtop oscilloscopes for PAM4 eye, jitter analysis, and synchronized compliance testing via shared triggers.

-

Ports

2 to 4

-

Interface speed modes

800G, 400G

-

Interface

QSFP-DD, OSFP800

-

Protocol support

Ethernet

Most popular configurations

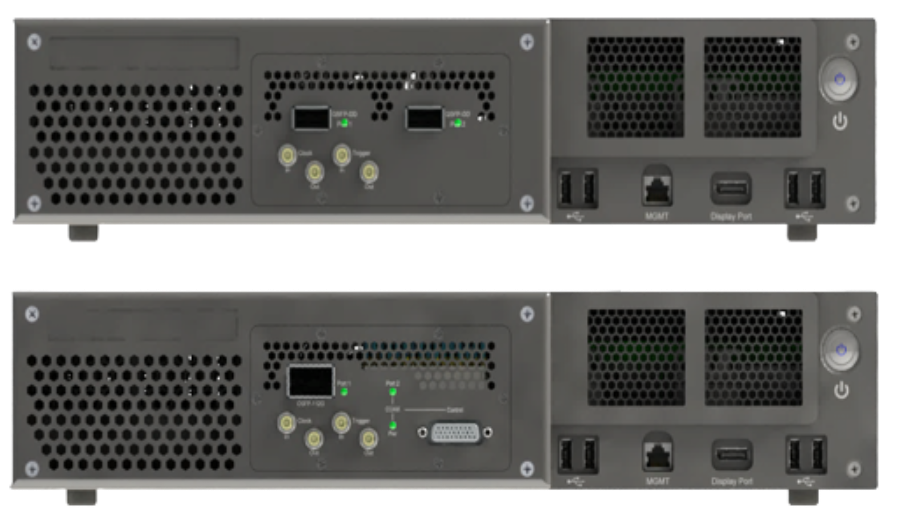

A400GE-QDD 4-Port Layer 1 BERT QSFP-DD Test System

A400GE-QDD 4-Port Layer 1 BERT QSFP-DD Test System

941-0081

The Keysight A400GE-QDD four-port, 400GE / 200GE / 100GE / 50GE Layer 1 BERT QSFP-QDD test system includes a fixed chassis containing the latest version of the Keysight KiOS software.

- Identify issues quickly with KiOS. The application offers a system-wide view of bit error rate testing (BERT) and forward error correction (FEC) statistics across all lanes. It supports 1 x 400GE, 2 x 200GE, 4 x 100GE, and 8 x 50GE speeds.

- Measure BER and FEC performance in minutes instead of hours. Evaluate new optical transceivers and copper cable interconnects at all Ethernet speeds simultaneously using the Enhanced BERT option.

- Easily generate pass / fail test reports and conduct long-duration (timed) and stress tests using Keysight KP4 FEC symbol bit error distribution analysis to detect bursty and thermal errors over time.

- Simplify connections between the A400GE-QDD and the Keysight M8040A BERT analyzer, as well as your development boards, using optional host and module compliance boards, cables, and adapter bundles.

- Leverage field-proven technology built on two generations of 400GE QSFP-DD test systems.

G800GE-02 2-Port OSFP Test System

G800GE-02 2-Port OSFP Test System

941-0086

The Keysight G800GE-02 system ensures reliable, high-speed network performance with advanced error detection and correction, comprehensive Layer 1 and Layer 2 testing, and an intuitive interface for streamlined test management.

Engineers can quickly identify and resolve issues with the browser-based single-page application (SPA). The intuitive interface provides a comprehensive system view of all the bit error rate tester (BERT), forward error correction (FEC), and packet statistics across all lanes or ports.

The solution supports a wide range of Ethernet gigabit speeds, including 1 x 800 (800GE), 2 x 400 (400GE), 4 x 200 (200GE), 8 x 100 (100GE), 8 x 100 (100GE) with clock (ck), 1 x 400 (400GE), 2 x 200 (200GE), 4 x 100 (100GE), and 8 x 50 (50GE).

This versatility ensures that engineers can effectively test and measure performance across various configurations, leading to faster problem resolution and enhanced network reliability to help you do the following:

- Validate the BER performance of optical transceivers, active and passive copper cables, and silicon devices with the G800GE-02 800GE BERT, FEC, and packet blast test capabilities.

- Evaluate optical transceivers, copper interconnects, and silicon devices BER at all Ethernet speeds simultaneously.

- Perform long-duration timed and stress tests by using the FEC symbol bit error density distribution analysis to identify bursty errors that occur over time.

- Connect any G800GE-02 to the Keysight M8040A high-performance BERT analyzer or the Keysight Infiniium UXR-Series oscilloscopes for advanced FEC-aware physical layer test and validation of IEEE802.3ck and OIF CEI-112G or CEI-56 IA specifications.

- Connect a module compliance board or device evaluation board using the G800GE-02 electrical coaxial cabling interface.

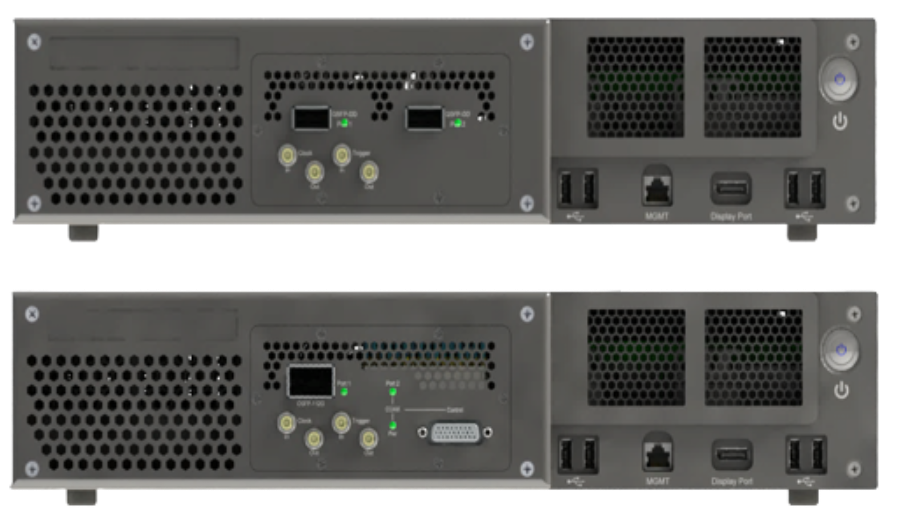

G800GE-01 QSFP-DD Coxial Test System

G800GE-01 QSFP-DD Coxial Test System

941-0089

The Keysight G800GE system enhances network reliability and performance with advanced error detection and correction, high-speed data testing, and an intuitive interface for efficient test management.

Engineers can quickly identify and resolve issues with the browser-based single-page application (SPA). The intuitive interface provides a comprehensive system view of all the bit error rate tester (BERT), forward error correction (FEC), and packet statistics across all lanes or ports.

The solution supports a wide range of Ethernet gigabit speeds, including 1 x 800 (800GE), 2 x 400 (400GE), 4 x 200 (200GE), 8 x 100 (100GE), 8 x 100 (100GE) with clock (ck), 1 x 400 (400GE), 2 x 200 (200GE), 4 x 100 (100GE), and 8 x 50 (50GE).

This versatility ensures that engineers can effectively test and measure performance across various configurations, leading to faster problem resolution and enhanced network reliability to help you do the following:

- Validate the BER performance of optical transceivers, active and passive copper cables, and silicon devices with the G800GE-02 800GE BERT, FEC, and packet blast test capabilities.

- Evaluate optical transceivers, copper interconnects, and silicon devices BER at all Ethernet speeds simultaneously.

- Perform long-duration timed and stress tests by using the FEC symbol bit error density distribution analysis to identify bursty errors that occur over time.

- Connect any G800GE-02 to the Keysight M8040A high-performance BERT analyzer or the Keysight Infiniium UXR-Series oscilloscopes for advanced FEC-aware physical layer test and validation of IEEE802.3ck and OIF CEI-112G or CEI-56 IA specifications.

- Connect a module compliance board or device evaluation board using the G800GE-02 electrical coaxial cabling interface.

Services and support

Innovate at speed with curated support plans and prioritized response and turn-around times.

Get predictable, lease-based subscriptions and full lifecycle management solutions—so you reach your business goals faster.

Experience elevated service as a KeysightCare subscriber to get committed technical response and more.

Ensure your test system performs to specification and meets local and global standards.

Make measurements quickly with in-house, instructor-led training, and eLearning.

Download Keysight software or update your software to the newest version.

Frequently asked questions

Multispeed Ethernet test platforms allow engineers to validate 50GE, 100GE, 200GE, 400GE, and 800GE interfaces in a single, compact test system. This consolidated approach eliminates the need for multiple standalone testers or repeated reconfiguration, reducing both setup time and capital costs. With support for PAM4 signaling and multilane interoperability, these systems streamline silicon bring-up, interoperability testing, and IEEE 802.3 standard compliance. Multirate testing is especially valuable in hyperscale data centers, AI interconnects, and cloud infrastructure, where network elements often operate at different speeds in mixed deployments. By enabling full-speed validation without recabling or lane remapping, multispeed platforms ensure consistent performance and accelerate readiness for next-generation Ethernet rollouts.

Real-time FEC analysis gives continuous insight into error behavior at the symbol and lane level during high-speed Ethernet testing. By monitoring RS-544 (KP4) FEC parameters such as symbol error density, burst error tolerance, and lane margin, engineers can pinpoint weak links, retimer instabilities, or marginal optical paths that traditional BER (bit error rate) testing may overlook. Real-time visibility allows early detection of emerging problems, supports faster root cause isolation, and validates the effectiveness of FEC algorithms under stress. For switches, routers, and AI accelerator interconnects, accurate FEC diagnostics are critical for achieving ultra-low packet error rates and ensuring reliable high-throughput operation.

Ethernet debug features such as Codeword Trigger and Capture and BERT-inferred FEC simulation enable engineers to analyze error events without requiring physical FEC hardware. Codeword-based triggering allows precise capture of transient or intermittent faults, while inferred FEC simulation helps decode complex error sequences to determine whether they would have been corrected in a live network. These capabilities are especially important during silicon validation, retimer characterization, and PHY bring-up, where subtle lane-specific impairments can cause intermittent failures. Enhanced error localization shortens the debug cycle, reduces time-to-market, and ensures that multilane high-speed links meet stringent performance specifications.

PAM4-based Ethernet signaling is highly sensitive to noise, jitter, and crosstalk. Integrating a multirate Ethernet test platform with a high-performance benchtop oscilloscope enables engineers to perform detailed PAM4 eye diagram analysis, jitter decomposition, and signal integrity validation alongside Layer 1–2 protocol and FEC testing. Shared triggering between instruments synchronizes traffic generation with physical layer measurements, enabling correlated debug workflows that reveal both the cause and impact of impairments. This integration also supports automated compliance testing, margin analysis, and validation against IEEE and OIF-CEI specifications, which is critical for ensuring reliable performance in hyperscale data centers, AI fabrics, and carrier-grade networks.