Choose a country or area to see content specific to your location

何をお探しですか?

-

-

3D Interconnect Designer

3D Interconnect Designerは、チップレット、積層ダイ、パッケージ、PCBなど、あらゆる高度な相互接続構造に対応する柔軟なモデリングおよび最適化環境を提供します。

-

-

-

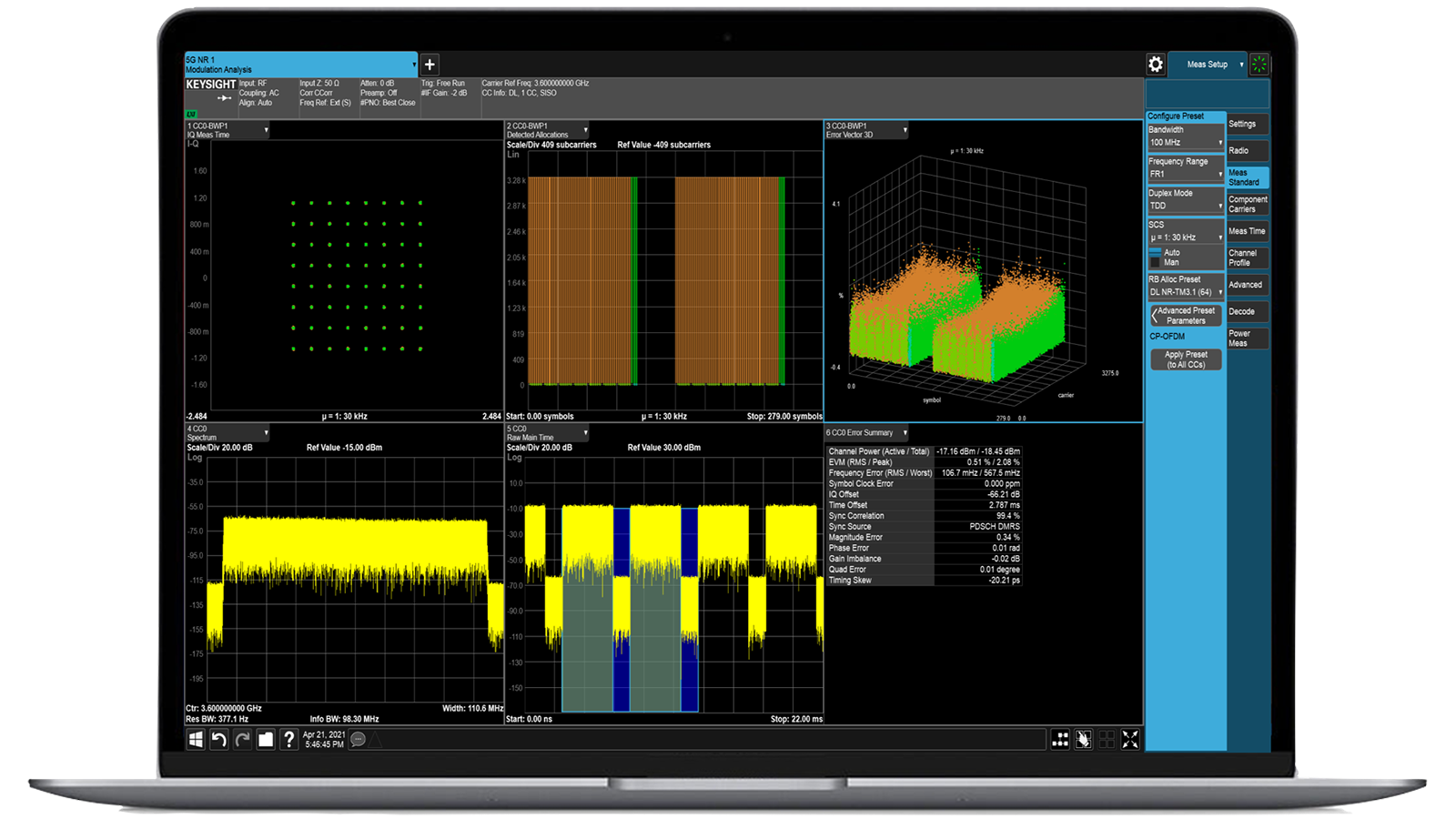

Xシリーズ測定アプリケーションで信号解析を加速

25種類以上のXシリーズアプリケーションを使用して、ワイヤレス、航空宇宙/防衛、EMI、位相ノイズの各分野で信号の解析、復調、トラブルシューティングを行います。

-

AI強化型パケットブローカーのご紹介

追加のメモリとストレージにより、これらの強化されたNPBは、キーサイトのAIセキュリティおよびパフォーマンス監視ソフトウェアとAIスタックを実行します。

-

-

-

-

-

- ソリューション

-

キーサイト Learnは、ソリューション、ブログ、イベントなど、関心のあるトピックに関する様々なコンテンツを提供しています。

- 購入

-

頻繁にお問い合わせされるサポート関連のお役に立つ情報すばやくアクセス

お持ちの製品をサポートするための追加情報

デジタルプロトコルアナライザ メモリインターフェースから高速シリアルプロトコルまで

キーサイトは、ポータブルロジックアナライザ、DDRロジックアナライザ、およびPCIeプロトコルソリューションを含む3つのクラスでプロトコルアナライザを提供しています。

-

ロジック・アナライザ

高速デジタル信号を正確に捕捉、解析、デバッグ

-

PCIeプロトコルアナライザ

PCIeおよびCompute Express Link (CXL) インターフェースの検証、テスト、デバッグ

-

PCIeプロトコル・エクササイザー

性能と標準のテストのためにPCIトラフィックを生成およびシミュレートします。

-

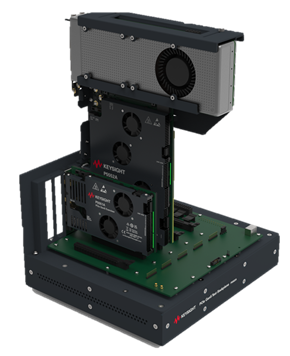

PCIeプロトコルテスト用バックプレーン

PCIeおよびCXLアドインカード向けに、安定した信号最適化インターフェースを提供します。

ロジック・アナライザ

キーサイトのロジックアナライザは、組み込みシステム、メモリ設計、高速デジタルインターフェースにおけるデジタル信号を正確に捕捉、解析、デバッグすることを可能にします。チャネル数、最大メモリ深度、サポートされる規格などの要素を考慮して、必要なロジックアナライザを選択してください。お客様のアプリケーションに最適なものを見つけるために、当社のポータブルおよびDDRロジックアナライザのラインアップをご覧ください。

PCIeプロトコルアナライザ

キーサイト LA5-class PCIeプロトコル・アナライザには、P5552AおよびP5570Aが含まれます。これらはPCIe通信に深い洞察を提供し、高速データトラフィックを正確に捕捉、デコード、解析することを可能にします。これらのアナライザは、プロトコルレベルの問題を特定し、システム性能を検証し、複雑なPCIe設計におけるデバッグを加速するのに役立ちます。データトランザクション、タイミング、プロトコル準拠に関する包括的な可視性を提供することで、PCIeインターフェースを使用するデバイス間の通信を検証するのに役立ちます。

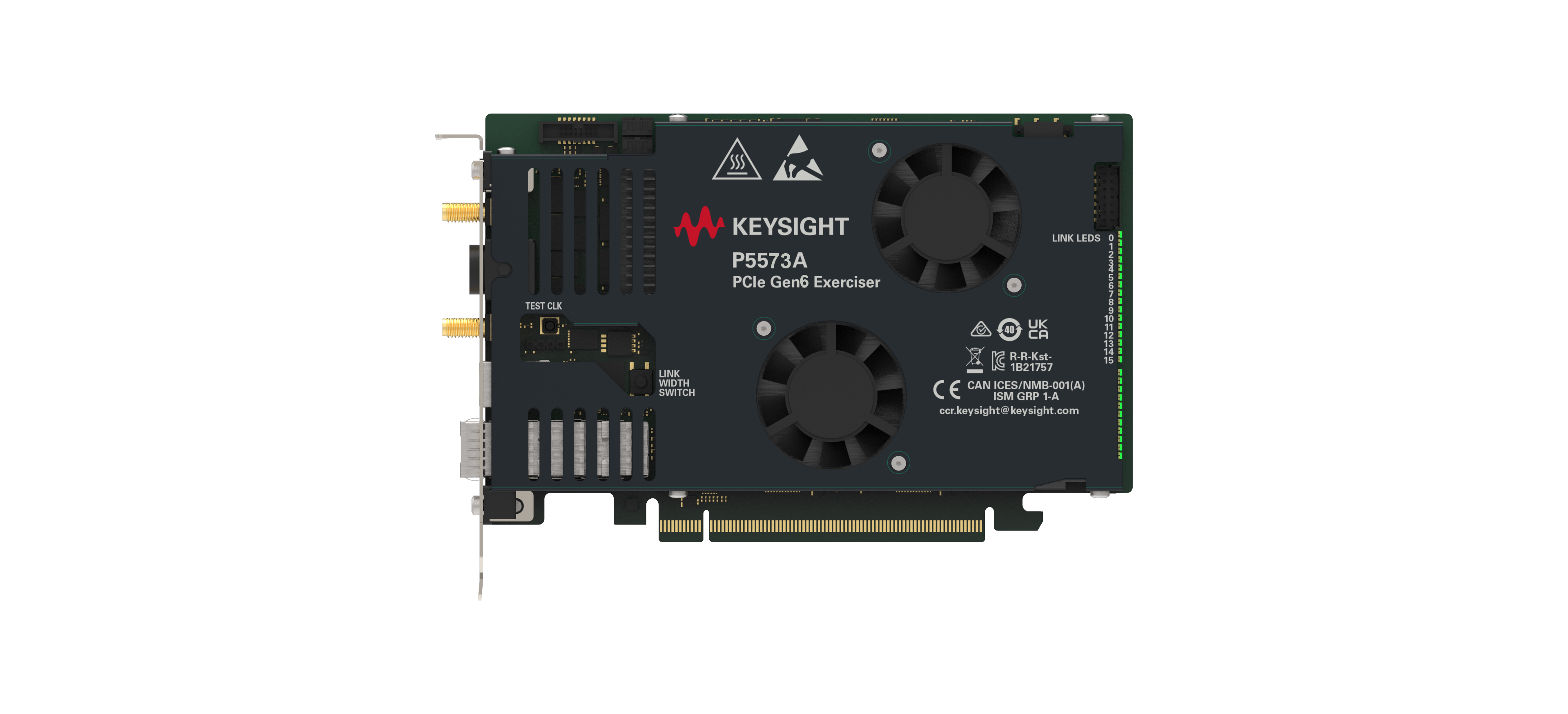

PCIeプロトコルエクササイザ

キーサイトのLA5クラスPCIeプロトコルエクササイザーには、P5551AおよびP5573Aが含まれます。これらのPCIeプロトコルエクササイザーはPCIe® トラフィックを生成・シミュレートし、PCIeデバイスおよびシステムの性能と堅牢性を厳密にテスト・検証することを可能にします。 現実の多様なシナリオやエラー状態をエミュレートすることで、当社のPCIe® プロトコル・エクササイザーは設計上の欠陥の発見、コンプライアンスの検証、様々なワークロード下でのシステム動作の最適化を支援します。

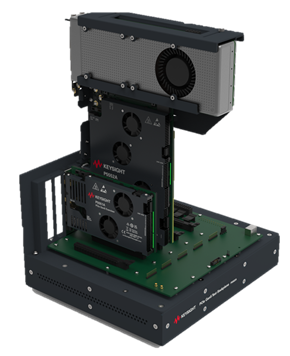

PCIeプロトコルテストバックプレーン

キーサイト LA5クラス プロトコルバックプレーンには、P5563Bが含まれます。これはPCIe® およびCXLアドインカード向けに、安定した信号最適化インターフェースを提供します。 当社のPCIeプロトコルバックプレーンは、実環境下でのデバイス性能、信号完全性、プロトコル準拠性を徹底的に評価することを保証します。堅牢な機械設計と幅広いフォームファクター互換性により、開発サイクルの加速と次世代コンピューティング、ストレージ、ネットワークソリューションの確実な提供を実現する重要なツールとなります。

ロジック・アナライザ

キーサイトのロジックアナライザは、組み込みシステム、メモリ設計、高速デジタルインターフェースにおけるデジタル信号を正確に捕捉、解析、デバッグすることを可能にします。チャネル数、最大メモリ深度、サポートされる規格などの要素を考慮して、必要なロジックアナライザを選択してください。お客様のアプリケーションに最適なものを見つけるために、当社のポータブルおよびDDRロジックアナライザのラインアップをご覧ください。

ロジック・アナライザ

キーサイトのロジックアナライザは、組み込みシステム、メモリ設計、高速デジタルインターフェースにおけるデジタル信号を正確に捕捉、解析、デバッグすることを可能にします。チャネル数、最大メモリ深度、サポートされる規格などの要素を考慮して、必要なロジックアナライザを選択してください。お客様のアプリケーションに最適なものを見つけるために、当社のポータブルおよびDDRロジックアナライザのラインアップをご覧ください。

PCIeプロトコルアナライザ

キーサイト LA5-class PCIeプロトコル・アナライザには、P5552AおよびP5570Aが含まれます。これらはPCIe通信に深い洞察を提供し、高速データトラフィックを正確に捕捉、デコード、解析することを可能にします。これらのアナライザは、プロトコルレベルの問題を特定し、システム性能を検証し、複雑なPCIe設計におけるデバッグを加速するのに役立ちます。データトランザクション、タイミング、プロトコル準拠に関する包括的な可視性を提供することで、PCIeインターフェースを使用するデバイス間の通信を検証するのに役立ちます。

PCIeプロトコルアナライザ

キーサイト LA5-class PCIeプロトコル・アナライザには、P5552AおよびP5570Aが含まれます。これらはPCIe通信に深い洞察を提供し、高速データトラフィックを正確に捕捉、デコード、解析することを可能にします。これらのアナライザは、プロトコルレベルの問題を特定し、システム性能を検証し、複雑なPCIe設計におけるデバッグを加速するのに役立ちます。データトランザクション、タイミング、プロトコル準拠に関する包括的な可視性を提供することで、PCIeインターフェースを使用するデバイス間の通信を検証するのに役立ちます。

PCIeプロトコルエクササイザ

キーサイトのLA5クラスPCIeプロトコルエクササイザーには、P5551AおよびP5573Aが含まれます。これらのPCIeプロトコルエクササイザーはPCIe® トラフィックを生成・シミュレートし、PCIeデバイスおよびシステムの性能と堅牢性を厳密にテスト・検証することを可能にします。 現実の多様なシナリオやエラー状態をエミュレートすることで、当社のPCIe® プロトコル・エクササイザーは設計上の欠陥の発見、コンプライアンスの検証、様々なワークロード下でのシステム動作の最適化を支援します。

PCIeプロトコルエクササイザ

キーサイトのLA5クラスPCIeプロトコルエクササイザーには、P5551AおよびP5573Aが含まれます。これらのPCIeプロトコルエクササイザーはPCIe® トラフィックを生成・シミュレートし、PCIeデバイスおよびシステムの性能と堅牢性を厳密にテスト・検証することを可能にします。 現実の多様なシナリオやエラー状態をエミュレートすることで、当社のPCIe® プロトコル・エクササイザーは設計上の欠陥の発見、コンプライアンスの検証、様々なワークロード下でのシステム動作の最適化を支援します。

PCIeプロトコルテストバックプレーン

キーサイト LA5クラス プロトコルバックプレーンには、P5563Bが含まれます。これはPCIe® およびCXLアドインカード向けに、安定した信号最適化インターフェースを提供します。 当社のPCIeプロトコルバックプレーンは、実環境下でのデバイス性能、信号完全性、プロトコル準拠性を徹底的に評価することを保証します。堅牢な機械設計と幅広いフォームファクター互換性により、開発サイクルの加速と次世代コンピューティング、ストレージ、ネットワークソリューションの確実な提供を実現する重要なツールとなります。

PCIeプロトコルテストバックプレーン

キーサイト LA5クラス プロトコルバックプレーンには、P5563Bが含まれます。これはPCIe® およびCXLアドインカード向けに、安定した信号最適化インターフェースを提供します。 当社のPCIeプロトコルバックプレーンは、実環境下でのデバイス性能、信号完全性、プロトコル準拠性を徹底的に評価することを保証します。堅牢な機械設計と幅広いフォームファクター互換性により、開発サイクルの加速と次世代コンピューティング、ストレージ、ネットワークソリューションの確実な提供を実現する重要なツールとなります。

アプリケーションに最適なDDRロジック・アナライザを数分で見つける

デジタル

プロトコルレベルのインサイトと解析ツールを通じて、DDR5システム検証とデバッグのベストプラクティスを習得してください。

デジタル

さまざまな動作状態におけるIoTデバイスの消費電力を正確に測定および解析する方法を学ぶ。

デジタル

PCIe®プロトコルの性能と準拠性を、開発の全段階にわたって検証する方法を学びます。

サービスとサポート

厳選されたサポートプランと、優先的な対応および迅速なターンアラウンドタイムにより、迅速なイノベーションを実現します。

予測可能なリースベースのサブスクリプションとフルライフサイクル管理ソリューションにより、ビジネス目標をより迅速に達成できます。

KeysightCareのサブスクライバーとして、コミットされた技術サポートなど、より質の高いサービスをご体験ください。

テストシステムが仕様どおりに動作し、ローカルおよびグローバルな標準に準拠していることを保証します。

社内での講師主導トレーニングやeラーニングにより、迅速に測定を実施できます。

キーサイトのソフトウェアをダウンロードするか、最新バージョンにアップデートしてください。

よくあるご質問

デジタルプロトコルアナライザは、PCIe、CXL、DDRなどの標準化されたデジタルインターフェース上のトラフィックをキャプチャ、デコード、分析するために使用されるテスト機器です。システム開発中に、正しいプロトコル動作、タイミング、トランザクションフローを検証するために使用されます。

適切なアナライザの選択は、ターゲットプロトコル、リンク速度、レーン幅、および検証ステージによって異なります。ロジックアナライザとは異なり、プロトコルアナライザはトランザクションレベルで動作するため、低レベルの信号デバッグよりも、システム検証、相互運用性テスト、およびコンプライアンスワークフローに最適です。

ロジックアナライザは、ピンまたはバスレベルで複数のデジタル信号をキャプチャおよび観測するために使用されるデジタルデバッグ機器であり、タイミング関係、状態変化、および制御信号の可視性を提供します。プロトコル動作が完全に確立される前の、低レベルのハードウェア立ち上げ、ファームウェアデバッグ、および信号相互作用の検証に使用されます。

対照的に、デジタルプロトコルアナライザは、キャプチャされたトラフィックをPCIe、CXL、DDRなどの標準のプロトコル対応トランザクションにデコードすることにより、より高い抽象レベルで動作します。

エンジニアは通常、初期のハードウェア検証にはロジックアナライザを選択し、システムレベルの検証、相互運用性テスト、性能分析、およびコンプライアンス検証にはプロトコルアナライザを選択します。

デジタルプロトコルアナライザは、PCI Express (PCIe)、Compute Express Link (CXL)、DDRメモリ、その他の高速インターコネクトなど、特定のインターフェース規格をサポートしています。各アナライザは、定義されたプロトコル仕様に従ってトラフィックをデコードおよび解釈するように設計されています。

選択は、プロトコルバージョン、最大データレート、レーン数、およびコンプライアンス要件に基づきます。多目的デジタルツールとは対照的に、プロトコルアナライザは、トランザクション、リンク状態、およびエラー条件を正しくデコードするために、テスト対象のプロトコルリビジョンに正確に一致する必要があります。

デジタルプロトコルアナライザの主要な仕様は、プロトコル動作を正確に観測およびキャプチャできるかどうかを定義します。これらには、サポートされるデータレート、レーン数、キャプチャメモリ深度、タイムスタンプ分解能、およびトリガ機能が含まれます。

高速インターフェースの場合、十分なメモリ深度と正確なトリガは、まれなエラーや長いトランザクションシーケンスを分離するために不可欠です。アナログ波形忠実度に焦点を当てるオシロスコープとは異なり、プロトコルアナライザは、複雑な高スループットリンク全体での完全なロスレスキャプチャと正しいプロトコルデコードを優先します。

プロトコルアナライザは実際のシステムトラフィックをパッシブに観測しますが、プロトコルエクササイザはプロトコルトランザクションをアクティブに生成および制御します。これらは連携して、設計の立ち上げ、エラー処理検証、およびストレステストに使用される閉ループ検証を形成します。

実際には、エンジニアはエクササイザを使用してデバイスをエミュレートしたり、制御されたトラフィックやエラー条件を注入したりし、その後アナライザを使用してトランザクションレベルで応答を検証します。この組み合わせたワークフローにより、完全なシステムを必要とせずに繰り返し可能なテストが可能になり、初期開発、コンプライアンス試験、および根本原因分析の基礎となります。

デジタルプロトコルアナライザは、キャプチャされたトラフィックをプロトコル仕様で定義されたトランザクション、リンク状態、およびタイミング関係にデコードすることにより、プロトコルエラーのトラブルシューティングに使用されます。これにより、エンジニアは違反、リトライ、不正なパケット、または予期しない状態遷移を特定できます。

性能分析の場合、アナライザは物理層では見えないトランザクション遅延、スループットのボトルネック、および順序付けの問題を明らかにします。この機能により、最新のコンピューティングシステムで使用される複雑なデジタルインターフェース全体での相互運用性の問題のデバッグ、システムレベルの性能チューニング、および標準準拠にとって不可欠なものとなります。キーサイト・テクノロジーは、これらのプロトコルレベルの検証手法を進歩させていることで広く認識されています。