Choose a country or area to see content specific to your location

何をお探しですか?

-

-

3D Interconnect Designer

3D Interconnect Designerは、チップレット、積層ダイ、パッケージ、PCBなど、あらゆる高度な相互接続構造に対応する柔軟なモデリングおよび最適化環境を提供します。

-

-

-

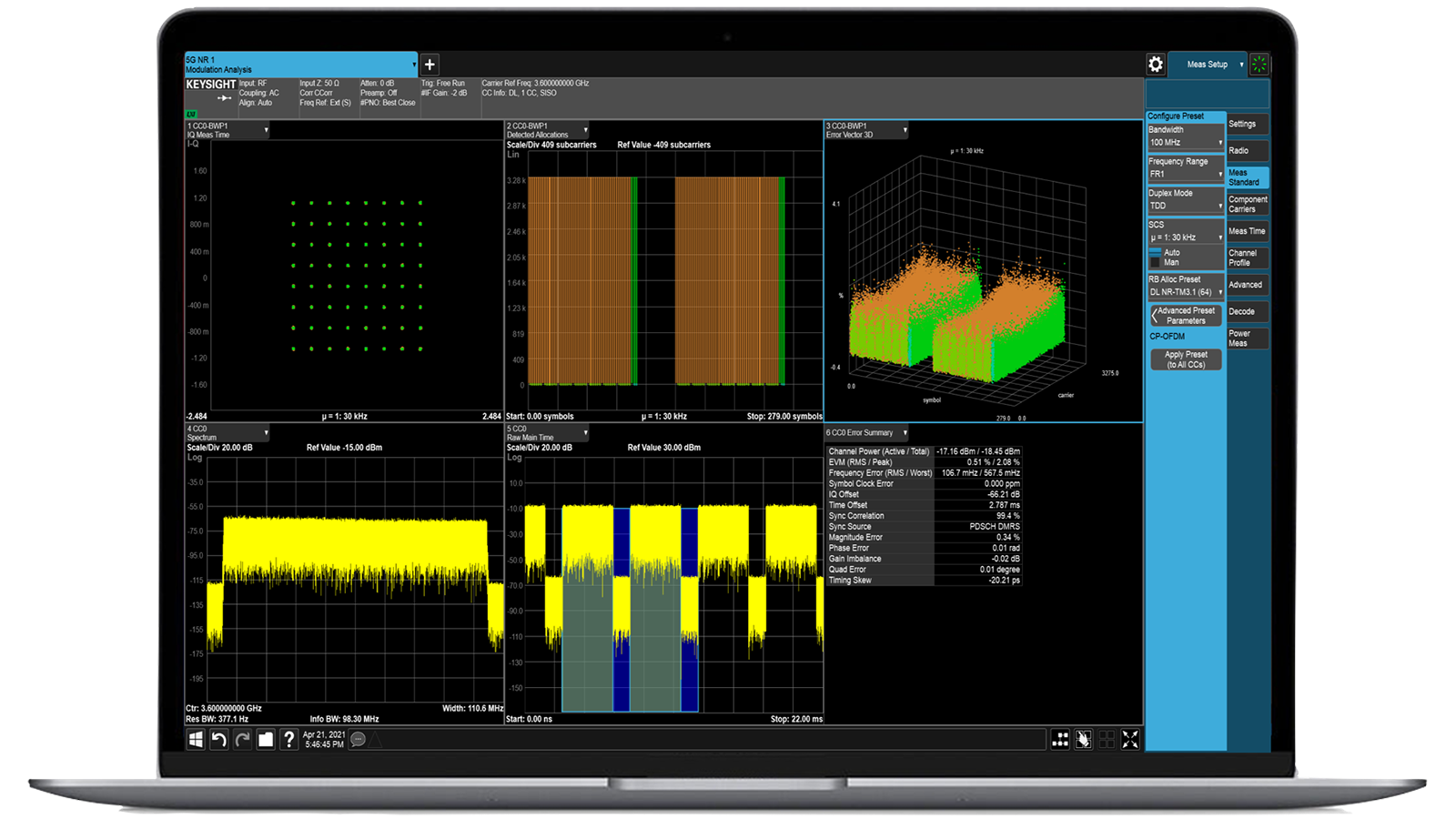

Xシリーズ測定アプリケーションで信号解析を加速

25種類以上のXシリーズアプリケーションを使用して、ワイヤレス、航空宇宙/防衛、EMI、位相ノイズの各分野で信号の解析、復調、トラブルシューティングを行います。

-

AI強化型パケットブローカーのご紹介

追加のメモリとストレージにより、これらの強化されたNPBは、キーサイトのAIセキュリティおよびパフォーマンス監視ソフトウェアとAIスタックを実行します。

-

-

-

-

-

- ソリューション

-

キーサイト Learnは、ソリューション、ブログ、イベントなど、関心のあるトピックに関する様々なコンテンツを提供しています。

- 購入

-

頻繁にお問い合わせされるサポート関連のお役に立つ情報すばやくアクセス

お持ちの製品をサポートするための追加情報

- 概要

- すべてのモデル

- アクセサリ

- ソフトウェア

- サポート

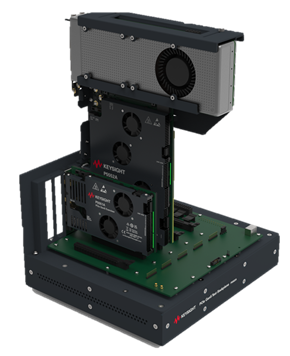

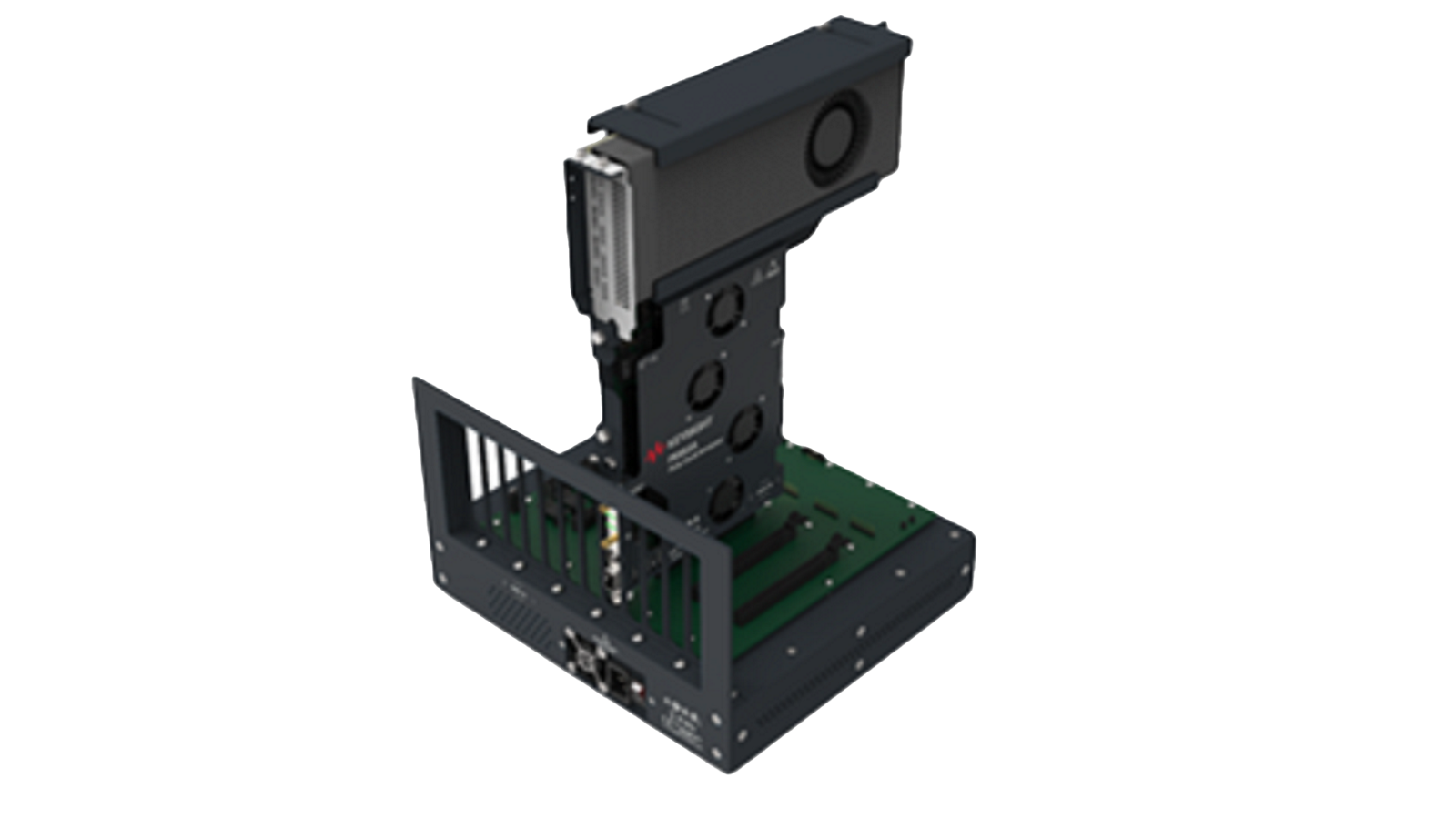

実環境条件下でPCIeデバイスを評価する

キーサイト LA5-class プロトコルバックプレーンは、PCIeおよびCXLアドインカード向けに安定した信号最適化インターフェースを提供します。当社のPCIeプロトコルバックプレーンは、実環境条件下でデバイスの性能、信号完全性、およびプロトコル準拠を徹底的に評価できることを保証します。その堅牢な機械設計と広範なフォームファクタ互換性により、開発サイクルを加速し、次世代のコンピューティング、ストレージ、およびネットワーキングソリューションを自信を持って提供するための不可欠なツールとなっています。今すぐキーサイトのPCIeプロトコルバックプレーンの見積もりを依頼するか、ご注文ください。選定でお困りですか?以下のリソースをご確認ください。

高速データサポート

PCIe 6.0のデータレートをレーンあたり最大64 GT/sまで正確かつ信頼性高くテストすることを可能にし、次世代デバイスにおけるシグナルインテグリティ、プロトコルコンプライアンス、および性能を検証するために不可欠です。

信号インテグリティの強化

バックプレーンとPCIeデバイス間のクロストークを低減し、インピーダンスを維持し、信号伝送を最適化するために、PCI-SIG®カード電気機械的(CEM)仕様に準拠して設計されています。

フォームファクタの互換性

Enterprise and Data Center SSD Form Factor (EDSFF) およびOpen Compute Project Network Interface Card (OCP-NIC) をサポートし、多様なデータセンター、ストレージ、およびネットワーキングデバイスのテストを可能にします。

統合型電源

低ノイズ、高効率の電源を搭載し、PCIe補助電源も利用可能で、高電力エンドポイント・デバイスに確実に対応し、安定した一貫性のある性能テストを実現します。

-

Maximum data rate

64 GT/s

-

Protocols

NRZ, PAM4

-

規格

PCIe 6.0, PCIe 5.0, PCIe 4.0, PCIe 3.0, PCIe 2.0, PCIe 1.0, CXL 1.1, CXL 2.0

標準構成

LA5-class PCIeプロトコルアナライザ、PCIe 6.0用プロトコルテストバックプレーン

LA5-class PCIeプロトコルアナライザ、PCIe 6.0用プロトコルテストバックプレーン

P5563B

キーサイト P5563B PCIe 6.0 プロトコルテスト用バックプレーンは、自立ポータブル パッシブバックプレーンにより、PCIe 6.0 アドインカードのテストを容易に実現します。P5563B は、あらゆる組み合わせのエクササイザーとアナライザー、および被試験デバイスに必要な電力を供給します。

設計の真の性能を確認する

テストプラットフォームには、1つのテストバスCEM-CEMコネクタが付属しています。フル機能で便利、かつポータブルなP5563Bは、新しいPCIe製品のテスト中のセットアップを簡素化します。

- 2.5 GT/sから64 GT/sまで対応

- x4、x8、x16の物理レーン幅をサポートするCEM接続

- Supports PCIe 6.0

- クロストークを低減し、シグナルインテグリティを向上させるためのCEM SIの機能強化

- 信頼性の高い64GT/s動作をサポートするために、低損失材料を使用しています。

- Integrated low noise power supply with PCIe auxilary power available for high power endpoint devices

- 顧客のDUTとの信頼性の高い動作を実現する安定した機械的構造

- EDSFF/OCP-NICフォームファクターに対応

サービスとサポート

厳選されたサポートプランと、優先的な対応および迅速なターンアラウンドタイムにより、迅速なイノベーションを実現します。

予測可能なリースベースのサブスクリプションとフルライフサイクル管理ソリューションにより、ビジネス目標をより迅速に達成できます。

KeysightCareのサブスクライバーとして、コミットされた技術サポートなど、より質の高いサービスをご体験ください。

テストシステムが仕様どおりに動作し、ローカルおよびグローバルな標準に準拠していることを保証します。

社内での講師主導トレーニングやeラーニングにより、迅速に測定を実施できます。

キーサイトのソフトウェアをダウンロードするか、最新バージョンにアップデートしてください。

よくあるご質問

PCIプロトコル・テスト・バックプレーンは、PCIeデバイスおよびテスト対象システムを評価するための制御された信頼性の高い環境を提供するため、有用です。これにより、PCIeホストとエンドポイントの間にプロトコル・アナライザ、エクササイザ、その他のテスト・ツールを簡単に挿入でき、DUTやマザーボードを変更することなく信号アクセスを容易にします。バックプレーンは、さまざまなフォームファクタをサポートしながら信号完全性を維持し、異なるデバイスタイプ間でのシームレスな検証を可能にします。特に、再現可能なテスト、相互運用性の問題のデバッグ、およびコンプライアンス検証に価値があり、高速PCIe開発およびテスト・ワークフローにおける重要なコンポーネントとなっています。

PCIeは高速で高感度なインターフェースであり、機械的接続不良、信号反射、電圧変動などのわずかな不安定性でも、断続的なエラー、リンク障害、または不正確なテスト結果につながる可能性があります。安定したインターフェースは、デバイス自体とは無関係な変数を排除し、真のパフォーマンス、プロトコル準拠、およびエラー検出に集中できるようにします。この安定性は、異なる速度 (例:Gen4、Gen5) でのテストや、長時間のストレステスト中に特に重要です。これらのテストでは、不安定性があるとデータ整合性が損なわれたり、実際の設計上の問題が隠蔽されたりする可能性があります。

PCIeテストバックプレーンに統合された電源は、ホストシステムから独立して、被試験デバイス(DUT)に安定した、制御された、絶縁された電源を提供するため役立ちます。これにより、テスト中に電源条件を正確に管理し、消費電力を監視し、パワーマージニングや故障注入を実行できます。外部電源の必要性を排除し、高速信号の完全性を妨げる可能性のあるノイズや不安定性を低減することで、セットアップを簡素化します。統合された電源は、自動電源サイクルも可能にし、これはPCIeデバイスにおけるストレス試験、検証、および電源関連の問題のデバッグに不可欠です。