What are you looking for?

Suggested searches

No product matches found - System Exception

Matched content

PathWave Advanced Design System (ADS) 2020 Update 1.0 Product Release

Highlights

PathWave ADS 2020 Update 1.0 delivers solutions and more for:

- High-Speed Digital (HSD) Design

- Electromagneitc (EM) Simulation

- Circuit Simulation

- Power Electronics Design

- Design and Technology Management

- Design Editing

Description

PathWave ADS 2020 Update 1.0 delivers solutions and more for challenging High-Speed Digital, RF & Microwave and Power Electronics designs including the following.

PathWave ADS 2020 Update 1.0 delivers solutions and more for challenging High-Speed Digital, RF & Microwave and Power Electronics designs including the following.

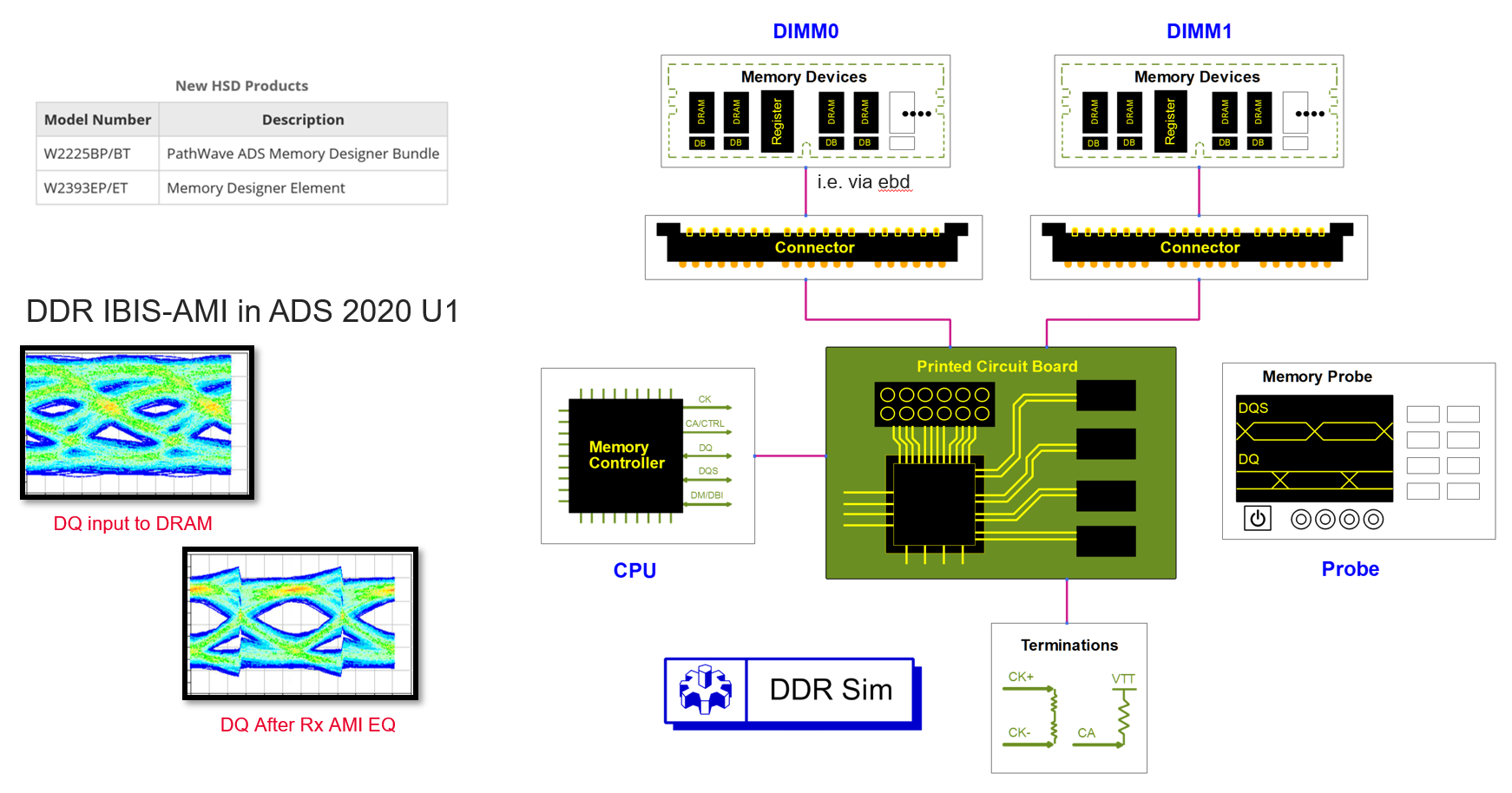

High-Speed Digital Design

- DDR/Memory

- DDR5 support in Memory Designer

- Innovative Bit-By-Bit simulation mode supporting IBIS-AMI models, enhanced for single-ended signals, and externally supplied clocking

- Write Leveling (delay file) support

- Data Bus Inversion (DBI) support

- Automated signal property assignment for 3rd party PCB data

- Group editing support, Memory Designer Setup Controller, easier IBIS/model setup

- SIPro & PIPro

- Increased accuracy by reducing port parasitics in both SIPro and PIPro-AC. This was achieved by moving to Sheet Ports, and by splitting pins in PIPro. This is particularly important for PDNs with a low resistance where inductance dominates.

- Parallel simulation is now available in SIPro through option ‘Mesh-Splitting’. It allows a singular analysis setup to be split into multiple parallel jobs, with control over the threads used per job. It can greatly speed up simulation time on a big workstation or server farm. Or it can be used to reduce the maximum memory needed to solve the solution.

- PIPro AC and SIPro Analysis support non-updatable (embedded) components for all component model types, improving simulation time

- SIPro and PIPro can both use ADS schematic cells as passive components in the simulation.

- SIPro accuracy improvement for differential lines with vias having a common clearance hole (e.g. merged anti-pads)

EM Simulation

- RFPro

- Speed improvements when opening RFPro or switching component roles

- The FEM solver is now available in RFIC platforms to complement Momentum for FBAR filters or Wafer-Level Packaging

- Introduction of a new FEM solver : Generation 2

- Dramatically decrease the pre-processing time

- Improved robustness in meshing

- New Mesh Domain Optimization mode for FEM to automatically decrease the simulation space when selecting nets or components while keeping an accurate ground return path

- FEM now supports encrypted substrates

Circuit Simulation

- Models

- Support of TMI models

- Support of XL for BSIMSOI models

- Circuit Envelope

- Introduction of Compact Test Signals to dramatically accelerate Envelope EVM simulations

- Convolution in Envelope is now available easing settings when frequency-dependent files are used

- ElectroThermal

- FloorPlanner results are now accurate when power specified is in [mW/uW/pW].

Power Electronics

- Power Electronics Professional (PEPro)

- New test bench to plot Radiated EMI versus frequency and angle for pre-compliance testing of PCB layout candidates

- Improved the Conducted EMI results data display for better spectral accuracy and noise level

- Fixed the PEPro bugs. For example, display text in the Undo button

- Design Translation

- Fixed the issue where the netlist file import failed on Windows operating systems when there was a space in the input file's path

- Fixed the issue where the file name along with the file path was being used instead of just the file name in the NetlistInclude component's IncludeFile field, generated during netlist file import

- Fixed the LTspice import bugs. For example, the simulator reserved words are fixed

Design and Technology Management

- General

- Fixed the crash when workspace changes during a library rename

- Fixed possible crash editing Instance Parameters

- Fixed possible crash in Design Search and Show Reference

- Support "patch" component of basic library in Cadence

- Drag/Drop support between reference/dependent windows

- Data Display

- Data Display Expression Manager and Expression Hierarchy improvements

- Datalink (Python Interface)

Design Editing

- Added AEL functions to get end or corner for line segment of an interconnect

- Added db_rotate_selected_objects() function to rotate all the selected objects in the given context

- Added AEL functions to use in macro recording when user places an unconstrained via

- Now can draw a Trace (with AEL commands) using a Line Type

- Added tech_get_padstack_def_names() AEL function

- Added AEL functions to extract Keepout information

- Added AEL functions to get ground plane outline points

- Added AEL functions to access via name, template name, start stop layer of a PCB Via instance

Learn More

View other ADS Product Versions.

Return to Keysight Advanced Design System (ADS)