무엇을 찾고 있습니까?

추천 검색어

No product matches found - System Exception

일치하는 컨텐츠

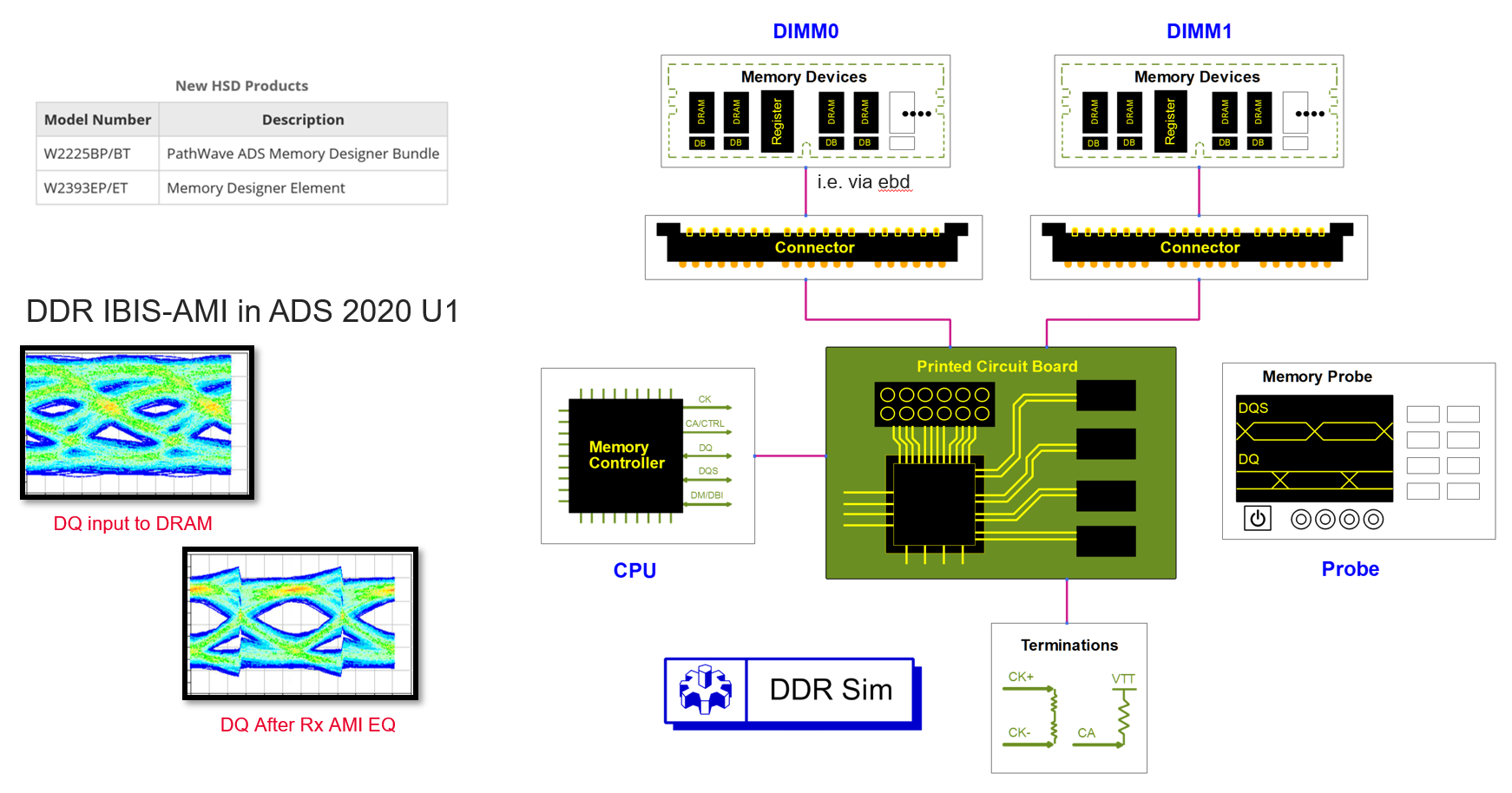

PathWave ADS(Advanced Design System) 2020 업데이트 1.0

Highlights

PathWave ADS(Advanced Design System) 2020 업데이트 1.0은 다음을 위해 솔루션과 기타 기능을 제공합니다.

- 고속 디지털(HSD) 설계

- 전자기(EM) 시뮬레이션

- 회로 시뮬레이션

- 전력 전자장치 설계

- 설계 및 기술 관리

- 설계 편집

PathWave ADS(Advanced Design System) 2020 업데이트 1.0을 지금 사용할 수 있습니다!

위 체험판 및 라이선스 탭을 클릭한 다음, 세부 정보 및 다운로드 버튼을 클릭해서 최신 소프트웨어를 다운로드하십시오.

Description

PathWave ADS(Advanced Design System) 2020 업데이트 1.0은 다음을 포함하여 까다로운 고속 디지털, RF 및 마이크로웨이브, 전력 전자장치 설계를 위해 솔루션과 기타 기능을 제공합니다.

PathWave ADS(Advanced Design System) 2020 업데이트 1.0은 다음을 포함하여 까다로운 고속 디지털, RF 및 마이크로웨이브, 전력 전자장치 설계를 위해 솔루션과 기타 기능을 제공합니다.

고속 디지털 설계

- DDR/메모리

- 메모리 설계자의 DDR5 지원

- IBIS-AMI 모델을 지원하는 혁신적인 시간축 시뮬레이션 모드. 싱글 엔드 신호를 위해 강화됨. 외부적 공급 클럭킹

- 쓰기 레벨링(지연 파일) 지원

- DBI(Data Bus Inversion) 지원

- 제3자 PCB 데이터를 위해 자동화된 신호 속성 할당

- 그룹 편집 지원. 메모리 설계자 설정 컨트롤러. 더 간편한 IBIS/모델 설정

- SIPro & PIPro

- SIPro와 PIPro-AC에서 포트 기생 감소를 통한 정확성 증가 Sheet Ports로 이동하고 PIPro의 핀을 분할해서 달성했습니다. 이는 인덕턴스가 지배적인 낮은 저항의 PDN에 특히 중요합니다.

- 이제 '메시-분할' 옵션을 통해 SIPro에서 병렬 시뮬레이션을 이용할 수 있습니다. 작업당 사용되는 스레드에 대한 제어를 통해 단수형 분석 설정이 여러 병렬 작업으로 분할되도록 허용합니다. 대형 워크스테이션이나 서버 팜에서 시뮬레이션 속도를 크게 높일 수 있습니다. 또는 솔루션이 문제를 해결하는 데 필요한 최대 메모리를 감소시키는 데 사용할 수 있습니다.

- PIPro AC 및 SIPro 분석은 시뮬레이션 시간을 개선하면서 모든 콤포넌트 모델 유형에 대해 업데이트할 수 없는(임베디드) 콤포넌트를 지원합니다.

- SIPro와 PIPro는 시뮬레이션에서 패시브 콤포넌트로 ADS 스케매틱 셀을 사용할 수 있습니다.

- 공통의 헐거운 구멍이 있는 비아를 통한 차동 라인의 SIPro 정확도 개선(예: 병합된 안티 패드)

EM 시뮬레이션

- RFPro

- RFPro 개방 또는 콤포넌트 역할 전환 시 속도 개선

- FEM 솔버는 이제 RFIC 플랫폼에서 지원되며 FBAR 필터 또는 웨이퍼 레벨 패키징을 위해 Momentum을 보완할 수 있습니다.

- 새로운 FEM 솔버 도입: Generation 2

- 전처리 시간의 극적 감소

- 메싱의 견고성 개선

- 정확한 접지 반환 경로를 유지하는 동안 망과 콤포넌트를 선택할 때 FEM이 시뮬레이션 공간을 자동으로 감소시키기 위한 새로운 메시 도메인 최적화 모드

- 암호화된 기판을 지원하는 FEM

회로 시뮬레이션

- 모델

- TMI 모델 지원

- BSIMSOI 모델을 위한 XL 지원

- 회로 Envelope

- Envelope EVM 시뮬레이션을 극적으로 가속화하기 위한 컴팩트 테스트 신호 도입

- Envelope의 컨볼루션은 주파수 종속 파일이 사용될 때 설정을 완화하는 데 사용할 수 있습니다.

- 전열

- 이제 전력이 [mW/uW/pW]로 명시되면 FloorPlanner 결과가 정확합니다.

전력 전자장치

- PEPro(Power Electronics Professional)

- 방사성 EMI를 PCB 레이아웃 후보의 사전 인증 테스트를 위한 주파수 및 각도에 비교하여 그리기 위한 새로운 테스트 벤치

- 더 나은 스펙트럼 정확도와 노이즈 레벨을 위해 개선된 전도성 EMI 결과 데이터 디스플레이

- PEPro 버그 해결. 예: 실행 취소 버튼에 텍스트 표시

- 설계 전환

- 입력 파일의 경로에 스페이스가 있었을 때 Windows 운영 체계에서 넷리스트 파일 가져오기가 실패한 경우 문제 해결

- 넷리스트 파일 가져오기 중에 생성된 NetlistInclude 콤포넌트의 IncludeFile 필드에 있는 파일 이름만 있지 않고 파일 경로가 파일 이름과 함께 사용되었을 경우 문제 해결

- LTspice 가져오기 버그 해결. 예: 시뮬레이터 예약어 고정

설계 및 기술 관리

- 일반 사항

- 라이브러리 이름 변경 중에 작업 공간을 바꿀 때 크래시 해결

- 인스턴스 파라미터 편집의 가능한 크래시 해결

- 설계 검색과 레퍼런스 표시의 가능한 크래시 해결

- Cadence에서 기본 라이브러리의 "패치" 콤포넌트 지원

- 레퍼런스/종속 요소 창 사이의 드래그/드롭 지원

- Data Display

- Data Display Expression Manager와 Expression Hierarchy 개선

- 데이터링크(Python 인터페이스)

설계 편집

- 인터커넥트의 라인 세그먼트에 대해 끝부분 또는 구석을 얻기 위해 AEL 펑션 추가

- 주어진 맥락에서 선택된 객체를 모두 회전시키기 위해 db_rotate_selected_objects() 펑션 추가

- 사용자가 무제한적 비아를 배치할 때 매크로 기록에서 사용하기 위해 AEL 펑션 추가

- 이제 라인 유형을 사용해서 트레이스(AEL 명령을 통해)를 그릴 수 있음

- tech_get_padstack_def_names() AEL 펑션 추가

- Keepout 정보를 추출하기 위해 AEL 펑션 추가

- 접지판 윤곽선 지점을 얻기 위해 AEL 펑션 추가

- PCB 비아 인스턴스의 이름, 템플릿 이름, 시작 정지 레이어를 통해 액세스하기 위해 AEL 펑션 추가

시작하기

ADS 2019 업데이트 1.0을 사용할 준비가 되셨습니까? 무료 체험판을 신청하십시오.