Choose a country or area to see content specific to your location

-

PRODUCTS AND SERVICES

-

Oscilloscopes

-

Analyzers

- Spectrum Analyzers (Signal Analyzers)

- Network Analyzers

- Logic Analyzers

- Protocol Analyzers and Exercisers

- Bit Error Ratio Testers

- Noise Figure Analyzers and Noise Sources

- High-Speed Digitizers and Multichannel DAQ Solutions

- AC Power Analyzers

- DC Power Analyzers

- Materials Test Equipment

- Device Current Waveform Analyzers

- Parameter / Device Analyzers and Curve Tracers

-

Meters

-

Generators, Sources, and Power Supplies

-

Software

-

Wireless

-

Modular Instruments

-

Network Test and Security

-

Network Visibility

-

Services

-

Additional Products

- All Products, Software, Services

-

- Learn

- Buy

- Support

What are you looking for?

Double Data Rate (DDR) Memory

Next-generation AI comes with various challenges for memory technology. Training of AI models requires extremely high-bandwidth memory, and low memory latency is needed for inference applications. To address growing model sizes, large and scalable memory capacity is a must.

Keysight has you covered with high-precision and ultra-fast solutions for every stage of your next DDR design - for data center, consumer electronics, automobiles, and other memory systems.

DDR Design-to-Test Solutions

Design Simulation

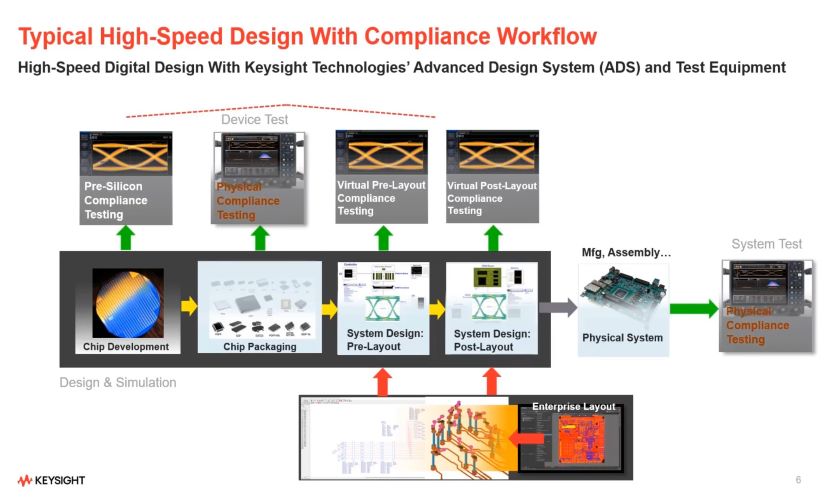

Faster networking speeds require faster memory. Each new version of the LPDDR / DDR standards supports faster access to data stored in memory. As the speed of double data rate technology increases, you face new design and validation challenges. Design and simulation of DDR memory systems help you discover issues before silicon tape-out and ensure good signal integrity of your designs. Design and simulation software enable you to optimize your transmitter, receiver, and channel designs for best performance and reliability at the desired speed grade. We can help you design upfront to resolve signal integrity issues, ensure power efficiency, and stay within tight error margins before the first prototypes.

Transmitter Compliance Testing

Ensuring interoperability of your DDR5 transmitter with other devices requires you to test it against JEDEC conformance standards. When testing your DDR5 devices, automate the calibration, setup, execution, and documentation of your compliance tests with purpose-built hardware and software. Ideally, use a high-bandwidth oscilloscope (25 GHz+) with a high effective number of bits, high-bandwidth probes designed for minimal effects on the measured signal, and interposer boards for probing as close to the silicon as possible. Couple this with software for test configuration, execution, evaluation, automation, and report generation.

Receiver Compliance Testing

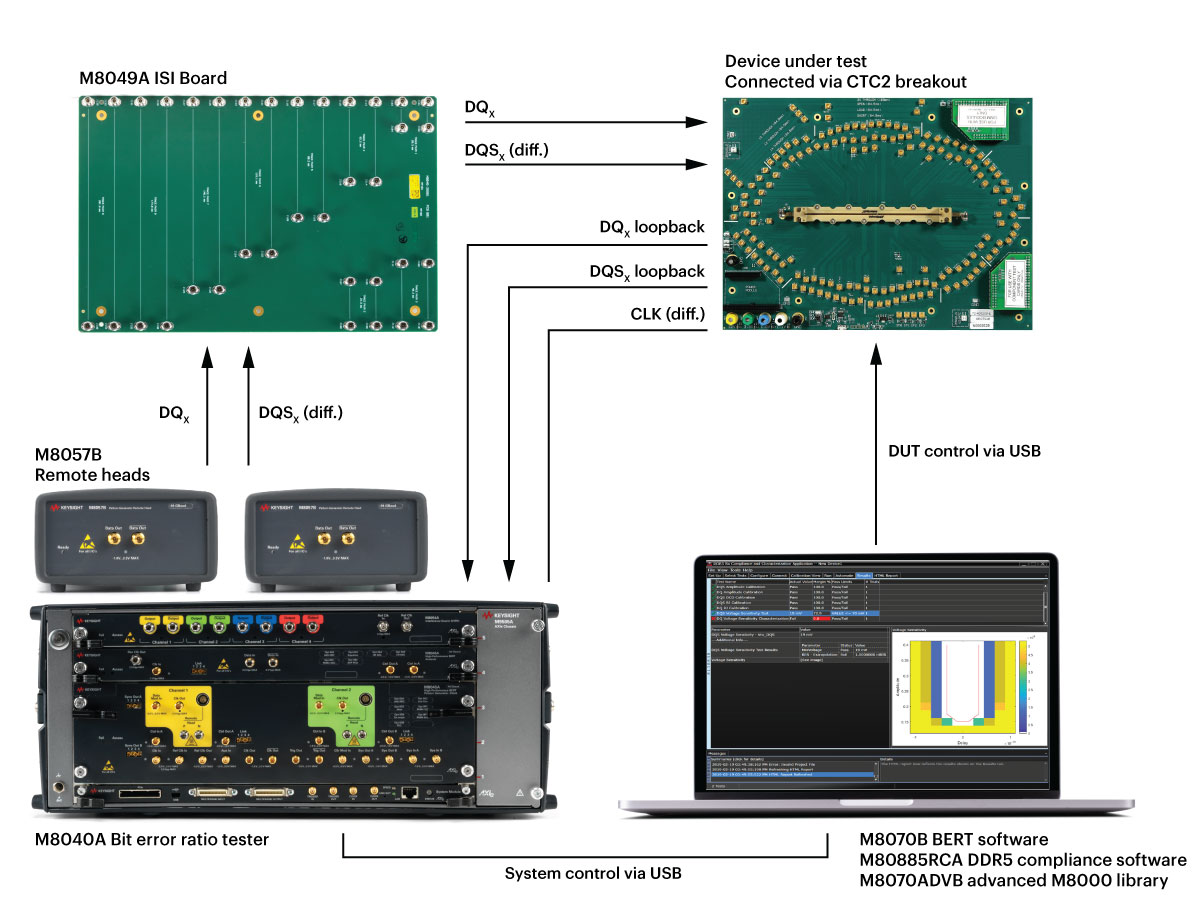

Ensuring compliance with the fifth generation of double data rate memory (DDR5) devices requires the performance of an exhaustive list of interoperability tests set forth by the JEDEC specifications. Physical layer receiver conformance testing involves characterization of the receiver, calibration of a stress signal using a high-bandwidth oscilloscope, and device receiver tests with a bit error ratio tester.

Protocol Validation

Data corruption is a common symptom encountered during validation of LPDDR / DDR designs. The root cause of data corruption can be difficult to determine. Usually, there are either signal integrity or functional issues with your designs.

When DDR memory systems do not behave as expected, you need functional debug, analysis, and protocol compliance validation solutions that provide trace capture and analysis capabilities. We can provide you the insight needed to understand your system’s behavior and quickly find the root cause of any issues.

Further Reading

Want help or have questions?

- © Keysight Technologies 2000–2024

- Privacy

- Sitemap

- Terms

- Trademark Acknowledgements

- Feedback

- Accessibility