What are you looking for?

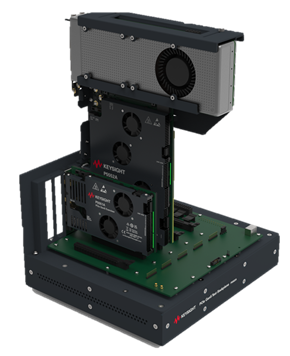

P5573A PCIe 6.0 Protocol Exerciser

Keysight P5573A PCIe 6.0 Protocol Exerciser gives the flexibility in providing realistic traffic to devices under test and also able to emulate as a complex host system

Starting from

Highlights

See the Real Performance of Your Design

The foundation of the P5573A is the improved signal integrity provided through the integrated design of the Exerciser card which provides a solid, trustworthy test platform. This compact design allows Keysight engineers great versatility in ensuring that the P5573A would have signal integrity characteristics that could be configurable enough to be tuned for many different test environments, while also offering quick link up capability for test cases that focus on higher layer protocol debugging. The P5573A is designed to be easy to setup, connect, and be quickly configured to bring up the PCIe link and check basic LTSSM and protocol functionality. To support this the P5573A has many features included that allow for quick validation of fundamental PCIe features.

- Support up to 64GT/s with x4, x8 and x16 physical lane width options

- Automated Link training with skip and bypass support

- Traffic generation with lane reversal and polarity detection

- Scalable flow control support

- Link training and LTSSM control

- Real Time Equalization

- Transactional Layer Generation

- Error Insertion

- Complete RAS test protocol solution

Key Specifications

Customized PCIe Traffic Generation

With PCIe Exerciser mode, customizable Configuration Reads and Writes, I/O Reads and Writes, Memory Reads and Writes, Messages, and specific Completion types are possible. Templates for each command type are provided in order to create test cases quickly. The Traffic Setup interface in the P5573A allows I/O workloads and payloads to be created to simulate different conditions for the DUT and perform Performance Characterization.

P5573A PCIe 6.0 Protocol Exerciser Single Add-in-card Simplifies Connection and Setup

Keysight P5573A PCIe 6.0 Protocol Exerciser creates a test and validation environment, a powerful tool for vetting and debugging PCIe designs. The single add-in-card simplifies connection and setup of the tool while offering improved signal integrity when comparing to other architectures. With the option of RAS (Reliability, Accessibility and Serviceability) testing capability, gives the user full control in emulating different error scenarios to test the performance of their system or system under test.

- Supports 2.5 GT/s through 64 GT/s

- CEM connection with x4, x8 and x16 physical lane width support

- LTSSM Tester

- Link and Lane configuration

- Replay function

- Equalization and Transceiver configuration

- Skip configuration

- Customized traffic generation

- Power Management

- Automation API

- Auto Equalization

- Bifurcation

- SRIOV Virtualization

- RAS testing

- Liquid cooled for excellent heat dissipation to maintain overall performance and reduce over-loading on a CEM card form factor

Interested in a P5573A PCIe 6.0 Protocol Exerciser?

Extend the Capabilities of Your P5573A PCIe 6.0 Protocol Exerciser

Featured Resources

Want help or have questions?