這是我們認為您想查看的頁面.

觀看搜尋結果:

Choose a country or area to see content specific to your location

- Home

- 產品與服務

- ...

- EDA 軟體

- PathWave 先進設計系統

- W2320EP 進階布局元件 [Discontinued]

- 產品概述與特色

- 採購後升級選項

- 資源

HIGHLIGHTS

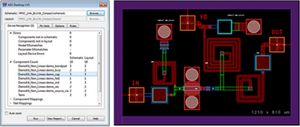

先進設計系統(ADS)先進布局元件:

- 電路布局驗證(LVS)

- 設計規則檢查(DRC)

- DRC 與 LVS 第三方工具

- 製造網格

- 矽晶虛擬金屬填充工具程式

先進設計系統(ADS)W2320EP 進階布局元件讓您能在布局驗證、製造網格、矽晶 RFIC 工具中使用更多的 ADS 布局功能。

先進設計系統(ADS)W2320EP 進階布局元件讓您能在布局驗證、製造網格、矽晶 RFIC 工具中使用更多的 ADS 布局功能。

電路布局驗證(LVS)

- ADS 模組 LVS

o 為多重技術模組設計進行 LVS

o 模組設計功能包含使用面積圖釘標註 IC 尺寸,或是使用銲墊元件象徵內嵌的 IC

o 檢查模組層級的連接性,以及 IC 中的焊線與銲墊間的連接性。 - ADS 元件識別 LVS

o 規則導向的 IC 設計 LVS - ADS 實體 LVS

o 為 IC 與射頻電路板設計的布局實體連接進行 LVS

o 使用元件面狀接腳和層接合來建構實體線網。在建構實體線網時,檢察傳導層的圖形細節以提供準確的短路偵測。 - ADS Pin Nets LVS

o 可輕鬆地排除 LVS 錯誤

o 執行 Pin Nets LVS 可確認每項子設計是否為「LVS clean」

o 使用階層化檢視瀏覽設計,並檢測每一階層對映的元件 - 使用電路圖的布局線網名稱

o 使用「電路圖差異」子視窗,將線網名稱從電路圖套用進布局中

o 在 Navigator 和 LVS 報告中顯示布局線網名稱,可輕鬆識別、標示重要線網

設計規則檢查(DRC)

- 對 IC、模組、射頻電路板設計進行 DRC。

- 當布局視窗保持開啟時,可選擇規則類別以單獨執行該類別的檢查,或以背景作業的 DRC執行全套規則。

- ADS DRC 在本機上執行,可保證您的資料安全

DRC 與 LVS 第三方工具

- 執行 DRC 和 LVS 第三方工具,並在布局視窗標記錯誤。

- 將第三方 DRC 結果匯入 DRC 對話框

製造網格

- 識別偏離網格的布局物件,並以手動覆寫,快速將其校正到製造網格上

矽晶 RFIC 工具程式

- 為矽晶 RFIC 產生虛擬金屬填充。

- 檢查設計符合目標所需的金屬密度。

- 在設計程序前期,以 Momentum 驗證設計中的金屬填充效應

排序依據 :

日期

日期

標題

Filter Results

找不到此產品的相關資訊

重新填寫

依內容類型