Choose a country or area to see content specific to your location

Que recherchez-vous ?

-

-

Concepteur d'interconnexions 3D

3D Interconnect Designer offre un environnement de modélisation et d'optimisation flexible pour toute structure d'interconnexion avancée, y compris les chiplets, les puces empilées, les boîtiers et les circuits imprimés.

-

Économisez jusqu'à 50 % sur un oscilloscope XR8

Bénéficiez d'une validation numérique plus rapide à moindre coût grâce à une reprise.

-

Découvrez Keysight AI Data Center Builder

Émulez chaque composant de votre infrastructure de centre de données. Émulez tout. Optimisez tout.

-

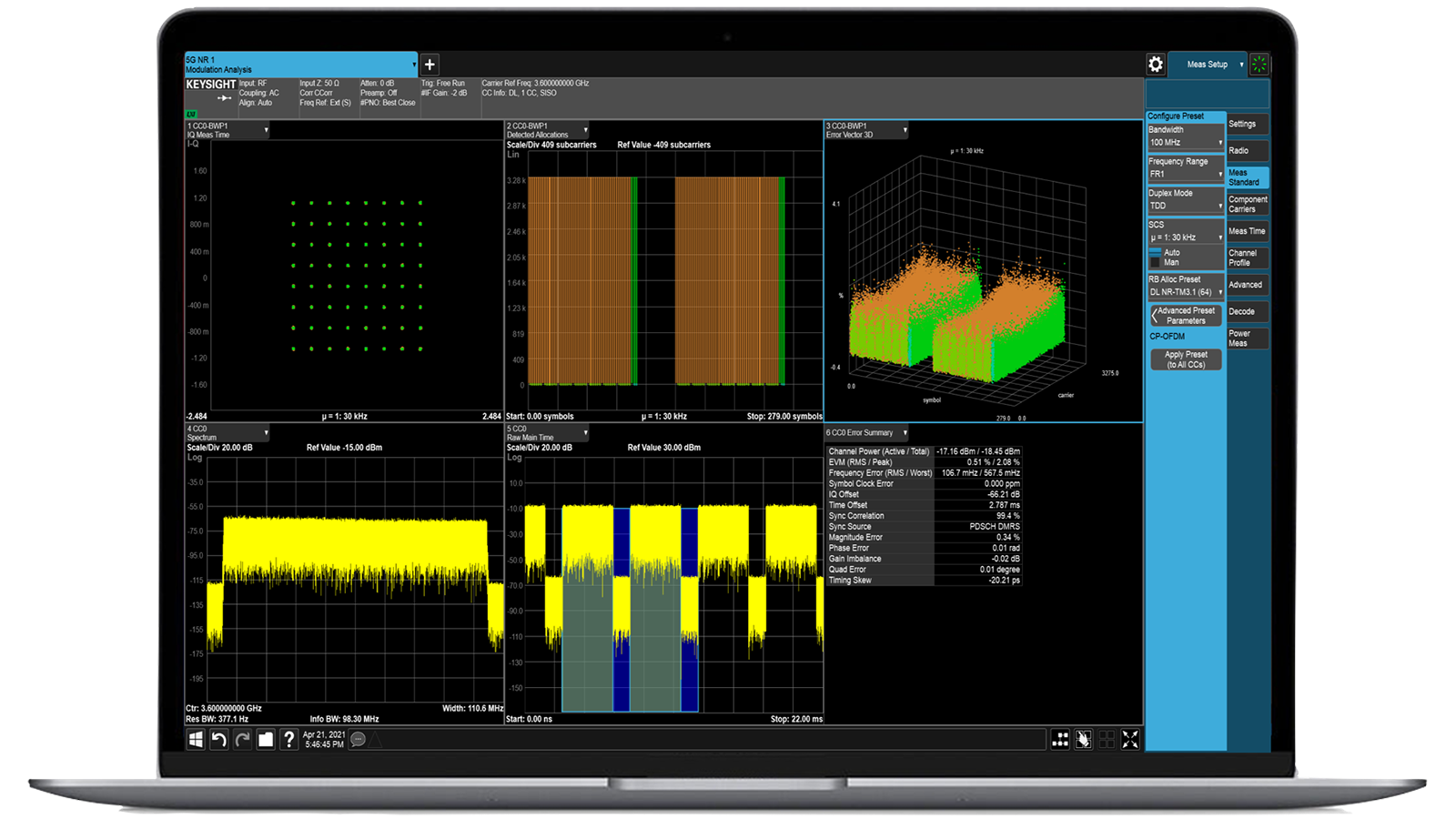

Accélérez l'analyse des signaux grâce aux applications de mesure de la série X

Utilisez plus de 25 applications de la série X pour analyser, démoduler et dépanner des signaux dans les domaines des communications sans fil, de l'aérospatiale et de la défense, des interférences électromagnétiques (EMI) et du bruit de phase.

-

Présentation des courtiers en paquets améliorés par l'IA

Grâce à leur mémoire et leur capacité de stockage supplémentaires, ces NPB améliorés exécutent le logiciel de sécurité et de surveillance des performances IA de Keysight, ainsi que la pile IA.

-

Test en circuit de précision pour la production

Réalisez des tests rapides et précis au niveau des cartes grâce à une ICT en ligne et hors ligne robuste, conçue pour la fabrication moderne.

-

Accélérez votre moteur d'innovation

Découvrez des plans d'assistance personnalisés, dont la priorité est de vous permettre d'innover rapidement.

-

Génération de formes d'onde à 448 Gb/s

Réaliser des signaux modulés à plusieurs niveaux de 200+ Gbaud avec des AWG à grande vitesse pour les normes numériques et optiques.

-

Transmettez des données I/Q à 120 MHz vers votre ordinateur portable sur le terrainLocalisez précisément les interférences à l'aide d'un logiciel de gestion du spectre post-traitement en laboratoire.

Trouvez la solution d'alimentation ATE qui vous convient

Trouvez la solution d'alimentation ATE qui vous convientUtilisez cet outil de sélection pour identifier rapidement l'alimentation électrique la mieux adaptée à vos besoins en matière d'équipements de test automatique (ATE) dans les secteurs de l'aérospatiale et de la défense.

-

- Solutions

-

Explorez les contenus rédigés par des ingénieurs et une vaste base de connaissances offrant des milliers de possibilités d'apprentissage.

Keysight Learn offre un contenu immersif sur des sujets d'intérêt, y compris des solutions, des blogs, des événements et plus encore.

Mon tableau de bord LearnPoursuivre. Découvrir. Personnaliser.

Le tout en un seul endroit. - Acheter

-

Accès rapide aux tâches d'auto-assistance liées au soutien.

Contenu supplémentaire pour répondre à vos besoins en matière de produits.

Faites-en plus avec les services KeysightDécouvrez les services permettant d'accélérer chaque étape de votre parcours d'innovation.

Testeur de structures électriques Contrôle non destructif des structures électriques pour les liaisons par fil

Détecter avec précision les défauts subtils au niveau des liaisons filaires

- Vue d'ensemble

- Tous les modèles

- Accessoires

- Logiciel

- Soutien

Contrôle non destructif des structures électriques des soudures par fil

Le testeur de structure électrique Keysight s8050 est une solution de test non destructive basée sur la technologie capacitive, conçue pour détecter les défauts de soudure des fils dans les boîtiers de circuits intégrés (CI). Grâce à la technologie nanoVTEP (nano Vectorless Test Enhanced Performance) et à la méthode PAT (Part Average Testing), le s8050 identifie les défauts structurels subtils sans mettre sous tension le dispositif testé. Il est couramment utilisé dans les processus d'assemblage de circuits intégrés après moulage pour vérifier l'intégrité des soudures avant le test final, aidant ainsi les fabricants à réduire les défauts non détectés, à minimiser les retouches et à améliorer le rendement global. Demandez un devis ou commandez dès aujourd'hui l'une de nos configurations les plus populaires. Besoin d'aide pour choisir ? Consultez les ressources ci-dessous.

Parallélisme élevé et architecture évolutive

Prend en charge jusqu'à 20 sites de test en parallèle grâce à l'utilisation de plusieurs cartes de conditionnement VAM+ et nanoVTEP. Cette conception évolutive permet une extension flexible du système tout en offrant un débit de test élevé pouvant atteindre 72 000 unités par heure.

Détection des défauts subtils au niveau des liaisons par fil

Détecte un large éventail de défauts de soudure par fil, notamment les quasi-courts-circuits, les fils parasites, le balayage des fils et l'affaissement des fils. Permet la détection précoce de problèmes latents susceptibles d'affecter le rendement en aval et la fiabilité à long terme.

Contrôle non destructif

Évalue la présence et l'orientation des fils de connexion à l'aide de la technologie de détection capacitive nanoVTEP, qui utilise des stimuli électriques de faible intensité. Cette approche évite toute contrainte physique ou électrique sur le dispositif sous test (DUT), ce qui la rend idéale pour l'assemblage de circuits intégrés après moulage.

Détection des écarts à l'aide de la méthode PAT (Part Average Testing)

Utilise la PAT dynamique pour les tests sur bandes et la PAT en temps réel pour les dispositifs individuels afin de garantir la précision des valeurs de référence. Les limites adaptatives réduisent les rejets injustifiés, minimisent les rebuts et diminuent les besoins de retests.

-

System width

700 mm to 1,430 mm

-

Maximum parallel testing

4 to 20 sites

-

Test types

Single Die Wire-Bonded Packages

Configurations courantes

Testeur de structures électriques

Testeur de structures électriques

Q3800A

Découvrez une solution de contrôle capacitif non destructif qui permet d'identifier avec précision les défauts dans les microélectroniques liées par des fils.

Solutions innovantes pour la détection des défauts de soudure par fil

Le testeur de structure électrique Keysight est une solution de test capacitive conçue pour détecter avec précision les défauts de soudure des fils. Grâce à l'analyse avancée de la moyenne des composants (PAT), le testeur établit une référence à partir d'unités dont la conformité est avérée afin de détecter rapidement les anomalies telles que les quasi-courts-circuits, les fils errants, les déviations de fils et les affaissements au sein des circuits intégrés (CI). Cette fonctionnalité garantit une gestion rigoureuse de la qualité des produits et améliore considérablement l'efficacité de la production. Le testeur de structure électrique vous permet de :

- Tester des boîtiers à puce unique avec connexion par fil, sous forme de puces individuelles ou en bande.

- Assurez une production à haut débit grâce à un maximum de 20 postes de test en parallèle, pour atteindre jusqu'à 72 000 circuits intégrés par heure (UPH).

- Améliorez le rendement grâce à des méthodes avancées telles que le test de réessai marginal (MaRT), le test de moyennage dynamique des pièces (DPAT) et le test de moyennage en temps réel des pièces (RPAT).

livre blanc

Étude de cas

étude de cas

étude de cas

Services et assistance

Innovez rapidement grâce à des plans d'assistance personnalisés et à des délais de réponse et d'exécution prioritaires.

Bénéficiez d'abonnements prévisibles basés sur un contrat de location et de solutions de gestion du cycle de vie complet afin d'atteindre plus rapidement vos objectifs commerciaux.

Bénéficiez d'un service haut de gamme en tant qu'abonné KeysightCare pour obtenir une assistance technique dédiée et bien plus encore.

Assurez-vous que votre système de test fonctionne conformément aux spécifications et respecte les normes locales et internationales.

Effectuez rapidement des mesures grâce à des formations internes dispensées par des instructeurs et à l'apprentissage en ligne.

Téléchargez le logiciel Keysight ou mettez à jour votre logiciel vers la dernière version.

Questions fréquemment posées

Un testeur de structure électrique (EST) évalue l'intégrité physique des connexions internes, telles que les liaisons filaires à l'intérieur d'un boîtier de circuit intégré, sans ouvrir ni endommager le dispositif. Grâce à la détection capacitive, il détecte les variations structurelles qui, bien qu'elles n'affectent pas immédiatement le fonctionnement, peuvent entraîner une perte de rendement ou des problèmes de fiabilité à long terme.

Le s8050 détecte un large éventail de défauts de soudure par fil, notamment les quasi-courts-circuits, les fils errants ou mal alignés, le balayage des fils et l'affaissement des fils. Ces défauts subtils échappent souvent à l'inspection visuelle ou aux tests fonctionnels, mais peuvent entraîner des défaillances latentes s'ils ne sont pas détectés à un stade précoce.

Le s8050 permet de réaliser des tests à haut débit grâce à une capacité multi-sites évolutive pouvant aller jusqu'à 20 sites en parallèle. Contrairement aux méthodes d'inspection traditionnelles basées sur l'échantillonnage, il permet aux fabricants de contrôler efficacement un pourcentage bien plus élevé de dispositifs, améliorant ainsi la qualité des produits sortants tout en maintenant la cadence de production.

Les systèmes d'inspection visuelle et par rayons X reposent sur l'imagerie et sont souvent utilisés sur la base d'échantillonnages, ce qui peut faire passer inaperçus des défauts subtils ou à un stade précoce. Le s8050 utilise une détection électrique combinée à la méthode PAT (Part Average Testing) pour établir des valeurs de référence à partir d'unités dont la conformité est avérée et détecter de légers écarts structurels sur l'ensemble des appareils testés. Cela permet une détection plus cohérente des défauts et réduit le risque de défauts non détectés dans la production à grand volume.

Oui. Le S8050 utilise une détection capacitive de bas niveau qui n'exerce aucune contrainte physique ou électrique sur le dispositif sous test (DUT). Cela garantit que les dispositifs restent intacts et aptes à subir des tests en aval, à être intégrés dans un système ou à être expédiés.

Le modèle s8050 est optimisé pour les boîtiers de circuits intégrés à puce unique assemblés par câblage, tels que les QFP et autres formats similaires à grille de connexion. Sa technologie nanoVTEP est spécialement conçue pour assurer une détection hautement sensible de l'intégrité structurelle des câbles de connexion dans ces types de boîtiers, où un dépistage précis des défauts est essentiel pour garantir la qualité et la fiabilité.

Le modèle S8050 est généralement utilisé après le conditionnement des circuits intégrés (post-moulage) dans les processus d'assemblage et de test des semi-conducteurs. Il complète les inspections et les tests fonctionnels en détectant les défauts structurels avant le test final ou l'expédition, ce qui améliore la qualité globale du produit.