What are you looking for?

HeatWave Technical Papers

Below are links to various technical papers related to HeatWave Electro-Thermal analysis software.

Large ΔT at transistor scale is validated by thermography

Source: University of Bristol, U.K.

Figure 1. Temperature line scan through the center of the active region of an AlGaN/GaN HFET (source-drain gap of 4.8 µm, 1.2 µm long gate, 50 µm wide device) on SiC, operated at 1 W, recorded using Raman and IR thermography. For comparison results of a three dimensional finite difference thermal simulation are shown.

Figure 4. Time-evolution of device peak temperature in the center of an AlGaN/GaN ungated device on SiC (15 µm contact separation, 150 µm wide device), operated with 2 µs long square drain pulses (5.3W) at a 50% duty cycle. Simulation results are also shown.

M. Kuball, J. W. Pomeroy, R. Simms, G. J. Riedel, H.F. Ji, A. Sarua, M. J. Uren, T. Martin, “Thermal Properties and Reliability of GaN Microelectronics: Sub-Micron Spatial and Nanosecond Time Resolution Thermography”, 2007 IEEE Compound Semiconductor IC Symposium, October 2007

READ THE ARTICLE on IEEE Xplore.

Fine-grain ΔT - in space and time

Source: IBM Yorktown Heights Research Center

Figure 3.

- ΔT » 96°C above 25°C ambient

- τth » 107ns thermal time constant

- nFET, 110-nm PD-SOI floating-body, at Vd=1.8V

Figure 4.

- ΔT » 57°C above 25°C ambient

- τth » 62ns thermal time constant

- nFET, 110-nm strained silicon, at Vd=1.8V

S. Polonsky & K. A. Jenkins, “Time-Resolved Measurements of Self-Heating in SOI and Strained-Silicon MOSFETs Using Photon Emission Microscopy”, IEEE Electron Device Letters, Vol. 25, No. 4, April 2004

READ THE ARTICLE on IEEE Xplore.

Practical Chip-centric Electro-thermal Simulations

Source: ON Semiconductor

- Full-chip dynamic electro-thermal simulation achieved by coupling circuit simulator and thermal solver

- In all cases simulation results agree well with measured data

Figure 10. Measured and simulated thermal impulse response. Note the last data-point measured separately at 1000 s.

R. Gillon, P. Joris, H. Oprins, B. Vandevelde, A. Srinivasan, R. Chandra, “Practical chip-centric electro-thermal simulations”, THERMINIC, 24-26 September 2008, Rome, Italy

READ THE ARTICLE on IEEE Xplore.

Junction-level Thermal Extraction and Simulation of 3DICs

Source: North Carolina State University

- Low resolution simulations obscure the hotspots

- High resolution thermal analysis, coupled with accurate power and layout data, captures hotspots in the thermal profile

Figure 8. A close-up of the analysis of the 3D SAR with Gradient FireBolt, showing the level of detail that is provided by a high resolution simulation. The region shown is on the middle tier (tier B). The tentpoles caused by clock buffers and the effects of wires are clearly seen at this resolution.

S. Melamed, T. Thorolfsson, A. Srinivasan, E. Cheng, P. Franzon & R. Davis, “Junction-level Thermal Extraction and Simulation of 3DICs”, IEEE 3DIC Conference, Sep. 2009

READ THE ARTICLE on IEEE Xplore.

T. Thorolfsson, S. Melamed, R. Davis, and P. Franzon, “Low-Power Hypercube Divided Memory FFT Engine Using 3D Integration”, ACM Transactions on Design Automation of Electronic Systems, Nov. 2010

READ THE ARTICLE on IEEE Xplore.

Fine Grain Thermal Modeling of 3D Stacked Structures

Source: IMEC, Belgium

- Detailed methodology for thermal analysis of stacked die packages

- Measurements are well matched by a thermal simulation, which computes heat transport through the full-chip layout, including TSVs

Figure 6. Schematic representation of the materials in the die stack (not to scale), including the BEOL structure of the top and bottom die.

H. Oprins, M. Cupak, G. Van der Plas, P. Marchal, B. Vandevelde, A. Srinivasan, E. Cheng, “Fine Grain Thermal Modeling of 3D Stacked Structures”, THERMINIC, 7-9 October 2009, Leuven, Belgium

READ THE ARTICLE on IEEE Xplore.

THERMINATOR Project Warms Efforts to Cool Semiconductors

Source: STMicroelectronics

- THERMINATOR - Modeling, Control and Management of Thermal Effects in Electronic Circuits of the Future

- This 3-year project is designed to maintain the strong positions that Europe’s semiconductor and electronics equipment companies have achieved in highly competitive application areas such as automotive systems and factory automation where the semiconductor devices are often required to work under harsh conditions with temperatures in excess of 100 degrees Celsius

THERMINATOR Project Warms Efforts to Cool Semiconductors

READ THE PRESS RELEASE on the Cision PR Newswire website.

Electro-thermal modeling/characterization of large lateral PNP drivers

Source: ON Semiconductor

- Temperatures at two discrete points were measured by sensors located in the field of the drivers. Transient Interferometric Mapping (TIM) produced temperature map of the chip at 10µm/pixel spatial resolution by scanning an infrared laser probe beam to the chip backside.

- Segmented according to temperature variations, the power transistor underwent electro-thermal modeling and simulation; the non-uniform current density profile and the thermal profile of the large power driver agree well with measured data.

Figure 9. (a) Top view layout of the driver, (b) and (c) show simulated maximal temperature distributions in 2D and along a central axis respectively.

J. Rhayem, A. Vrbicky, R. Blecic, P. Malena, S. Bychikhin, D. Pogany, A. Wieers, A. Baric, M. Tack, "New methodology on electro-thermal characterization and modeling of large power drivers using lateral PNP BJTs", EuroSimE, 26-28 April 2010, Bordeaux, France

READ THE ARTICLE on IEEE Xplore.

A Practical Approach to Thermal Modeling and Validation of 3D ICs

Source: IMEC, Belgium

- This article presents a practical approach to perform detailed thermal analysis of stacked-die packages, interconnections between the dies, and the complete electrical design layout.

- The methodology is demonstrated on a two stacked die structure in a BGA package.

Figure 8. Comparison of the simulation results (red dots) with the experimental temperature measurements (blue dots and error bars) for a 100x100 µm2 meander heater.

M. Cupak, H. Oprins, G. Van der Plas, P. Marchal, B. Vandevelde, A. Srinivasan, and E. Cheng, “A Practical Approach to Thermal Modeling and Validation of 3D ICs”, Design Automation Conference - User Track paper 4U.5S, 13-15 June 2010

READ THE ARTICLE on the Penn State University website.

H. Oprins, A. Srinivasan, M. Cupak, V. Cherman, C. Torregiani, M. Stucchi, G. Van der Plas, P. Marchal, B. Vandevelde, and E. Cheng, “Fine grain thermal modeling and experimental validation of 3D-ICs”, Microelectronics Journal, Vol. 42, Issue 4, April 2011, pp. 572-578.

READ THE ARTICLE on ScienceDirect website.

Improve Thermal Profile of Memory-on-Logic 3DICs by Tier-swapping

Source: North Carolina State University

Temperature in the 1024-point, memory-on-logic 3DIC FFT processor for synthetic aperture radar (SAR) was simulated with 80 nm spatial resolution, and was modeled to include the effect of each line of interconnect, as well as each via and fill structure exactly as drawn in the layout. Large isolated temperature spikes were found near groups of clock buffers at the edge of the SRAMs on the middle tier.

By reordering the stackup of memory and logic tiers, it was found that placing the memory tier closer to the heatsink improved not only the thermal profile of the memories but also of the logic tiers. Temperature spikes in the memories no longer significantly impacted the logic tiers, yielding a design where the thermal profile of the tiers were significantly less dependent on each other.

S. Melamed, T. Thorolfsson, A. Srinivasan, E. Cheng, P. Franzon, R. Davis, “Investigation of Tier-swapping to Improve the Thermal Profile of Memory-on-Logic 3DICs”, THERMINIC Workshop, 6-8 October 2010, Barcelona, Spain

READ THE ARTICLE on IEEE Xplore.

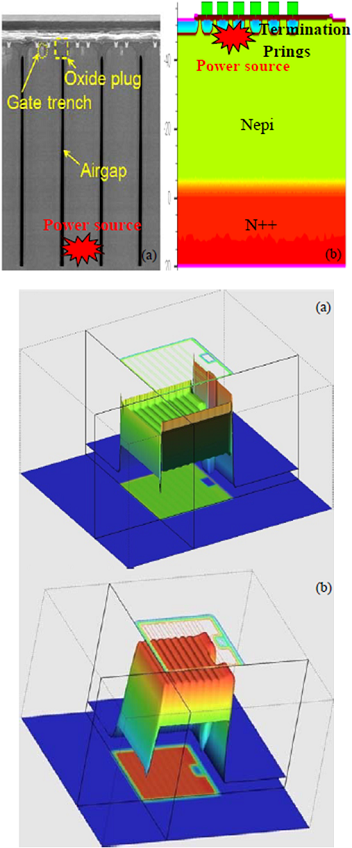

Electro-thermal modeling of multi-trenched MOS power transistors

Source: ON Semiconductor

- A thermal model of a multi-trenched vertical MOS power transistor is constructed from transient interferometric mapping (TIM) data. Temperature variation along the width of each gate is modeled by splitting the gate into segments.

- Transient electro-thermal simulation at the length-scales of the segmented gates of the power-transistor is performed. Simulation results agree very well with measured data. The transient simulation is used to quantify the thermal effects of oxide in gate-trenches at various powers.

Figure 7. Results of the electro-thermal simulation that models the gate and isolation trenches. These snapshots are taken at 100ms and the power is 1.2 Watts.

Figure 8. Simulation shows the significant effect of oxide in gate-trenches at higher powers.

J. Rhayem, B. Besbes, R. Blecic, S. Bychikhin, G. Haberfehlner, D. Pogany, B. Desoete, R. Gillon, A. Wieers, M. Tack, “Electro-Thermal Characterization and Simulation of Integrated Multi Trenched XtreMOS Power Devices”, THERMINIC Workshop, 6-8 October 2010, Barcelona, Spain

READ THE ARTICLE on IEEE Xplore.

Thermal-aware reliability analysis of nanometer designs

Source: Advanced Micro Devices

- This 3D static thermal analysis flow demonstrates the need to compute temperature at the resolution-level of interconnect metal, via resistors and device fingers, and was used to verify reliability constraints on successive iterations of nanometer-level designs.

- The results obtained using the discussed methodology was compared against alternative approaches to better understand the importance of 3D thermal analysis.

An example full-custom block designed in 45-nm technology is analyzed. The design has close to 800,000 transistors and 150,000 CCRs, and operates on flat, transistor-level extracted data. The total number of power-generating elements, including device and interconnect, is about 4.5 million. Utilizing 30 parallel CPUs, the maximum run time was 8 hours, which included the full 3D thermal simulation.

Figure 4 shows the thermal map of the example block (E). It was simulated in context to the entire core and cache both kept at an uniform power density. They can also be given different power patterns. Power for the E block is spread across the entire GDS, including various metal layers, whereas it is applied on the active region for the rest of the core and cache. The hot spots seen in Figure 4 can be traced back to a single via, metal, or a device.

S. Krishnamoorthy, V. Venkatraman, Y. Apanovich, T. Burd, A. Daga, “Thermal-Aware Reliability Analysis of Nanometer Designs”, 2010 IEEE 19th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), 25-27 October, 2010, Austin, Texas

READ THE ARTICLE on IEEE Xplore.

Switching constraint-driven thermal & reliability analysis of nm designs

Source: Advanced Micro Devices

- This paper presents a true three-dimensional thermal analysis in order to accurately transform power dissipation into a temperature profile for more accurate reliability estimation at the level of interconnect metal, via resistors and device fingers.

- This enhancement to prior electromigration analysis flows was a critical enabling technology for deep sub-micron microprocessor design, and will prove only more essential as process technology continues to shrink, and electromigration constraints become ever more restrictive.

- In addition, the thermal analysis enabled better prediction of device reliability, which we can now calculate and measure the impact of, at the block-level.

Figure 7 shows the error in the estimation of interconnect temperatures by the 3D thermal methodology. It can be seen that the maximum error is only about 1°C.

The hot spots seen in Figure 8 can be traced back to a single via, metal, or a device as shown in the zoomed region.

S. Krishnamoorthy, V. Venkatraman, Y. Apanovich, T. Burd, A. Daga, “Switching Constraint-driven Thermal and Reliability Analysis of Nanometer Designs”, International Symposium on Quality Electronic Design, 14-16 March 2011, Santa Clara, California

READ THE ARTICLE on IEEE Xplore.

Robustness Optimization of Power MOSFETs under Inductive Breakdown

Source: ON Semiconductor

The avalanche breakdown of a multi-trenched vertical MOS power transistor is modeled including layout details, and electro-thermally simulated over time.

Figure 1a. Power dissipation in the core device comprising gate trenches, air-gaps and oxide plugs.

Figure 1b. Power dissipation in the termination rings near the semiconductor surface.

Most existing thermal simulation techniques are inadequate, because:

- Breakdown power is dissipated in volumes with significant thickness that are near both the top and the bottom of the vertical transistor. Many thermal simulators model power-dissipating regions in only two dimensions.

- The initial power values during breakdown exceed 7KW. Most thermal simulators cannot converge simulating such high powers, especially at sub-micron length scales.

- Microscale layout features include air-gaps, gate-trenches, and oxide plugs that most thermal simulators cannot model in detail, particularly in a full-chip context.

- These obstacles are overcome, resulting in an accurate electro-thermal simulation of avalanche breakdown. Electro-thermal simulation results agree well with transient temperatures measured with IR thermography, and with measured breakdown-voltage waveforms. Simulation produces the locations and times at which peak temperatures occur, which are very difficult to measure.

Figure 6a. Surface plot of temperature in the termination rings at 25µs.

Figure 6b. Surface plot of temperature in the core device at 80µs.

J. Rhayem, A. Wieers, A. Vrbicky, P. Moens, A. Villamor-Baliarda, J. Roig, P. Vanmeerbeek, A. Irace, M. Riccio, M. Tack, “Novel 3D Electro-Thermal Robustness Optimization Approach of Super Junction Power MOSFETs under Unclamped Inductive Switching”, SEMI-THERM, 20 March 2012, San Jose, California

READ THE ARTICLE on IEEE Xplore.

Learn more about PathWave Thermal Design (HeatWave) Electro-Thermal Analysis Software.