Choose a country or area to see content specific to your location

- Keysight.Home

- リソース

- リソース

何をお探しですか?

関連キーワード

No product matches found - System Exception

検索結果

PathWave Advanced Design System(ADS)のメモリデザイナー

PathWave ADS 2019アップデート1.0には、高速デジタル(HSD)デザインおよびシミュレーションのための魅力的な新製品が含まれています。

PathWave ADS 2019アップデート1.0には、高速デジタル(HSD)デザインおよびシミュレーションのための魅力的な新製品が含まれています。

PathWave ADSメモリ・デザイナー・バンドル

メモリシステムを設計するハードウェアデザイナーは、タイミングと電圧のマージン縮小に対処するとともに、動作の信頼性を検証するためにいくつもの複雑なコンプライアンス測定を実行する必要があります。DDR4以降への移行に伴い、ランダムジッタの重要性が大幅に増し、デザイナーはきわめて低いビット・エラー・レート(BER)でレシーバー・マスク・テストに合格することを要求されるようになっています。キーサイトの新しいPathWave ADSメモリ・デザイナー・ワークフローを使えば、セットアップ、電磁界モデルの抽出、バスのシミュレーション、コンプライアンステストの実行に必要なエンジニアリングの労力を最小化できます。シミュレーションとハードウェア検証の両方のステージで同じ測定技術を使用できる独自の機能により、シミュレーションと測定の比較が容易になります。

予測可能、高い生産性、優れた理解。

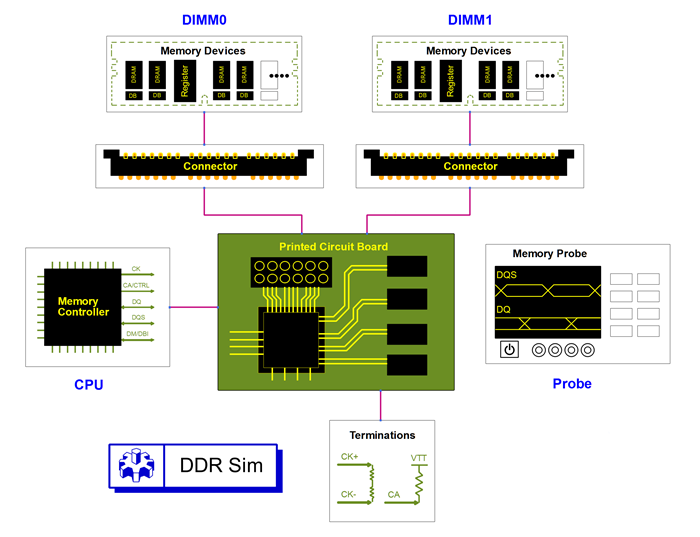

図1. PathWave ADS 2019アップデート1.0のメモリデザイナー

主な特長

- 新しいスケマティックコンポーネントによる、コントローラー、PCB、コネクタ、終端、メモリの容易なセットアップ

- IBISファイルをデバイス単位で適用することで、信号グループの設定のセットアップとパラメータ指定を高速化

- レイアウトデザインで見つかった信号IDを使用した自動配線接続

- シグナルインテグリティーを評価するDDRバスシミュレータにより、マスクテストのマージンを把握してきわめて低いBERを実現

- 新しいメモリプローブにより、グループ単位で測定をセットアップし、信号基準をインテリジェントに選択

- 新しいストローブ・アイ・ダイアグラムとスキュー測定

- 業界で定評のあるキーサイトのDDR4測定技術を使用した自動DDR4コンプライアンス・テスト・スイートおよびレポート作成

| モデル番号 | 概要 |

|---|---|

| W2225BP/BT | PathWave ADSメモリ・デザイナー・バンドル |

| W2393EP/ET | メモリ・デザイナー・エレメント |

高速デジタル・デザイン・フローの詳細を見る。