What are you looking for?

B4661A Memory Analysis Software for Logic Analyzers

Achieve greater insight faster using the B4661A memory analysis software and your Keysight logic analyzer system for debug and validation of DDR3, DDR4, LPDDR2, LPDDR3, or LPDDR4 systems.

Starting from

HIGHLIGHTS

DDR3, DDR4, DDR5, LPDDR2, LPDDR3, LPDDR4, LPDDR5, and GDDR6 Analysis

- Rapidly navigate traffic flow using “Transaction Decode” and “Traffic Overview” views

- Follow transactional decode of low power data transfers, self-refresh entry/exit, multipurpose commands (MPC), DDR4 3DS (three-dimensional stacking of DRAM die), LPDDR5 Bank organization modes, speed changes, and Mode registers

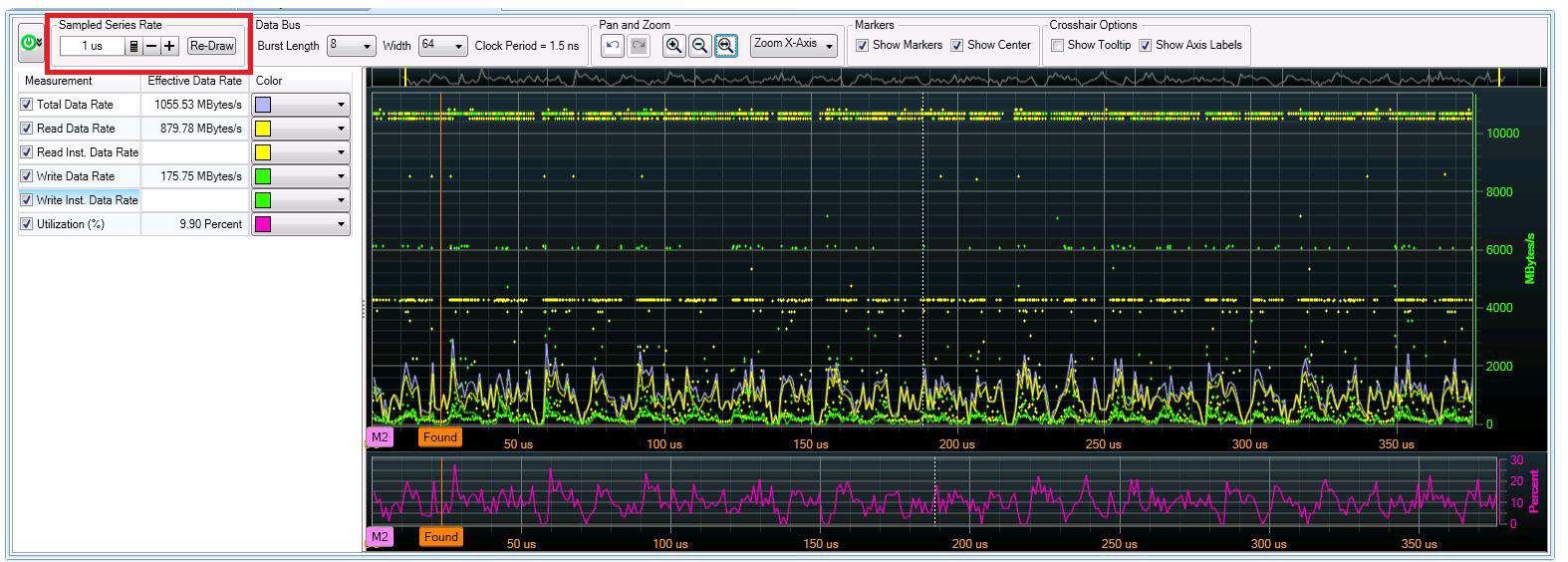

- View performance calculations and graphs of data rates and % bus utilization, observe refresh rates using a graphic rolling refresh window, and see Page open/close transaction associations and data transmitted for each READ or WRITE transactions

- Visualize address mapping and see addresses at risk of Row Hammer issues from too many Activates between refreshes

DDR3, DDR4, DDR5, LPDDR2, LPDDR3, LPDDR4, and LPDDR5 Compliance Validation

- Test protocol compliance violations across speed changes using the post-process compliance violation tool

- Identify DDR/2/3/4/5 or LPDDR/2/3/4/5 state machine, protocol compliance, and protocol level bus cycle timing violations using either post-process or real-time tools

- Save time with automated real-time DDR2/3/4/5 or LPDDR2/3/4/5 protocol compliance measurements and trace captures using the real-time compliance violation analysis tool

- Edit parameters of the DDR2/3/4/5 or LPDDR2/3/4/5 standard preset tests easily using an enhanced parameter editing interface for both post-process and real-time tools

ONFi (Open NAND Flash Interface) Analysis

- Supports Toggle mode and proprietary NAND protocols using customization feature.

- Navigate quickly across multiple ONFi targets using the condensed ONFi analysis “Timeline” view.

- Save time by visualizing an ONFi operation as a set of logically associated commands in a sequence, using the “Details” view of the ONFi transactions

Listing Decoders for DDR, DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3, and LPDDR4

- Decodes DDR, DDR2, DDR3, DDR4, LPDDR, LPDDR2, LPDDR3 and LPDDR4 commands and MRS commands

- Includes selection to decode MRS of DDR4 RDIMM and LRDIMM

- Enables fast physical address trigger setup with physical address trigger tool for DDR/2/3/4 and LPDDR/2/3

The Keysight B4661A memory analysis software offers a suite of options that include the industry’s first protocol compliance violation testing capability across speed changes, a condensed traffic overview for rapid navigation to areas of interest in the logic analyzer trace, powerful performance analysis graphics, and DDR and LPDDR decoders. With the B4661A memory analysis software and a Keysight logic analyzer*, users can monitor DDR/2/3/4/5, LPDDR2/3/4/5, GDDR6, or ONFi systems to debug and improve performance. Validation of compliance to DDR/2/3/4/5 and LPDDR2/3/4/5 protocols are important options. Powerful traffic overviews, multiple viewing choices, and real-time compliance violation triggering help identify elusive DDR/LPDDR system issues.

The Keysight B4661A memory analysis software provides four standard software features and seven licensed memory analysis options. GDDR6 analysis (licensed option -7FP/7TP/7NP) will be added in the 6.70 release in March 2020.

Standard software features:

- Default configurations for DDR and LPDDR probing solutions for Keysight logic analyzers

- DDR setup assistant

- DDR eye finder / eye scan

- DDR configuration creator

Free Trials

Get a 30-day trial license for B4661B.

Interested in a B4661A?

Extend the capabilities for your Memory Analysis Software for Logic Analyzers

Featured Resources for B4661A Memory Analysis Software for Logic Analyzers

Want help or have questions?