Choose a country or area to see content specific to your location

何をお探しですか?

-

-

3D Interconnect Designer

3D Interconnect Designerは、チップレット、積層ダイ、パッケージ、PCBなど、あらゆる高度な相互接続構造に対応する柔軟なモデリングおよび最適化環境を提供します。

-

-

-

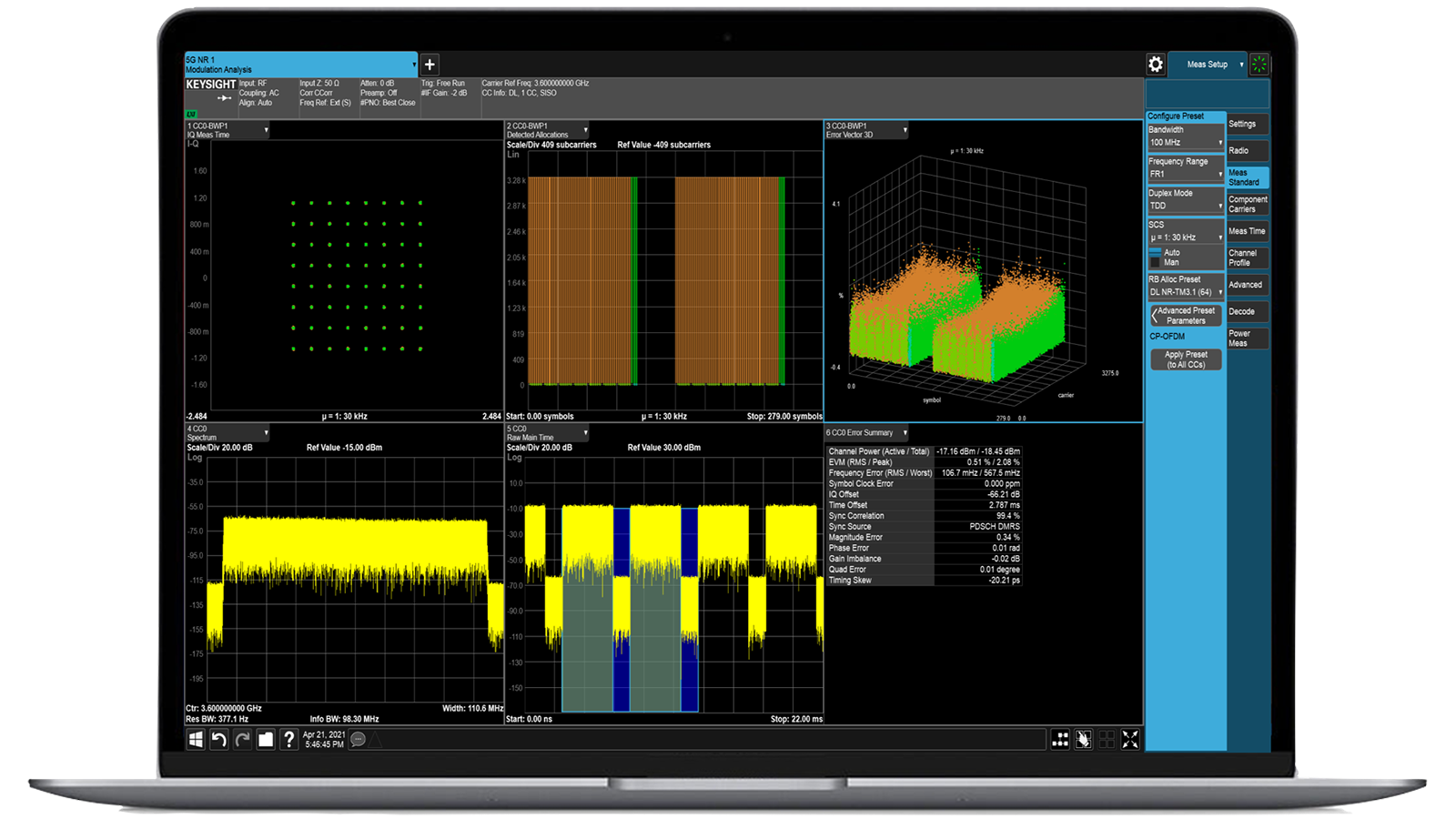

Xシリーズ測定アプリケーションで信号解析を加速

25種類以上のXシリーズアプリケーションを使用して、ワイヤレス、航空宇宙/防衛、EMI、位相ノイズの各分野で信号の解析、復調、トラブルシューティングを行います。

-

AI強化型パケットブローカーのご紹介

追加のメモリとストレージにより、これらの強化されたNPBは、キーサイトのAIセキュリティおよびパフォーマンス監視ソフトウェアとAIスタックを実行します。

-

-

-

-

-

- ソリューション

-

キーサイト Learnは、ソリューション、ブログ、イベントなど、関心のあるトピックに関する様々なコンテンツを提供しています。

- 購入

-

頻繁にお問い合わせされるサポート関連のお役に立つ情報すばやくアクセス

お持ちの製品をサポートするための追加情報

モジュラー AXI BERT、デジタイザ、およびDAQ

モデル: M8041A- 概要

- オプション

- アクセサリ

- ソフトウェア

- サポート

Pattern Generator for M8020A

高性能キーサイト・テクノロジーJ-BERT M8020Aは、最大16または32 Gb/sで動作するシングルおよびマルチレーンデバイスの高速かつ正確なレシーバー特性評価を可能にします。

-

サポートされるデータレート

32 Gb/s

-

モジュラータイプ

Pattern Generator

-

Number of channels

1, 2

-

規格

PCIe 4.0, USB 3.2, SATA 6G, SAS 24G, DP, SD-UHS II, TBT, MIPI, DDR5, PON, 64G FC, 10/40/100 GbE, OIF-CEI-26G

-

Line coding

NRZ

お見積りはこちら

同梱品をご確認いただき、キーサイトが提供する利用可能なアップグレードオプションをご覧ください。

ハイライト

J-BERT M8020A 高性能BERT

高性能なキーサイトJ-BERT M8020Aは、最大16Gb/sまたは32Gb/sで動作するシングルレーンおよびマルチレーンデバイスの高速かつ正確なレシーバー特性評価を可能にします。

今日の最高レベルの統合により、M8020Aはテストセットアップを簡素化します。さらに、信号状態の自動インサイチュ校正により、正確で再現性の高い測定が保証されます。インタラクティブなリンク・トレーニングにより、被試験デバイスのリンク・パートナーのように動作させることができます。J-BERT M8020Aは、設計に対する洞察を加速させます。

ターゲットアプリケーション

M8020Aは、最大16 Gb/sおよび32 Gb/sのシリアルI/Oポートを備えたチップ、デバイス、ボード、およびシステムの特性評価とコンプライアンス検証を行う研究開発エンジニアおよびテストエンジニア向けに設計されています。M8020Aは、PCI Express、USB、MIPI M-PHYTM、SATA/SAS、DisplayPort、SD UHS-II、Fibre Channel、メモリーバス、バックプレーン、リピーター、アクティブ光ケーブル、Thunderbolt、10 GbE、100 GbE(光および電気)、SFP+、CFP2/4トランシーバー、CEIなどの一般的なシリアルバス規格のテストに使用できます。

- パターンジェネレータおよびエラーディテクタ向けデータレートは最大8.5/16 Gb/s

- M8062A、32 Gb/s BERTフロントエンドにより、32 Gb/sまで拡張可能です。

- 統合された校正済みジッタ注入:RJ、PJ1、PJ2、SJ、BUJ、正弦波干渉(コモンモードおよび差動モード)、SSC(三角波および任意波、残留)

- 最大20 dBの8タップ・デエンファシス (正および負)

- ロスエミュレーション用の統合された調整可能なISI

- SAS-3、USB 3.0/3.1、PCI Express(8 GT/sおよび16 GT/s対応)用のインタラクティブリンク・トレーニング

- IEEE 10GBASE-KR、25GBASE-KR、および100GBASE-KR4用のインタラクティブTxEQトレーニング

- 内蔵クロックデータリカバリおよびイコライゼーション

- M8000 BERシリーズ向けM8070Aソフトウェアとのシステム統合

- BERT/スコープおよび任意波形発生器とのシームレスな動作

サービスとサポート

厳選されたサポートプランと、優先的な対応および迅速なターンアラウンドタイムにより、迅速なイノベーションを実現します。

予測可能なリースベースのサブスクリプションとフルライフサイクル管理ソリューションにより、ビジネス目標をより迅速に達成できます。

KeysightCareのサブスクライバーとして、コミットされた技術サポートなど、より質の高いサービスをご体験ください。

テストシステムが仕様どおりに動作し、ローカルおよびグローバルな標準に準拠していることを保証します。

社内での講師主導トレーニングやeラーニングにより、迅速に測定を実施できます。

キーサイトのソフトウェアをダウンロードするか、最新バージョンにアップデートしてください。