무엇을 찾고 있습니까?

추천 검색어

No product matches found - System Exception

일치하는 컨텐츠

ADS 2019 업데이트 1.0의 제품별 릴리즈

Highlights

ADS(Advanced Design System) 2019 업데이트 1.0은 다음을 위한 새로운 기능을 제공합니다.

신호 무결성과 전력 무결성 설계

- DDR5 메모리 설계자

- SIPro

- PIPro

- SerDes

전력 전자장치 설계

- 확장된 라이브러리

- 자동화된 시뮬레이션 설정

- LPE(Layout Parasitic Extraction)를 위한 자동화된 주파수 계획

RF & Microwave Design

- RFPro: 다중 기술/RF 모듈 시뮬레이션

- 최신 5G NR 테스트를 통해 업데이트된 5G VTB

- 개선된 작업 공간 관리 도구

- 스택형 PCB VIA

ADS 2019 업데이트 1.0을 지금 바로 다운로드할 수 있습니다.

위 체험판 및 라이선스 탭을 클릭한 다음, 세부 정보 및 다운로드 버튼을 클릭해서 최신 소프트웨어를 다운로드하십시오.

Description

ADS 2019 업데이트 1.0은 새로운 기능, 새로운 기술, 그리고 더 많은 개선 기능을 제공하는 데 있어 크게 진일보했습니다.

ADS 2019 업데이트 1.0은 새로운 기능, 새로운 기술, 그리고 더 많은 개선 기능을 제공하는 데 있어 크게 진일보했습니다.

신호 무결성과 전력 무결성 설계

ADS 2019 업데이트 1.0은 신호 무결성 및 전력 무결성 설계를 위한 새로운 기능을 제공합니다.

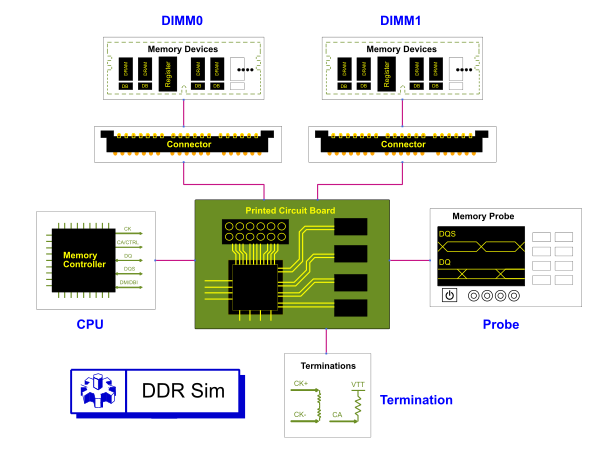

DDR5 메모리 설계자

메모리 시스템 설계에 혁신적인 워크플로우를 도입했습니다. 이 새 기능은 몇 시간이 걸리던 DDR 설정 시간을 몇 분으로 줄이고, DDR4 이상에 예측적 설계 흐름을 제공합니다.

- 메모리 컨트롤러 및 메모리 장치를 설정하기 위한 새로운 슈퍼 컴포넌트로, 신호 그룹으로서 IBIS 모델을 적용합니다.

- 단 한 번의 클릭으로 새 슈퍼 컴포넌트와 PCB 간에 버스-와이어를 연결합니다. 신호 ID 정보를 매칭하여 자동으로 연결이 이루어집니다.

- 과도 및 DDR 버스 시뮬레이터 모두를 위한 단일 개략도가 제공되기 때문에 둘 간의 교환을 위해 개략도를 변경할 필요가 없습니다 (신호 자극이 변경되면 변경 내용이 자동으로 넷리스트에 나열).

- 새로운 범용 메모리 프로브가 개략도 내 어디서든 신호에 대한 지능적 액세스를 제공하고, 그룹으로서 측정값을 적용합니다.

- 메모리 프로브는 업계에서 성능이 입증된 키사이트의 측정 기술(하드웨어 적합성 테스트에 사용되는 것과 같이 Infiniium이 포함된 DDR4 적합성 테스트 제품군)을 사용해 자동화된 DDR4 적합성 테스트를 시작할 수 있습니다.

그림 1. ADS 2019 업데이트 1.0의 메모리 설계자

SIPro 업데이트

- 메모리 설계자 워크플로우를 지원하기 위한 SIPro 업데이트에는 매우 생산적인 방식으로 EM 설정값을 생성하도록 도와주는 DDR 설정 마법사와 레이아웃 정보로부터 구문 분석된 신호 ID를 확인/편집하기 위한 DDR 속성 편집기가 포함되어 있습니다.

- 전력 평면 금속 공정과 불량 분석 공정이 추출에 포함되어 있는 SIPro 전력 인식 SI EM 추출의 속도가 매우 빨라졌습니다.

고속 시리얼 채널 시뮬레이션

- FlexDCA 프로브는 파형 메모리와 슬롯 구성을 모두 지원하기 때문에 고객들은 TDECQ, 지터 분해, 802.3bs 적합성 테스트 등을 포함한 PAM-4 측정 같은 복잡한 분석에 액세스하기 위해 키사이트의 FlexDCA에 파형을 손쉽게 전달할 수 있게 되었습니다.

- 새로운 MIPI C-PHY 3-와이어 Tx 및 EyeProbe가 채널 시뮬레이터 파트 팔레트에 추가되었습니다. 이러한 새 모델들은 채널 시뮬레이터 및 과도 시뮬레이션 모두에서 작동하며, 사용자가 트리거된 eye와 트리거되지 않은 eye를 볼 수 있도록 해줍니다.

- COM(Channel Operating Margin)은 IEEE 802.3bs 및 일부 JEDEC 표준에서 사용되는 채널 적합성 테스트입니다. SNR 계산과 비슷한 이 측정 기능이 이제는 채널 시뮬레이터에 대한 새로운 시뮬레이션 옵션으로 내장되어 있습니다. 원활한 워크플로우에서 IBIS-AMI 및 COM 흐름을 모두 지원합니다. 이 시뮬레이션 옵션은 표준에 따라 COM 계산을 처리하기 위해 Matlab 런타임(또는 선택에 따라 풀 버전)을 자동으로 호출합니다.

- BCI(Back Channel Interface) - IBIS-AMI v7 모델은 링크 트레이닝을 지원할 수 있습니다. 따라서 동일한 BCI 프로토콜을 지원하는 Tx 및 Rx IBIS-AMI 컴포넌트는 Tx 및 Rx 모두에서 이퀄라이제이션 설정을 최적화하기 위해 서로에게 메시지를 전달할 수 있습니다. 이 모델은 사용자를 위해 유용성과 생산성을 크게 개선했기 때문에 두 모델 모두에서 가능한 모든 EQ 설정을 스위프하지 않고도 최적의 이퀄라이제이션 eye를 달성할 수 있습니다.

신호 무결성/전력 무결성

- 일반적으로 PIPro DC 전기열 시스템의 메모리 사용량이 70% 줄고 성능이 1.5배 높아졌습니다.

- 전력 인식 시뮬레이션(전력 평면 금속 공정과 불량 분석 공정)이 추출에 포함된 시뮬레이션을 위해 속도를 크게 향상시켜(5배 이상) DDR SIPro 시뮬레이션의 성능을 개선했습니다.

- DDR 신호 ID(참조 지시, 신호 유형, 신호 인덱스 같은 속성)를 확인 및 수정할 수 있게 해주는 속성 편집기를 포함한 DDR 분석 설정 도구가 새로 제공됩니다. DDR 설정 도구를 사용해 생성된 DDR에 대한 분석이 속도에 맞게 최적화되었습니다.

- SIPro 시뮬레이션 및 PIPro-AC 시뮬레이션을 위해 컴포넌트 모델에 새로운 옵션 ("모델 업데이트 시 반드시 새 시뮬레이션이 필요하지 않음")이 포함되어 있습니다.

- 이 옵션을 활성화하면 시뮬레이션 이후에 컴포넌트 가치나 모델을 수정할 수 있습니다. PIPro 시뮬레이션을 새로 설정할 때 이 옵션이 기본 설정이 됩니다.

- 이 옵션을 비활성화하면 새 시뮬레이션을 수행하는 경우를 제외하고 더 이상 컴포넌트 가치를 변경할 수 없습니다. SIPro 시뮬레이션을 새로 설정할 때 이 옵션이 기본 설정이 됩니다. 이 옵션을 비활성화하면 보통 SIPro 시뮬레이션 시간과 메모리 요구사항이 줄어듭니다.

- 표에서 편집된 네트워크에 따라 SIPro에서 백 드릴 바이어스를 정의할 수 있는 기능이 제공됩니다.

- 분석 시뮬레이션 동안 사용 중인 스레드 수를 지정할 수 있는 기능을 통해 모든 SIPro 및 PIPro 분석에서 리소스 컨트롤을 제어할 수 있습니다.

- SIPro 또는 PIPro 사용자 인터페이스가 클러스터의 머신에서 시작될 때 LSF/PBS/Subgrid 클러스터에서 원격 시뮬레이션을 할 수 있는 기능이 제공됩니다.

전력 전자장치 설계

ADS 2019 업데이트 1.0은 전력 전자장치 설계를 위해 새로운 전력 전자장치 확장 라이브러리를 제공합니다.

전력 전자장치 라이브러리

- 과도 시뮬레이션, 고조파 균형 시뮬레이션 및 시뮬레이션 옵션을 위한 전력 전자장치 고유의 컨트롤러가 전력 전자장치 라이브러리에 추가되었습니다.

- LTspice와 호환되는 Schmitt 컴포넌트가 전력 전자장치 라이브러리에 추가되었습니다.

- Set Dominant 및 Reset Dominant 플립플롯이 전력 전자장치 라이브러리에 추가되었습니다.

- ASM-HEMT(Advanced Spice Model for High Electron Mobility Transistors)를 위해 Spectre 호환성이 추가되었습니다.

자동화된 시뮬레이션 설정

LPE(Layout Parasitic Extraction)를 위한 자동화된 주파수 계획

RF & MICROWAVE 설계

ADS 2019 업데이트 1.0은 다음을 포함하여 까다로운 RF 및 마이크로웨이브 설계를 위해 솔루션과 기타 기능을 제공합니다.

회로 시뮬레이션

가상 테스트 벤치

- 최신 5GNR 테스트를 지원하도록 가상 테스트 벤치가 업그레이드 되었습니다.

- 이제는 변조된 신호 조건 하에서 회로 통찰력을 지원하기 위해 VTB를 사용할 때 회로 데이터가 기본적으로 저장됩니다.

신규 모델 또는 업데이트 모델 지원:

- 최신 BSIM-IMG 모델(102.9.2)을 지원합니다.

EM 시뮬레이션

RFPro

- 다음과 같이 다중 기술 설계(중첩 기술 또는 스마트 마운트)를 위한 EM 분석 기능이 새롭게 제공됩니다.

- 본딩 와이어를 포함해 기술 경계를 가로지르는 물리적 상호 연결을 추출할 수 있습니다.

- 설계 계층 구조 어디에서나 배치된 (가상) 핀으로부터 포트를 손쉽게 정의할 수 있습니다.

- 새로운 사용자 정의 EM 추출 분석 유형이 대규모 설계에 대해 선택한 네트워크를 EM 시뮬레이션할 수 있도록 해줍니다.

- 설계 상의 유전체 크기 옵션 컨텍스트 메뉴는 FEM 시뮬레이션을 위한 무한 유전체 계층의 크기를 제어할 수 있도록 해줍니다.

- 분석 옵션 → 주파수 계획 → 필드 스토리지 아래의 원거리 영역 센서 설정에서 원거리장 계산을 활성화 또는 비활성화할 수 있습니다. 3D 원거리 영역 센서의 분해능도 지정할 수 있습니다.

EM 설정

- 새로운 'SMPS' 주파수 계획 유형은 스위치 모드 파워 서플라이(Switched Mode Power Supply) 시뮬레이션을 지원합니다.

FEM

- 'Direct', 'SMD' 및 'Delta-Gap' 피드 유형의 포트 교정 접근 방식에 대한 제어 기능이 새롭게 제공됩니다. 자세한 내용은 FEM의 포트를 참조하십시오.

Momentum

- FEM 시뮬레이션을 위한 Momentum 레이아웃 전처리가 새로운 FEM 포트 교정 기능을 지원할 때 피드 유형을 보존할 수 있도록 향상되었습니다.

검증 테스트 벤치(VTB)

- 현재 단일 포트 VTB(소스만) 시뮬레이션이 지원되고 있습니다. 이제는 SystemVue에서 복잡한 변조 소스를 생성하고 ADS Circuit Envelope에서 이를 사용할 수 있습니다.

설계 및 기술 관리

- 작업 공간에서 현재 지원되지 않는 라이브러리/pdk 기술 추가를 지원할 수 있도록 기술 마법사가 새로 업데이트되었습니다.

- 참조 DB의 성능과 이것이 다른 작업에 미치는 영향이 개선되었습니다.

- 읽기 전용 사용자 라이브러리를 처리하기 위한 참조 DB가 고정되었습니다.

- 참조 또는 종속 요소를 나열한 후 어떤 것을 삭제하면 참조 및 종속 요소 창에 해당되는 프롬프트 메시지가 나타납니다.

- 이제는 저장 없이 수정된 설계를 닫으면 참조 DB가 업데이트됩니다.

- 라이브러리 또는 라이브러리 정의 파일을 제거하면 제거 중인 라이브러리 세트에 있는 종속 요소들에 대한 경고 메시지가 나타납니다.

- 확인 작업 공간에서 설정이 활성화될 때 읽기 전용 사용자 라이브러리에서 발생하는 문제를 확인할 수 있습니다.

시작하기

ADS 2019 업데이트 1.0을 사용할 준비가 되셨습니까? 무료 체험판을 신청하십시오.

다른 ADS 제품 버전을 보십시오.