何をお探しですか?

関連キーワード

No product matches found - System Exception

検索結果

ADS 2019アップデート1.0製品リリース

Highlights

Advanced Design System(ADS)2019アップデート1.0は、以下のために使用できる新しい機能を提供します。

シグナルインテグリティー/パワーインテグリティーのデザイン

- DDR5メモリデザイナー

- SIPro

- PIPro

- SerDes

パワー・エレクトロニクス・デザイン

- 拡張ライブラリ

- 自動シミュレーションセットアップ

- レイアウト寄生成分抽出用の周波数プランの自動化

RF/マイクロ波デザイン

- RFPro:マルチテクノロジー/RFモジュールシミュレーション

- 最新の5G NRテストを用いた5G VTBアップデート

- ワークスペース管理ツールの改善

- スタック可能なPCBビア

ADS 2019アップデート1.0がダウンロード可能になりました。

上の[トライアル&ライセンス]タブをクリックしてから、[詳細&ダウンロード]ボタンをクリックして最新ソフトウェアをダウンロードしてください。

Description

ADS 2019 Update 1.0 は大きく前進し、新しい機能とテクノロジーが追加されただけでなく従来の機能も強化されています。これにより、デザインの生産性と効率が向上します。

ADS 2019 Update 1.0 は大きく前進し、新しい機能とテクノロジーが追加されただけでなく従来の機能も強化されています。これにより、デザインの生産性と効率が向上します。

シグナルインテグリティー/パワーインテグリティーのデザイン

ADS 2019アップデート1.0は、シグナルインテグリティー/パワーインテグリティーのデザインのための新しい機能を提供します。

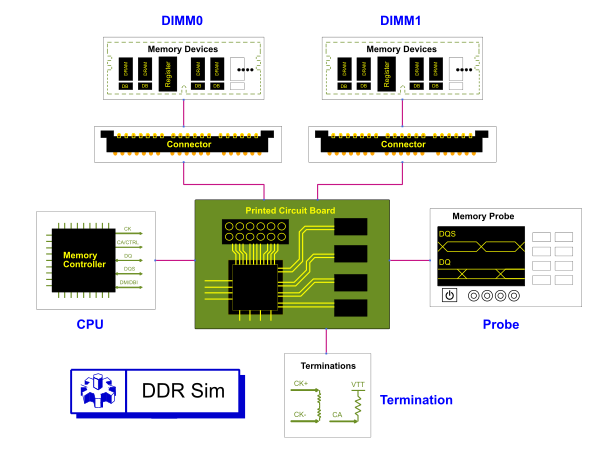

DDR5メモリデザイナー

メモリ・システム・デザイン向けの革新的なワークフローが追加されました。この新しい機能により、DDRのセットアップ時間が数時間から数分に短縮され、DDR4以降向けに予測可能なデザインフローが提供されます。

- メモリコントローラーおよびメモリデバイスのセットアップ用の新しい高度なコンポーネント ‐ IBISモデルを信号グループとして適用可能。

- ワンクリックで信号ID情報を適合させて、新しい高度なコンポーネントとPCBコネクタの間のバスワイヤーを自動的に接続。

- トランジェントシミュレータとDDRバスシミュレータをスケマティックで入れ替えなくても、両シミュレーションを1つのスケマティックで実行可能。(信号スティミュラスを自動的に変更/ネットリスト化)

- 新しいユニバーサル・メモリ・プローブ ‐ スケマティック内のあらゆる位置の信号にインテリジェントなアクセスを提供。グループとして測定を適用可能。

- メモリプローブにより自動DDR4コンプライアンステストを起動可能 ‐ 業界で実績のあるキーサイトの測定技術(ハードウェア・コンプライアンス・テストで使用されているInfiniiumによるDDR4コンプライアンス・テスト・スイート)を使用。

図1. ADS 2019アップデート1.0のメモリデザイナー

SIProアップデート

- SIProのアップデートにより、メモリ・デザイナー・ワークフローをサポート。これには、非常に生産性の高い方法で電磁界セットアップを作成できる新しいDDRセットアップウィザードや、レイアウト情報からパースされた信号IDの表示/編集が可能なDDR属性エディターが含まれています。

- パワープレーンのメタライゼーション/Decapが抽出に含まれる位置におけるSIPro Power-Aware SIの電磁界抽出を大幅に高速化。

高速シリアル・チャネル・シミュレーション

- FlexDCAプローブが波形メモリ構成とスロット構成の両方をサポート。このアップデートにより、Keysight FlexDCAに波形を容易に転送できるようになり、TDECQ、ジッタ分離、802.3bsコンプライアンステストを含むPAM4測定のような複雑な解析が可能になります。

- チャネルシミュレータのパーツパレットに新しいMIPI C-PHY 3ワイヤーTxとEyeProbeを追加。これらの新しいモデルはチャネルシミュレーションとトランジェントシミュレーションの両方で動作するので、トリガのあるアイとトリガのないアイを確認できます。

- IEEE 802.3bsおよび一部のJEDEC規格で使用されているチャネル・コンプライアンス・テスト、チャネル動作マージン(COM)を新しいシミュレーションオプションとして組み込み。この測定はS/N比の計算に似たもので、チャネルシミュレータに新しいシミュレーションオプションとして組み込まれます。使いやすいワークフローでIBIS-AMIフローとCOMフローの両方がサポートされています。このシミュレーションオプションは、自動的にMatlabランタイム(オプションによりフルバージョンも可能)を起動して、規格に従ってCOM計算を処理します。

- バック・チャネル・インタフェース(BCI) ‐ IBIS-AMI v7モデルがリンクトレーニングのサポートを提供可能。同じBCIプロトコルをサポートするTx/Rx IBIS-AMIコンポーネントで互いにメッセージを交換して、TxとRxの両方のイコライゼーション設定を最適化できます。ユーザーの使い勝手と生産性が大幅に向上します。多くの場合、両モデルで可能性があるすべてのEQ設定を掃引しなくても最適にイコライズされたアイを実現できます。

シグナルインテグリティー/パワーインテグリティー

- PIPro DC電気-熱シミュレーション向けのメモリ使用量を70 %(代表値)削減、性能が1.5倍高速化。

- Power-Awareシミュレーション(パワープレーンのメタライゼーション/Decap)が抽出に含まれるシミュレーションの大幅な高速化(5倍以上)により、DDR SIProシミュレーションの性能が向上。

- 新しいDDR解析セットアップツールの追加。属性エディターによりDDR信号ID(参照識別子、信号タイプ、信号インデックスなどの属性)を表示/変更できます。DDRセットアップツールで作成されたDDRの解析は、速度が最適化されます。

- SIProシミュレーションとPIPro-ACシミュレーションのコンポーネントモデルに新しいオプションを追加(「モデルのアップデートで新しいシミュレーションは必要ありません」)。

- このオプションをオンにするとシミュレーション後にコンポーネント値やモデルを変更できます。これは新しいPIProシミュレーションセットアップのデフォルト設定です。

- このオプションをオフにすると、新しいシミュレーションの実行時しかコンポーネント値を変更できなくなりました。これは新しいSIProシミュレーションセットアップのデフォルト設定です。本オプションをオフにすると、通常はSIProシミュレーション時間とメモリ要件が改善されます。

- SIProでバック・ドリル・ビアを定義する機能を追加。表でネットごとに編集できます。

- 解析シミュレーション中に使用されるスレッド数を指定する機能により、すべてのSIPro/PIPro解析のリソースコントロールを制御可能。

- SIProまたはPIProのユーザーインタフェースがクラスターのマシン上で起動されたときに、LSF/PBS/Subgridクラスターをリモートシミュレートする機能。

パワー・エレクトロニクス・デザイン

ADS 2019アップデート1.0は、パワー・エレクトロニクス・デザイン向けの新しいパワーエレクトロニクス拡張ライブラリを提供します。

パワー・エレクトロニクス・ライブラリ

- トランジェントシミュレーション、ハーモニック・バランス・シミュレーション、シミュレーションオプション向けのパワーエレクトロニクス専用コントローラーをパワー・エレクトロニクス・ライブラリに追加。

- LTspiceで使用できるシュミットコンポーネントをパワー・エレクトロニクス・ライブラリに追加。

- セット優先/リセット優先フリップフロップをパワー・エレクトロニクス・ライブラリに追加。

- 高電子移動度トランジスタ用Advanced Spice Model(ASM-HEMT)にSpectreとの互換性を追加。

自動シミュレーションセットアップ

レイアウト寄生成分抽出用の周波数プランの自動化

RF/マイクロ波デザイン

ADS 2019アップデート1.0は、困難なRF/マイクロ波デザインに対して、以下を含むソリューションを提供します。

回路シミュレーション

仮想テストベンチ(VTB)

- 仮想テストベンチのアップグレードにより、最新の5G NRテストをサポート。

- VTBを使用している場合はデフォルトで回路データを保存。これにより、変調された信号の条件で回路解析が可能。

新しいモデルおよびアップデートモデルのサポート:

- 最新のBSIM-IMGモデル(102.9.2)のサポート

電磁界シミュレーション

RFPro

- マルチテクノロジーデザイン(ネストテクノロジーまたはスマートマウント)向けの新しい電磁界解析機能:

- ボンドワイヤーを含む、複数のテクノロジーバウンダリーにわたる物理的なインターコネクトの抽出。

- デザイン階層内のどこでも、配置された(仮想)ピンを元にポートを容易に定義可能。

- 新しいユーザー定義電磁界抽出解析手法により、大規模なデザインで選択したネットを電磁界シミュレート可能。

- デザイン上のDielectric Size Optionsコンテキストメニューを使用して、FEMシミュレーションでそのサイズの無限誘電体レイヤー全体を制御可能。

- Analysis Options→Frequency Plans→Fields Storageの下にあるFar Zone Sensor設定により、近傍界の計算をオン/オフ可能。3D Far Zone Sensorの確度分解能も指定可能。

電磁界セットアップ

- 新しい"SMPS"周波数プランによりスイッチング電源シミュレーションをサポート。

FEM

- "Direct"、"SMD"、"Delta-Gap"の給電タイプを用いたポート校正手法に新しい制御を提供。詳細は、FEMの"Ports"を参照してください。

Momentum

- FEMシミュレーションのMomentumレイアウトプリプロセッシングを拡張して、新しいFEMポート校正機能をサポートする給電タイプに対応。

検証テストベンチ(VTB)

- シングルポートVTB(ソースのみ)シミュレーションをサポート。SystemVueで複雑な変調ソースを作成して、ADS Circuit Envelopeと一緒に使用可能。

デザイン/テクノロジーの管理

- 新しいテクノロジーウィザードのアップデートにより、現在ワークスペースにないライブラリ/pdkテクノロジーの追加をサポート。

- 参照DBの性能の向上、それが別の動作に及ぼす影響の改善。

- 読み取り専用のユーザーライブラリを扱えるように、参照DBを修正。

- 参照/依存をリスト表示した後に何かが削除された場合に、参照/依存ウィンドウが適切なメッセージを表示。

- 変更デザインを保存せずにクローズすると、参照DBをアップデート。

- ライブラリまたはライブラリ定義ファイルが削除された場合に、削除されたライブラリセット内の依存関係に関する警告を表示。

- 設定がオンの場合、ワークスペースのチェック機能により、読み取り専用ユーザーライブラリの問題をチェック可能。

デザイン編集

- ADS 2019アップデート1.0で、これまでと異なる新しいPcbビアを提供。従来のPcbビアは"Padstack Templates"と呼ばれるようになります。使用するPadstack Templatesを指定して新しいPcbビアを作成できます。さらにユーザーは、スタート/ストップレイヤーとスタック可能な属性を指定できます。新しいPcbビアの詳細については、"Define and Insert PCB Vias and Pads using Padstack Templates"を参照してください。

- 新しいスマートマウントのサブタイプであるマルチマウントの追加。これらは、ボトムマウント、フリップチップ、カスタムマウントのいずれかとして使用できるデザインを目的にしています。スマート・マウント・デザインをインスタンス化する際の決定はモジュールデザイナーが行います。インスタンスのマウントタイプも配置時に変更できます。詳細については、ヘルプトピック、"Multi-Mount under What is Smart Mount"を参照してください。

使用するには

ADS 2019アップデート1.0をご利用ください。無料試用のお申し込みはこちらです。

他のADS製品のバージョンを表示できます。