Digitaler Hochgeschwindigkeitsentwurf

Lernen Sie die Grundlagen des HSD-Schaltungsdesigns.

Mit der Komplexität moderner Elektronik Schritt halten

Entdecken Sie die vier Überlegungen für ein erfolgreiches digitales Hochgeschwindigkeitsdesign mit einem ganzheitlichen Designansatz vom Konzept bis zur Simulation, Emulation und Konformität.

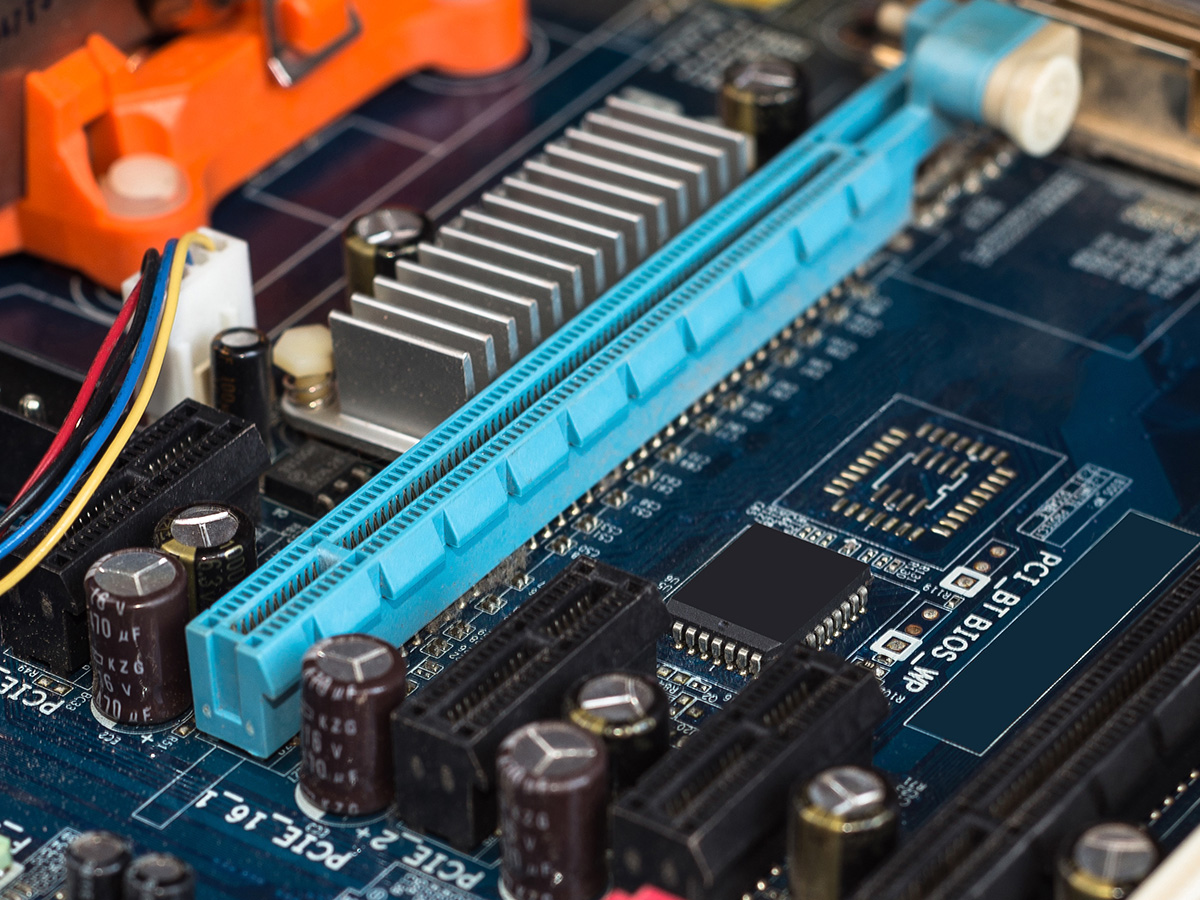

Erfahren Sie mehr über die neuen Funktionen, die mit PCIe® 6.0 eingeführt wurden, und die wichtigsten Vorteile einer End-to-End-Lösung von der Simulation bis zum Protokolltest.

Überprüfen Sie den technischen Weg, den das Normungsgremium JEDEC eingeschlagen hat, um zu DDR5 zu gelangen, sowie weitere Überlegungen, die für den Übergang zu DDR5 erforderlich sind.

Lernen Sie die USB4-Technologie, die Architektur und die mehrstufige Signalisierung kennen.

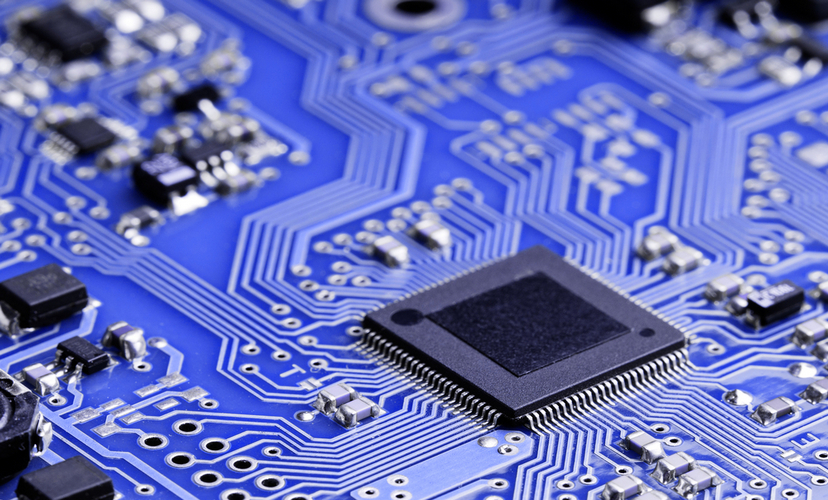

Was ist ein Chiplet und warum sollte es Sie interessieren?

Entdecken Sie, wie chiplets ein offenes Ökosystem von modularen Komponenten ermöglichen, die wiederverwendet und angepasst werden können.

Ausgewählte Kurse

Entdecken Sie Designkurse zu Standards

Lernen Sie die Bedeutung von Pre- und Post-Layout-Modellen für Speicherkanäle kennen und erfahren Sie, wie Sie mit diesen Modellen bauen und entwerfen können.

Entdecken Sie, wie Sie einen durchgängigen Arbeitsablauf zur Durchführung einer Augenmessung nutzen können.

Optimierung von Hochgeschwindigkeits-Digitalschnittstellen

Erwerben Sie neue Fähigkeiten, um digitale Hochgeschwindigkeitsschnittstellen zu simulieren und Designentscheidungen zur Verbesserung der Signalintegrität zu erkunden.

Schnellstart für DDR5-Speicherdesign

Erhalten Sie einen schnellen Einstieg in die neuen Herausforderungen von DDR5 und Strategien für den Aufbau eines neuen Design-to-Test-Workflows für DDR5.

Auf DDR-Simulation basierende Konformitätstests

Gehen Sie die Konformitätstests und Designuntersuchungen mit verschiedenen Speicherstandards durch, einschließlich (LP) DDR und DDR5.

Optimierung des DDR5-Design-Workflows

Erwerben Sie das Wissen, um DDR5-Verlustreflexionen mit integrierter Design-Automatisierungs- und Analysesoftware zu reduzieren.

Lernen Sie, wie man JEDEC IBIS AMI-Modelle für DRAM-Treiber und -Empfänger (Dynamic Access Random Memory) erstellt und verwendet.

Advanced Techniken zur USB4-Simulation und -Messung

Überprüfung der USB4-Technologie, Signalverschlechterung, Kanalleistung, TP3-Konformitätspunkt und Multi-Level-Signalisierung.

Entdecken Sie Kurse zum Thema Signalintegrität

Optimierung der Signalintegrität

Entdecken Sie drei Möglichkeiten zur Optimierung der Signalintegrität in Ihrem Design und erfahren Sie, wie Sie unerwartete differentielle Impedanzen, SDD11 und SDD21 beheben können.

Entwurf eines robusten Arbeitsablaufs für die Signalintegrität

Gehen Sie die Mechanismen durch, die sich auf die Signalintegrität auswirken, und lernen Sie praktische Tipps für die Fehlersuche in Designs.

Finden und Lösen von Signalintegritätsproblemen

Erfahren Sie, wie Sie Probleme mit der Signalintegrität erkennen können, und lernen Sie Techniken kennen, die Ihnen helfen, die Augen für Ihren digitalen Kanal zu öffnen.

Entdecken Sie Kurse zum Thema Machtintegrität

Erfahren Sie mehr über leitungsgebundene elektromagnetische Störungen (CEMI), Normen und wie Sie Simulationen einrichten und durchführen.

Auswahl, Platzierung und Optimierung von Kondensatoren

Verwenden Sie EM-Simulatoren, um die richtigen Kondensatoren auszuwählen und die Platzierung für eine ruhige Energieverteilung zu optimieren.

Power Integrity Simulation Arbeitsablauf

Erfahren Sie, wie Sie einen End-to-End-Workflow nutzen können, der sich ideal für die Lösung der nächsten Generation von Niederspannungs- und Hochstromversorgungsdesigns eignet.

Entwurf eines Stromverteilungsnetzes

Entdecken Sie einen umfassenden Power-Integrity-Workflow, um eine flache Impedanz zu entwerfen und die Ursache für Ringing auf Stromschienen zu identifizieren.

Fähigkeiten zur Simulation und Messung der Leistungsintegrität

Anwendung digitaler Zwillinge zur Simulation von Entwürfen und Verwendung moderner Oszilloskope zur Messung von Stromversorgungssignalen.

HSD: Tiefer gehen

Erfahren Sie mehr über die Signal- und Stromversorgungsintegrität mit einer ausgewählten Auswahl an fortgeschrittenen Themen.

Verwandte Anwendungsfälle