Diseño digital de alta velocidad

Aprenda los fundamentos del diseño de circuitos HSD

Manténgase al día con la complejidad de la electrónica moderna.

Descubra las cuatro consideraciones para lograr el éxito en el diseño digital de alta velocidad utilizando un enfoque de diseño holístico desde el concepto hasta la simulación, la emulación y la conformidad.

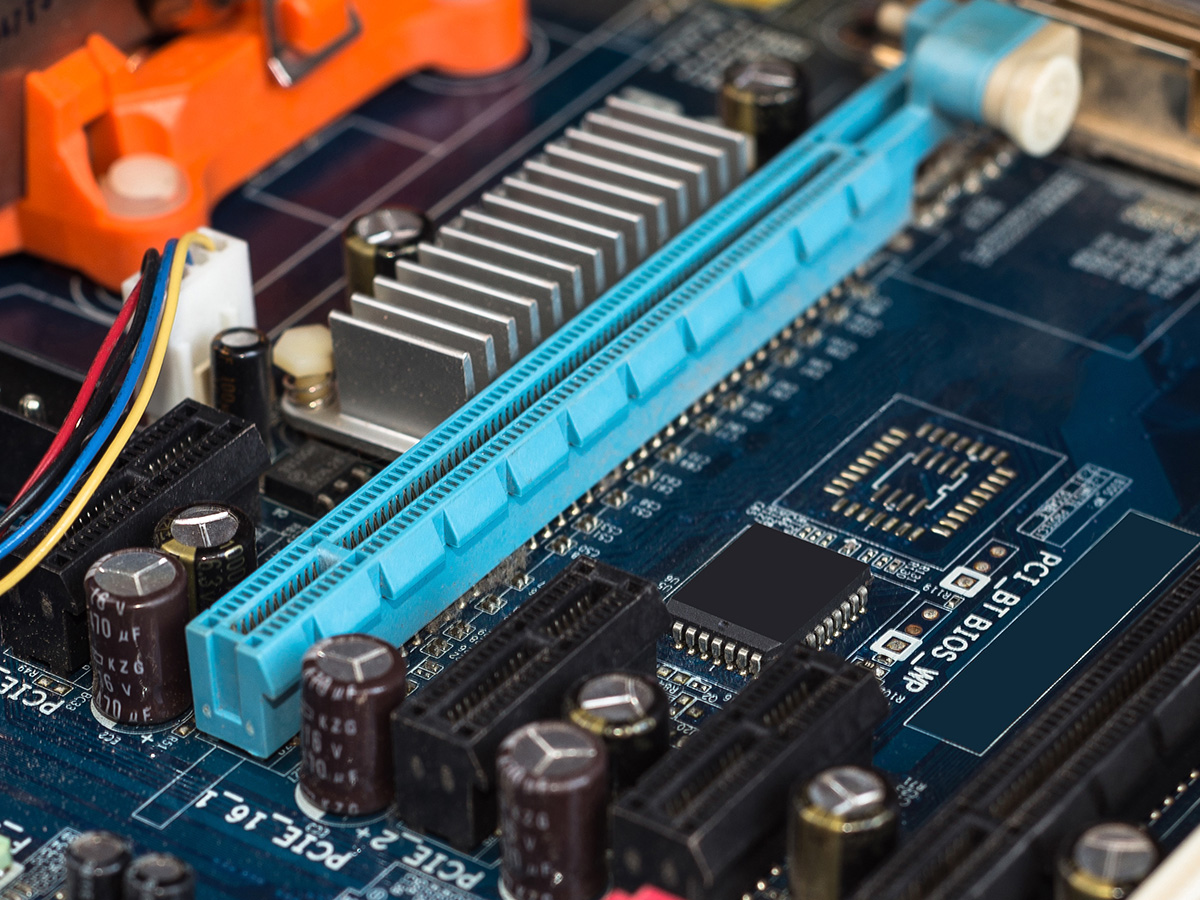

Conozca las nuevas capacidades introducidas con PCIe® 6.0 y los beneficios clave de una solución integral, desde la simulación hasta la prueba de protocolo.

Repasar el camino técnico que ha recorrido el organismo de normalización JEDEC para llegar a la DDR5 y otras consideraciones necesarias para ir más allá de la DDR5.

Visión general de la tecnología USB4

Explore la tecnología USB4, su arquitectura y la señalización multinivel.

Qué es un chiplet y por qué debería importarle

Descubra cómo los chiplets permiten un ecosistema abierto de componentes modulares que pueden reutilizarse y personalizarse.

Cursos destacados

Explore los cursos de diseño sobre normas

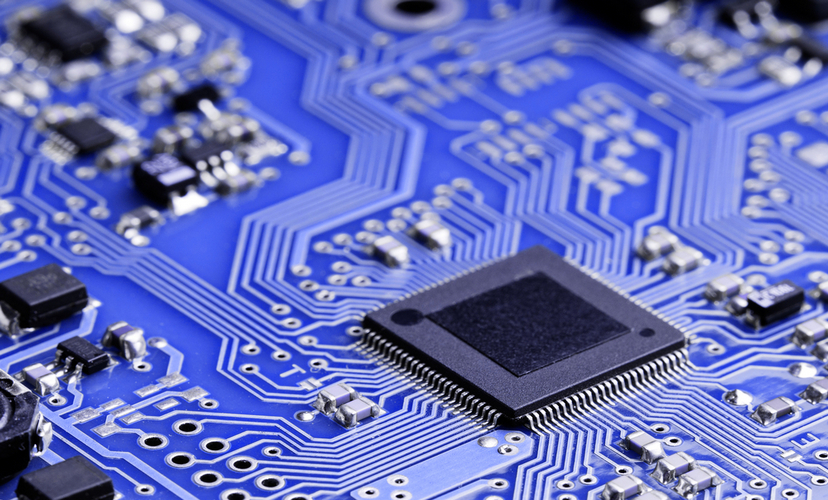

Análisis del bus de memoria DDR

Aprenda la importancia de los modelos de pre y post disposición de los canales de memoria y cómo construir y diseñar con ellos.

Tutorial del diseñador de memorias

Descubra cómo utilizar un flujo de trabajo integral para realizar una medición ocular.

Optimización de interfaces digitales de alta velocidad

Adquiera nuevos conocimientos para simular interfaces digitales de alta velocidad y Explorer opciones de diseño para mejorar la integridad de la señal.

Introducción rápida al diseño de memorias DDR5

Obtenga información rápida sobre los nuevos retos de la DDR5 y estrategias para crear un nuevo flujo de trabajo de diseño a pruebas para la DDR5.

Pruebas de conformidad basadas en simulación DDR

Recorrido por las pruebas de conformidad y Exploreción del diseño con varios estándares de memoria, incluidos (LP) DDR y DDR5.

Optimización del flujo de trabajo de diseño de DDR5

Adquiera los conocimientos necesarios para reducir el reflejo de pérdida de DDR5 con el software integrado de automatización y análisis de diseños.

Aprenda a crear y utilizar modelos JEDEC IBIS AMI para controladores y receptores de memoria aleatoria de acceso dinámico (DRAM).

Advanced para la simulación y medición de USB4

Repase la tecnología USB4, la degradación de la señal, el rendimiento de los canales, el punto de conformidad TP3 y la señalización multinivel.

Descubra los cursos sobre integridad de la señal

Optimización de la integridad de la señal

Descubra tres formas de optimizar la integridad de la señal en su diseño y cómo solucionar impedancias diferenciales, SDD11 y SDD21 inesperadas.

Diseñar un flujo de trabajo robusto para la integridad de la señal

Conozca los mecanismos que afectan a la integridad de la señal y aprenda consejos prácticos para solucionar problemas en los diseños.

Encontrar y resolver problemas de integridad de la señal

Aprenda a identificar los problemas de integridad de la señal y obtenga técnicas que le ayudarán a abrir los ojos de su canal digital.

Explore los cursos sobre integridad de la alimentación eléctrica

Conozca las interferencias electromagnéticas conducidas (CEMI), las normas y cómo configurar y ejecutar simulaciones.

Selección, colocación y optimización de condensadores

Utiliza simuladores EM para seleccionar los condensadores correctos y optimizar la colocación para una distribución silenciosa de la energía.

Flujo de trabajo de simulación de integridad de potencia

Aprenda a utilizar un flujo de trabajo integral ideal para resolver la próxima generación de diseños de suministro de energía de baja tensión y alta corriente.

Diseño de redes de distribución de energía

Descubra un completo flujo de trabajo de integridad de la potencia para diseñar con impedancia plana e identificar la causa raíz del zumbido en los carriles de potencia.

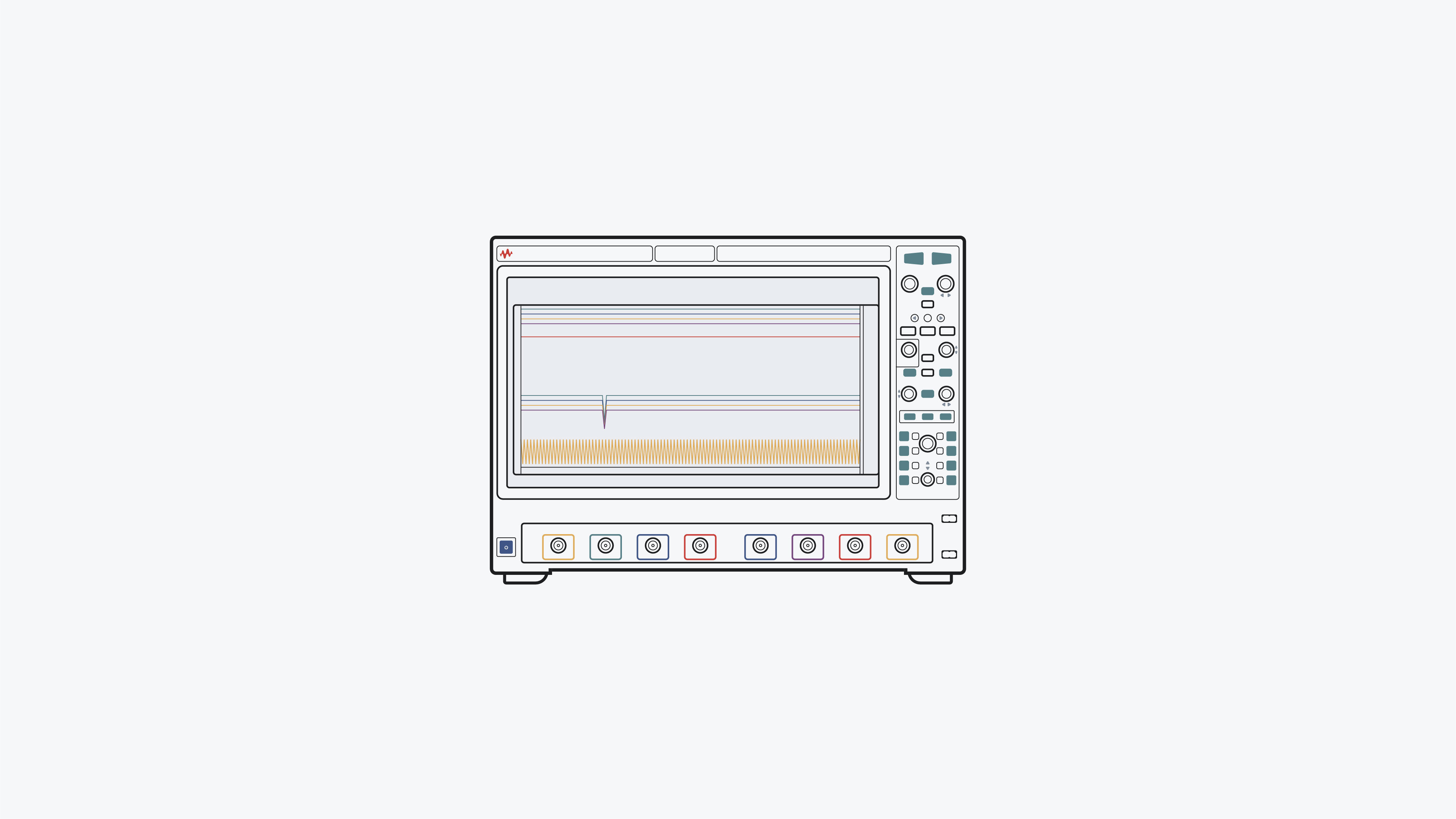

Simulación y medición de la integridad de la energía

Aplicar gemelos digitales para simular diseños y utilizar osciloscopios avanzados para medir señales de integridad de potencia.

HSD: Profundiza

Aprenda más con una inmersión más profunda en la integridad de la señal y la alimentación con una selección curada de temas avanzados.

Casos prácticos relacionados