What are you looking for?

Suggested searches

No product matches found - System Exception

Matched content

PathWave ADS 2023 Product Release

Highlights

The PathWave Advanced Design System (ADS) 2023 product release includes new capabilities and enhancements for:

- File and Workspace Management Tools

- Design Editing and Layout

- Data Display

- Circuit Simulation

- Electrothermal Simulation

- High Performance Computing (HPC)

- High Speed Digital (HSD) Design

- EM Simulation

- Verification

- Design Kits

- Power Electronics

- Virtual Test Bench

- Documentation

PathWave ADS 2023 is available now!

PathWave ADS 2023 continues to offer the industry’s most complete RF and microwave, High-Speed Digital, and Power Electronics design capabilities simulation software that you’ve come to depend on. This release delivers new and enhanced capabilities to improve productivity and usability for RF and Microwave circuit and system designers.

Watch some of our new videos on YouTube:

File and Workspace Management Tools

- Microsoft Visual Studio (VS) code debug extension to AEL for multiple ADS sessions

- Open workspace performance improvement to enable ADS sessions while loading libraries

- Workspace archive lists dataset files outside of workspace directory for data-display references

- TclTK 8.5 scripting now shipped with ADS

Design Editing and Layout

- Improved editing of Vias and Padstacks

- Enhanced GDSII import

- Connectivity overlaps one-click resolution enhancements

- 3D layout bounding cuboid view for easier editing

- New AEL functions for automation

- Automated design refresh when via rules modified

- Retrieving master substrate name

- Selecting entire list

Data Display

- Native Python functions for Data Viewing, Analysis and Manipulation

- New DATA_HOME environment variable for referencing a common directory across workspaces to improve cross-platform usage

- Single Specification object for grouping of Limit Line and Mask on plots

Circuit Simulation

- Streamlined remote and distributed simulation management to support cloud-based High-Performance Computing (HPC)

- New Leti-UTSOI 102.6 transistor model for accurate analog and RF circuit designs

- Monte Carlo statistical controller now includes Yield optimization

Electrothermal Simulation

- Supports custom multi-technology electrothermal (ETH) flow even when layout and schematic hierarchies are mismatched

- PathWave ADS offers the industry’s most accurate electro-thermal simulation that predicts the location and timing of harmful transient temperature peaks so that they can be fixed before hardware production

- PathWave ADS’ Electro Thermal Dynamic model generator speeds up transient electro-thermal simulation by typically 10x and up to 100x to ensure thermal reliability for mission-critical and reputation-critical designs

High Performance Computing (HPC)

- EM and Circuit simulation acceleration through parallelized High-Performance Computing (HPC) with cost-effective, powerful, and high-capacity cloud-based hardware resources enable typical speed up from 5x to 20x

- Parallel EM simulation (RFPro) parameter sweep

- Even with a modest 5x speed up, this means a time saving of 4 days out of a 5-day work week, enabling many more simulations to design high-performance, tolerance-insensitive RF/MW components and to significantly shorten time-to-market

High Speed Digital (HSD) Design

Memory Designer

- Supports HBM3, LPDDR5x, IBIS – EMD models

- IBIS 7.1 parser with custom IBIS file viewer

- Multi-Segment smart bus wire connection

- Drag-n-drop multi-plots from Expression Manager

- Improved CA/Data Bus Pre-layout builder editing

- Cloud based High Performance Computing (HPC)

SerDes Design

- New Ethernet AMI modeler

- USB AMI model for NZR modulation and Spread Spectrum Clocking (SSC)

- USB reference channel models

- PCIe AMI model generation for Gen 6 with PAM4 modulation, DFE taps and 6-lance reference channel with crosstalk

- PAM6 modulation for Tx in Channel Simulator

- SmartEye Probe for transient PAM4 simulation

- Channel Operating Margin (COM) versions 3.4 and 3.7 added

- Measured Data based model for TX Waveform AMI component in Rx package and external channel models

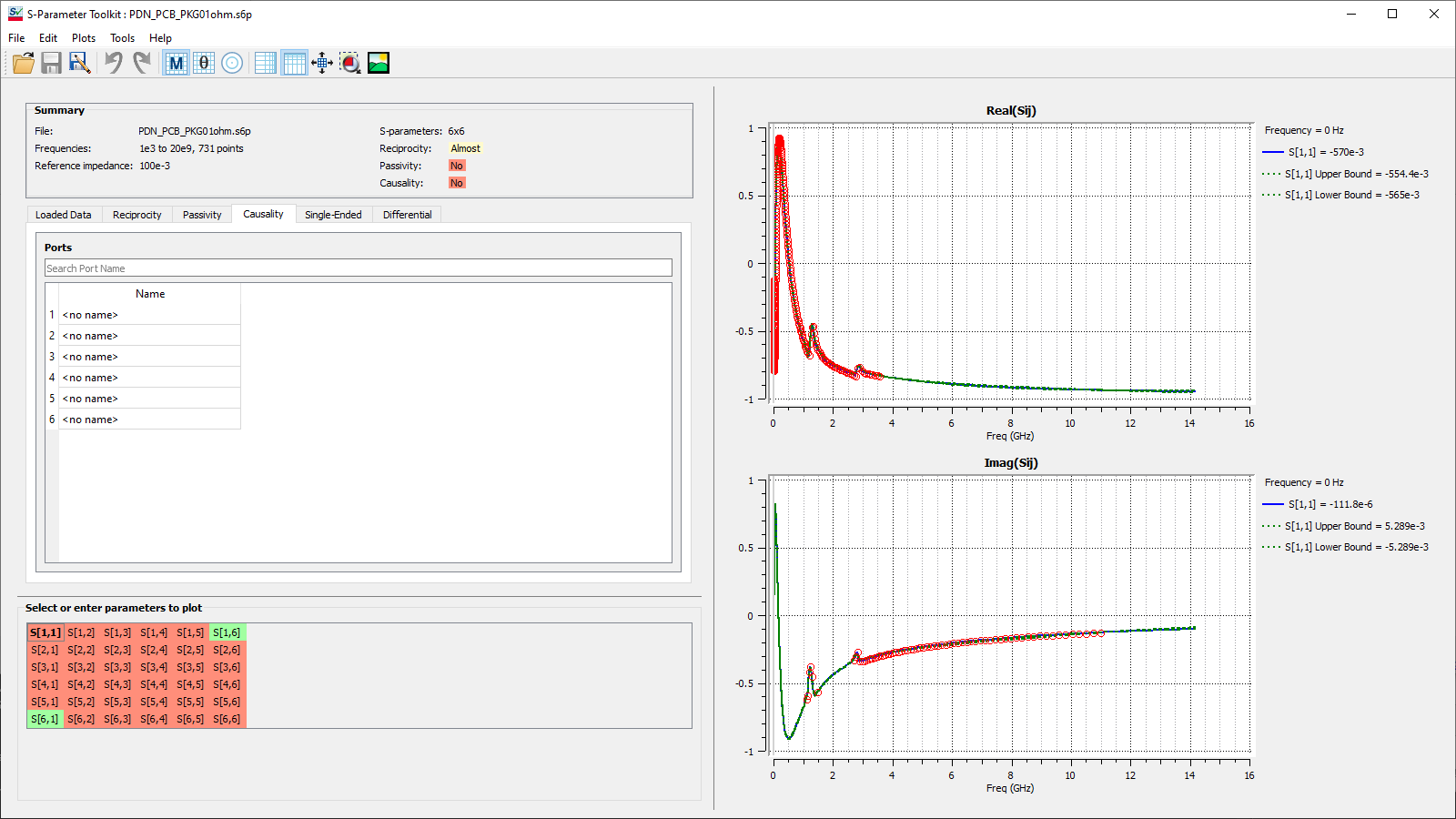

- PowerSum crosstalk and ICR/ICN analysis in S-parameter Toolkit

EM-SIPro/PIpro

- RapidScan support for trapezoidal conductor cross-sections and improved coplanar ground detection

- Python 3.10 update for SIPro, PIPro, RFPro and PEPro

- PIPro radiated emission in conducted EMI analysis

- CEMI analysis on remote, cloud and cluster compute nodes

- Power Integrity conducted EMI Picotest SIC531 PCB example

- Parameter sweeps, e.g. ambient temperature in PIPro-DC simulation

EM Simulation

RFPro Platform

- OpenAccess component instance swept parameters

- Opening complex designs, switching component roles and net re-extraction now faster and using less memory

- Simulation mesh and ports now visible

- Multi-port excitation in field visualization can be exported/imported via .csv or .json file

- 3D component editing, measuring and placement enhancements

- Improved resource management for remote, cloud and cluster simulations

- Improved schematic interoperability between ADS and Virtuoso

Momentum

- TSMC advanced IC process node features supported including width, thickness, resistivity, bias, multi-patterning colors and, damage K.

- Compliance with foundry recommendations for layout scaling and bias sequence

- Ground loss correction no longer applied when substrate stack contains a semi-conductor layer for better accuracy

FEM

- Improved meshing for multi-technology designs

- Improved accuracy for passive device modeling on Silicon substrates

- Gen 2 solver correctly handles temperature dependency of conductor with surface resistance

HFSS Option

- HFSS simulation support in PathWave Design Cloud simulation service

Verification

Design Rule Check (DRC)

- 20 new rules for polygon and edge selection

- Enhanced ADS help navigation for DRC functions

- New Create Rules dialog to facilitate writing ADS DRC rules easily

Layout Versus Schematic (LVS)

- Evaluates parameters passed from top-level hierarchy into a sub-circuit

- LVS from schematic when layout containing SmartMount components is not opened

- Enhanced error reporting during device recognition rule file compilation

Assura DRC Link

- Troubleshooting tips updated in Documentation

Calibre LVS Link

- Troubleshooting tips updated in Documentation

Design Kits

Process Design Kit (PDK) Validator

- Component default callbacks executed prior to test value applications

- Enhancement flexibility and error handling

Power Electronics

SMPS Performance Testbench

- Enables switched mode power supply (SMPS) designers to quickly perform all required simulations on schematic-only or post-layout (including parasitic) designs

Power Electronics Library

- New diode model for PE design

Examples

- New Flyback Converter PE design example

Netlist Import

- Enhanced SPICE netlist import to retain pin names

PE Model Builder

- Enhanced PEMB tool

Virtual Test Bench

- Virtual Test Bench (VTB) are installed by separately downloading the VTB installer from the “Add-On Software / Utilities” section of the PathWave Advanced Design System (ADS) Software download page

- Both Linux and Windows versions of the VTB installer are available depending on your operating system

Documentation

- A new home page that gives quick access to all sections of the documentation

- Improved navigation with the table of contents, breadcrumbs, and On this page

- Product release switcher to view the current page in other supported releases

- On-the-fly PDF generation

- New responsive UI design enables use of help on all device sizes

- Enhanced search UI to allow selecting the scope of the search

- Light and dark theme to suit readability preference

- QR code to open any page on mobile and tablet