The W1465 SystemVue System Architect dramatically cuts design time and verification effort for System Architects and Algorithm Developers doing communications system design at the physical layer (PHY). The W1465 is a product bundle that adds 3 different design flow personalities to the base W1461 SystemVue core environment, enabling a versatile modeling platform for Enterprise workgroups, as well as multi-technology modelers.

The W1465 SystemVue System Architect dramatically cuts design time and verification effort for System Architects and Algorithm Developers doing communications system design at the physical layer (PHY). The W1465 is a product bundle that adds 3 different design flow personalities to the base W1461 SystemVue core environment, enabling a versatile modeling platform for Enterprise workgroups, as well as multi-technology modelers.

The W1465 connects baseband algorithm modeling with FPGA design flow, embedded C++ design flow, and a dedicated RF System Architecture personality. Together they bridge the analog-digital divide for system architects and system verifiers, uniting several disparate toolsets in one “Comms PHY cockpit.”

SystemVue combines an easy to use environment with native polymorphic modeling and proprietary simulation technology to create an enhanced electronic system-level (ESL) design flow that "speaks RF". SystemVue is designed specifically for the task of Communications PHY architects and hardware designers. It allows rapid investigation and creation of algorithms and signal processing architectures, as well as rapid prototyping, verification, and re-use, all the way from math fragment to live test equipment. SystemVue therefore helps system designers in aerospace/defense and commercial wireless turn their physical layer concepts into proven designs faster and with higher confidence than was possible before.

Why should I buy SystemVue System Architect?

- Cut Comms physical layer (PHY) architecture design effort in half

- Yields higher real-world performance and fits within multi-discipline design flows

- Licensed for easy sharing among networked workgroups. The W1465 is particularly popular among larger aerospace/defense organizations as a “standard” environment.

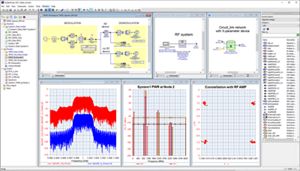

Figure 1. The W1465 SystemVue System Architect bundle connects to enterprise Baseband and RF EDA tools as well as test equipment, making it an extremely versatile environment for workgroups to share and cross-verify sophisticated communications designs.

Who will benefit from SystemVue System Architect?

- System architects can avoid guesswork and make more optimal design choices and partitioning for high-performance PHYs. HDL generation enables rapid prototyping of working hardware, for faster design maturity and evolution.

- HDL hardware designers may incorporate their own HDL IP blocks alongside the blocks supplied by the Hardware Design Kit. This allows for rapid generation of high-quality code, yet allows HDL designers to work at the ESL level in either Gui or text formats, with all the user-interface and verification advantages of the SystemVue platform. SystemVue can be the originating platform for your Comms PHY IP.

- Software-defined Radio (SDR) architects and designers responsible for multiple disciplines will appreciate the productivity gains of proven, HDL generation for routine blocks that are good quality, human readable, and target neutral.

Figure 2. The W1465 integrates baseband modeling interfaces with RF, measurements ,and standards references to provide cross-domain validation and debug of challenging communications systems.

Figure 2. The W1465 integrates baseband modeling interfaces with RF, measurements ,and standards references to provide cross-domain validation and debug of challenging communications systems.

Configuration

Click on any of the items below to learn more about the advantages of the W1465 SystemVue System Architect.

What is included with SystemVue System Architect?

To view all SystemVue configurations, refer to the SystemVue Product Structure & Options Summary.

The W1465 SystemVue System Architect dramatically cuts design time and verification effort for System Architects and Algorithm Developers doing communications system design at the physical layer (PHY). The W1465 is a product bundle that adds 3 different design flow personalities to the base W1461 SystemVue core environment, enabling a versatile modeling platform for Enterprise workgroups, as well as multi-technology modelers.

The W1465 SystemVue System Architect dramatically cuts design time and verification effort for System Architects and Algorithm Developers doing communications system design at the physical layer (PHY). The W1465 is a product bundle that adds 3 different design flow personalities to the base W1461 SystemVue core environment, enabling a versatile modeling platform for Enterprise workgroups, as well as multi-technology modelers.

Figure 2. The W1465 integrates baseband modeling interfaces with RF, measurements ,and standards references to provide cross-domain validation and debug of challenging communications systems.

Figure 2. The W1465 integrates baseband modeling interfaces with RF, measurements ,and standards references to provide cross-domain validation and debug of challenging communications systems.