Más información

segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs

Cómo comprobar la conformidad del receptor USB4 versión 2.0

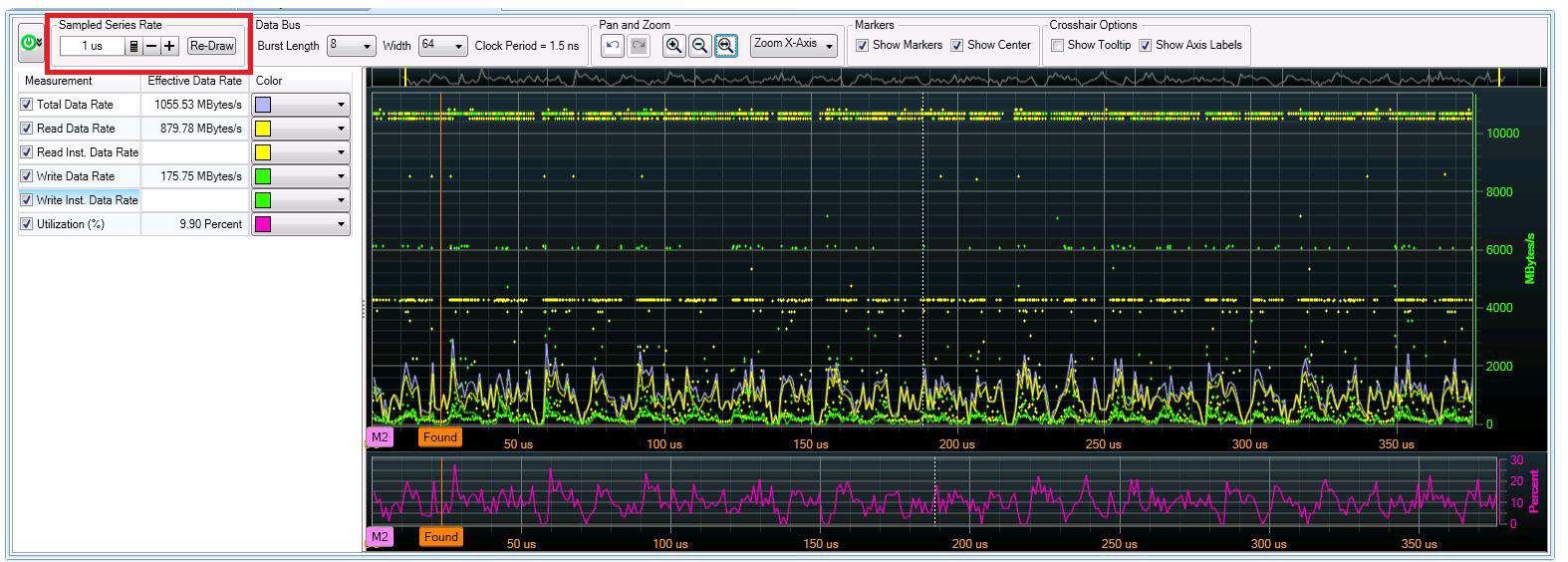

Las pruebas del receptor USB4 Versión 2.0 requieren una calibración precisa de la señal de tensión, una generación de patrones consistentemente repetible y mediciones de la tasa de error de bits. Aprenda a realizar una prueba de conformidad del receptor USB4 Versión 2.0 utilizando un comprobador de relación de bits erróneos (BERT), un osciloscopio de gran ancho de banda, software de aplicación de prueba del receptor USB y la utilidad USB-IF SigTest.

Más información