# **Innovations in EDA Webcast**

Series

August 2, 2012

IC, Laminate, Package Multi-Technology PA Module **Design Methodology** Journal Free 1-hour Webcast

August 2 - 10 AM (Pacific Time)

**Jack Sifri MMIC Design Flow Specialist**

IC, Laminate, Package Multi-Technology PA Module Design Methodology

Realizing the Multi-Technology Vision within a fully integrated design flow in ADS

Jack Sifri MMIC Design Flow Specialist

August 2nd, 2012

#### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

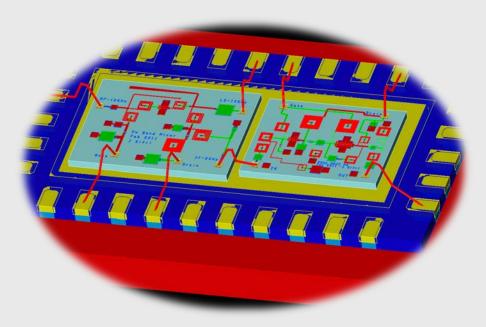

Typical Example:

Complex ICs in multi-chip RF modules:

The New iPad

Typical Example:

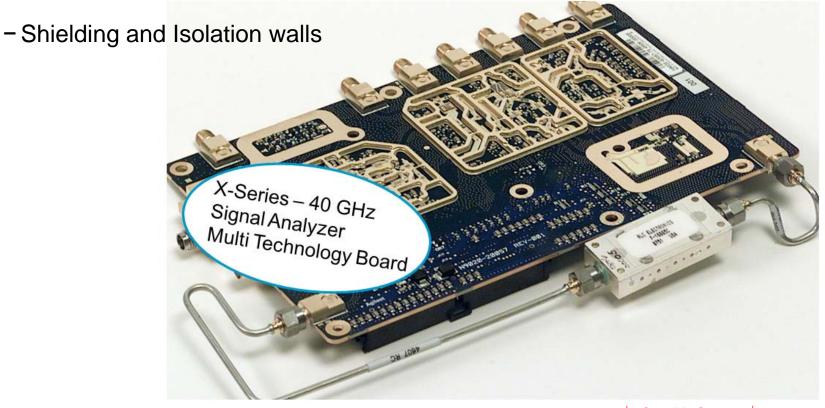

Agilent's X-Series 40 GHz Signal Analyzer Multi Technology Board

# Multi Technology Example (Agilent EMG)

- Stripline Filter on PC Board

- Designs with SMT packages and bare die components (wire bonded)

- Integrated Circuits Designs and Thin Film Circuit Designs

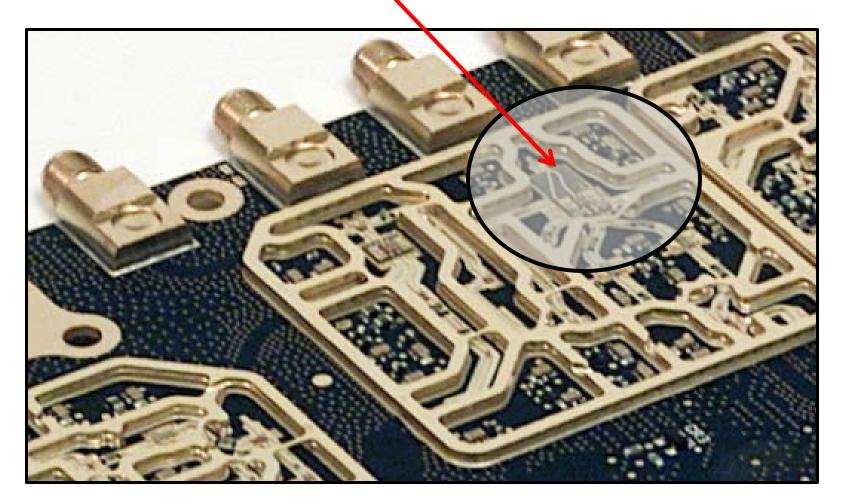

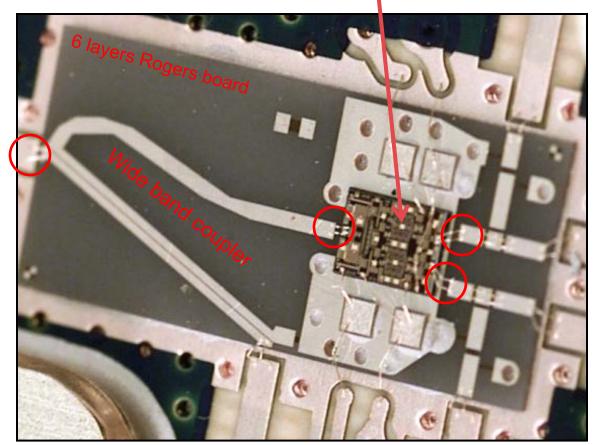

# Zooming on the Thin Film IC Interface

Wide Band LO Distributing Amp

Copyright © 2014 Keysight Technologies

Page 7

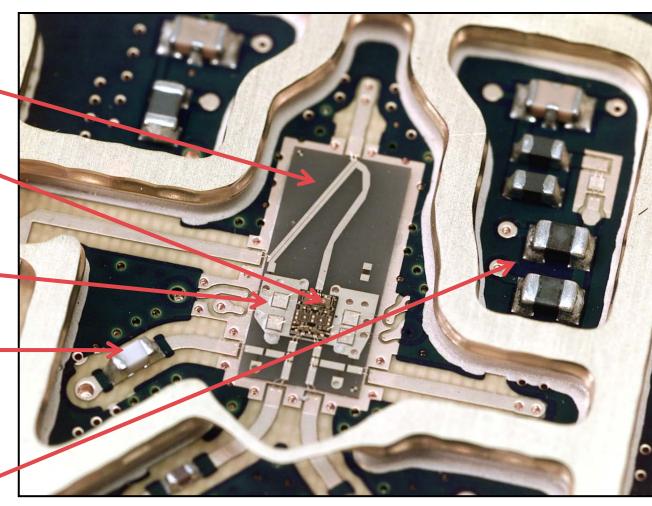

# Thin Film Coupler / LO Distributing Amp Interface

- 6 Layers Rogers Board

- Octave wideband coupler

- GaAs LO distributing amp

- Bond wired and epoxy SMT Caps (DC)

- Blocking Capacitor to Edge connector

- available LO for testing mixers

- Filtering DC Lines

Copyright © 2014 Keysight Technologies

# Board / Laminate / IC/ SMT / Bondwires

A multi-technology module example requires Full 3D FEM Simulation

Wide band LO distributing amp swept for use at different bands

Bond wires / coupler / IC interface caused unleveled ripple in the wide band output signal

#### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

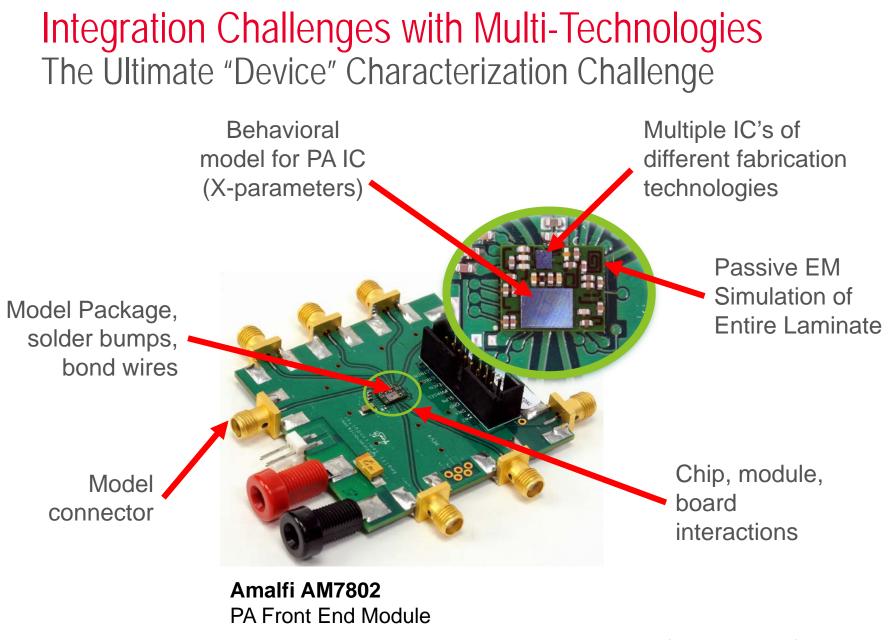

IC, Laminate, Package Multi Technology Module Design Challenges

Design flows are not able to address multiple technology designs

- IC, laminate, package, and PCB need to be designed together

- EM interactions between substrates need to be modeled and accounted for

- The need to move from disjointed tools design flows to simplified integrated flows

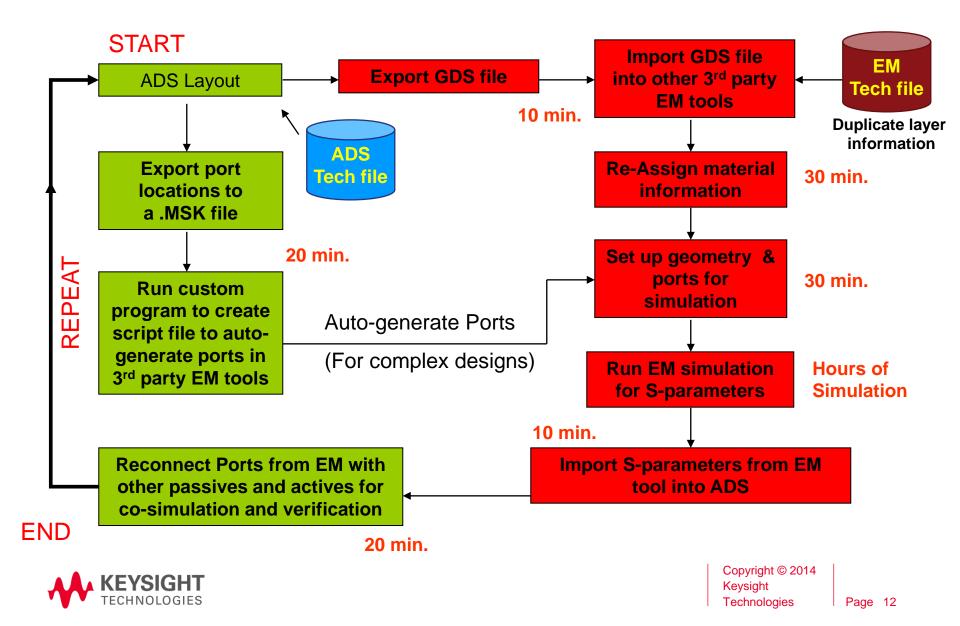

# EM Modeling Process in a Disjointed Design Flow

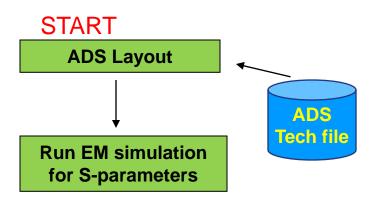

# EM Modeling Process in an Integrated Design Flow

Finish

#### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

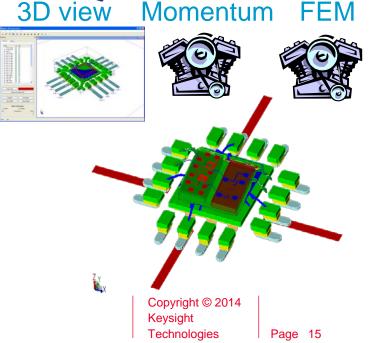

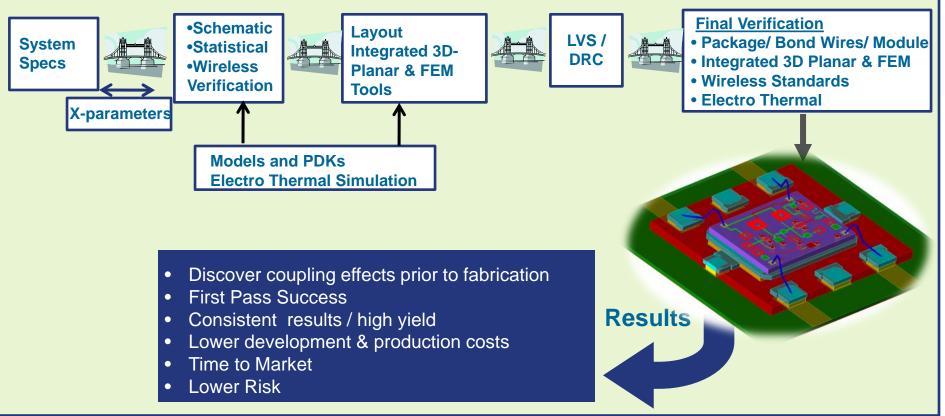

# Multi-Technology Design Methodology

#### Multi-technology EM Simulation

- Discover coupling efforts prior to fabrication

- More effectively optimize design elements for final packaging

- More easily make design trade-offs

- Help diagnose and solve performance problems

Fully Integrated Design Flow in ADS 2011 and 2012 System; Circuit; Physical; Thermal; Planar/3D EM; Wireless Verification

#### ADS Multi Technology Integrated Design Environment

No Walls and no loops in this design process; Fully Integrated Flow; One designer completes and verifies the full design all in one design environment

Copyright © 2014 Keysight Technologies

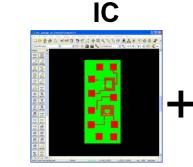

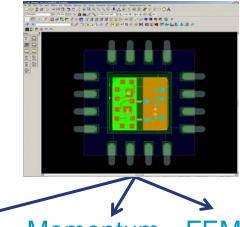

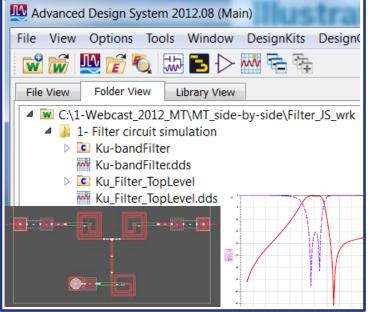

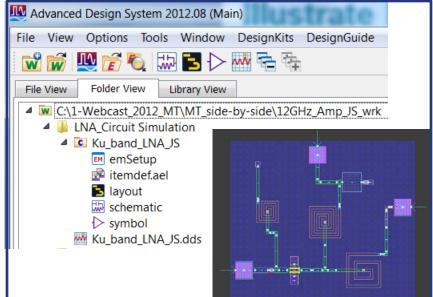

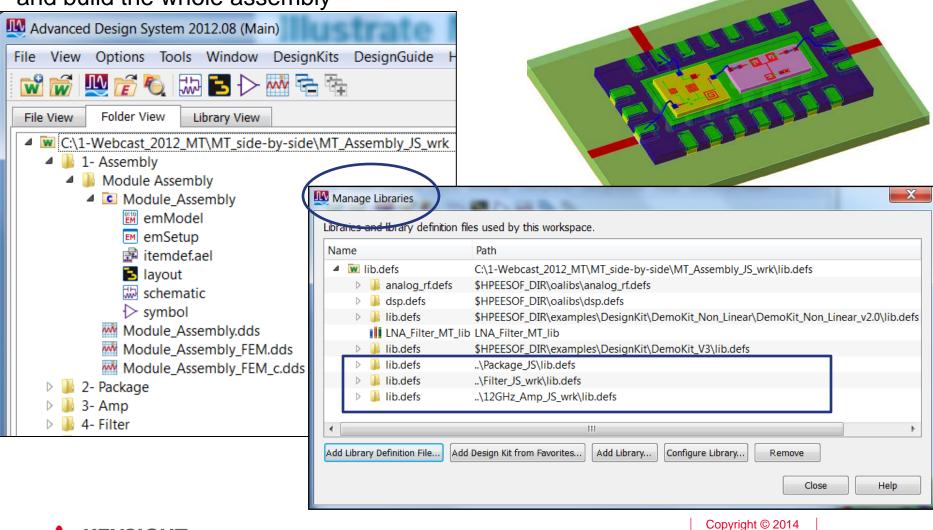

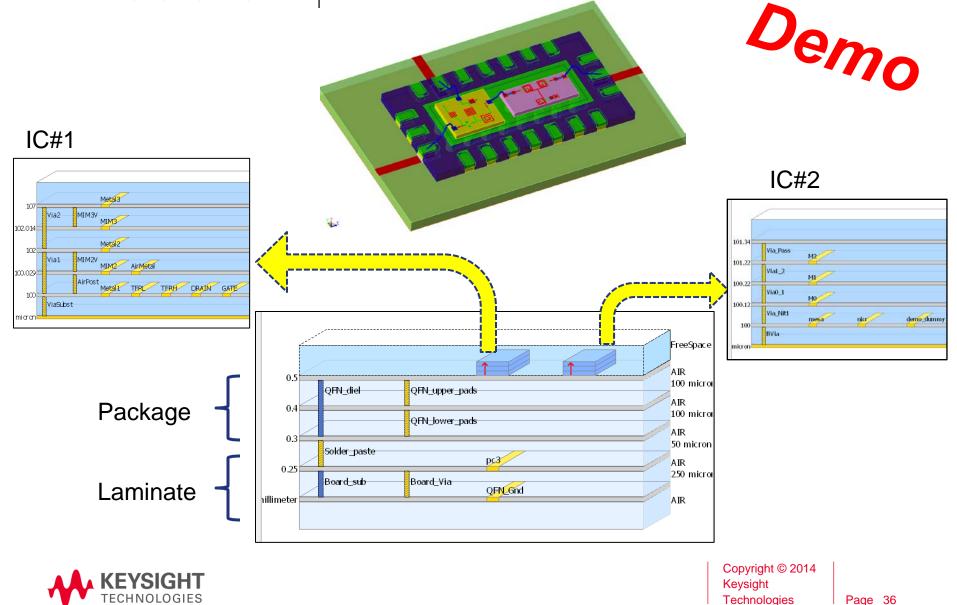

#### Multi-Technology Design Methodology Design IC #1 (IPD – Filter)

#### Design IC #2 (LNA)

Design Package/Laminate

w

File View

M Advanced Design System 2012.08 (Main)

Folder View

File View Options Tools Window DesignKits De

Library View

😿 🖳 📂 🍋 🐺 🔁 🗁 째

Copyright © 2014 Keysight Technologies

Page 17

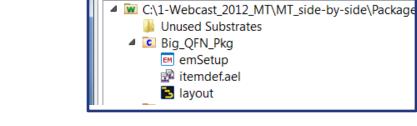

# Multi-Technology Design Methodology

# Bring in all the libraries together and build the whole assembly

Keysight Technologies

Page 18

#### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

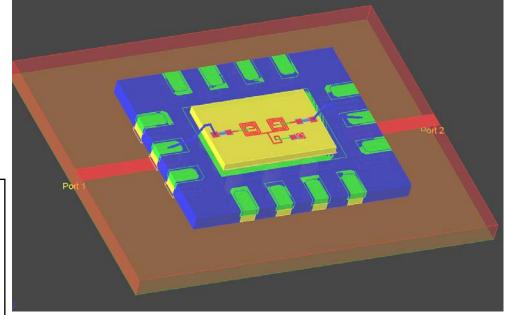

# Example: Packaged LTE PA on Laminate

#### - Two Stage LTE PA built on a GaAs substrate

• Placed onto a DFN package and mounted on a laminate board.

Y ZX

Copyright © 2014 Keysight Technologies

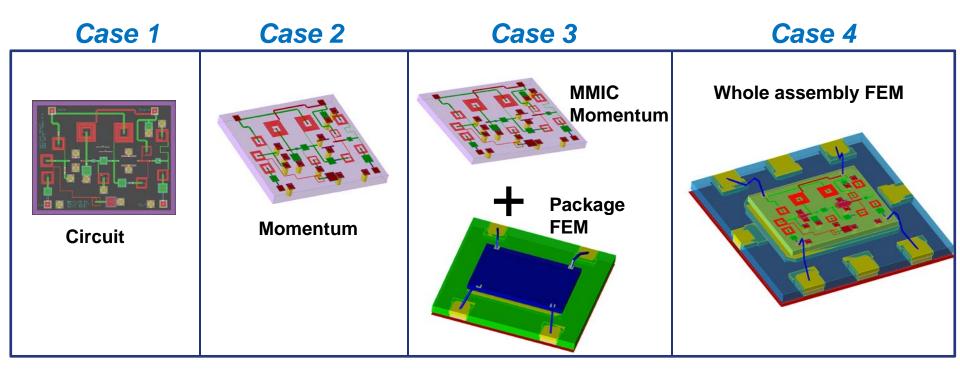

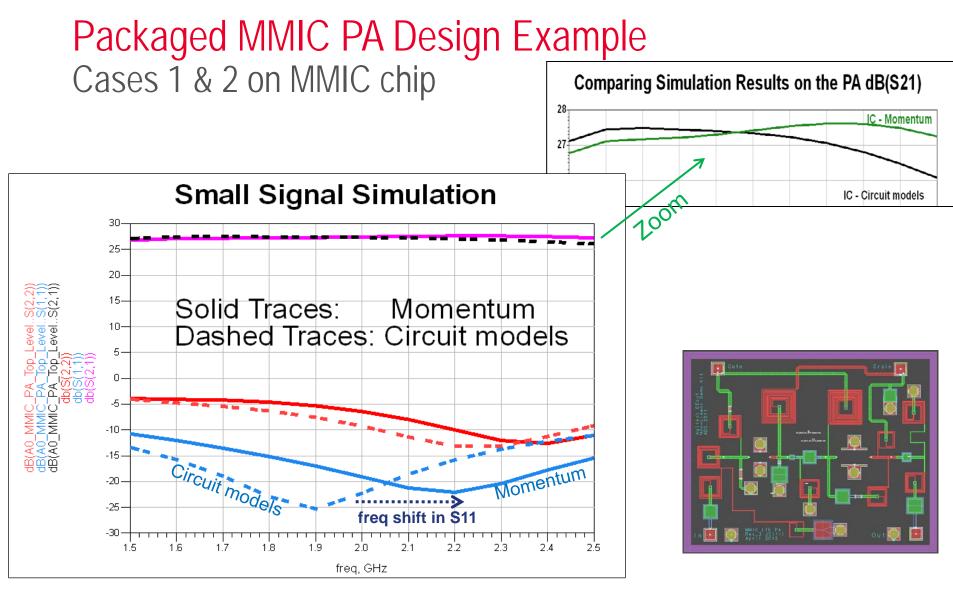

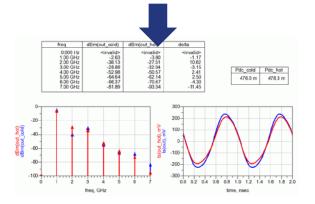

# Packaged MMIC PA Design Example

Case 1: MMIC PA - Circuit models Simulation

**Case 2:** MMIC PA – Momentum Simulation

- **Case 3:** Combine MMIC Momentum & FEM of Package

- **Case 4:** FEM on the Whole Module

Input Matching Network is shown to exhibit coupling effects (freq shift)

Copyright © 2014 Keysight Technologies P

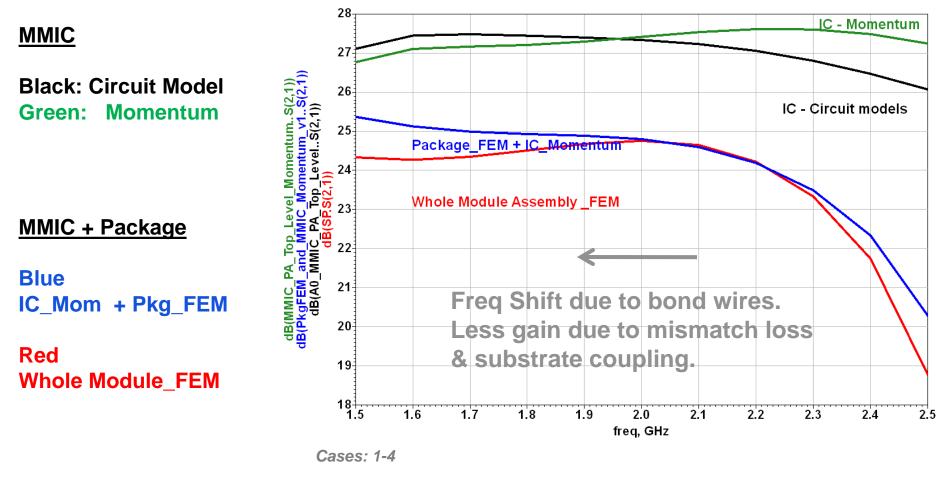

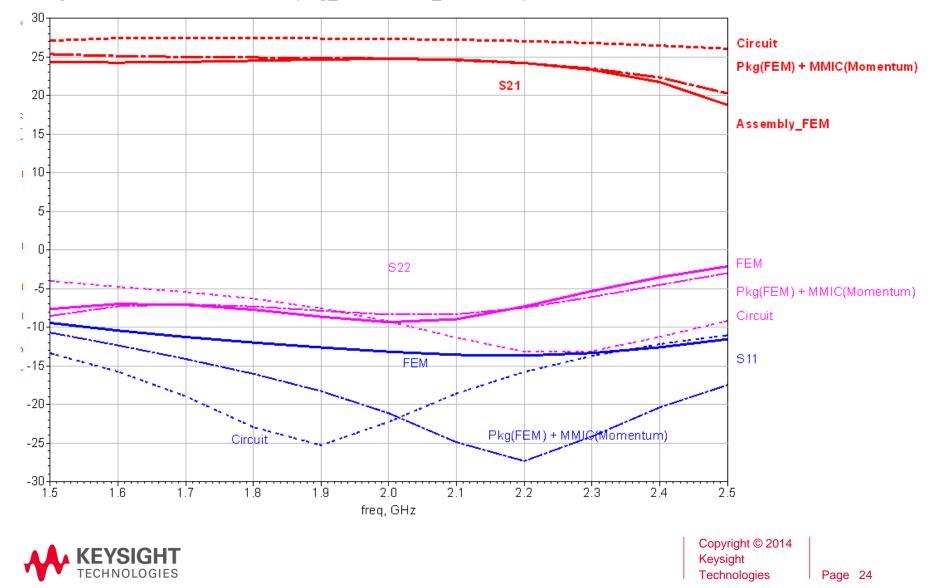

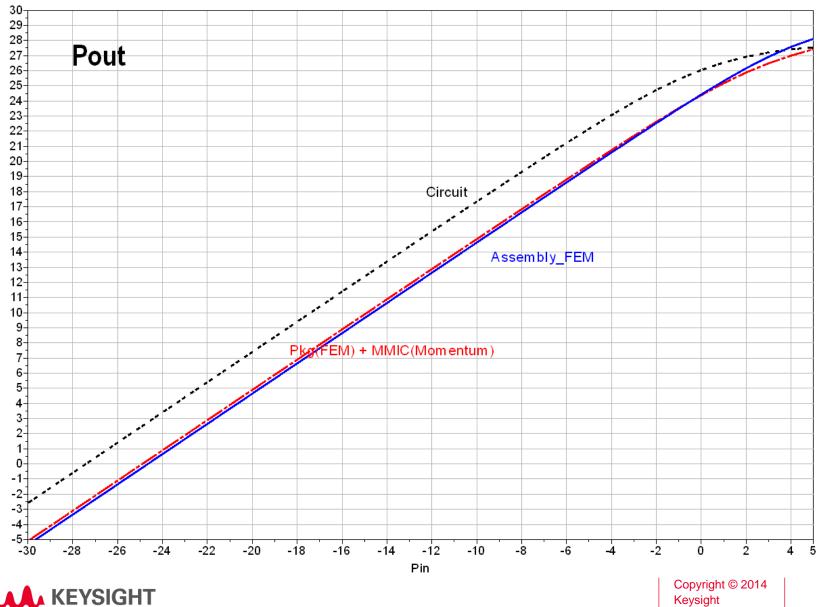

## Packaged MMIC PA - Results Four different simulation results (case 1-4)

#### Comparing Simulation Results on the PA dB(S21)

#### Compare Module FEM Results with (Pkg\_FEM + MMIC\_Momentum) and with Circuit simulation results

# Packaged MMIC PA Design Example Results

CHNOLOGIES

Technologies Pag

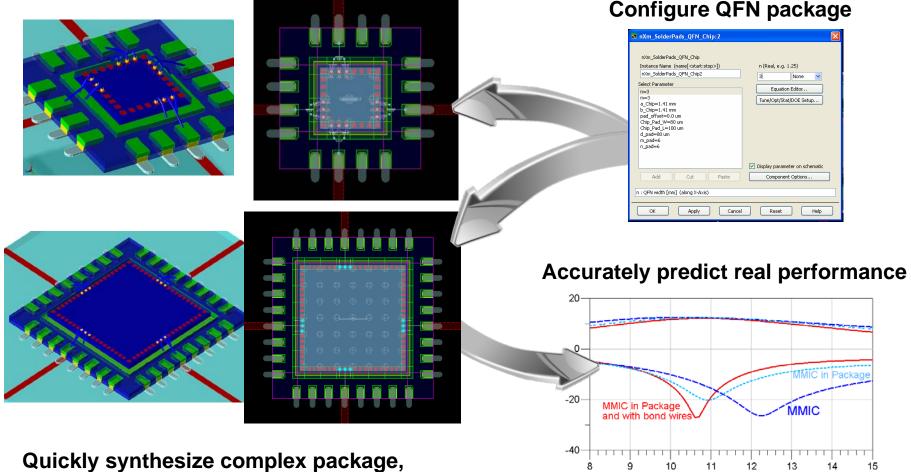

## **OFN Designer in ADS** Predict Packaged Performance in Minutes

combine with IC & PCB data

Freq, GHz Performance w/ & w/o package

> Copyright © 2014 Keysight Technologies Page 26

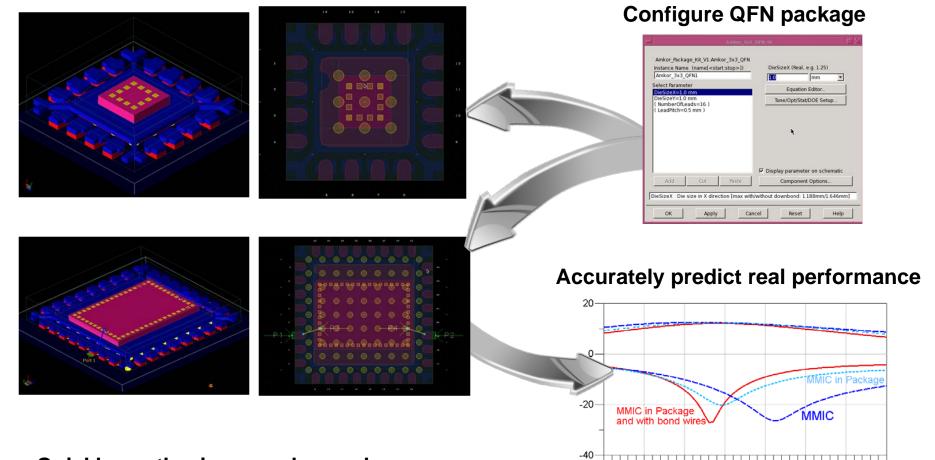

### Amkor Package Design Kit for ADS Predict Packaged Performance in Minutes

Quickly synthesize complex package, combine with IC & PCB data

8 9 10 11 12 13 14 15 freq, GHz Performance w/ & w/o package Copyright © 2014

**Keysight**

**Technologies** Page 27

#### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

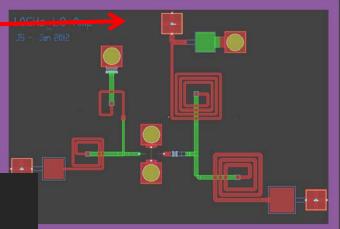

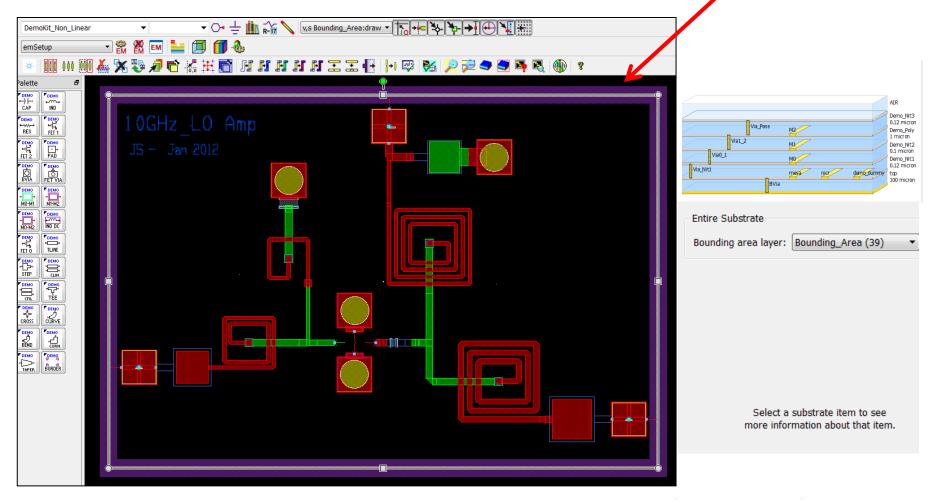

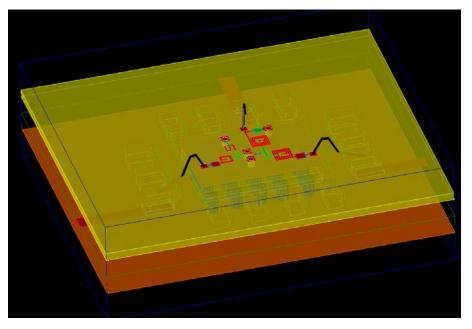

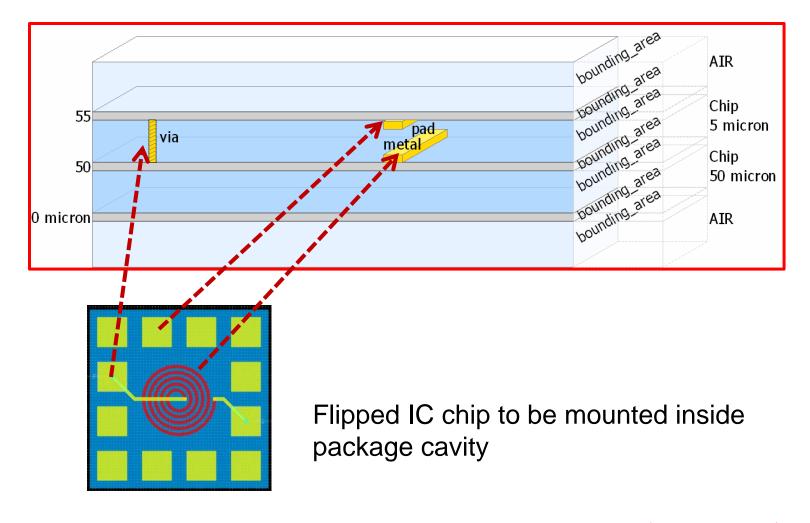

# Bounding the IC within the Package/ Laminate Assembly

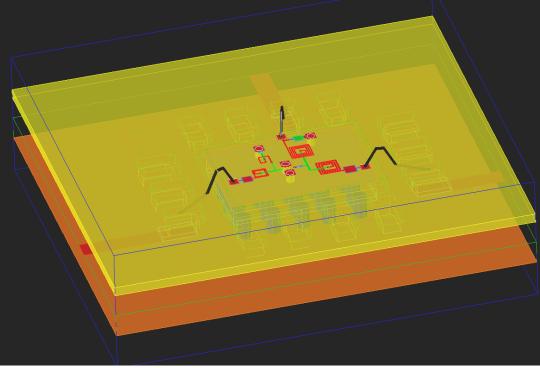

# A Word on Bounding the IC using "Boundary Area Layer"

- Layout has no Bounding Area

- 3D view shows the MMIC substrate extending out through the bond wires (Results in inaccurate FEM simulation results)

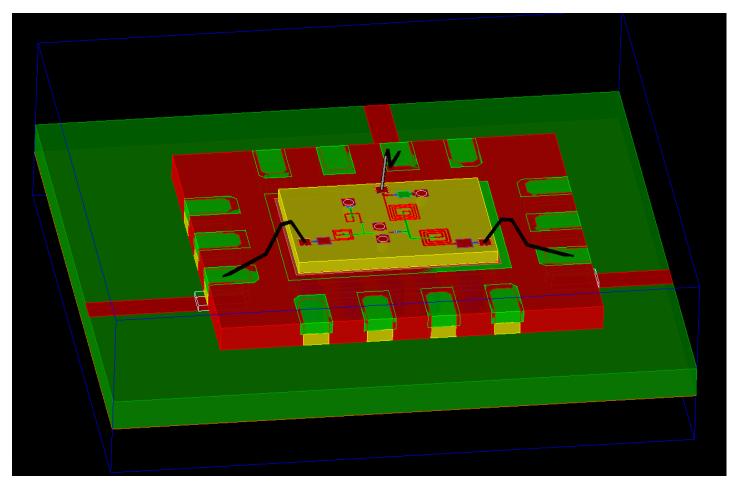

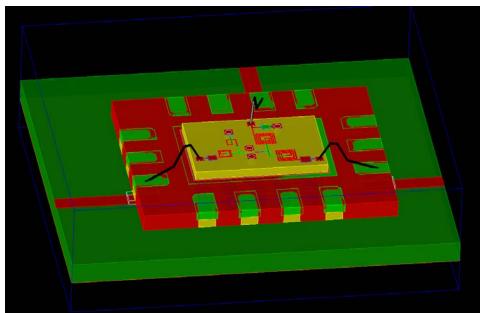

# Multi Technology Module Setup with Bounding the IC

- Bounding Area layer box has been added in the Layout as shown.

- 3D view (next page) shows the bounding of the MMIC for FEM simulation

Copyright © 2014 Keysight Technologies

# Multi Technology Module Setup with Bounded IC

- 3D view shows how the use of "Bounding Area Layer" (last page) has resulted in bounding IC substrate (cookie cut) for FEM simulation

Copyright © 2014 Keysight Technologies

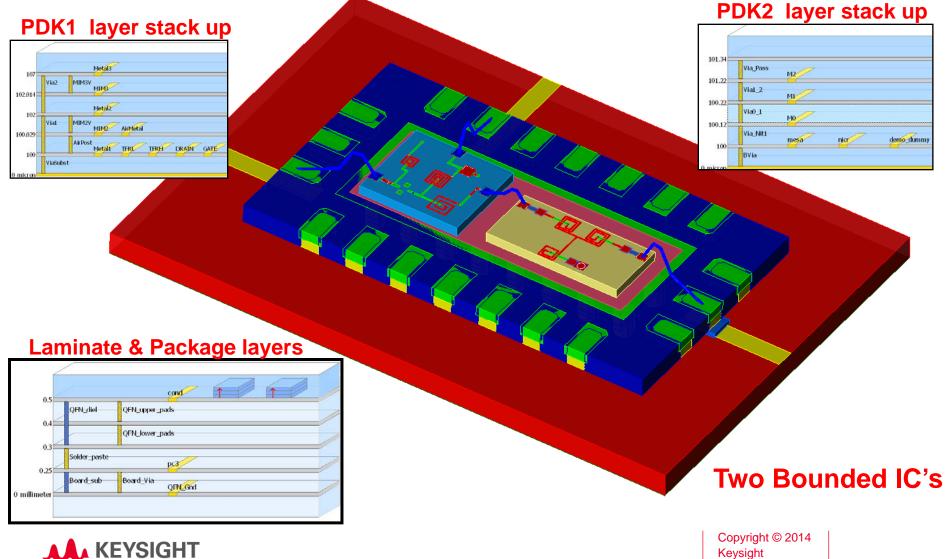

## Multi Technology Module Setup With and without Bounding area layer

Before adding Bounding Layer to the IC

#### After adding Bounding Layer to the IC

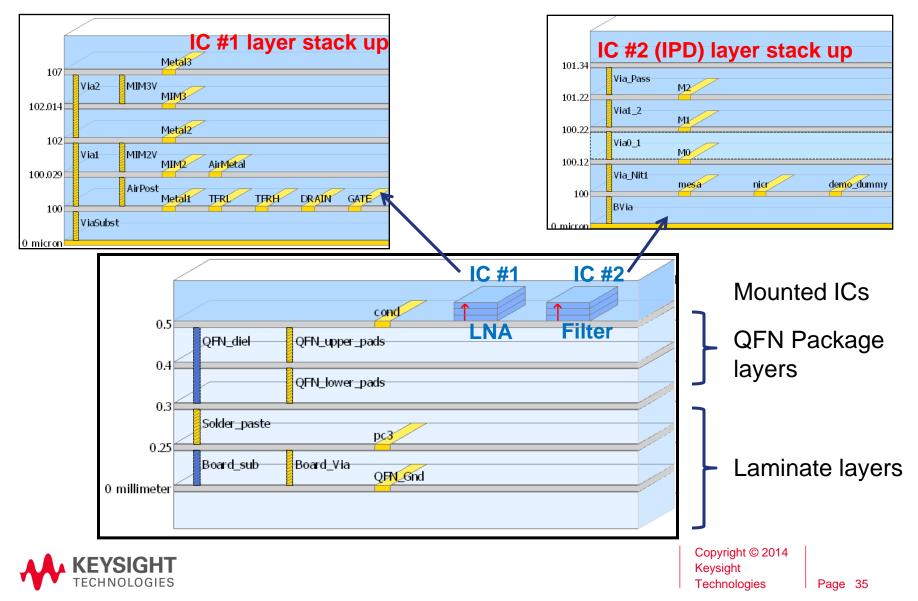

## Multi Technology FEM Simulation Set up Ku band LNA (PDK1) followed by Ku band Filter (PDK2)

TECHNOLOGIES

Page 34

**Technologies**

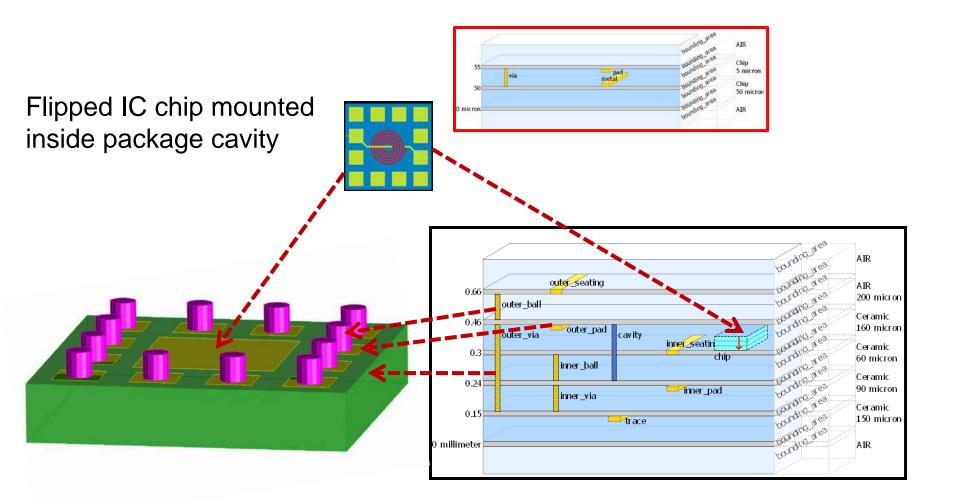

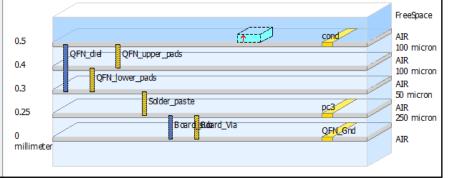

## Multi Technology Module Layers Stack up Nested Technology substrates

### Multi Technology 3D FEM Simulation in ADS 2012 Substrate stackup

## IC, Laminate, Package Multi Technology PA Module Design

### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

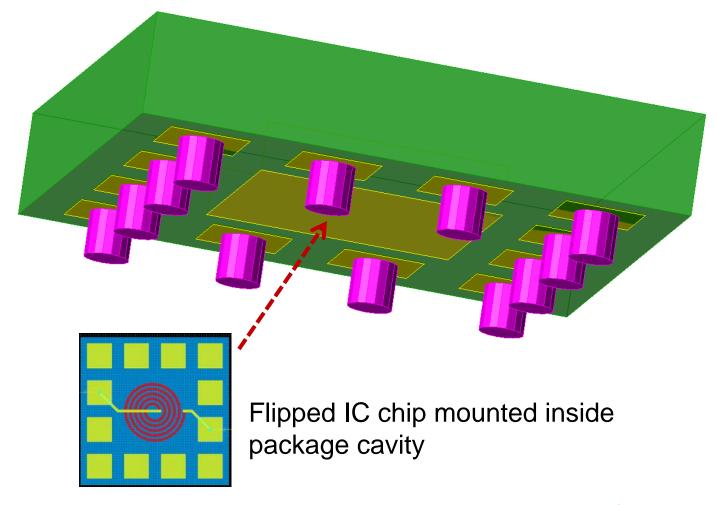

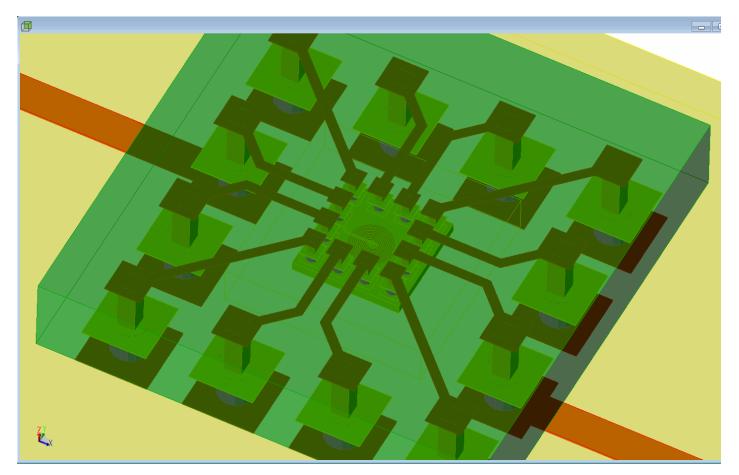

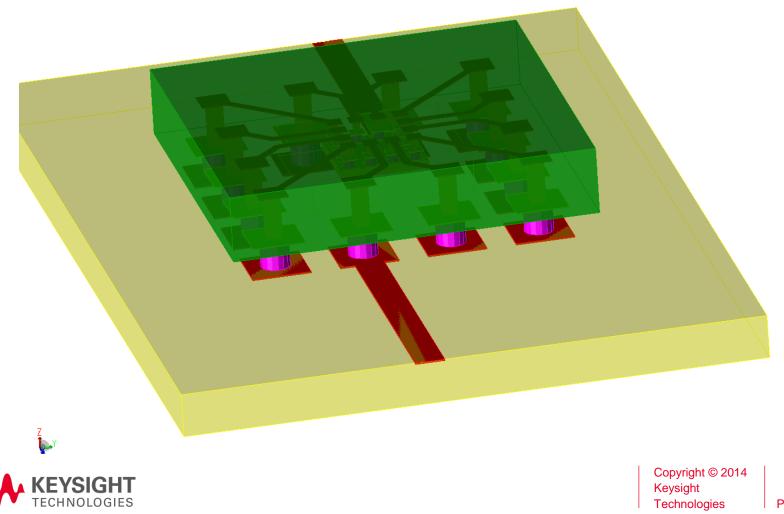

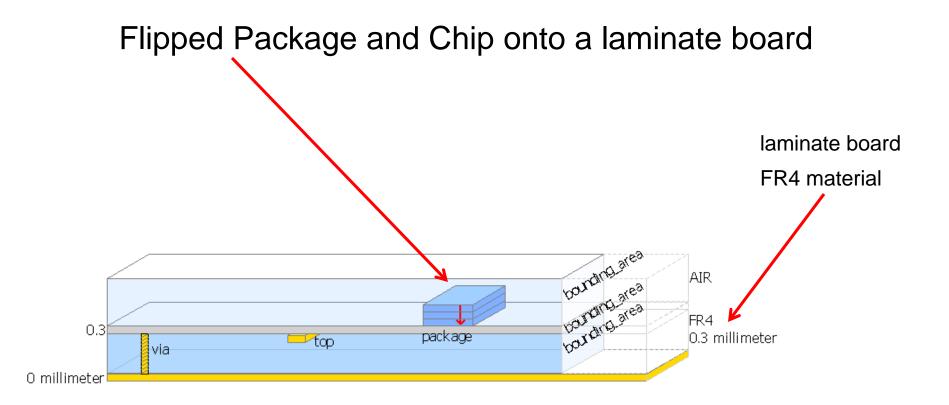

### Flipped Package ready to mount onto a board

### Flipped Package mounted onto a board

Flipped Package mounted onto a board

# Flipped IC chip mounted inside package cavity

Flipped Package mounted onto a board – side view

## IC, Laminate, Package Multi Technology PA Module Design

### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

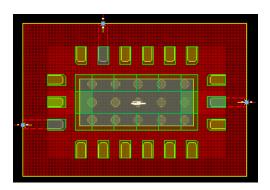

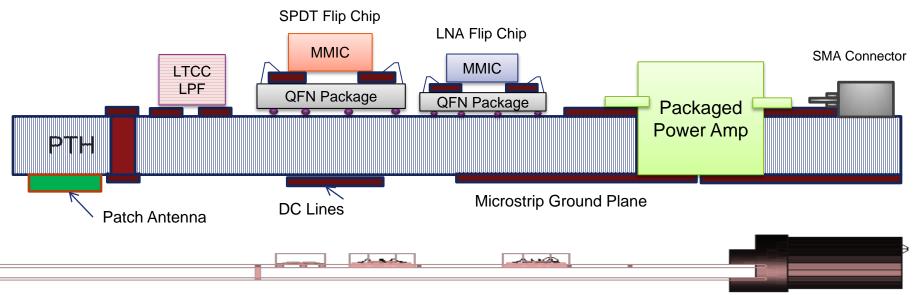

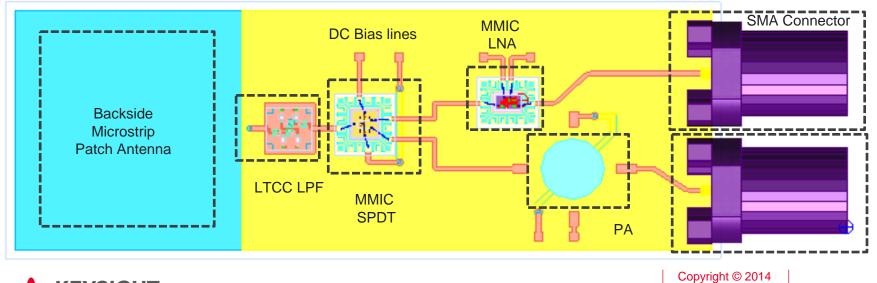

## Example: Transceiver using Multi Technology

- Transceiver consists of mainly seven major technologies:

- 1. Antenna: single layer C-band microstrip patch antenna

- 2. Power Amplifier X-parameter file of MMIC power amplifier

- 3. LTCC BPF : 3 pole filter based on 6 layer LTCC technology

- 4. 3D SMA Connector from EMPro library

- 5. Standard QFN Package for LNA and switch

- 6. MMIC SPDT switch

- 7. MMIC LNA

## **Transceiver Cross Section View**

KEYSIGHT TECHNOLOGIES Keysight Technologies Page 47

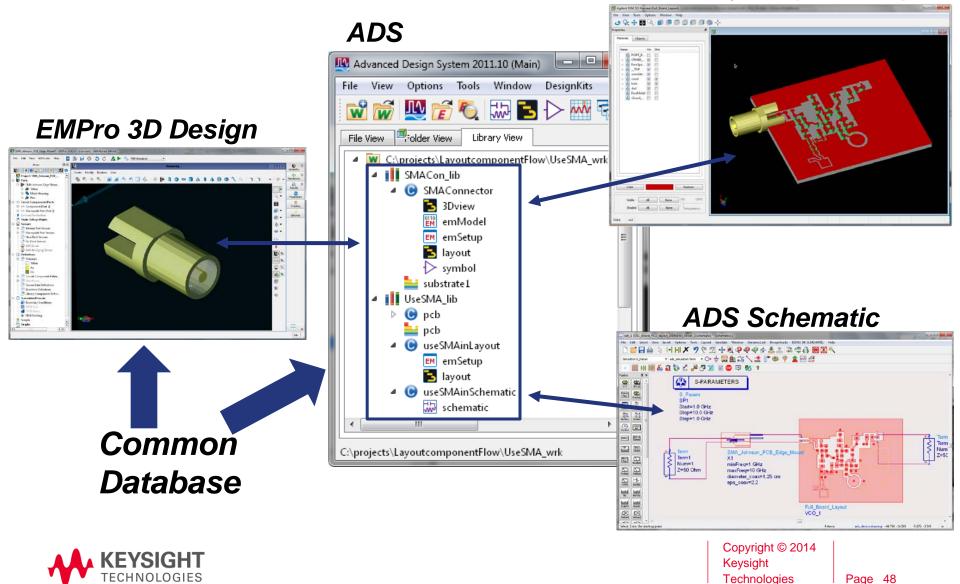

## EMPro 2012 3D EM Components Improved ADS Integration

### ADS Layout (3D View)

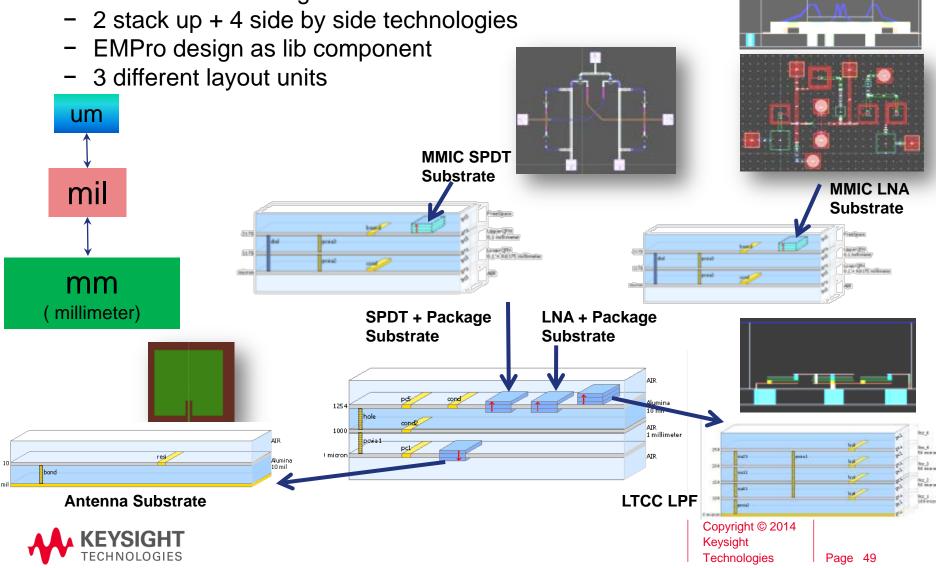

## **Transceiver Parts and Technologies**

- Total 12 equivalent layer board

- 7 different technologies

## IC, Laminate, Package Multi Technology PA Module Design

### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

- 5. Conclusion

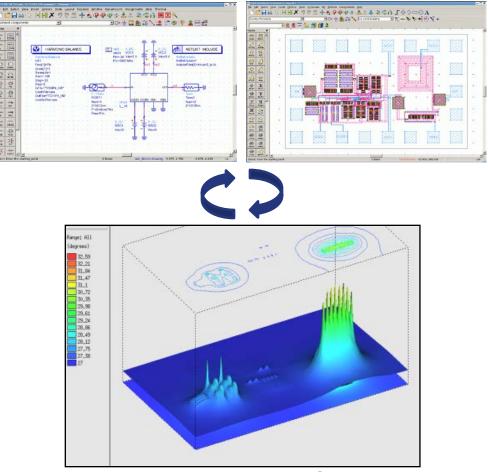

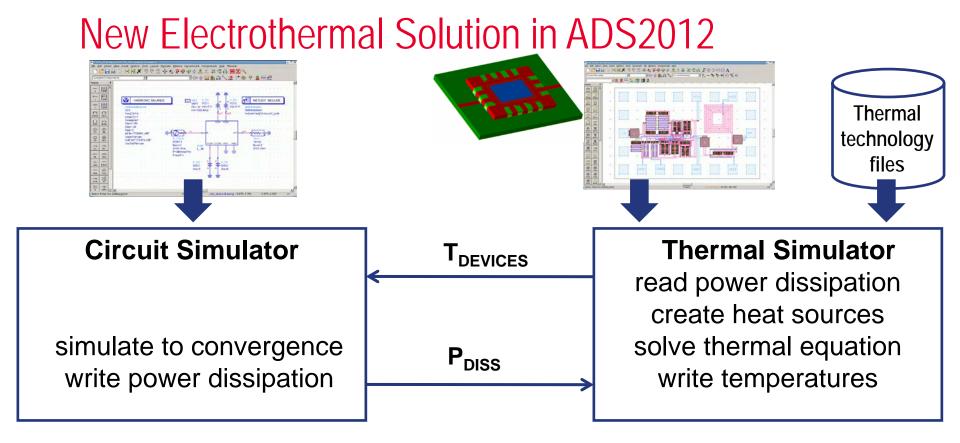

- Improves high power MMIC / RFIC designs

- Delivers 'thermally aware' circuit simulation results

- Includes effects of package and PCB

- Easy to set up and use from within ADS

- Works with all simulation types: DC, AC, SP, HB, Transient, Envelope

**ADS Schematic**

ADS Layout

Integrated Thermal Solver

Copyright © 2014 Keysight Technologies

Page 51

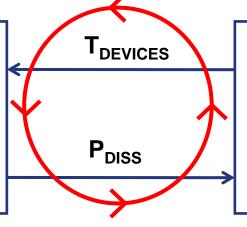

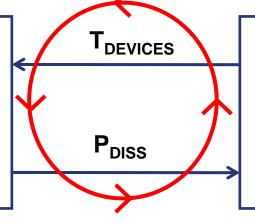

### **Circuit Simulator** read temperatures use previous solution simulate to convergence write power dissipation

### **Thermal Simulator**

read power dissipation create heat sources solve thermal equation write temperatures

Iteration loop is done automatically until powers and temperatures are self-consistent

### **Circuit Simulator** read temperatures use previous solution

simulate to convergence write power dissipation

### **Thermal Simulator**

read power dissipation create heat sources solve thermal equation write temperatures

Iteration loop is done automatically until powers and temperatures are self-consistent

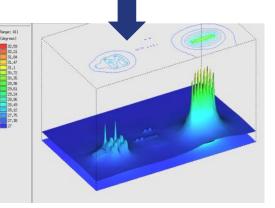

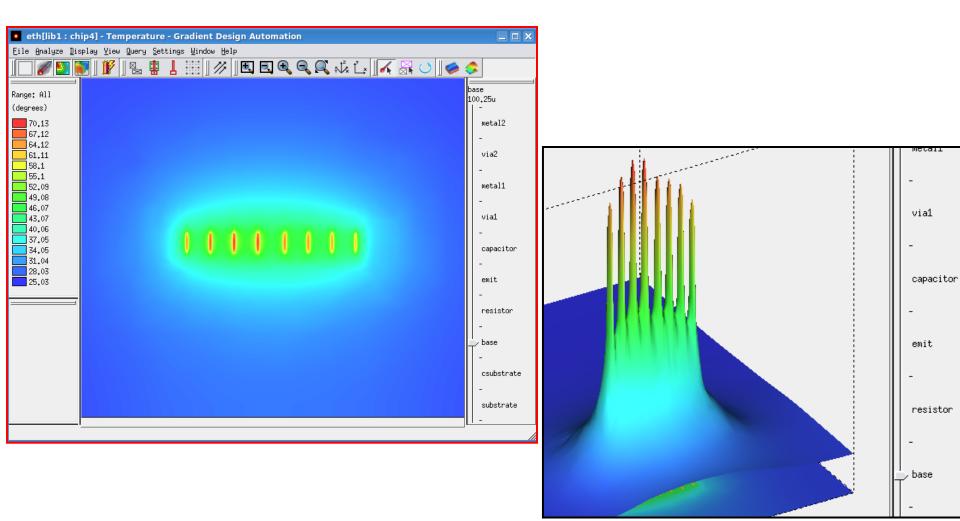

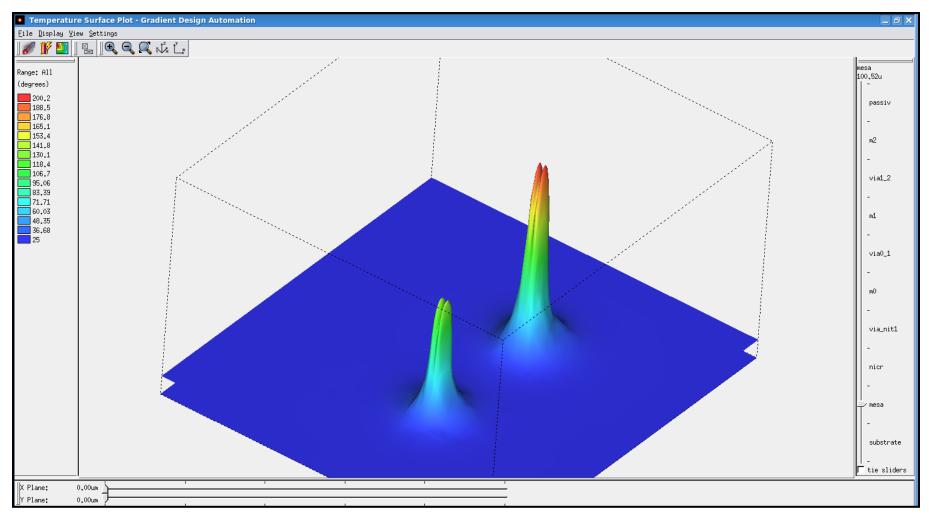

## Temperature Profile – Active Base Region

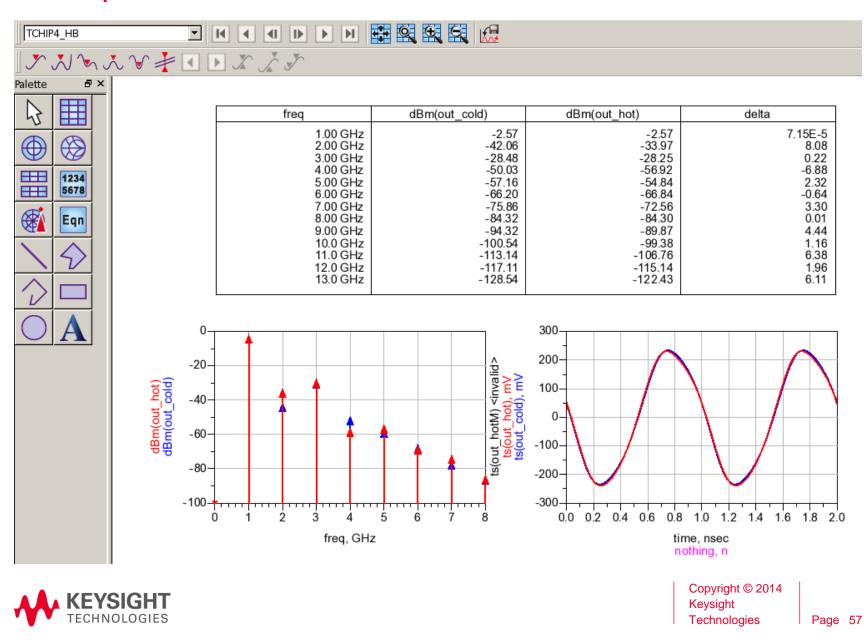

## **Output Results**

## **Time-Domain Results**

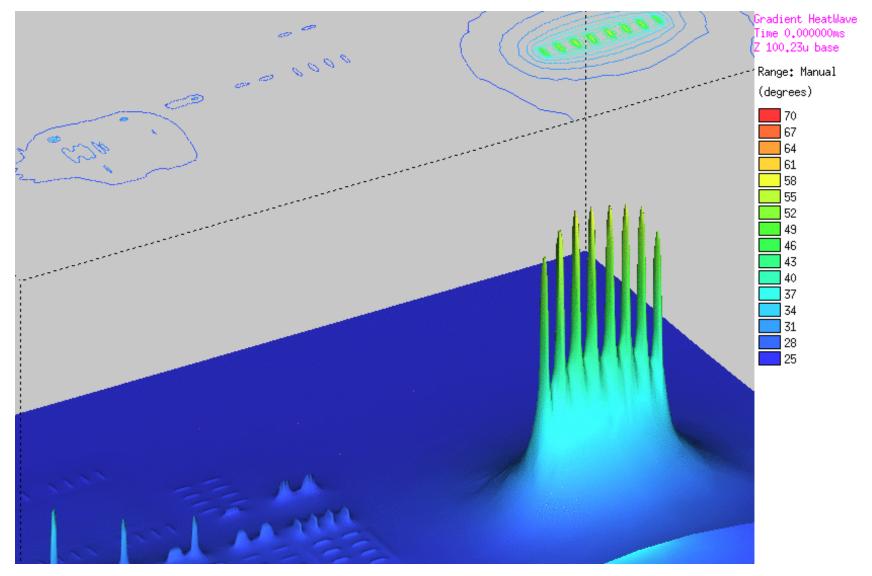

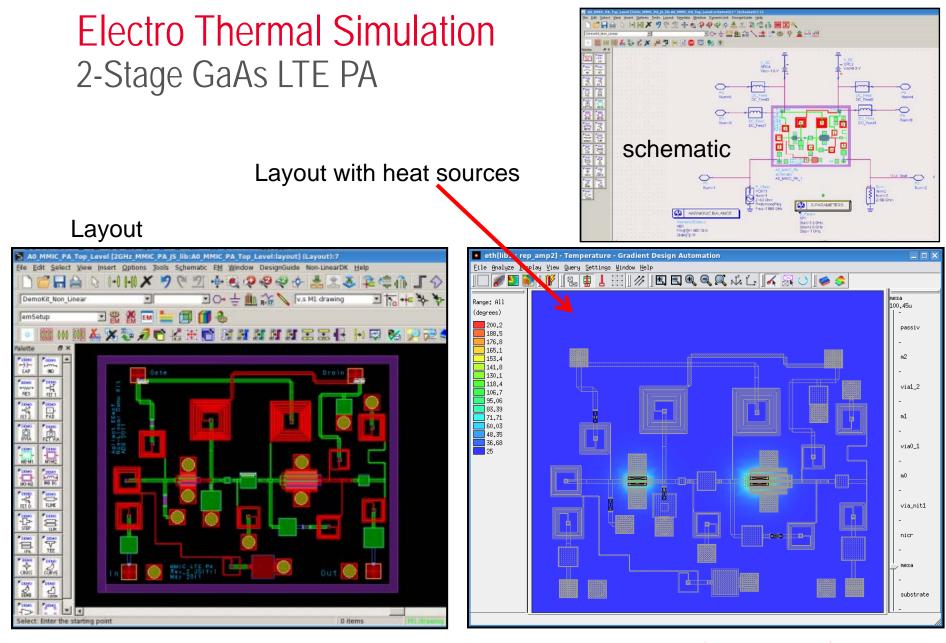

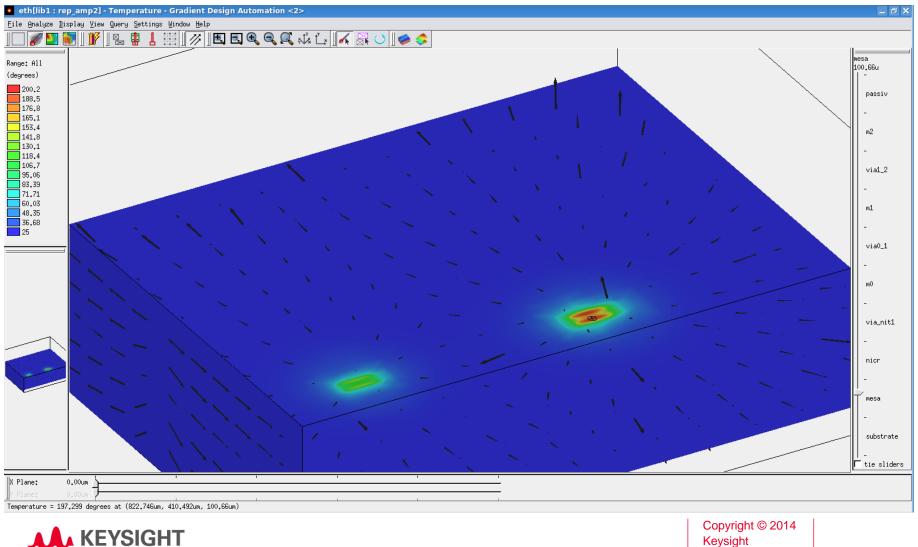

## Electro Thermal Simulation 2-Stage GaAs LTE PA

## **Electro Thermal Simulation – Heat Flux** 2-Stage GaAs LTE PA

Page 61

**Technologies**

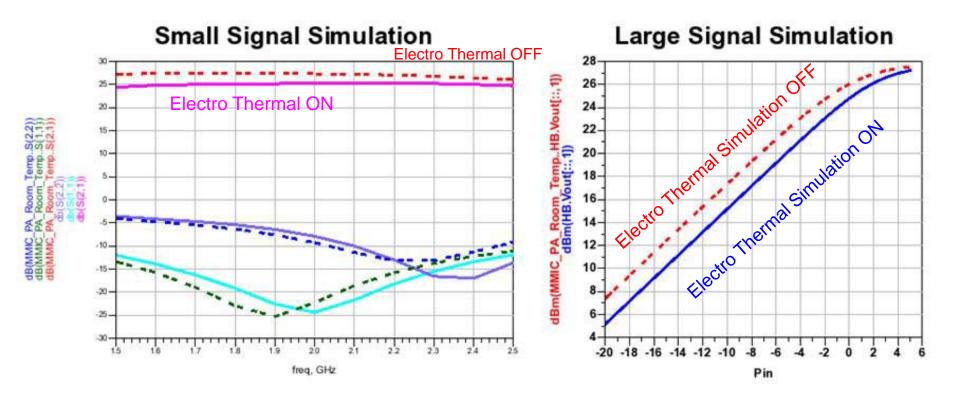

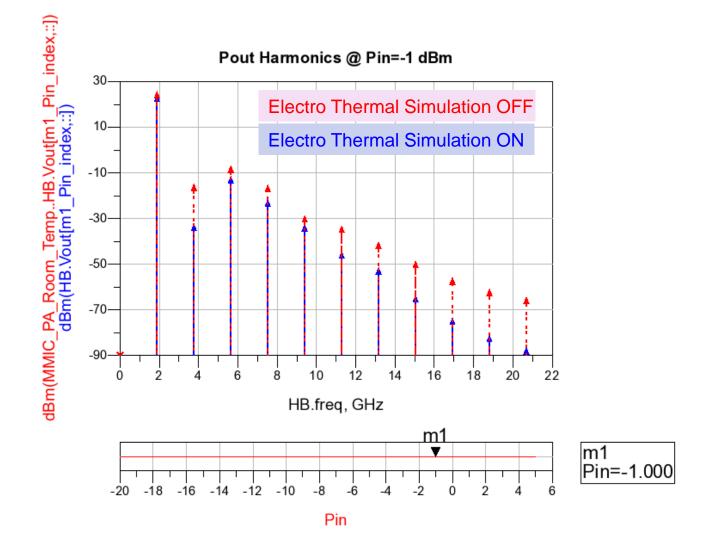

## Electro Thermal Simulation Results 2-Stage GaAs LTE PA

Solid Lines: Electro Thermal Simulation ON Dashed Lines: Electro Thermal Simulation OFF

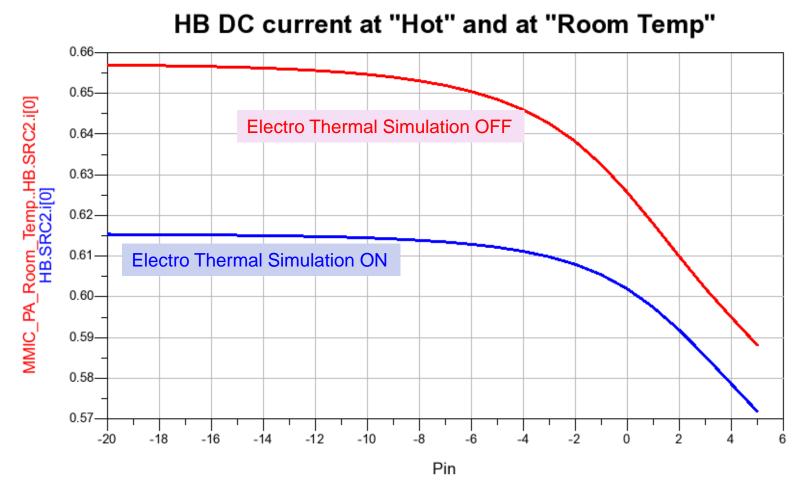

## Electro Thermal Simulation Results HB DC current at Hot Vs Room Temp

## Electro Thermal Simulation Results Harmonics at Hot Vs Room Temp

## IC, Laminate, Package Multi Technology PA Module Design

#### <u>Agenda</u>

- 1. Multi technology Examples

- 2. Design Challenges

- 3. Improved Design Methodology

- 4. Illustrate with few applications

- Single chip module

- Multi chip module

- Flip chip /solder bumps module

- Transceiver module

- Electro thermal simulation

5. Conclusion

## Summary

- RF design has moved to complex ICs in multi-chip RF modules

- Today's design flows are not able to address multiple technology design

- The IC, laminate, package, and PCB need to be designed together

- Electro-magnetic interactions between substrates need to be modeled

- ADS 2012 EDA software is able to address these multi-technology design challenges

Keysight EEsof EDA "Innovative Solutions, Breakthrough Results"

## Hands-on Workshop Available

A Hands-on Workshop is available for training

## Workshop Outline

| Section 1  | Starting a New Workspace "Module"                | Page 5  |

|------------|--------------------------------------------------|---------|

| Section 2  | Adding Libraries to our Module Workspace         | Page 12 |

| Section 3  | Creating a new Cell for Module FEM simulation    | Page 21 |

| Section 4  | Nested Technology / View Specific Configuration  | Page 28 |

| Section 5  | Nested Technology Setup                          | Page 31 |

| Section 6  | Building the Module Assembly                     | Page 41 |

| Section 7  | Placing and Configuring the Bond Wires           | Page 46 |

| Section 8  | Creating the Module Layer Stack-up Substrate     | Page 52 |

| Section 9  | Defining the IC Bounding Area for FEM Simulation | Page 63 |

| Section 10 | FEM Simulation Set-up and Results                | Page 76 |

## You Are Invited

www.keysight.com/find/eesof-innovations-in-eda www.keysight.com/find/eesof-webcasts-recorded

Dr. Larry Dunleavy, President & CEO Modelithics Inc.