What are you looking for?

Signal Integrity Workshop

Designing serial links and memory interfaces used to be simpler. You look at the previous design, make some changes, fabricate a physical prototype, fix a few things in the design based on the fabricated prototype, and you are good to go. Nowadays, as the technology quickly advances and the demand for higher data rate intensifies, the old fabricate-and-fix approach is no longer timely and profitable.

Designing serial links and memory interfaces used to be simpler. You look at the previous design, make some changes, fabricate a physical prototype, fix a few things in the design based on the fabricated prototype, and you are good to go. Nowadays, as the technology quickly advances and the demand for higher data rate intensifies, the old fabricate-and-fix approach is no longer timely and profitable.

If you don’t have a virtual prototype and a robust simulation workflow to troubleshoot before fabrication, you are going to lag behind competitors and miss the optimal product release window. To avoid losing profit and missing critical time to market, reliable simulation tools are necessary.

PathWave Advanced Design System (ADS) provides versatile simulation capabilities for both serial links and memory interfaces, so you can stay ahead of any competition. You can find workshop content and tutorials below to help you get started on creating virtual prototypes and simulating your serial links and memory interfaces.

Unlock Your SI Analysis Potential with ADS 2022 (August 13, 2021)

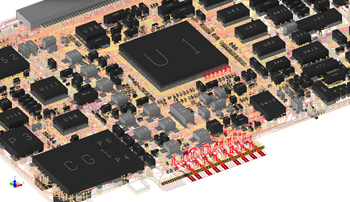

This workshop covers both serial link and memory interface analyses. The workshop uses a serial link on Xilinx’s FPGA to demonstrate ways you can unlock your SI analysis potential. You will learn to perform 3D EM simulations with SIPro and use ADS to perform additional channel-related simulations. An introduction to ADS’ Memory Designer gives you a quick look at how ADS increases your memory design efficiency.

- Unlock_SI_Analysis_Potential_with_ADS2022.zip (ZIP, 139.5 MB) includes:

- Unlock Your SI Analysis Potential with ADS2022.pdf (PDF, 13.5 MB)

- unlock_si_potential_wrkshpADS2022_wrk.7zads (ZIP, 127.8 MB)

Unlock Your SI Analysis Potential with ADS 2021 (April 14, 2021)

This workshop covers both serial link and memory interface analyses. The workshop uses a serial link on Xilinx’s FPGA to demonstrate ways you can unlock your SI analysis potential. You will learn to perform 3D EM simulations with SIPro and use ADS to perform additional channel-related simulations. An introduction to ADS’ Memory Designer gives you a quick look at how ADS increases your memory design efficiency.

- Unlock_SI_Analysis_Potential_with_ADS2021.zip (ZIP, 130.3 MB) includes:

- Unlock Your SI Analysis Potential with ADS2021.pdf (PDF, 13.2 MB)

- unlock_si_potential_wrkshp_wrk.7zads (ZIP, 118.7 MB)

Apply the 3-step Approach to Solve any SI Problems

This workshop is great for starting your signal integrity journey. The workshop demonstrates the three-step approach to solve any signal integrity problems, using analysis techniques such as eye diagrams, mixed-mode S-parameters, time domain reflectometry (TDR) and the single pulse response. You will learn the basics of signal integrity while familiarizing yourself with PathWave ADS.

- Signal_Integrity_Workshop_1_02-11-2020.zip (ZIP, 46.2 MB) includes:

- A Practical Guide to Signal Integrity: From Simulation to Measurement.pdf (PDF, 5.43 MB)

- Signal_Integrity_Analysis_Essentials_wrk_20200213.7zads (7ZADS, 41.4 MB)

Understand Your Single-Ended Channel: Crosstalk

This workshop uses transmission models and simulations to confirm the impact of trace proximity on crosstalk. You will create traces with different spacings to learn about the mechanism that drives crosstalk. Eye diagrams are used to visualize the impact of crosstalk.

- Signal_Integrity_Workshop_2_02-11-2020.zip (ZIP, 63.7 MB) includes:

- Channel to Channel Crosstalk: A Closer Look.pdf (PDF, 2.17 MB)

- Signal_Integrity_Analysis_Xtalk_wrk_20200213.7zads (ZIP, 61.8 MB)

Extract and Analyze Channel EM Model and Applications

This workshop is a great introduction to 3D EM simulation with SIPro. You will analyze an HDMI link on Xilinx’s FPGA and extract its S-parameters. The S-parameter data of the link is then used to perform channel simulations and other schematic level data mining.

- Signal_Integrity_Workshop_3_02-11-2020.zip (ZIP, 21.1 MB) includes:

- Robust_Signal_Integrity_Simulation_Workflow.pdf (PDF, 3.39 MB)

- Signal_Integrity_Analysis_SIPro_zynq_wrk_20200213.7zads (ZIP, 18 MB)