Choose a country or area to see content specific to your location

What are you looking for?

-

-

3D Interconnect Designer

3D Interconnect Designer provides a flexible modeling and optimization environment for any advanced interconnect structure, including chiplets, stacked die, packages, and PCBs.

-

Save up to 50% on an XR8 Oscilloscope

Get faster digital validation for less with a trade-in.

-

Discover Keysight AI Data Center Builder

Emulate every part of your data center infrastructure. Emulate Anything. Optimize Everything.

-

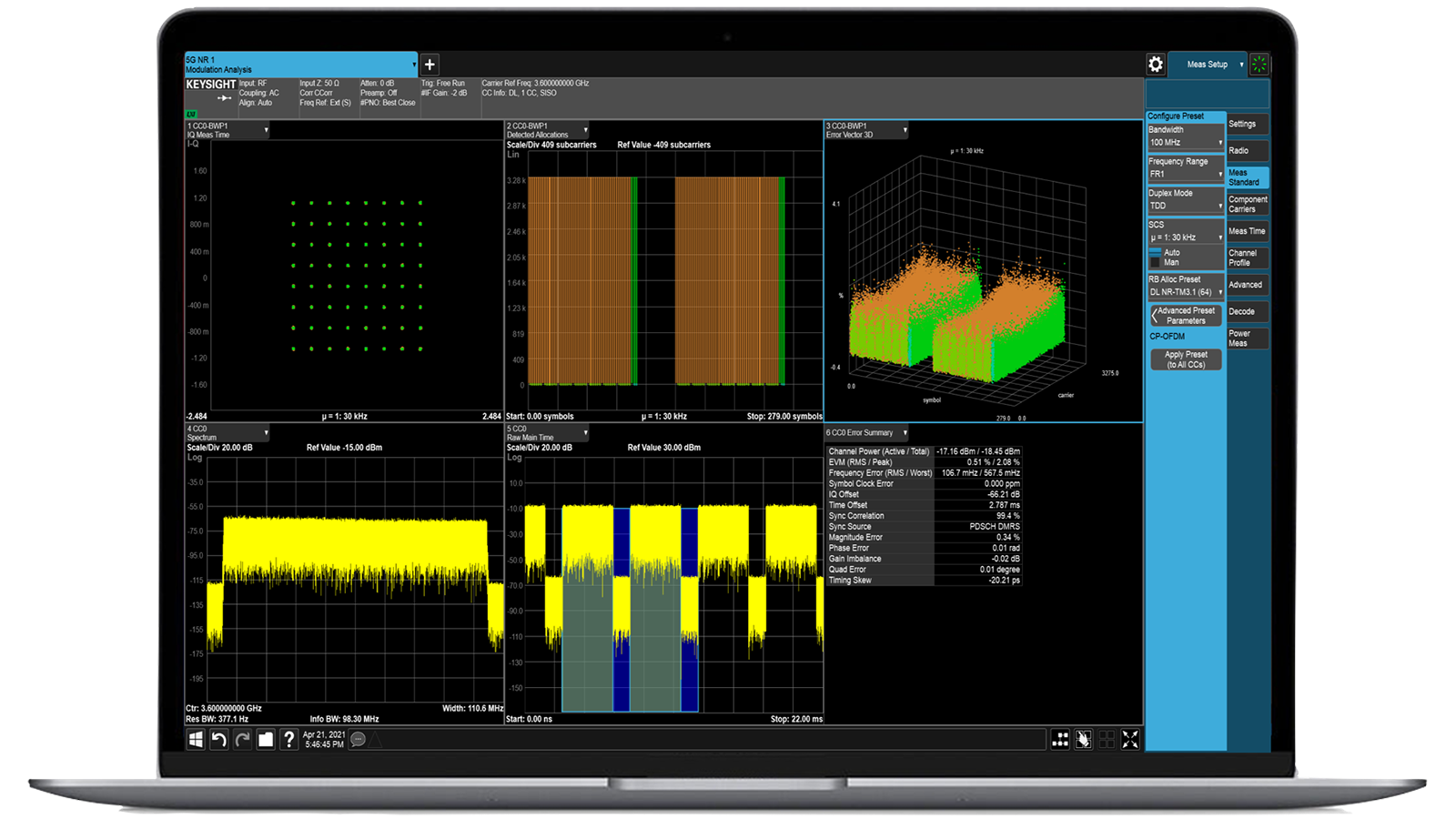

Accelerate Signal Analysis with X-Series Measurement Applications

Use 25+ X-Series applications to analyze, demodulate, and troubleshoot signals across wireless, aerospace/defense, EMI, and phase noise.

-

Introducing AI-Enhanced Packet Brokers

With extra memory and storage, these enhanced NPBs run Keysight's AI security and performance monitoring software and AI stack.

-

Precision In-Circuit Testing for Production

Achieve fast, accurate board-level testing with robust inline and offline ICT designed for modern manufacturing.

-

Accelerate Your Innovation Engine

Explore curated support plans, prioritized to keep you innovating at speed.

-

448 Gb/s Waveform Generation

Achieve 200+ Gbaud multi-level modulated signals with high-speed AWGs for digital and optical standards.

-

Stream 120 MHz I/Q Data to Your Laptop in the FieldPinpoint interference with post-processing spectrum management software in the lab.

Find the Right ATE Power Solution

Find the Right ATE Power SolutionUse this selector tool to quickly identify the best power supply for your aerospace and defense ATE requirements.

-

- Solutions

-

Explore engineer-authored content and a vast knowledge base with thousands of learning opportunities.

FeaturedKeysight Learn offers immersive content on topics of interest, including solutions, blogs, events, and more.

- Buy

-

Quick access to support related self-help tasks.

Additional content to support your product needs.

Do more with Keysight ServicesExplore services to accelerate every step of your innovation journey.

5G ORAN Pre-Silicon Emulation Virtual design and validation for ORAN radio units

- Overview

- All Models

- Support

Elastic virtual testbeds to accelerate ORAN development

Keysight 5G ORAN emulators enable early-stage teams to conduct pre-silicon and system-level validation of ORAN–compliant radio (O-RUs) and distributed (O-DUs) units. They fully emulate the ORAN protocol stack—management (M-plane), control/user (C/U-plane), and synchronization (S-plane)—for precise functional, timing, and conformance testing without hardware. Elastic virtual testbeds integrate with Keysight Open RAN Studio, Signal Studio Pro, Vector Signal Analysis software, and leading third-party tools. This ecosystem supports multi-vendor interoperability, accelerates debugging, and streamlines root cause analysis across the ORAN lifecycle. Request a quote for one of our popular configurations today. Need help selecting? Check out the resources below.

Multi-system integration

Integrates with Keysight Open RAN Studio, Vector Signal Analysis, and Signal Studio Pro, plus Cadence and Synopsys simulators, enabling full-stack testing.

Fronthaul behavior

Supports complete ORAN protocol stacks across M-plane, C/U-plane, and S-plane, including 7.2x functional split conformance and timing validation.

Pre-silicon verification

Enables validation of radio unit and distributed unit RTL, firmware, and protocol behavior in virtual testbeds, reducing hardware dependency.

Full-stack insight

Provides detailed logging and protocol-level statistics to support validation and compliance testing to accelerate issue isolation.

-

Emulation options

Cadence emulator, Synopsys emulator, Siemens emulator

-

Number of interfaces

32 to Unlimited

-

Protocol support

eCPRI/ IQ Data

-

License options

1-year

Most popular configurations

IxVerify for 5G O-RAN Floating Subscription

IxVerify for 5G O-RAN Floating Subscription

939-9988

Keysight IxVerify for 5G O-RAN medium-scale floating subscription.

- Build O-RAN-compliant control plane and user plane (CU-plane) test vectors.

- Inject traffic into the emulator to simulate complex downlink (DL) and uplink (UL) scenarios.

- Capture and decode O-RU chipset responses.

- Extract IQ vectors for modulation analysis.

- Measure the O-RAN radio unit (O-RU) chipset to ensure it meets standard compliance and radio performance.

- Analyze both FR1 and FR2 radio DL and UL paths.

IxVerify for 5G O-RAN Floating Subscription

IxVerify for 5G O-RAN Floating Subscription

939-9989

Keysight IxVerify for 5G O-RAN large-scale floating subscription.

- Build O-RAN-compliant control plane and user plane (CU-plane) test vectors.

- Inject traffic into the emulator to simulate complex downlink (DL) and uplink (UL) scenarios.

- Capture and decode O-RU chipset responses.

- Extract IQ vectors for modulation analysis.

- Measure the O-RAN radio unit (O-RU) chipset to ensure it meets standard compliance and radio performance.

- Analyze both FR1 and FR2 radio DL and UL paths.

IxVerify for 5G O-RAN Floating Subscription

IxVerify for 5G O-RAN Floating Subscription

939-9987

Keysight IxVerify for 5G O-RAN small-scale floating subscription.

- Build O-RAN-compliant control plane and user plane (CU-plane) test vectors.

- Inject traffic into the emulator to simulate complex downlink (DL) and uplink (UL) scenarios.

- Capture and decode O-RU chipset responses.

- Extract IQ vectors for modulation analysis.

- Measure the O-RAN radio unit (O-RU) chipset to ensure it meets standard compliance and radio performance.

- Analyze both FR1 and FR2 radio DL and UL paths.

Services and support

Innovate at speed with curated support plans and prioritized response and turn-around times.

Get predictable, lease-based subscriptions and full lifecycle management solutions—so you reach your business goals faster.

Experience elevated service as a KeysightCare subscriber to get committed technical response and more.

Ensure your test system performs to specification and meets local and global standards.

Make measurements quickly with in-house, instructor-led training, and eLearning.

Download Keysight software or update your software to the newest version.

Frequently asked questions

Keysight 5G ORAN is a pre-silicon protocol load test solution designed to validate 5G and future 6G ORAN radio unit (O-RU) SoC designs under real-world, full-load conditions. It helps engineers emulate massive MIMO traffic patterns, test beamforming and precoding functionality, and analyze IQ data compression performance over Ethernet and AXI/JESD interfaces. By providing early, virtualized testing before silicon is fabricated, 5G ORAN software minimizes costly design errors, shortens development cycles, and helps ensure O-RU chipsets comply with ORAN standards for robust deployment in disaggregated networks.

Yes, 5G O-RAN is engineered to handle complex massive MIMO testing, generating high-throughput traffic across multiple carriers and antenna arrays to simulate realistic network loads. It validates synchronization between ORAN functional splits, checks precise timing across signal paths, and verifies critical features like beamforming, precoding, and IQ compression. This capability ensures O-RU designs can meet performance demands for low latency and high spectral efficiency, crucial for delivering services like ultra-reliable low-latency communications (URLLC) and enhanced mobile broadband in 5G and beyond.

Yes, 5G O-RAN software offers a robust automation framework that integrates REST APIs and Python scripting, making it easy for engineers to automate complex test scenarios and regression suites. It’s designed for distributed, collaborative development environments, enabling teams across the globe to share configurations, test cases, and results seamlessly.

The tool provides real-time statistics, control/user-plane message analysis, and insightful performance metrics, empowering engineers to quickly identify issues and optimize O-RU designs for compliance and efficiency. In addition, the software supports continuous integration and continuous deployment (CI/CD) pipelines, allowing automated testing to be embedded directly into product development workflows.

Engineers can schedule large-scale test campaigns, run them in parallel across different sites, and aggregate the results in centralized dashboards. This ensures consistent validation, faster troubleshooting, and streamlined interoperability testing in multi-vendor environments. Together, these capabilities make the software well-suited for modern agile development practices and globally distributed engineering teams.