The challenge

You rely on the insight a MSO (mixed-signal oscilloscope) provides to understand the behavior of your FPGA in the context of the surrounding system. Design engineers typically take advantage of the programmability of the FPGA to route internal nodes to a small number of physical pins for debugging. While this approach is very useful, it has significant limitations.

- Since pins on the FPGA are typically an expensive resource, there are a relatively small number available for debug. This limits internal visibility (i.e. one pin is required for each internal signal to be probed).

- When you need to access different internal signals, you must change your design to route these signals to the available pins. This can be time consuming and can affect the timing of your FPGA design.

- Finally, the process required to map the signal names from your FPGA design to the MSO digital channel labels is manual and tedious.

- When new signals are routed out, you need to manually update these signal names on the MSO, which takes additional time and is a potential source of confusing errors.

Debug Your FPGAs Faster and More Effectively With a MSO

A better way

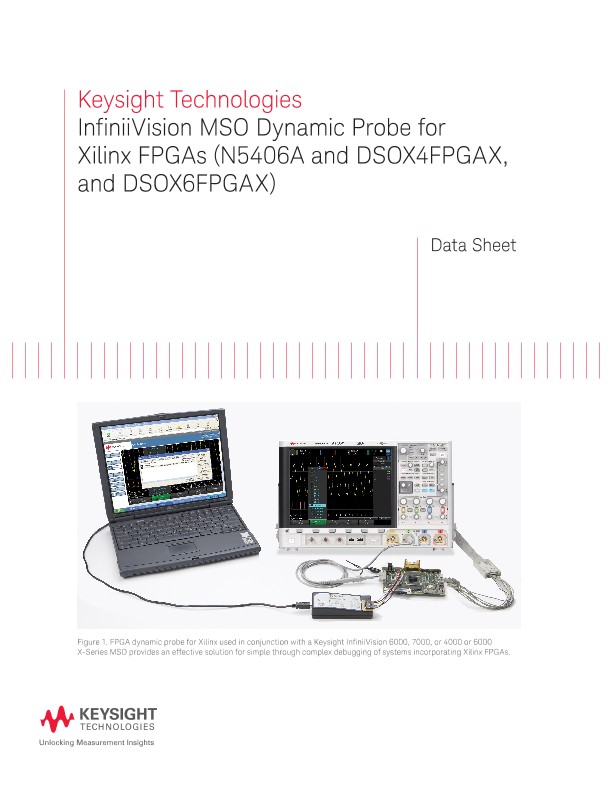

Collaborative development between Keysight Technologies, Inc. and Xilinx have produced a faster and more effective way to use your MSO to debug FPGAs and the surrounding system. The Keysight FPGA dynamic probe, used in conjunction with a Keysight MSO, provides the most effective solution for simple through complex debugging.

View internal activity

With the digital channels on your MSO, you are normally limited to measuring signals at the periphery of the FPGA. With the FPGA dynamic probe, you can now access signals internal to the FPGA. You can measure up to 64 internal signals for each external pin dedicated to debug, unlocking visibility into your design that you never had before.

Make multiple measurements in seconds

Moving probe points internal to an FPGA used to be time consuming. Now, in less than a second, you can easily measure different sets of internal signals without design changes. FPGA timing stays constant when you select new sets of internal signals for probing.

Leverage the work you did in your design environment

The FPGA dynamic probe maps internal signal names from your FPGA design tool to your Keysight MSO. Eliminate unintentional mistakes and save hours of time with this automatic setup of signal and bus names on your MSO.

Design step 1: Create the ATC2 core

Use Xilinx Core Inserter or EDK to select your ATC2 parameters and to create a debug core that best matches your development needs. Parameters include number of pins, number of signal banks, the type of measurement (state or timing), and other ATC2 attributes.

Design step 2: Select groups of signals to probe

Specify banks of internal signals that are potential candidates for MSO measurements (using Xilinx Core Inserter or EDK).

Activate FPGA dynamic probe for Xilinx

The FPGA dynamic probe application allows you to control the ATC2 core and set up the MSO for the desired measurements. This application runs on a PC.

Connect your MSO to your PC

From FPGA dynamic probe application software, specify the communication link between your PC and MSO.

Measurement setup step 1: Establish a connection between the PC and the ATC2 core

The FPGA dynamic probe application establishes a connection between the PC and a Xilinx cable. It also determines what devices are on the JTAG scan chain and lets you pick which one you wish to communicate with. Core and device names are user definable.

Measurement setup step 2: Map FPGA pins

Quickly specify how the FPGA pins (the signal outputs of ATC2) are connected to your MSO. Select your probe type and rapidly provide the information needed for the MSO to automatically track names of signals routed through the ATC2 core.

For ATC2 cores with auto setup enabled, each pin of the ATC2 core, one at a time, produces a unique stimulus pattern. The instrument looks for this unique pattern on any of its acquisition channels. When the instrument finds the pattern, it associates that instrument channel with the ATC2 output pin producing it. It then repeats the process for each of the remaining output pins eliminating the need to manually enter probe layout information.

Measurement setup step 3: Import signal names

Tired of manually entering bus and signal names on your MSO? The FPGA dynamic probe application reads a .cdc file produced by Xilinx Core Inserter. The names of signals you measure will now automatically show on your MSO digital channel labels.

Setup complete: Make measurements

Quickly change which signal bank is routed to the MSO. A single mouse click tells the ATC2 core to switch to the newly specified signal bank without any impact to the timing of your design. To make measurements throughout your FPGA, change signal banks as often as needed. User-definable signal bank names make it straight forward to select a part of your design to measure.

Triggering on valid states

MSOs incorporate logic state triggering for triggering on specific states. Set up a valid state trigger by specifying the clock edge and the desired bus/signal pattern. Because the ATC2 core outputs both the clock signal and bus values, triggering on the combination ensures your state trigger is valid—even though the digital channels are sampling asynchronously. Track valid states by measuring the bus value on each falling clock edge for image shown.

Automatic bus groupings

InfiniiVision MSOs include up to 2 bus groupings. Contiguous signal names are automatically grouped and displayed as buses. Bus values can be displayed as HEX or binary values. Additional signals are shown using independent waveforms.

Oscilloscopes

Analyzers

Meters

Generators, Sources, and Power Supplies

Software

Wireless

Modular Instruments

Network Test and Security

Network Visibility

Services

Additional Products