Choose a country or area to see content specific to your location

- 產品概述與特色

- 採購後升級選項

- 資源

HIGHLIGHTS

- 150 Mb/s 至 7 Gb/sM或 12.5 Gb/s 的碼型產生器和誤差檢測器

- >0.5 UI 校驗及整合抖動注入

- 優異的信號效能與靈敏度

- 具可調諧與相容迴路頻寬的內建時脈資料還原

Keysight N4903A 的可用配置

最新訊息 - J-BERT N4903B 高效能串列 BERT

2010 年 4 月 30 日是訂購 A 版 J-BERT N4903A 高效能串列 BERT 的最後截止日期。之後,我們建議您改用 J-BERT N4903B,該產品的售價與 N4903A 相當,可提供更多的抖動注入功能、半速時脈支援、內建的 CDR 和抖動消除輸出效能。 在 2011 年 4 月 30 日之前,您仍可採購 Keysight N4903A 的軟硬體升級選項。您可訂購 N4903B-UAB 以便從 N4903A 升級為 N4903B。 J-BERT N4903B

Keysight J-BERT N4903A 高效能序列 BERT,提供了序列 gigabit 裝置唯一完整抖動容許度測試方案。

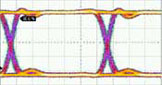

J-BERT 提供完整、整合式及校驗的抖動組合,可執行高達 12.5 Gb/s 接收器強調眼圖測試。

自動化及符合抖動容許度之測試,能迅速準確地分析所有常見的序列匯流排標準,例如 PCIeTM、SATA、FB-DIMM、Fibre Channel、CEI、Gigabit Ethernet 和 XFP/XFI。

J-BERT 與最新序列匯流排介面形成完美搭配,提供非決定性流量分析、產生複雜碼型序列、及次速率時脈輸出功能。可測試無時脈及差動式介面。

J-BERT 為可擴充且適用於未來 BERT 平台,所有選項皆可配置以符合目前測試需求,並於日後需求改變時進行升級。

此產品採用高達 12.5 Gb/s 的序列 I/O 連接埠,進行晶片與收發器模組的特性分析,為研發及驗證團隊最佳的選擇。

| 純淨眼圖 | 眼圖/輪廓/波罩 |

|---|---|

|

|

| 強調眼圖 | 自動化抖動容許度 |

|---|---|

|

|

| 最快速總抖動 | 抖動組合 |

|---|---|

|

|

- 150 Mb/s 到 7 Gb/s 或 12.5 Gb/s 操作範圍,提供今日及未來序列介面充足需求

- >0.5 UI 加入抖動。校驗及整合加入抖動 (選項J10、J20)。全方位機盒:用於接收器強調眼圖測試的 PJ、SJ、RJ、BUJ、ISI,及正弦干擾

- 可以含轉態時間 <20 ps 的純淨眼圖及 < 9 ps pp 的抖動進行準確量測

- 7Gb/s 與 12.5Gb/s 的碼型產生器選項

- 最符合序列介面需求:內建 CDR、差動式 I/O

- 以 1Gb/s 到 12.5 Gb/s 運作的時脈資料還原 (CDR) 與可調協迴路頻寬 (選項 CTR),進行相容量測

- 所有 1:n 次速率時脈

- 位元還原模式 (選項 A01),用來分析非決定性流量

- 碼型排序器與擷取功能,可簡化處理複雜的資料碼型的程序

- 所有外部加入抖動的外部延遲控制輸入

- 自動化抖動容許度特性分析與認證測試

- SSC - 展頻時脈 (選項 J11)

- 抖動容許度認證 (選項 J12) 測試:PCIeTM、SATA、Fibre Channel、FB-DIMM、CEI、10 GbE、XFP/XFI

- 快速總抖動量測

- 所有選項皆可升級

PCIe 是 PCI-SIG 的商標