這是我們認為您想查看的頁面.

觀看搜尋結果:

Choose a country or area to see content specific to your location

- Home

- 產品與服務

- ...

- EDA 軟體

- PathWave 先進設計系統

- W2309EP DDR 匯流排模擬器 [Discontinued]

- 產品概述與特色

- 採購後升級選項

- 資源

HIGHLIGHTS

- 針對任意低誤碼率位準進行嚴格的 DQ 和 DQS 眼圖計算

- 內建驅動程式解加強和接收器連續時間線性等化模型

- 混搭驅動程式和接收器的內建、IBIS 和電路模型

- 考慮信號線間的交互干擾

- 擷取上升和下降信號緣間的非對稱性

- 目標 BER 的完整邊限量測與 JEDEC DDR4 Rx 遮罩

- 設計空間探索與設計實驗的批次模擬

- 計算叢集上的可選參數掃描

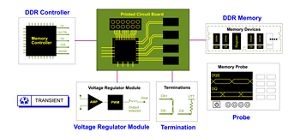

W2309EP DDR 匯流排模擬器可針對固態技術協會(JEDEC)公布的 DDR 記憶體匯流排規格,在兩者間快速產生準確的誤碼率(BER)輪廓、遮罩和邊限。此模擬器透過統計模擬來執行前述運算,因此不需計算冗長、耗時的位元樣型。相反的,它可利用發射器、通道和接收器脈衝響應,以及概念上為無限且不重複的位元樣型具有的隨機特性,來建構眼圖。如此一來,便可避免類 SPICE 模擬或卷積通道模擬不穩定的雙重 Dirac 外推演算法相關陷阱。

個別模擬速度非常快速,設計人員可執行批次模式,迅速探索設計空間。W2317EP DDR 匯流排模擬器分散式計算 8 個一組是我們的另外一個產品,您可將參數掃描送入計算叢集中,便能更快獲得答案。

DDR 匯流排模擬器為任意低誤碼率位準(包括 JEDEC 制定的 1E-16 輪廓)提供嚴謹的 DQ 和 DQS 眼圖計算,並將上升與下降轉態時間的交互干擾和非對稱性納入考量。提供指定 BER 輪廓與 DDR4 接收遮罩規格間,完整的時序和電壓邊限。

此產品支援三種 IC 模型:內建、IBIS 或電路模型。內建驅動程式和接收器模型分別提供解加強和連續時間線性等化(CTLE)功能。設計人員可在電路圖中「混搭」所需模型。

排序依據 :

日期

日期

標題

Filter Results

找不到此產品的相關資訊

重新填寫

依內容類型