---

# D9010ETHC Ethernet Compliance Test Application

# Notices

© Keysight Technologies 2015 - 2024

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

## Software Version

Version 2.75.10.0

## Edition

November 2024

Available in electronic format only

Keysight Technologies

1900 Garden of the Gods Road

Colorado Springs, CO 80907 USA

## Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

## Technology Licenses

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at

<http://www.keysight.com/find/sweula>. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater

than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

## Safety Notices

### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## Ethernet Automated Testing – At a Glance

The Keysight D9010ETHC Ethernet Compliance Test Application helps you verify Ethernet transmitter device under test (DUT) compliance to specifications using the Keysight Infiniium oscilloscopes.

This automated Ethernet test application offers:

- Capability for testing the DUT for 10 Base-T, 100 Base-TX, and 1000 Base-T transmitter electrical compliance.

- Capability for additional testing for Energy-Efficient Ethernet (EEE) compliance, which is defined in IEEE 802.3az, 10 Base-T, 100 Base-T EEE mode, and 1000 Base-T EEE mode.

The Ethernet Compliance Test Application:

- Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

- Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- Allows you to determine the number of trials for each test with the multi-trial run capability.

- Provides detailed information for each test that has been run, and lets you specify the thresholds at which marginal or critical warnings appear.

- Creates a printable HTML report of the tests that have been run.

### NOTE

The tests performed by the Ethernet Compliance Test Application are intended to provide a quick check of the electrical health of the DUT. These testing are not a replacement for an exhaustive test validation plan.

Compliance test measurements are described in the *IEEE 802.3-2018 Standard*, *IEEE 802.3az Standard*, and *ANSI X3.263-1995 Standard*. For more information, see the IEEE 802 Standards Web site at [www.ieee802.org](http://www.ieee802.org).

### Required Equipment and Software

In order to run the Ethernet Compliance Test Application, you need the following equipment and software:

- D9010ETHC Ethernet Compliance Test Application software.

- Use one of the following oscilloscope models:

- Keysight 9000-series, S-series, 90000-series, 90000 X-series, 90000 Q-series and Z-series Infiniium Oscilloscopes

- Keysight UXR Oscilloscopes (13GHz – 33GHz)

- Keysight MXR Oscilloscopes (4 channels with channels 1-3 and 2-4 pairing support, sampling rate up to 16GSa/s)

- Keysight EXR Oscilloscopes (4 channels with channels 1-3 and 2-4 pairing support, minimum bandwidth 1GHz, sampling rate up to 16GSa/s)

- The minimum version of Infiniium oscilloscope software (see the D9010ETHC test application release notes).

- Keysight N5395C and Wilder Technologies 110-1089-000 Ethernet electrical compliance test fixtures.

- InfiniiMax probe amplifiers.

- E2678A/B differential socket probe head.

- E2677A/B differential solder-in probe head.

- BNC cables.

- Keyboard, quantity = 1 (provided with the Keysight Infiniium oscilloscope).

- Mouse, quantity = 1 (provided with the Keysight Infiniium oscilloscope).

- Keysight also recommends using a second monitor to view the automated test application.

For more details on the required and recommended equipment, please refer to ["Required and Recommended Equipment"](#) on page 24.

For the information regarding required licenses to use this application, refer to the Data Sheet for this application.

Additionally, for the jitter and distortion test, at least 8M points of memory is required. Hence, Memory Upgrade Option 001 is recommended for the 54850 and 80000 Series oscilloscopes for best performance. Option 080 is recommended for the 54830 and 8000 Series oscilloscopes.

## In This Book

This manual describes the tests that are performed by the Ethernet Compliance Test Application in more detail; it contains information from (and refers to) the *IEEE 802.3-2018 Standard*, *IEEE 802.3az Standard*, and *ANSI X3.263-1995 Standard*, and it describes how the tests are performed.

- [Chapter 1](#), “Overview describes the tests supported by the Ethernet Compliance Test Application and the standard references.

- [Chapter 2](#), “Installing the Ethernet Compliance Test Application shows how to install and license the automated test application software (if it was purchased separately).

- [Chapter 3](#), “Preparing to Take Measurements shows how to start the Ethernet Compliance Test Application and gives a brief overview of how it is used.

- [Chapter 4](#), “1000 Base-T Tests contains more information on the 1000 Base-T tests.

- [Chapter 5](#), “100 Base-TX Tests contains more information on the 100 Base-TX tests.

- [Chapter 6](#), “10 Base-T Tests contains more information on the 10 Base-T tests.

- [Chapter 7](#), “1000 Base-T EEE Tests contains more information on the 1000 Base-T EEE tests.

- [Chapter 8](#), “100 Base-TX EEE Tests contains more information on the 100 Base-TX EEE tests.

- [Chapter 9](#), “10 Base-Te Tests contains more information on the 10 Base-Te tests.

- [Appendix 10](#), “InfiniiMax Probing describes the InfiniiMax probe amplifiers and probe head recommendations for Ethernet testing.

### See Also

- The Ethernet Compliance Test Application’s online help, which describes:

- Starting the Ethernet compliance test application.

- Creating or opening a test project.

- Setting up the Ethernet test environment.

- Setting up InfiniiSim.

- Setting up the precision probe/cable.

- Selecting tests.

- Configuring selected tests.

- Connecting the oscilloscope to the DUT.

- Running tests.

- Viewing test results.

- Viewing/exporting/printing the HTML test report.

- Understanding the HTML test report.

- Saving test projects.

- Installing/removing add-ins.

- Controlling the application via a remote PC.

- Using a second monitor for the application.

# Contents

Ethernet Automated Testing – At a Glance 3

In This Book 5

## 1 Overview

## 2 Installing the Ethernet Compliance Test Application

**Installing the Software** 18

**Installing the License Key** 19

Using Keysight License Manager 5 19

Using Keysight License Manager 6 20

## 3 Preparing to Take Measurements

**Required and Recommended Equipment** 24

Test Fixtures 24

Tests Supported by the Wilder Technologies 110-1089-000 EEE Test Fixture 26

Oscilloscope Compatibility and Recommended Probe Amplifiers 27

Number of Probes and BNC Cables Required 27

Supported Vector Network Analyzers for Return Loss Tests 28

Recommended Accessories 28

Recommended Infiniium Oscilloscope for Jitter and Distortion Test 28

Required Software 28

**Calibrating the Oscilloscope** 29

**Adding Instruments to the Keysight Connection Expert** 30

**Starting the Ethernet Compliance Test Application** 34

Online Help Topics 35

**Selecting the Probe Head** 37

## 4 1000 Base-T Tests

|                                                                                                    |    |

|----------------------------------------------------------------------------------------------------|----|

| <b>Probing for Test Mode 1 and Test Mode 4</b>                                                     | 42 |

| Without Disturbing Signal Probing for Test Mode 1 and Test Mode 4                                  | 42 |

| Calibration Setup for the 33612A Disturbing Signal Source                                          | 43 |

| Calibration Setup for the 81150A Disturbing Signal Source                                          | 44 |

| Calibration Setup for the 33250A Disturbing Signal Source                                          | 45 |

| Disturbing Signal Probing Setup for Test Mode 1 and Test Mode 4 Using the 33250A Signal Generators | 47 |

| Jumper Positions for Test Fixture Section 11                                                       | 49 |

| Disturbing Signal Probing Setup for Test Mode 1 and Test Mode 4 Using Non-33250A Signal Generators | 51 |

| <b>Test Mode 1</b>                                                                                 | 52 |

| Peak Output Voltage Tests                                                                          | 52 |

| Templates Tests                                                                                    | 58 |

| Droop Tests                                                                                        | 59 |

| <b>Test Mode 4</b>                                                                                 | 61 |

| <b>MDI Common Mode Output Voltage</b>                                                              | 63 |

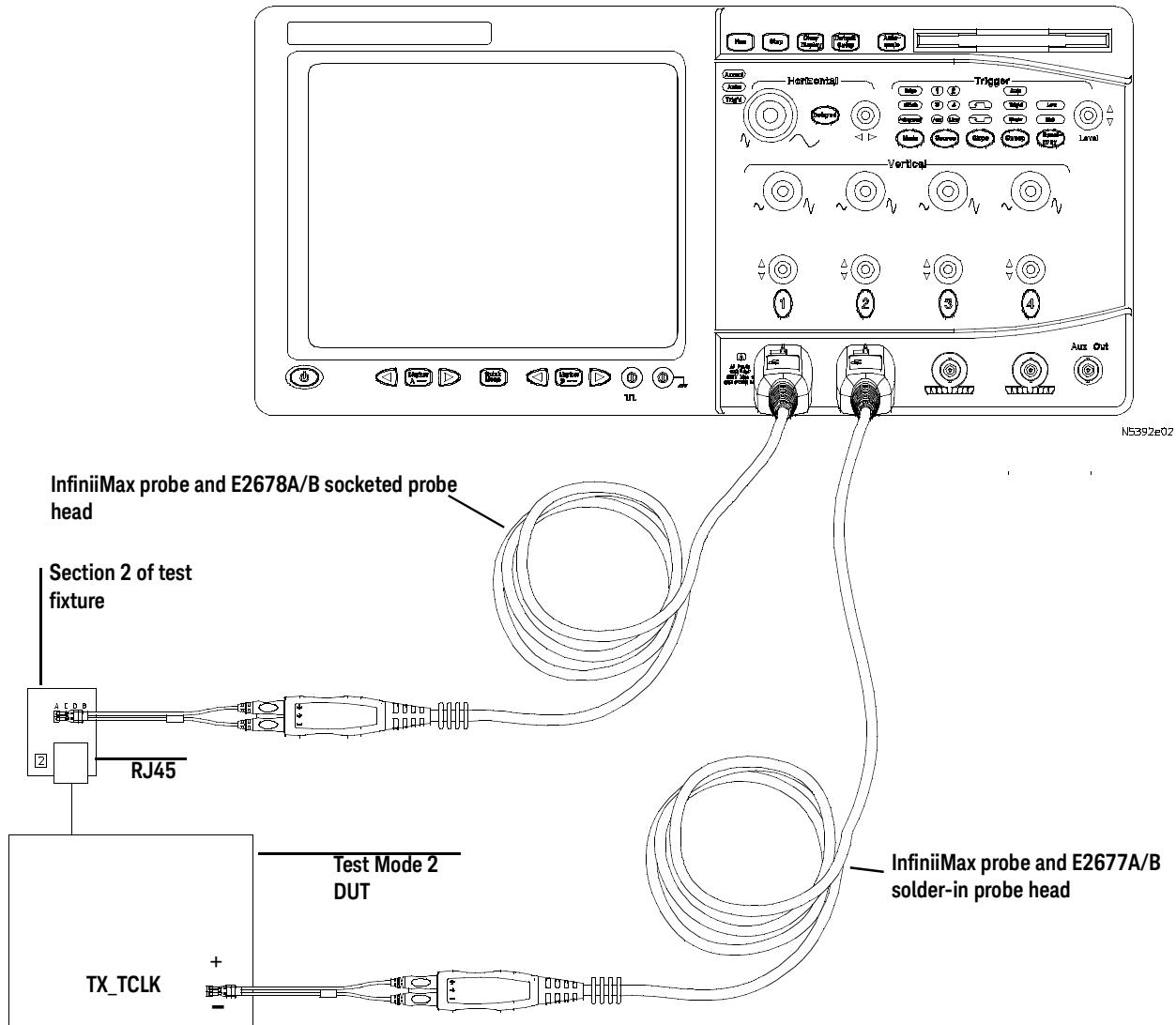

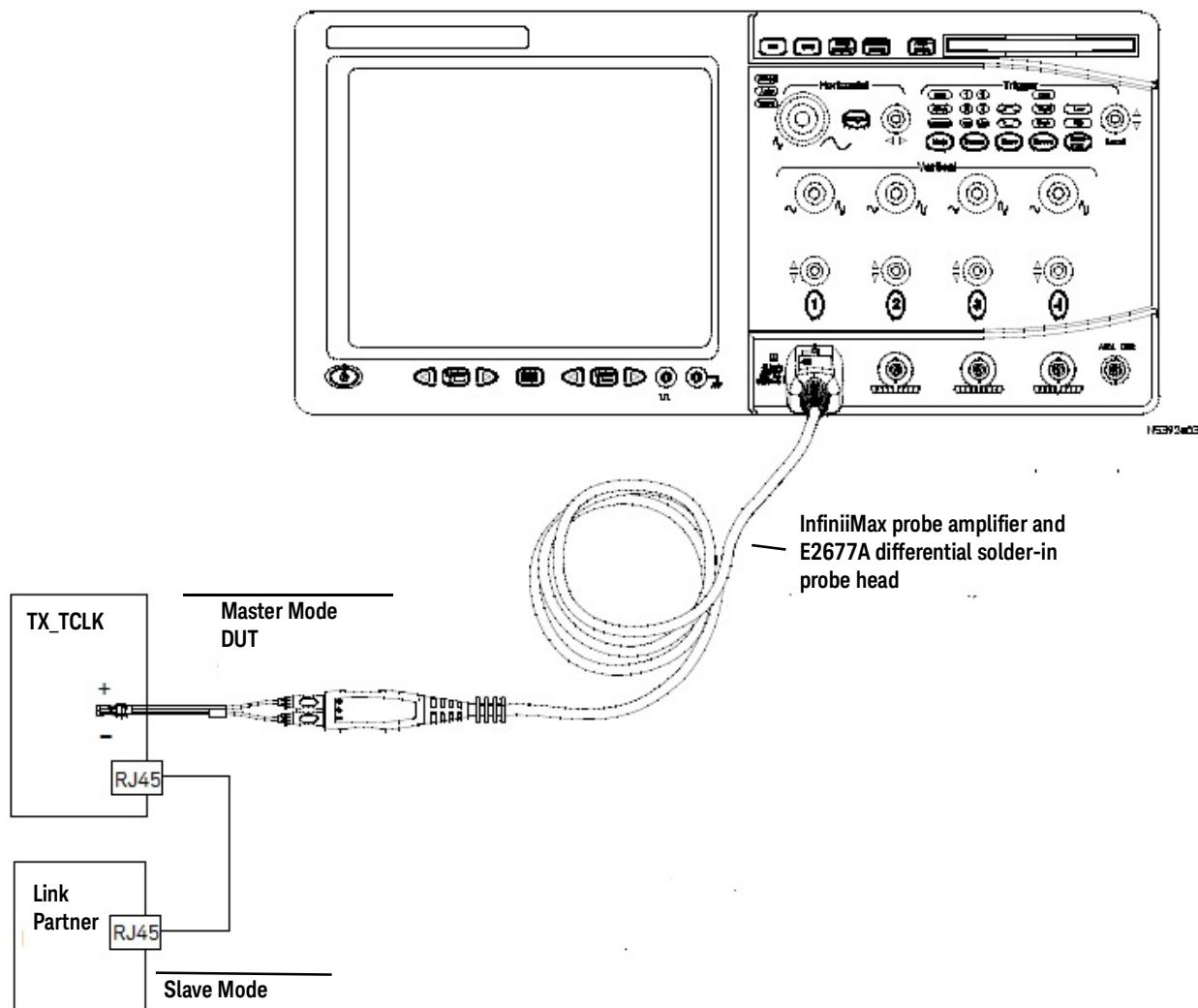

| <b>Jitter Tests with TX_TCLK, DUT in MASTER Mode</b>                                               | 67 |

| MASTER Mode JTxD                                                                                   | 67 |

| Jitter MASTER Unfiltered                                                                           | 70 |

| Jitter MASTER Filtered                                                                             | 73 |

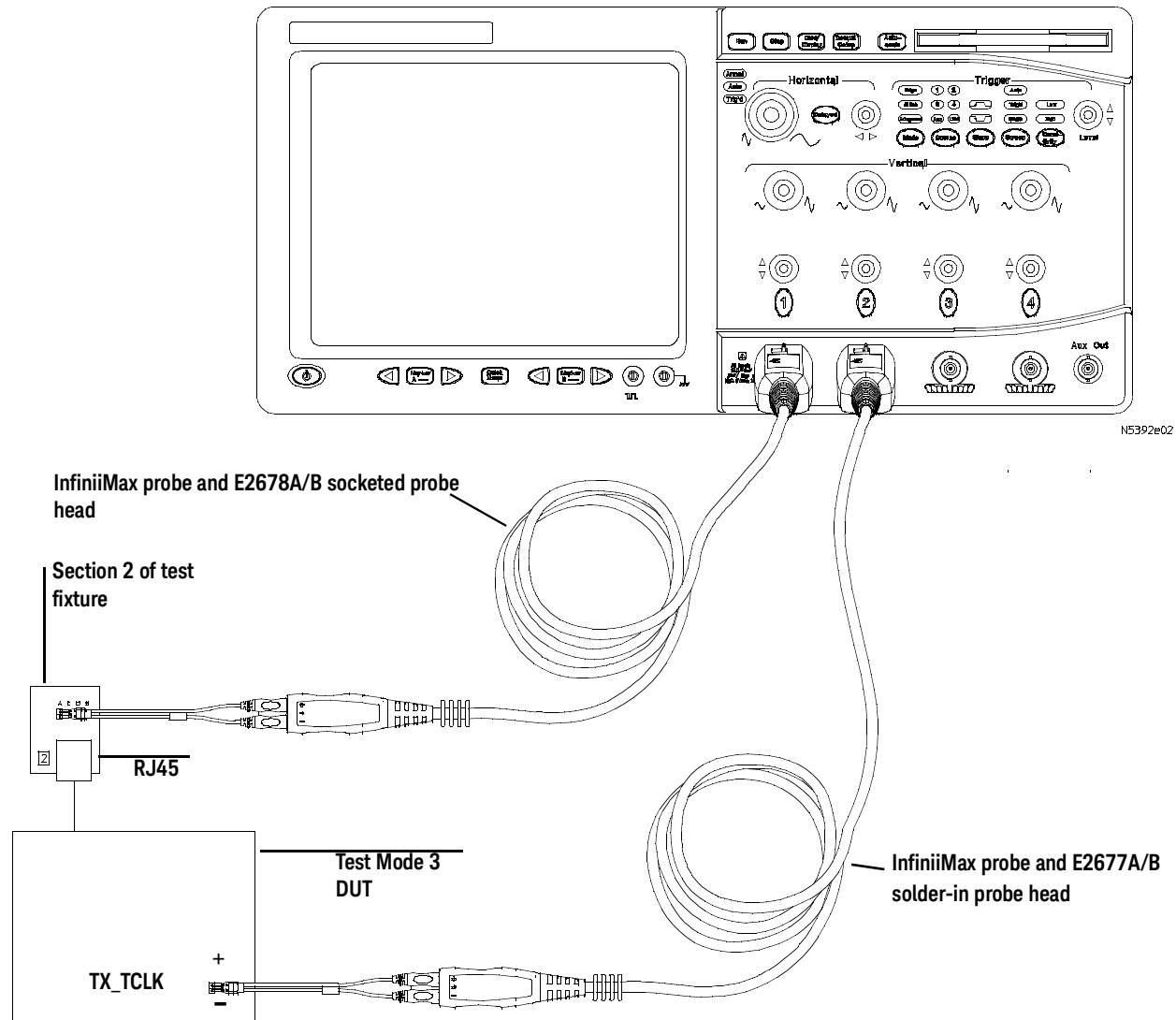

| <b>Jitter Tests with TX_TCLK, DUT in SLAVE Mode</b>                                                | 75 |

| SLAVE Mode JTxD                                                                                    | 75 |

| Jitter SLAVE Unfiltered                                                                            | 77 |

| Jitter SLAVE Filtered                                                                              | 80 |

| <b>Jitter Tests Without TX_TCLK</b>                                                                | 83 |

| <b>Jitter Tests Without TX_TCLK, DUT in MASTER Mode</b>                                            | 83 |

| Jitter MASTER Unfiltered                                                                           | 84 |

| Jitter MASTER Filtered                                                                             | 87 |

| <b>Jitter Tests Without TX_TCLK, DUT in SLAVE Mode</b>                                             | 89 |

| Jitter SLAVE Unfiltered                                                                            | 89 |

| Jitter SLAVE Filtered                                                                              | 92 |

| <b>MDI Return Loss</b>                                                                             | 94 |

## 5 100 Base-TX Tests

|                                                     |     |

|-----------------------------------------------------|-----|

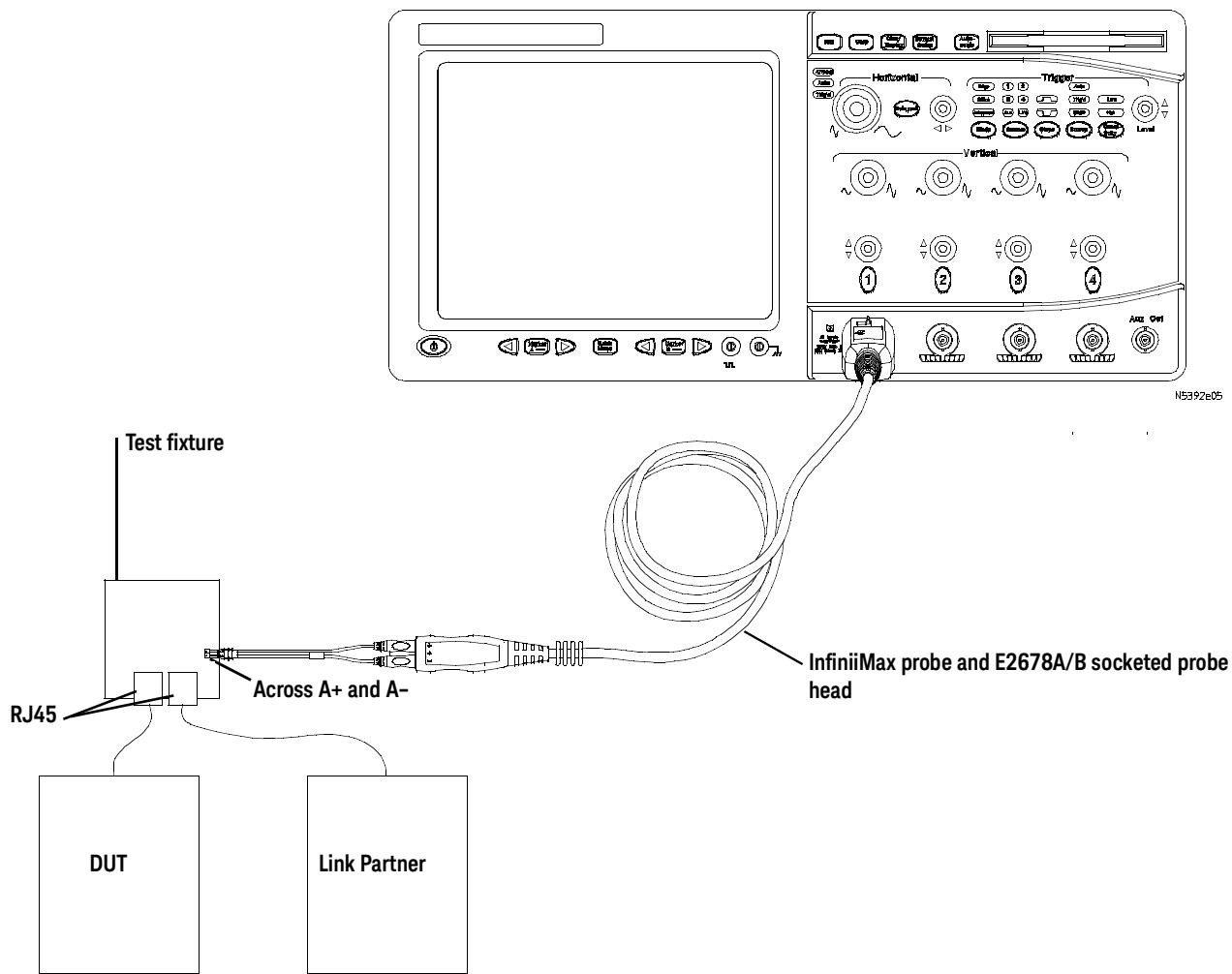

| <b>Probing for 100 Base-TX Tests</b>                | 100 |

| Probing for 100 Base-TX Tests, Without Link Partner | 100 |

| Probing for 100 Base-TX Tests, With Link Partner    | 102 |

|                                                                |     |

|----------------------------------------------------------------|-----|

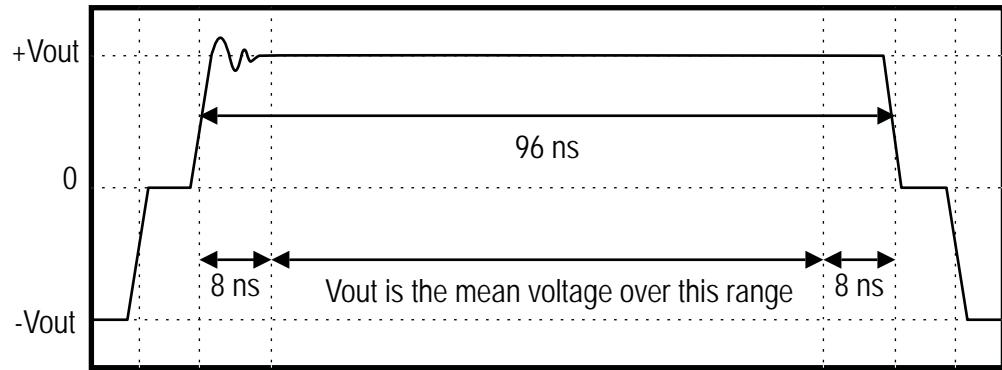

| <b>Peak Voltage Tests</b>                                      | 103 |

| UTP +Vout Differential Output Voltage                          | 103 |

| UTP -Vout Differential Output Voltage                          | 103 |

| Signal Amplitude Symmetry                                      | 104 |

| <b>Overshoot Tests</b>                                         | 106 |

| +Vout Overshoot                                                | 106 |

| -Vout Overshoot                                                | 106 |

| <b>Template Tests</b>                                          | 108 |

| UTP AOI Template                                               | 108 |

| <b>Rise and Fall Time Tests</b>                                | 110 |

| AOI +Vout Rise Time                                            | 110 |

| AOI +Vout Fall Time                                            | 110 |

| AOI +Vout Rise/Fall Symmetry                                   | 110 |

| AOI -Vout Rise Time                                            | 110 |

| AOI -Vout Fall Time                                            | 110 |

| AOI -Vout Rise/Fall Symmetry                                   | 110 |

| AOI Overall Rise/Fall Symmetry                                 | 110 |

| <b>DCD/Jitter Tests</b>                                        | 112 |

| Transmit Jitter                                                | 112 |

| Duty Cycle Distortion                                          | 113 |

| <b>Transmitter Return Loss</b>                                 | 117 |

| <b>Receiver Return Loss</b>                                    | 122 |

| <br><b>6 10 Base-T Tests</b>                                   |     |

| <b>Test Loads</b>                                              | 128 |

| <b>Measurements with TPM, Template Tests</b>                   | 129 |

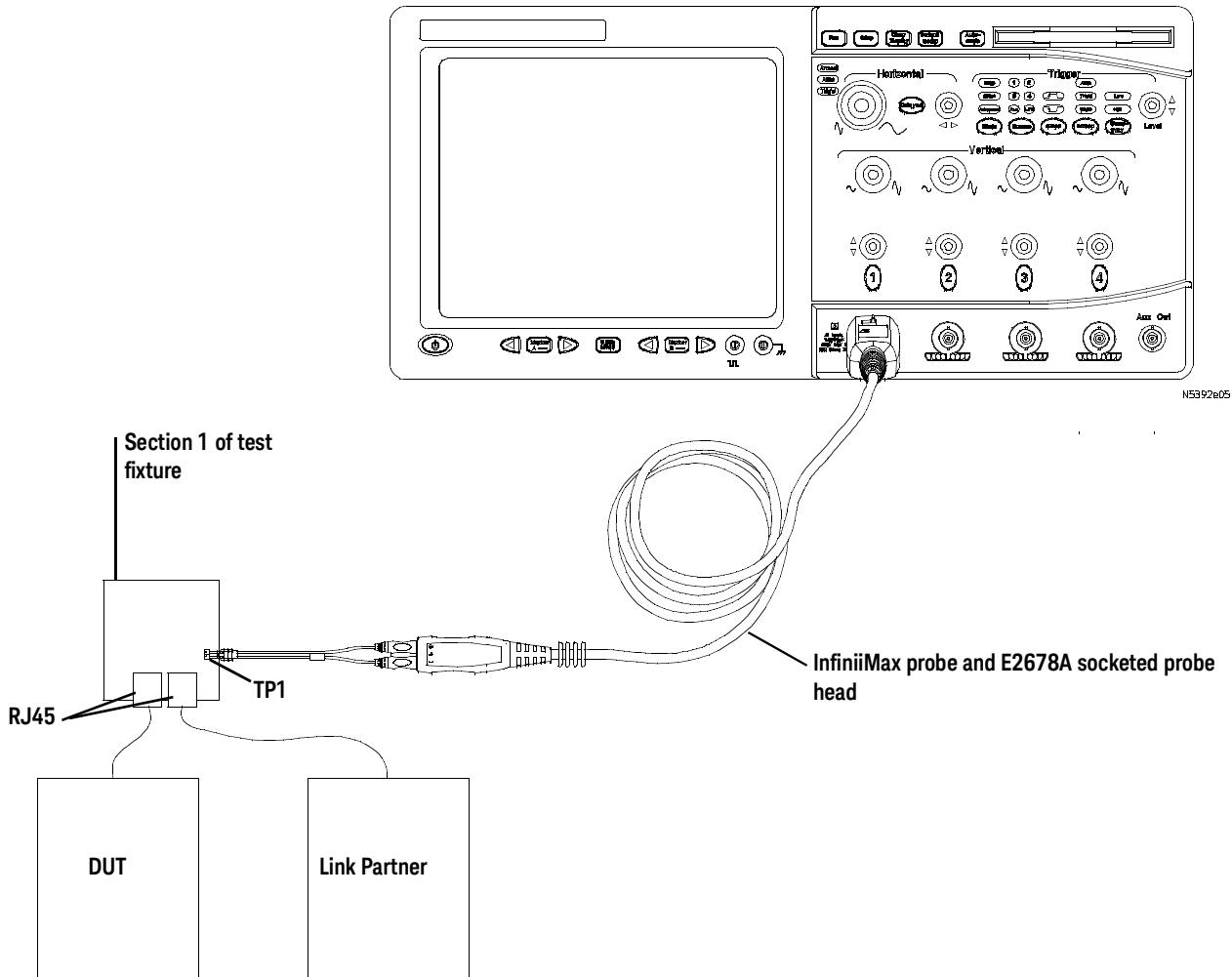

| Probing for 10 Base-T Tests With the TPM and Link Partner      | 129 |

| Link Test Pulse, with TPM                                      | 130 |

| TP_IDL Template, with TPM (Last Bit CD0)                       | 133 |

| TP_IDL Template, with TPM (Last Bit CD1)                       | 135 |

| MAU Template                                                   | 137 |

| <b>Measurements with TPM, Parametric Tests</b>                 | 140 |

| Jitter with TPM                                                | 140 |

| <b>Measurements without TPM, Template Tests</b>                | 143 |

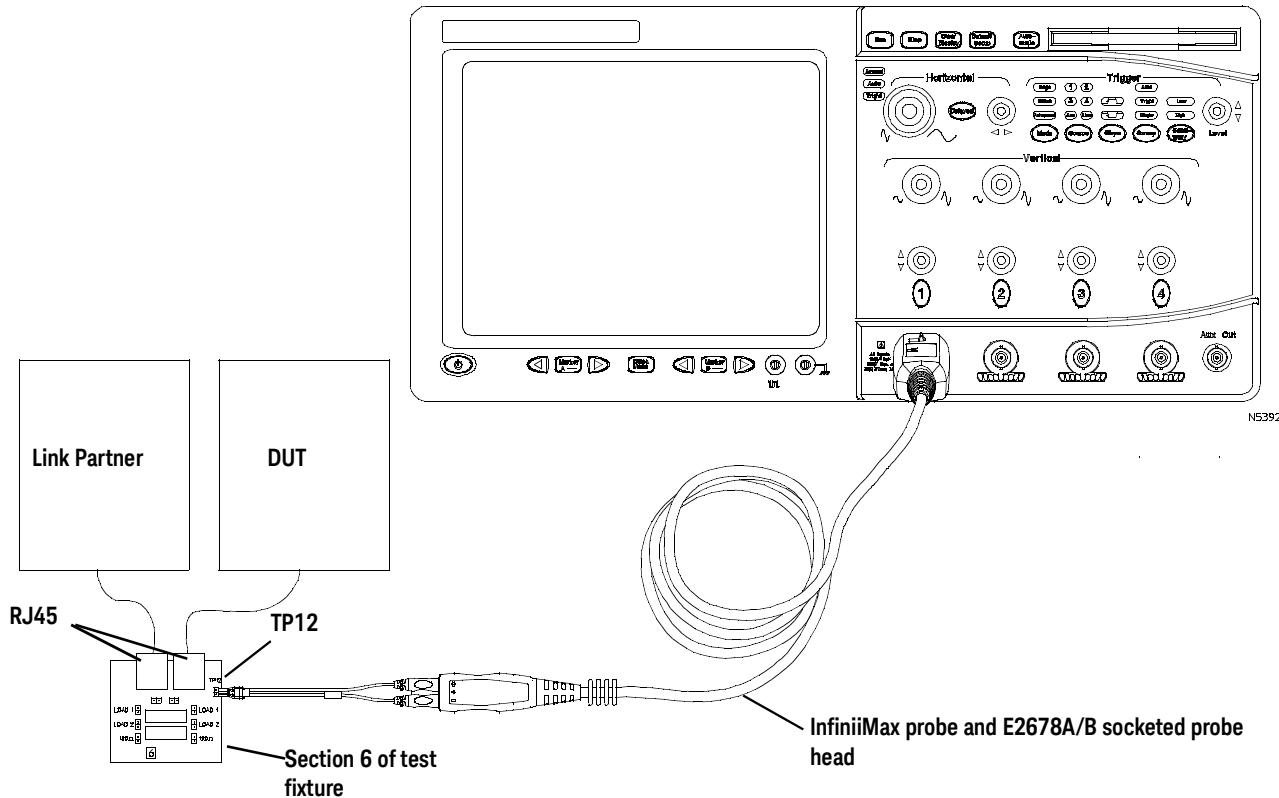

| Probing for 10 Base-T Tests Without the TPM, With Link Partner | 143 |

| Link Test Pulse, without TPM                                   | 144 |

| TP_IDL Template, without TPM (Last Bit CD0)                    | 147 |

| TP_IDL Template, without TPM (Last Bit CD1)                    | 149 |

|                                                                           |     |

|---------------------------------------------------------------------------|-----|

| <b>Measurements without TPM, Parametric Tests</b>                         | 152 |

| Jitter without TPM                                                        | 152 |

| Peak Differential Voltage                                                 | 154 |

| Harmonic Content                                                          | 155 |

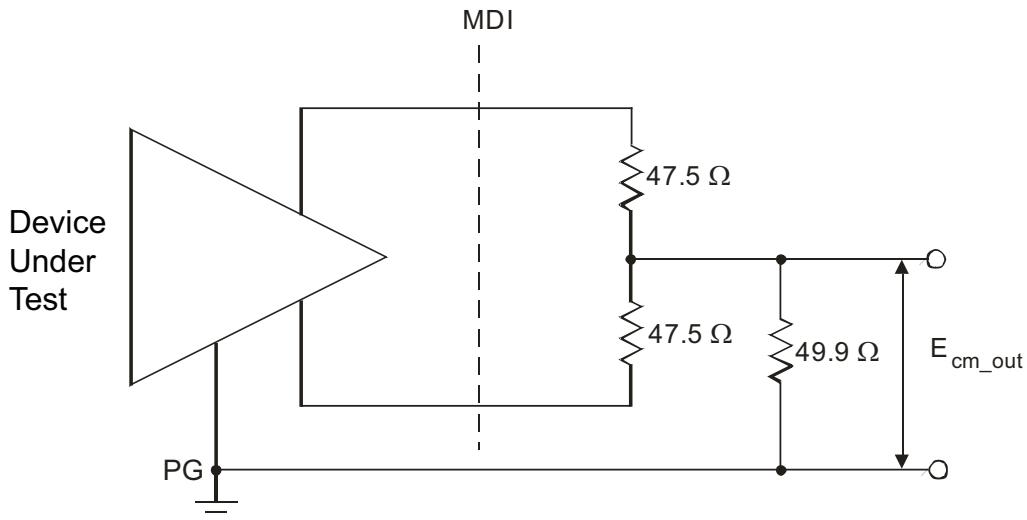

| <b>Common Mode Voltage Tests</b>                                          | 157 |

| Common Mode Output Voltage                                                | 157 |

| <b>Configuring 10 Base-T Device Output</b>                                | 160 |

| Configuring a 10 Base-T Device to Output Random Data                      | 160 |

| Configuring a 10 Base-T Device to Output Manchester Encoded Harmonic Ones | 161 |

| <b>Transmitter Return Loss</b>                                            | 162 |

| <b>Receiver Return Loss</b>                                               | 167 |

| <br><b>7 1000 Base-T EEE Tests</b>                                        |     |

| <b>1000 Base-T EEE Mode</b>                                               | 174 |

| <b>Probing for 1000 Base-T EEE Tests</b>                                  | 175 |

| <b>LPI Tests</b>                                                          | 176 |

| Quiet Time                                                                | 176 |

| Refresh Time (Master)                                                     | 176 |

| Refresh Time (Slave)                                                      | 177 |

| Transmitter Timing Jitter (Master)                                        | 178 |

| <b>Sleep Time Tests</b>                                                   | 180 |

| Sleep Time (Master)                                                       | 180 |

| Sleep Time (Slave)                                                        | 180 |

| <b>Wake Time Tests</b>                                                    | 182 |

| Transmit Wake Time (Master)                                               | 182 |

| Transmit Wake Time (Slave)                                                | 182 |

| Wake State Levels                                                         | 183 |

| <br><b>8 100 Base-TX EEE Tests</b>                                        |     |

| <b>100 Base-TX EEE Mode</b>                                               | 186 |

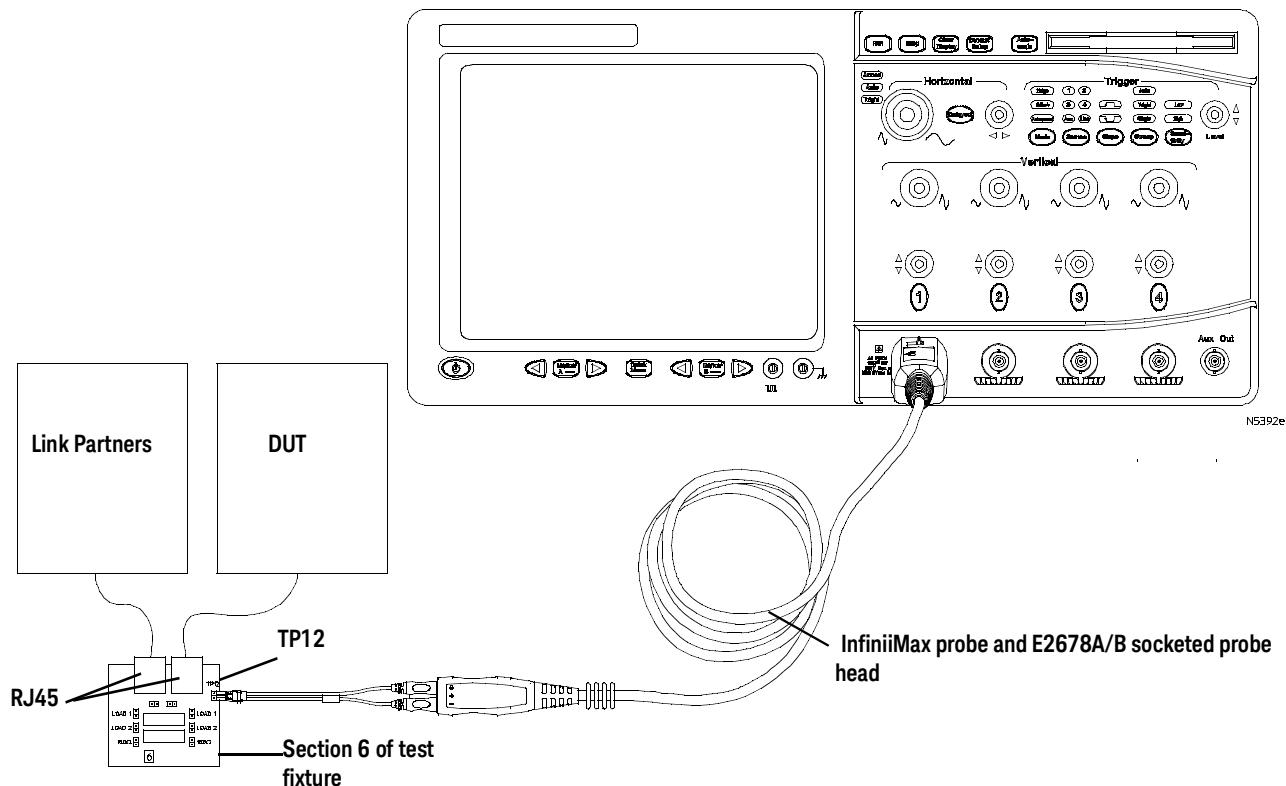

| <b>Probing for 100 Base-TX EEE Tests</b>                                  | 187 |

| <b>LPI Tests</b>                                                          | 188 |

| Quiet Time                                                                | 188 |

| Refresh Time                                                              | 188 |

| Transmitter Timing Jitter                                                 | 189 |

| <b>Sleep Time Test</b>                                                    | 190 |

| Sleep Time                                                                | 190 |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| <b>Wake Time Test</b>                                                      | 191 |

| Wake Time                                                                  | 191 |

| <b>9 10 Base-Te Tests</b>                                                  |     |

| <b>Test Loads</b>                                                          | 194 |

| <b>Measurements with TPM, Template Tests</b>                               | 195 |

| Probing for 10 Base-Te Tests with TPM and Link Partner                     | 195 |

| Link Test Pulse, with TPM                                                  | 197 |

| TP_IDL Template, with TPM (Last Bit CD0)                                   | 198 |

| TP_IDL Template, with TPM (Last Bit CD1)                                   | 201 |

| MAU Template                                                               | 203 |

| <b>Measurements with TPM, Parametric Tests</b>                             | 205 |

| Jitter with TPM                                                            | 205 |

| <b>Measurements Without TPM, Template Tests</b>                            | 208 |

| Probing for 10 Base-Te Tests Without TPM, With Link Partner                | 208 |

| Link Test Pulse, Without TPM                                               | 209 |

| TP_IDL Template, Without TPM (Last Bit CD0)                                | 211 |

| TP_IDL Template, Without TPM (Last Bit CD1)                                | 214 |

| <b>Measurements Without TPM, Parametric Tests</b>                          | 217 |

| Jitter Without TPM                                                         | 217 |

| Peak Differential Voltage                                                  | 219 |

| Harmonic Content                                                           | 220 |

| <b>Common Mode Voltage Tests</b>                                           | 222 |

| Common Mode Output Voltage                                                 | 222 |

| <b>Configuring 10 Base-Te Device Output</b>                                | 225 |

| Configuring a 10 Base-Te Device to Output Random Data                      | 225 |

| Configuring a 10 Base-Te Device to Output Manchester-Encoded Harmonic Ones | 226 |

| <b>10 InfiniMax Probing</b>                                                |     |

## Index

Keysight D9010ETHC Ethernet Compliance Test Application

Methods of Implementation

# 1 Overview

|                                                  |

|--------------------------------------------------|

| 1000 Base-T Tests by Standard Reference / 14     |

| 100 Base-TX Tests by Standard Reference / 14     |

| 10 Base-T Tests by Standard Reference / 15       |

| 1000 Base-T EEE Tests by Standard Reference / 15 |

| 100 Base-TX EEE Tests by Standard Reference / 15 |

| 10 Base-T Tests by Standard Reference / 16       |

The Ethernet Compliance Test Application performs the following tests as per the IEEE 802.3-2018, IEEE 802.3az, and ANSI X3.263-1995 standards.

**Table 1 1000 Base-T Tests by Standard Reference**

| Standard Reference                   | Description                    | See                     |

|--------------------------------------|--------------------------------|-------------------------|

| IEEE 802.3-2018 Subclause 40.6.1.2.1 | Output voltage                 | <a href="#">page 52</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.3 | Template test                  | <a href="#">page 58</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.2 | Droop test                     | <a href="#">page 59</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.4 | Transmitter distortion test    | <a href="#">page 67</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.5 | Jitter master unfiltered       | <a href="#">page 70</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.5 | Jitter master filtered         | <a href="#">page 73</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.5 | Jitter slave unfiltered        | <a href="#">page 77</a> |

| IEEE 802.3-2018 Subclause 40.6.1.2.5 | Jitter slave filtered          | <a href="#">page 80</a> |

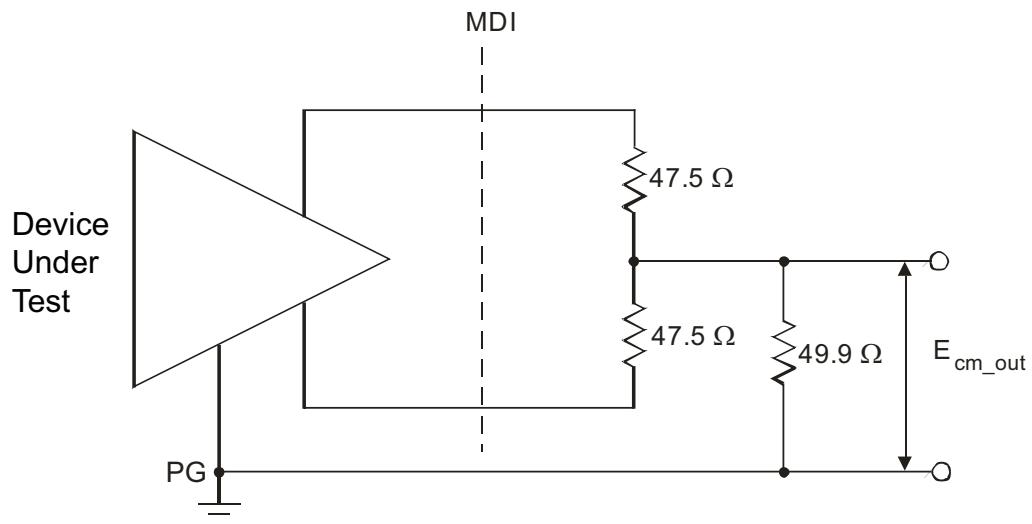

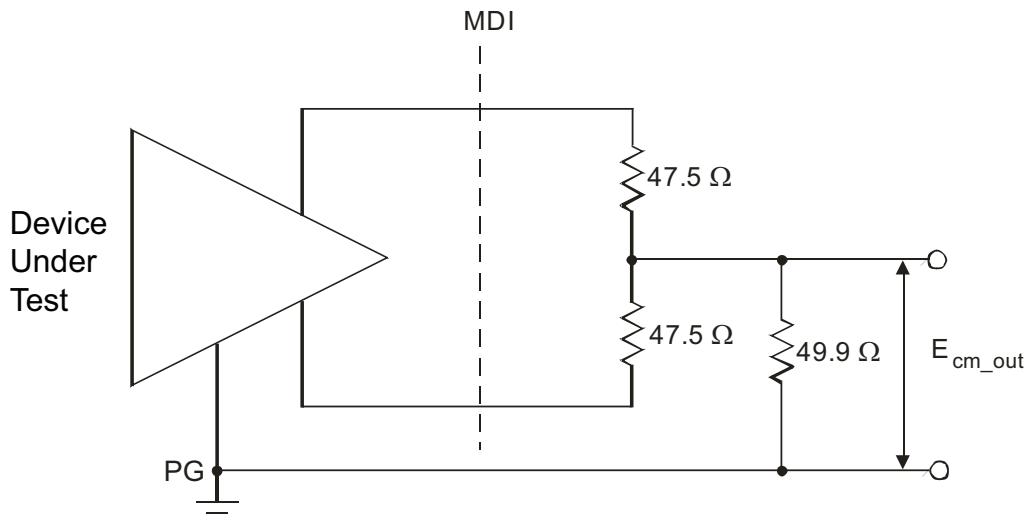

| IEEE 802.3-2018 Subclause 40.8.3.3   | MDI common mode output voltage | <a href="#">page 63</a> |

| IEEE 802.3-2018 Subclause 40.8.3.1   | MDI return loss                | <a href="#">page 94</a> |

**Table 2 100 Base-TX Tests by Standard Reference**

| Standard Reference                | Description                                | See                      |

|-----------------------------------|--------------------------------------------|--------------------------|

| ANSI X3.263-1995, Section 9.1.2.2 | UTP $+V_{out}$ differential output voltage | <a href="#">page 103</a> |

| ANSI X3.263-1995, Section 9.1.2.2 | UTP $-V_{out}$ differential output voltage | <a href="#">page 103</a> |

| ANSI X3.263-1995, Section 9.1.4   | Signal amplitude symmetry                  | <a href="#">page 104</a> |

| ANSI X3.263-1995, Section 9.1.3   | $+V_{out}$ overshoot                       | <a href="#">page 106</a> |

| ANSI X3.263-1995, Section 9.1.3   | $-V_{out}$ overshoot                       | <a href="#">page 106</a> |

| ANSI X3.263-1995, Annex J         | UTP AOI template                           | <a href="#">page 108</a> |

| ANSI X3.263-1995, Section 9.1.8   | Duty cycle distortion                      | <a href="#">page 113</a> |

| ANSI X3.263-1995, Section 9.1.9   | Transmit jitter                            | <a href="#">page 112</a> |

| ANSI X3.263-1995, Section 9.1.6   | AOI $+V_{out}$ rise time                   | <a href="#">page 110</a> |

| ANSI X3.263-1995, Section 9.1.6   | AOI $+V_{out}$ fall time                   | <a href="#">page 110</a> |

| ANSI X3.263-1995, Section 9.1.6   | AOI $+V_{out}$ rise/full-time symmetry     | <a href="#">page 110</a> |

| ANSI X3.263-1995, Section 9.1.6   | AOI $-V_{out}$ rise time                   | <a href="#">page 110</a> |

| ANSI X3.263-1995, Section 9.1.6   | AOI $-V_{out}$ fall time                   | <a href="#">page 110</a> |

| ANSI X3.263-1995, Section 9.1.6   | AOI $-V_{out}$ rise/fall time symmetry     | <a href="#">page 110</a> |

| ANSI X3.263-1995, Section 9.1.5   | Transmitter return loss                    | <a href="#">page 117</a> |

| ANSI X3.263-1995, Section 9.2.2   | Receiver return loss                       | <a href="#">page 122</a> |

**Table 3 10 Base-T Tests by Standard Reference**

| Standard Reference                                               | Description                      | See                      |

|------------------------------------------------------------------|----------------------------------|--------------------------|

| IEEE 802.3-2018 Subclause 14.3.1.2.1, Figure 14-12               | Template Link Pulse with TPM     | <a href="#">page 130</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.1, Figure 14-10               | Template TP_IDL with TPM         | <a href="#">page 133</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.1, Figure 14-9, Table 14-1    | Template MAU                     | <a href="#">page 137</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.3 and Annex B.4.1 and B.4.3.3 | Jitter with TPM                  | <a href="#">page 140</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.1, Figure 14-12               | Template Link Pulse without TPM  | <a href="#">page 144</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.1, Figure 14-10               | Template TP_IDL without TPM      | <a href="#">page 147</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.3 and Annex B.4.1 and B.4.3.3 | Jitter without TPM               | <a href="#">page 152</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.1                             | Peak differential output voltage | <a href="#">page 154</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.1                             | Harmonic content                 | <a href="#">page 155</a> |

| IEEE 802.3-2018 Subclause 14.3.1.2.5                             | Common mode output voltage       | <a href="#">page 157</a> |

| IEEE 802.3-2018 Subclause 14.3.1.3.4 and Annex B.4.3.5           | Receiver return loss             | <a href="#">page 167</a> |

**Table 4 1000 Base-T EEE Tests by Standard Reference**

| Standard Reference                                                       | Description               | See                      |

|--------------------------------------------------------------------------|---------------------------|--------------------------|

| IEEE 802.3az, Subclause 78.2, Table 78-2 and Subclause 40.4.5.2          | Quiet time                | <a href="#">page 176</a> |

| IEEE 802.3az, Subclause 40.4.6.1, Figure 40-15b and Subclause 40.4.5.2   | Refresh time              | <a href="#">page 176</a> |

| IEEE 802.3az, Subclause 40.4.5.2                                         | Sleep Time                | <a href="#">page 180</a> |

| IEEE 802.3az, Subclause 78.3, Figure 78-4 and Subclause 78.5, Table 78-4 | Wake Time                 | <a href="#">page 182</a> |

| IEEE 802.3az, Subclause 40.6.1.2.5                                       | Transmitter timing jitter | <a href="#">page 178</a> |

**Table 5 100 Base-TX EEE Tests by Standard Reference**

| Standard Reference                                                                     | Description               | See                      |

|----------------------------------------------------------------------------------------|---------------------------|--------------------------|

| IEEE 802.3az, Subclause 78.2, Table 78-2 and Subclause 24.8.3.5                        | Quiet time                | <a href="#">page 188</a> |

| IEEE 802.3az, Subclause 78.2, Table 78-2 and Subclause 24.8.3.5                        | Refresh time              | <a href="#">page 188</a> |

| IEEE 802.3az, Subclause 25.4.6                                                         | Transmitter timing jitter | <a href="#">page 189</a> |

| IEEE 802.3az, Subclause 78.2, Table 78-2, Subclause 24.2.2.1.1, and Subclause 24.8.3.5 | Sleep time                | <a href="#">page 190</a> |

| IEEE 802.3az, Subclause 78.3, Figure 78-4 and Subclause 78.5, Table 78-4               | Wake time                 | <a href="#">page 191</a> |

**Table 6 10 Base-T Tests by Standard Reference**

| Standard Reference                                                                           | Description                              | See                      |

|----------------------------------------------------------------------------------------------|------------------------------------------|--------------------------|

| IEEE 802.3az, Subclause 14.3.1.2.1 and IEEE 802.3-2018, Subclause 14.3.1.2.2                 | Link test pulse, with TPM                | <a href="#">page 197</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.1                                                        | TP_IDL template, with TPM (last bit CDO) | <a href="#">page 198</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.1                                                        | TP_IDL Template, with TPM (last bit CD1) | <a href="#">page 201</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.1                                                        | MAU template                             | <a href="#">page 203</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.3, Annex B.4.3.3, and Annex B.4.1 "System Jitter budget" | Jitter with TPM                          | <a href="#">page 205</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.1 and Subclause 14.3.1.2.2                               | Link test pulse, without TPM             | <a href="#">page 209</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.1                                                        | TP_IDL template, without TPM             | <a href="#">page 211</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.3, Annex B.4.3.3, and Annex B.4.1 "System Jitter Budget" | Jitter without TPM                       | <a href="#">page 217</a> |

| IEEE 802.3az, Subclause 14.3.1.2.1                                                           | Peak differential voltage                | <a href="#">page 219</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.1                                                        | Harmonic content                         | <a href="#">page 220</a> |

| IEEE 802.3-2018, Subclause 14.3.1.2.7                                                        | Common mode output voltage               | <a href="#">page 222</a> |

## 2 Installing the Ethernet Compliance Test Application

Installing the Software / 18

Installing the License Key / 19

If you purchased the D9010ETHC Ethernet Compliance Test Application separately, you must install the software and license key.

## Installing the Software

- 1    Make sure you have the required version of the Infinium oscilloscope software:

- a    See the compliance test application release notes for the required minimum version of the software.

- b    To check the software version on the oscilloscope, choose Help>About Infinium... from the main menu.

- 2    To obtain the Ethernet Compliance Test Application, go to the Keysight Web site:

<http://www.keysight.com/en/pc-1152185/oscilloscope-software>.

- 3    Navigate to the D9010ETHC Ethernet Compliance software download.

- 4    Follow the instructions to download and install the application software.

## Installing the License Key

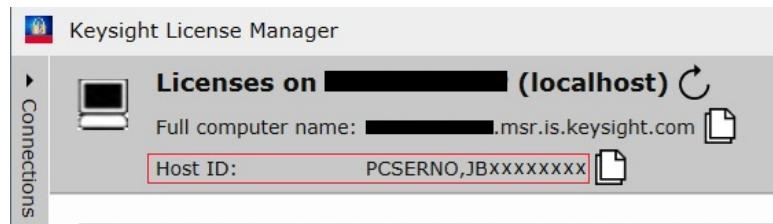

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

### Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

Figure 1 Viewing the Host ID information in Keysight License Manager 5

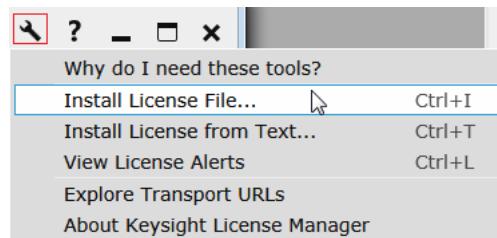

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

- 3 From the configuration menu, use one of the options to install each license file.

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to [Keysight License Manager 5 Supporting Documentation](#).

## Using Keysight License Manager 6

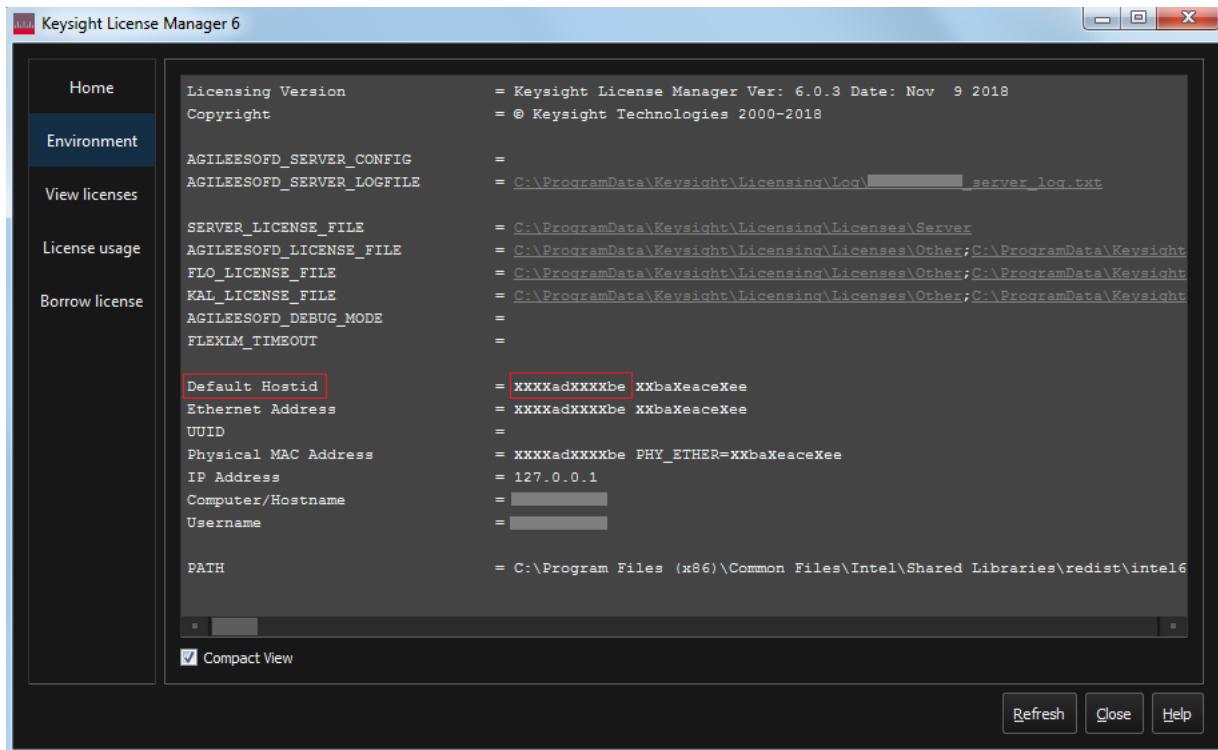

To view and copy the Host ID from Keysight License Manager 6:

- 1 Launch Keysight License Manager 6 on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID, which is the first set of alphanumeric value (as highlighted in [Figure 3](#)) that appears in the Environment tab of the application. Note that x indicates numeric values.

Figure 3 Viewing the Host ID information in Keysight License Manager 6

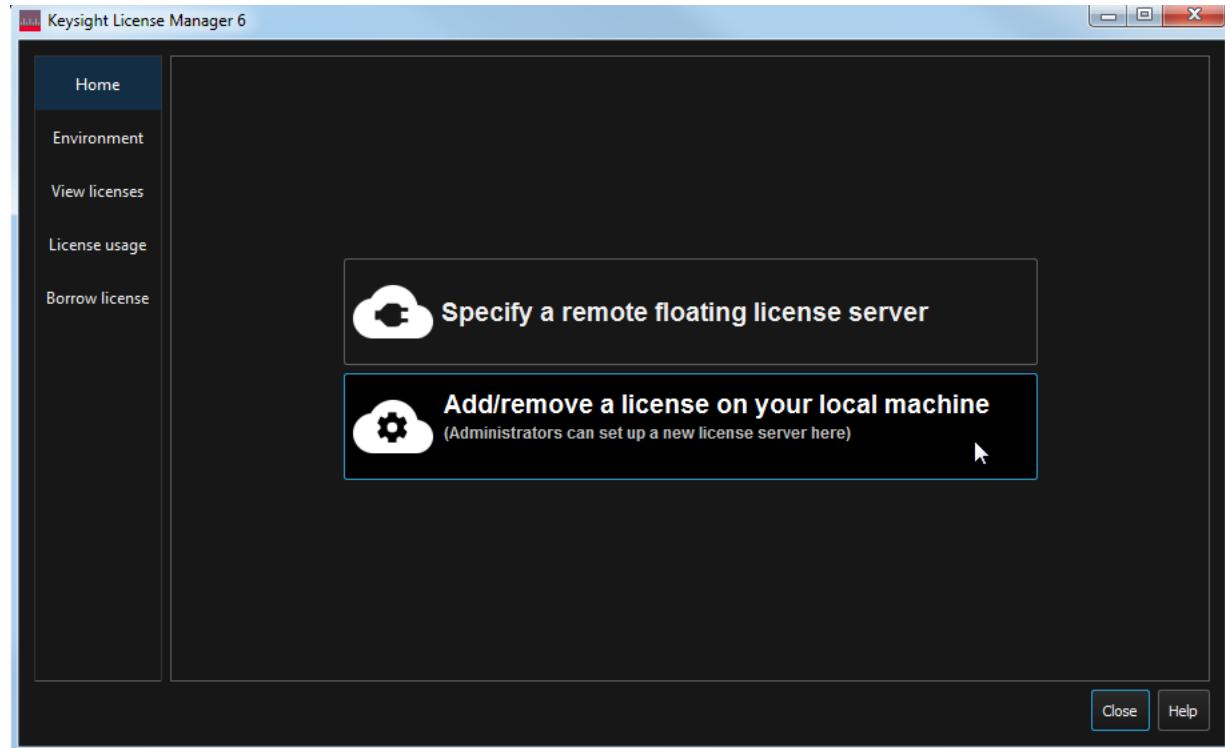

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager 6.

- 3 From the Home tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to [Keysight License Manager 6 Supporting Documentation](#).

# 3 Preparing to Take Measurements

|                                                      |      |

|------------------------------------------------------|------|

| Required and Recommended Equipment                   | / 24 |

| Calibrating the Oscilloscope                         | / 29 |

| Adding Instruments to the Keysight Connection Expert | / 30 |

| Starting the Ethernet Compliance Test Application    | / 34 |

| Selecting the Probe Head                             | / 37 |

Before running the Ethernet automated tests, you need to acquire the appropriate test fixtures, and you should calibrate the oscilloscope. After the oscilloscope has been calibrated, you are ready to start the Ethernet Compliance Test Application and perform the measurements.

## Required and Recommended Equipment

### Test Fixtures

#### N5395C Ethernet Electrical Compliance Test Fixture

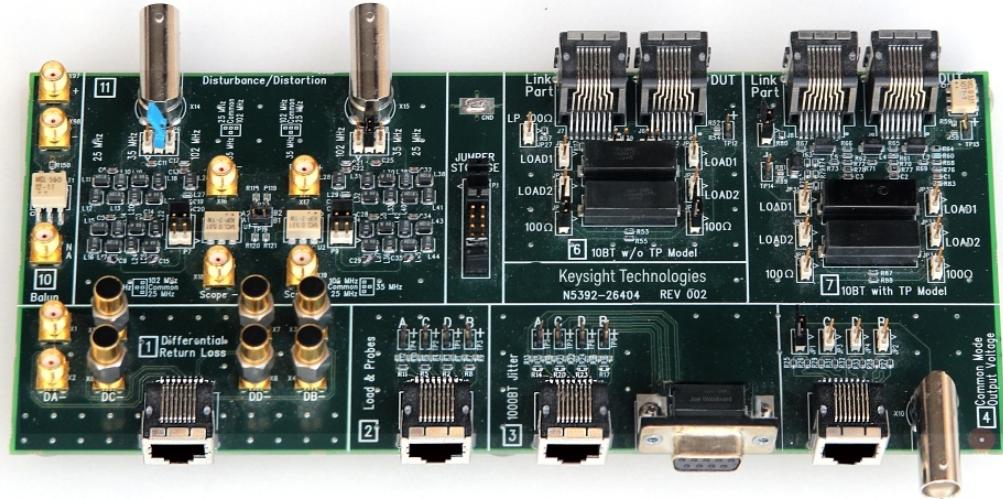

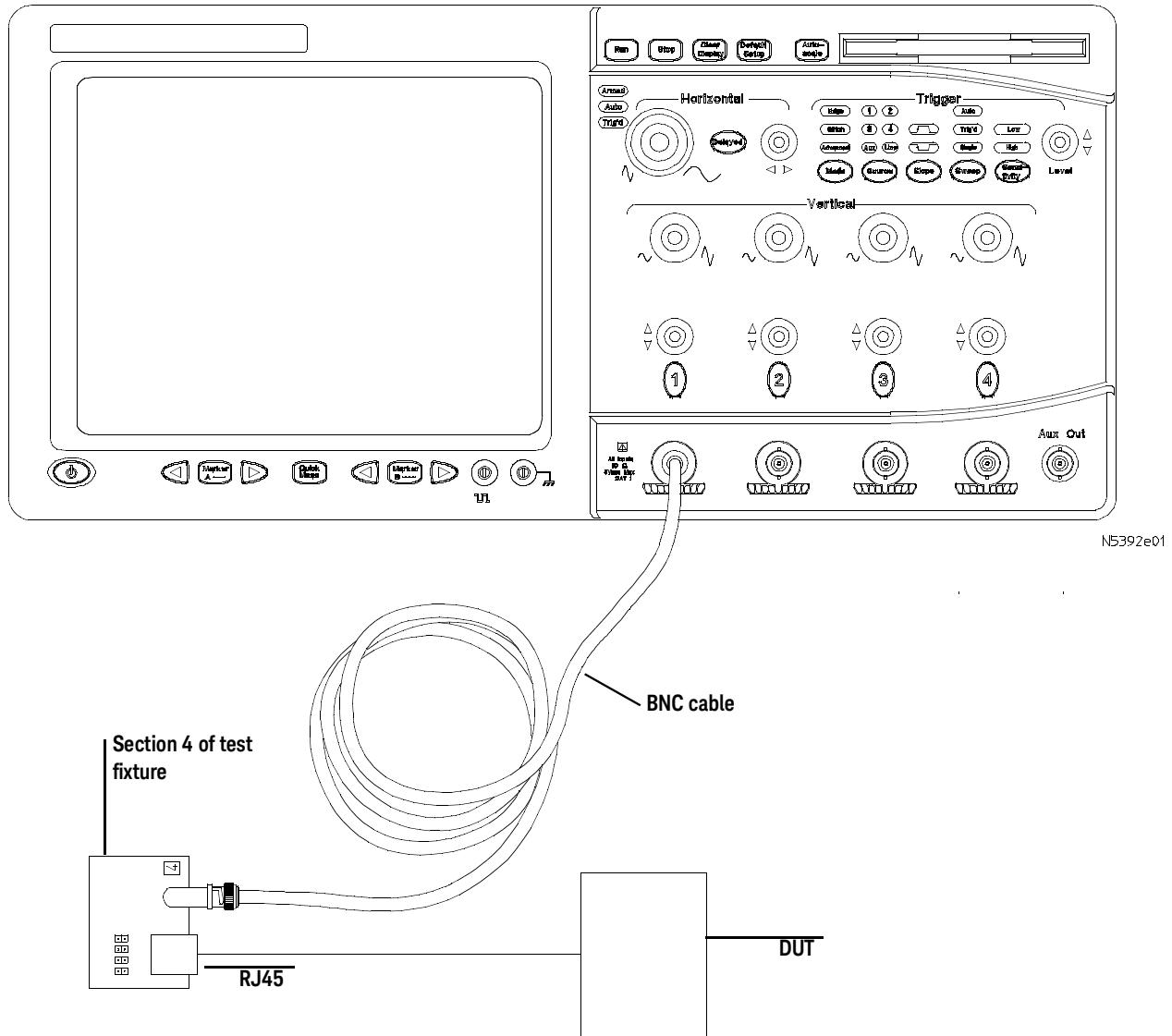

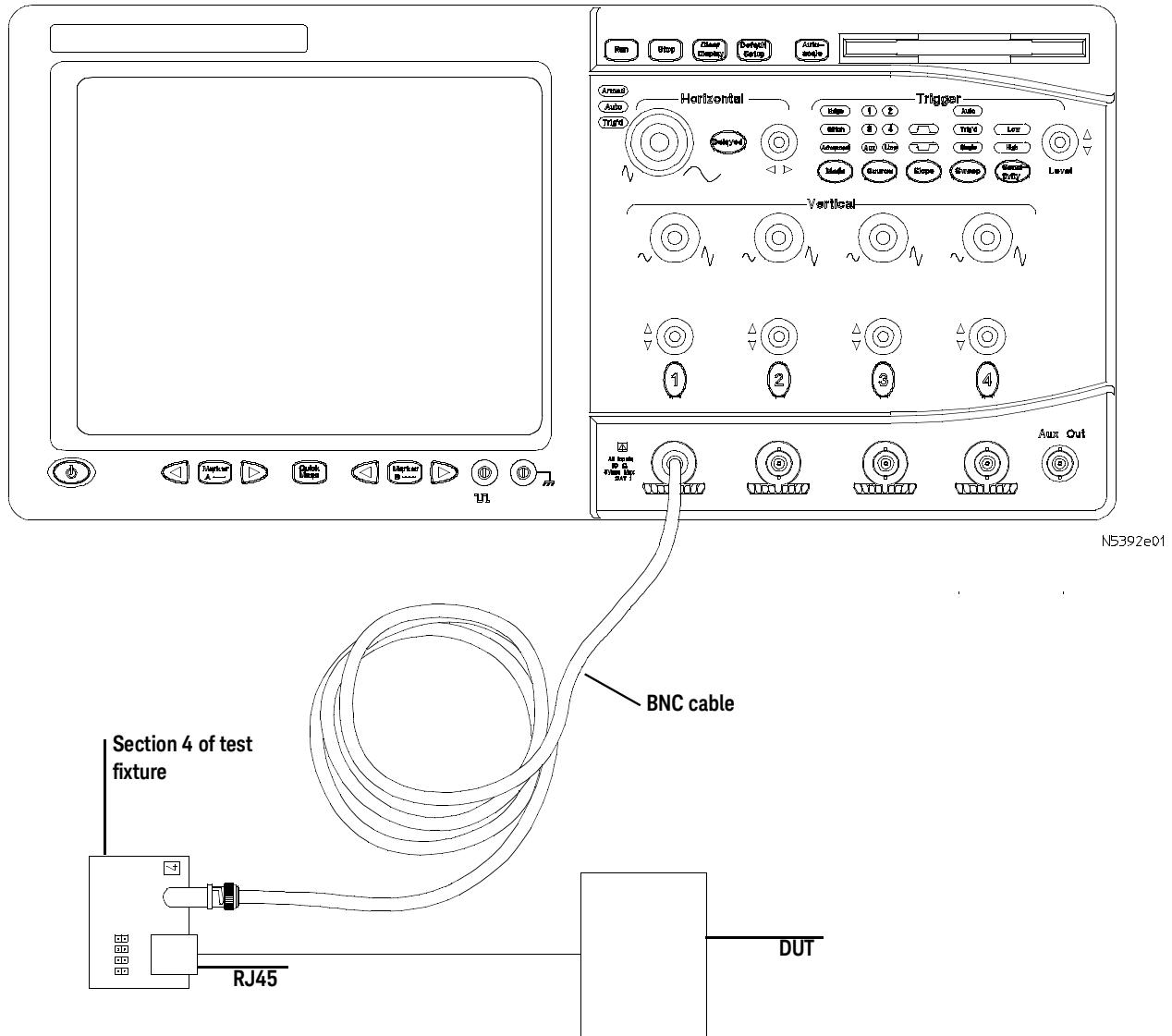

To use the D9010ETHC Ethernet electrical performance validation and compliance software, you also need the Keysight N5395C Ethernet electrical compliance test fixture, at least one InfiniiMax active differential probe (1131A/B, 1132A/B, or 1134A/B) with E2678A/B socketed differential probe head, and a BNC cable (for 1000 Base-T and 10 Base-T measurements only).

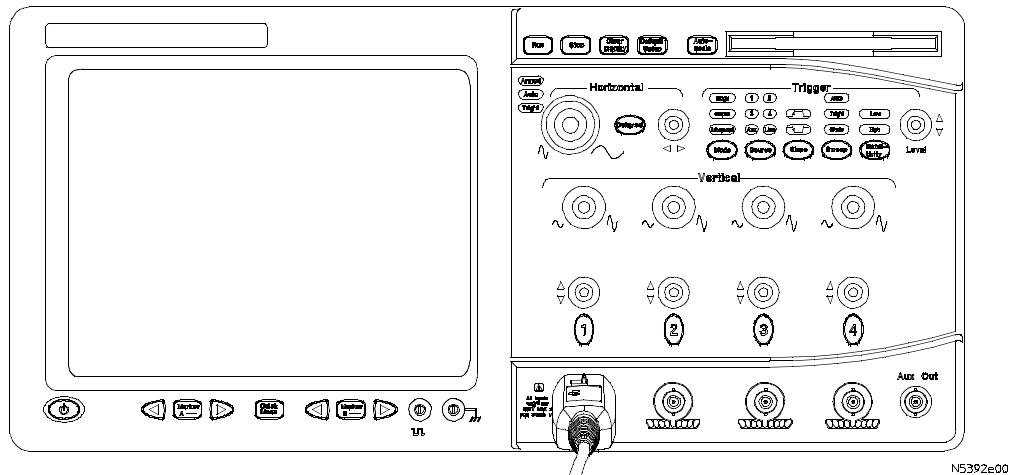

Figure 5 shows the N5395C Ethernet electrical compliance test board.

Figure 5 N5395C Ethernet Electrical Compliance Test Board

Table 7 shows the components of N5395C Ethernet electrical compliance test board. The N5395C test fixture is RoHS compliant.

Table 7 Components of N5395C Ethernet Electrical Compliance Test Board

| Probes and BNC Cables | 1000 Base-T Measurements                                 |

|-----------------------|----------------------------------------------------------|

| N5392-61601           | Short RJ-45 cable for the Ethernet test application      |

| N5392-66401           | Return loss calibration test fixture                     |

| N5392-66402           | Test fixture for the D9010ETHC Ethernet test application |

The Keysight Ethernet electrical compliance test fixture includes a main test fixture board, a short RJ-45 interconnect cable, and a small impedance calibration board. Probing points on the main test fixture board allow most oscilloscope measurements to be made using a Keysight InfiniiMax differential probe (1131A/B, 1132A/B or 1134A/B) with an E2678A/B socketed differential probe head. Some measurements are made using a BNC cable. The 1000 Base-T jitter measurements are best made using two Keysight InfiniiMax active differential probes with E2677A/B solder-in differential probe heads.

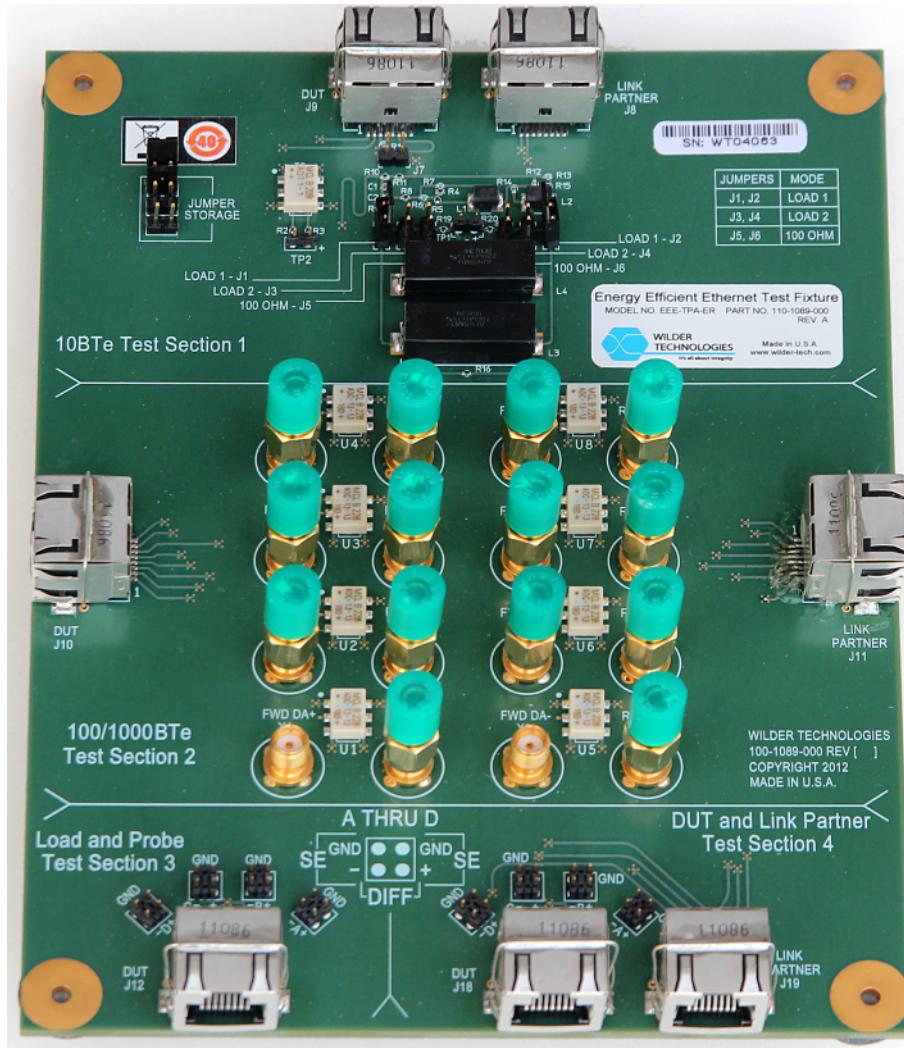

### Wilder Technologies 110-1089-000 EEE Electrical Compliance Test Fixture

To use the Ethernet electrical performance validation and compliance software for EEE compliance testing, you also need the Wilder Technologies 110-1089-000 EEE electrical compliance test fixture, at least one InfiniiMax active differential probe with E2678A/B socketed differential probe head, SMA cables, and a BNC cable. For the complete EEE fixture kit which includes fixture, two short Ethernet cables, and fourteen 50 Ω terminators, order part number 640-0581-001 (EEE-TPA-ERK).

Figure 6 Wilder Technologies EEE Electrical Compliance Test Board

### N5396A Gigabit Ethernet Jitter Test Cable

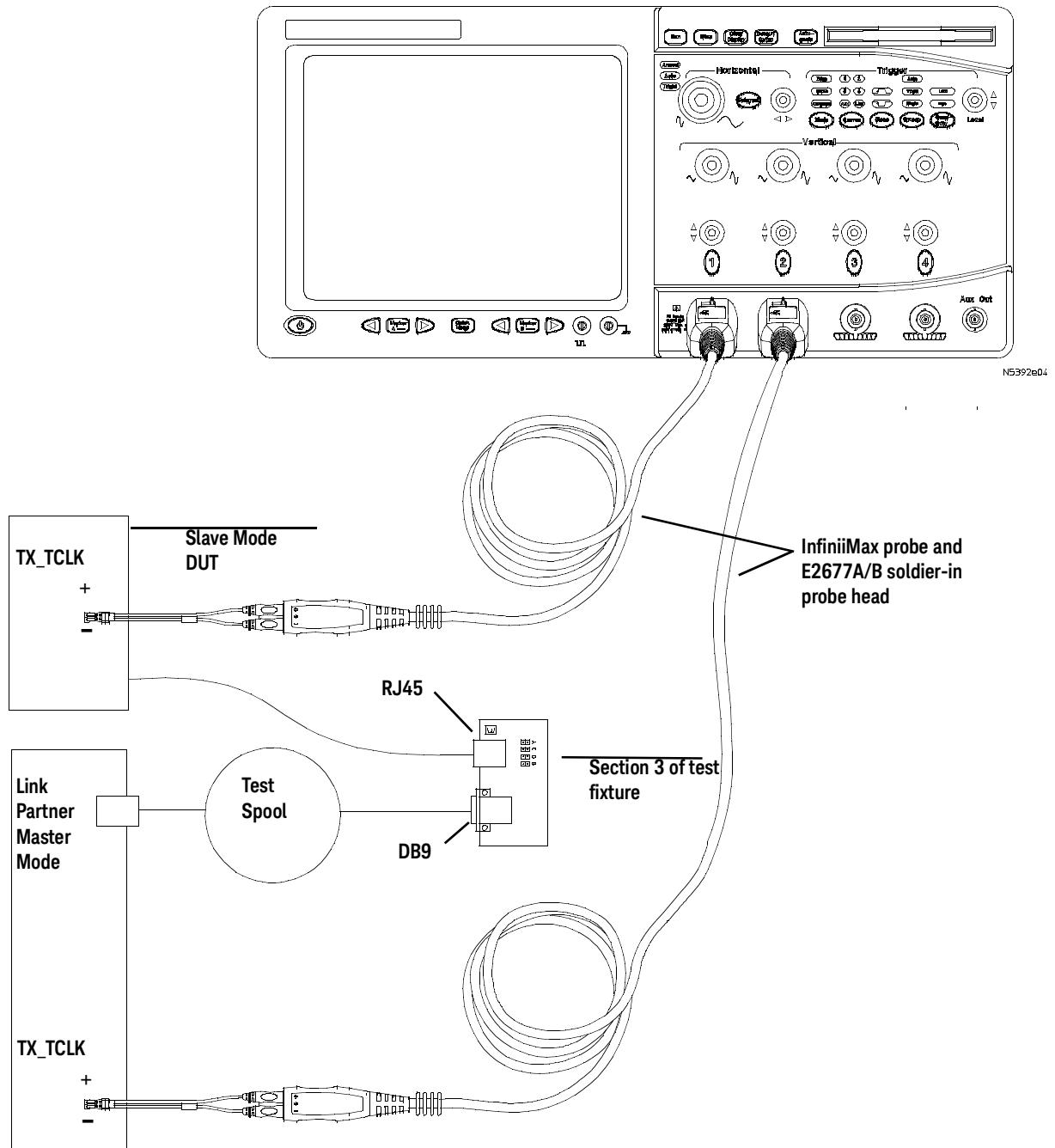

To make jitter measurements for 1000 Base-T, you need to use the N5396A Gigabit Ethernet jitter test cable along with the Ethernet test fixture, a second InfiniiMax active differential probe, and two E2677A/B solder-in differential probe heads.

The N5396A Gigabit Ethernet jitter test cable allows you to make 1000 Base-T jitter measurements with the Ethernet electrical compliance test fixture. The 103-m cable has a RJ-45 connector on one end to connect to a Link Partner, and a DB9 connector on the other end to connect to the Ethernet test fixture board.

## Tests Supported by the Wilder Technologies 110-1089-000 EEE Test Fixture

The Wilder Technologies 110-1089-000 EEE electrical compliance test fixture provides some testing capability that is currently not automated by the Ethernet electrical performance validation and compliance software. Some of these tests require other equipment. The following tables list the tests supported by each section of the test fixture, the tests that are automated/supported by the D9010ETHC software, and other hardware requirements.

- VNA = Vector Network Analyzer required.

- LP = Link Partner Required.

**Table 8 1000 Base-T EEE Tests Supported by the 110-1089-000 EEE Test Fixture**

| Test Name        | EEE Test Fixture Section | LP |

|------------------|--------------------------|----|

|                  |                          | 2  |

| LPI Tests        | X                        | X  |

| Sleep Time Tests | X                        | X  |

| Wake Time Tests  | X                        | X  |

**Table 9 100 Base-TX EEE Tests Supported by the 110-1089-000 EEE Test Fixture**

| Test Name        | EEE Test Fixture Section | LP |

|------------------|--------------------------|----|

|                  |                          | 4  |

| LPI Tests        | X                        | X  |

| Sleep Time Tests | X                        | X  |

| Wake Time Tests  | X                        | X  |

**Table 10 10 Base-Tx Tests Supported by the 110-1089-000 EEE Test Fixture**

| Test Name                          | Ethernet Test Fixture Section |   |   |    |    | EEE Test Fixture Section | LP | VNA |

|------------------------------------|-------------------------------|---|---|----|----|--------------------------|----|-----|

|                                    | 1                             | 4 | 6 | 10 | 11 |                          |    |     |

| Differential Output Voltage        |                               |   | X |    |    |                          |    |     |

| MAU Template                       |                               |   |   |    |    | X                        |    |     |

| TP_IDL/Link Pulse Template w/ TPM  |                               |   |   |    |    | X                        |    |     |

| TP_IDL/Link Pulse Template w/o TPM |                               |   | X |    |    |                          |    |     |

| Jitter, w/ TPM                     |                               |   |   |    |    | X                        |    |     |

| Jitter, w/o TPM                    |                               |   | X |    |    |                          |    |     |

| Harmonic Content                   |                               |   | X |    |    |                          |    |     |

| Common Mode Output Voltage         |                               | X |   |    |    |                          |    |     |

| Return Loss                        | X                             |   |   | X  |    |                          |    | X   |

## Oscilloscope Compatibility and Recommended Probe Amplifiers

**Table 11 Recommended Oscilloscopes and Recommended Probe Amplifiers**

| Standard    | Data Rate                        | Recommended Oscilloscope | Oscilloscope Bandwidth | Recommended Probe | Probe Bandwidth |

|-------------|----------------------------------|--------------------------|------------------------|-------------------|-----------------|

| 10 Base-T   | 10 Mb/s                          | Infiniium                | ≥ 600 MHz              | 113xA/B Series    | ≥ 3.5 GHz       |

| 100 Base-TX | 100 Mb/s                         | Infiniium                | ≥ 600 MHz              | 113xA/B Series    | ≥ 3.5 GHz       |

| 1000 Base-T | Gigabit Ethernet<br>(4x250 Mb/s) | Infiniium                | ≥ 1 GHz                | 113xA/B Series    | ≥ 3.5 GHz       |

## Number of Probes and BNC Cables Required

**Table 12 Number of Probes and BNC Cables Required**

| Probes and BNC Cables                      | 1000 Base-T Measurements | 100 Base-TX Measurements | 10 Base-T Measurements |

|--------------------------------------------|--------------------------|--------------------------|------------------------|

| InfiniMax active differential probe        | 2                        | 1                        | 1                      |

| E2677A/B solder-in differential probe head | 2                        |                          |                        |

| E2678A/B socketed differential probe head  | 1                        | 1                        | 1                      |

| BNC cable                                  | 4                        |                          | 1                      |

## Supported Vector Network Analyzers for Return Loss Tests

- 8752x/3x Models

- 4395x/6x Models

- E5070x/71x Models

- E5061x/62x Models

- N5230A Model

- N9917A Model

- E5080B Model

- E5063A Model

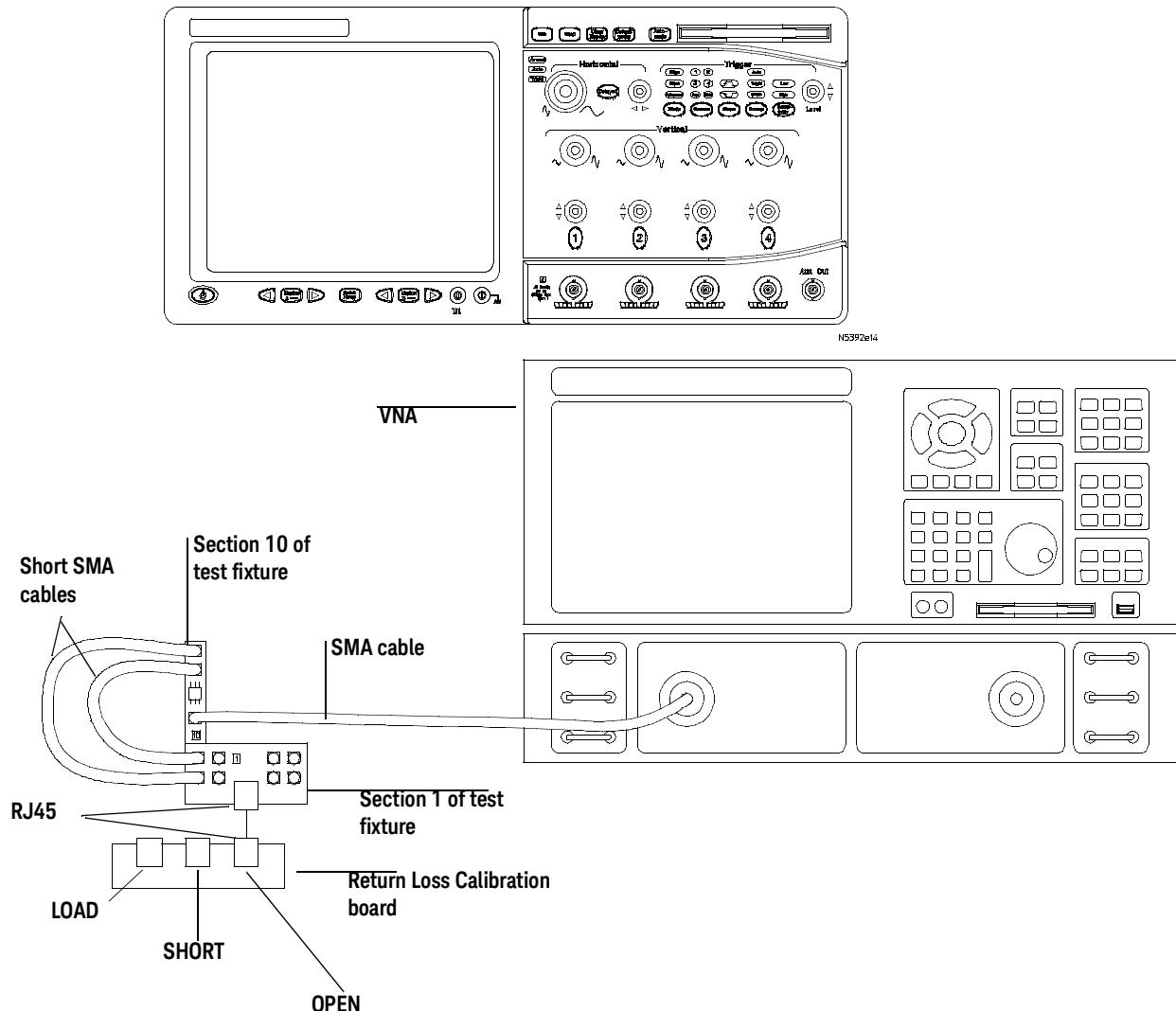

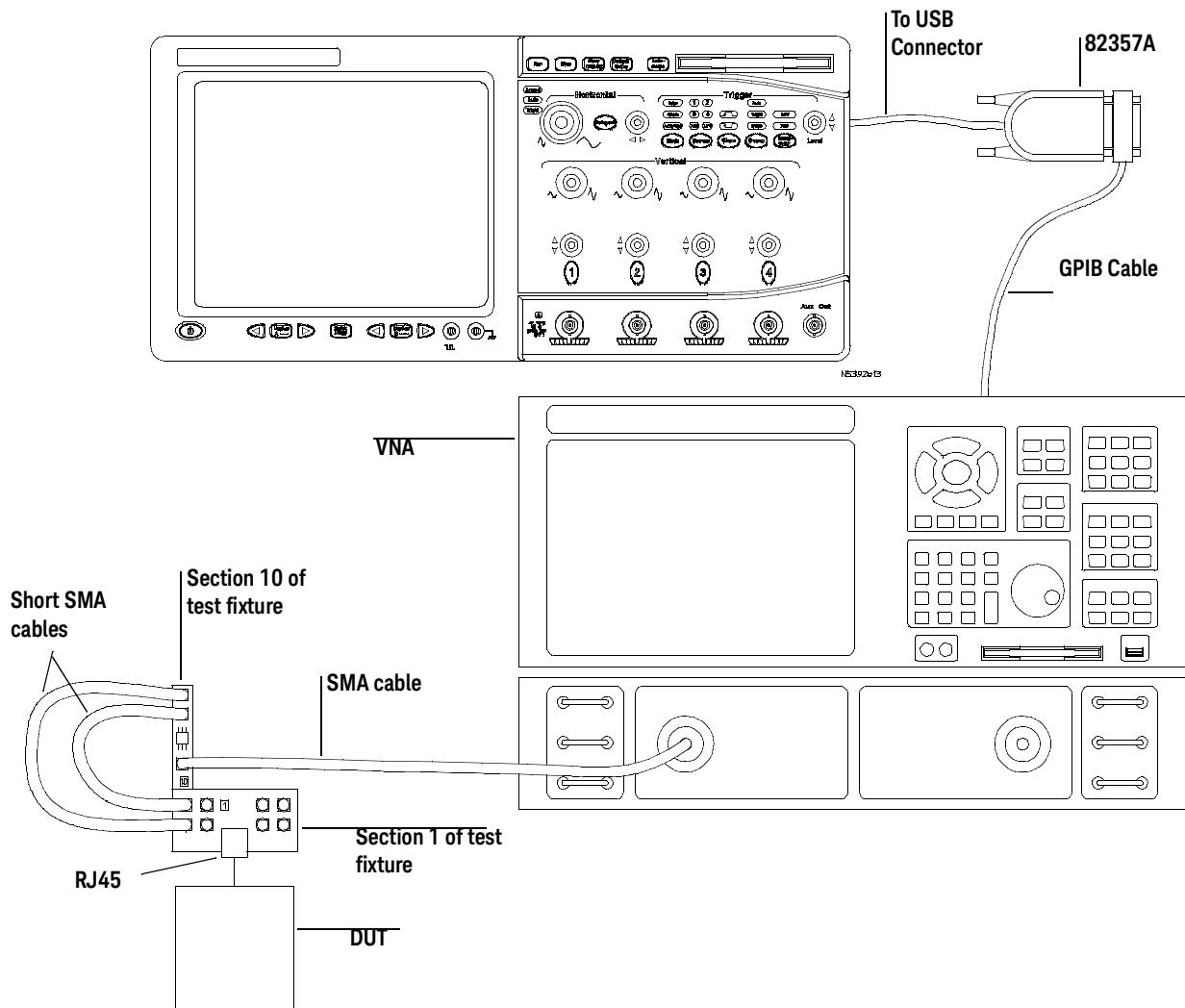

Note: Before using the Vector Network Analyzers (VNA), it has to be calibrated and configured. The VNA should support a minimum of 1 MHz usable power range. For more details on VNA calibration, please refer to these chapters: [“MDI Return Loss,” starting on page 94](#), [“Transmitter Return Loss,” starting on page 117](#), [“Receiver Return Loss,” starting on page 122](#), [“Transmitter Return Loss,” starting on page 162](#) and [“Receiver Return Loss,” starting on page 167](#).

## Recommended Accessories

**Table 13 Recommended Test Accessories**

| Keysight Part Number | Description                                                                                                      |

|----------------------|------------------------------------------------------------------------------------------------------------------|

| 8120-1839            | BNC cable (61 cm, 2 ft.)                                                                                         |

| 8120-4948            | SMA cable (90 cm, 3 ft.)                                                                                         |

| 82357A/B             | USB to GPIB Convertor                                                                                            |

| 33250A               | Function/Arbitrary Waveform Generator, Qty 2                                                                     |

| Not available        | Optional push on SMA connectors for most efficient connection. Order 33SMA-Q50-0-4 from S.M. Electronics, Qty 6. |

## Recommended Infiniium Oscilloscope for Jitter and Distortion Test

For jitter and distortion test, it is recommended to have at least 8M points of memory. Hence, option 001 is recommended for the 54850 and 80000 Series oscilloscopes for best performance. Option 080 is recommended for the 54830 and 8000 Series oscilloscopes.

## Required Software

The minimum version of Infiniium oscilloscope software (see the D9010ETHC test application release notes).

## Calibrating the Oscilloscope

If you have not already calibrated the oscilloscope, refer to the documentation for your oscilloscope and probes for the relevant procedures.

### NOTE

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the Utilities>Calibration menu.

### NOTE

If you switch cables or probes between channels or other oscilloscopes, it is necessary to perform cable and probe calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel for which they were calibrated.

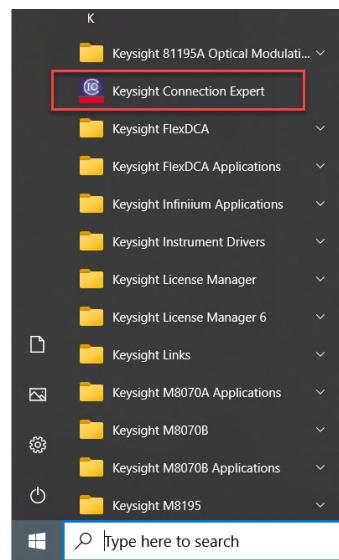

## Adding Instruments to the Keysight Connection Expert

Note that the Keysight I/O Library Suite must be installed on your machine before you add instruments to the Keysight Connection Expert. The user interface for Keysight Connection Expert 2022 (Version 18.2 and higher) is slightly different from its previous versions, such as Version 17.2 or earlier.

- 1 From the Windows **Start** menu, click **Keysight Connection Expert** to launch Connection Expert. Refer to [Keysight IO Libraries Suite](#) for information on how to install the Keysight Connection Expert.

Figure 7 Launching the Keysight Connection Expert

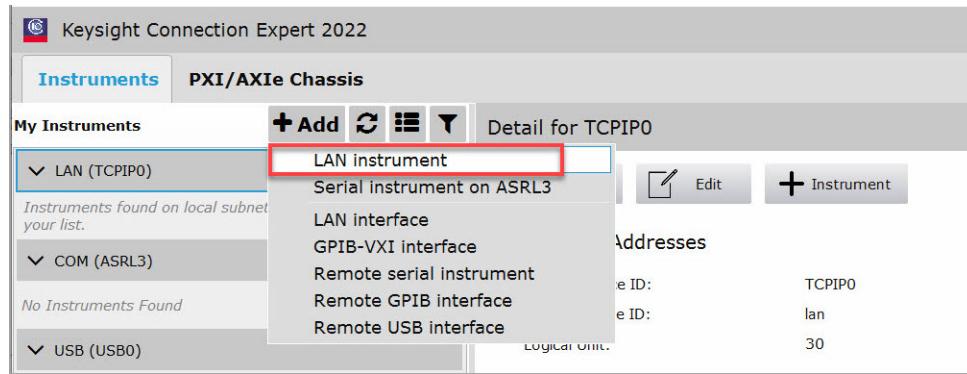

The **Keysight Connection Expert** window appears with the **Instruments** tab selected by default.

Figure 8 Keysight Connection Expert Window

2 To manually add instruments and interfaces, click **Add** (as highlighted in the above figure) and select **LAN instrument** from the drop-down options.

Figure 9 Selecting LAN Instrument option

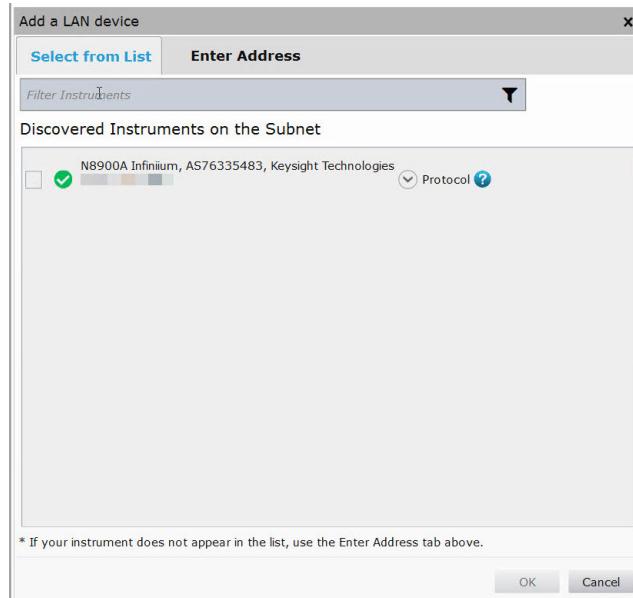

3 The **Select from List** tab appears with the list of instruments discovered on the Subnet (if any). Select the check box in front of the required instrument and click **OK** to add instrument. If your instrument does not appear in this list, then proceed to the next step.

Figure 10 Add a LAN device window-Select from List tab

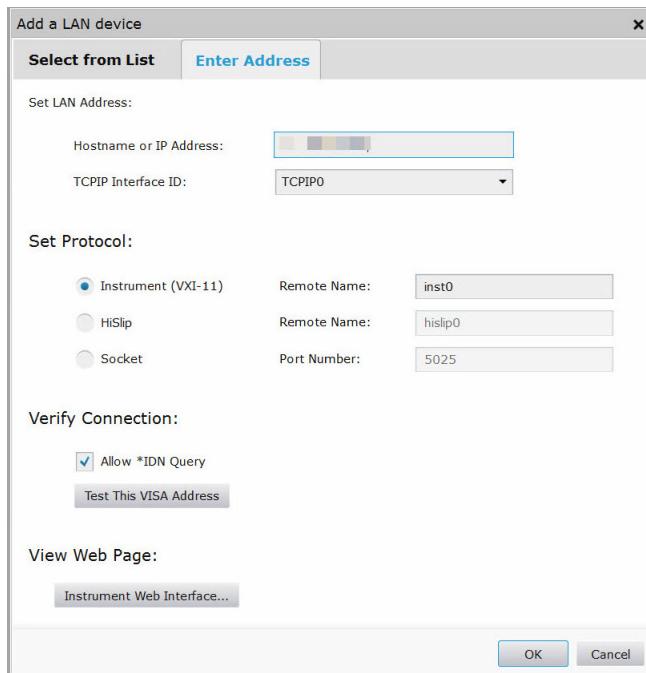

4 Click the **Enter Address** tab and perform the following steps:

- Under the **Set LAN Address:** area, enter the Hostname or IP Address of the instrument in the **Hostname or IP Address** field.

It is recommended to use the IP address of the instruments in the **Hostname or IP Address** field.

**NOTE**

- b Under the **Set Protocol:** area, the **Instrument (VXI-11)** option is selected by default and remote name displays in the **Remote Name** field. If required, you can select the **HiSlip** or **Socket** option and enter the remote name or port number in the corresponding **Remote Name** or **Port Number** fields.

- c Under the **Verify Connection:** area, click the **Test This VISA Address** to verify the entered Hostname or IP Address.

Figure 11 Adding instrument information in the Keysight Connection Expert

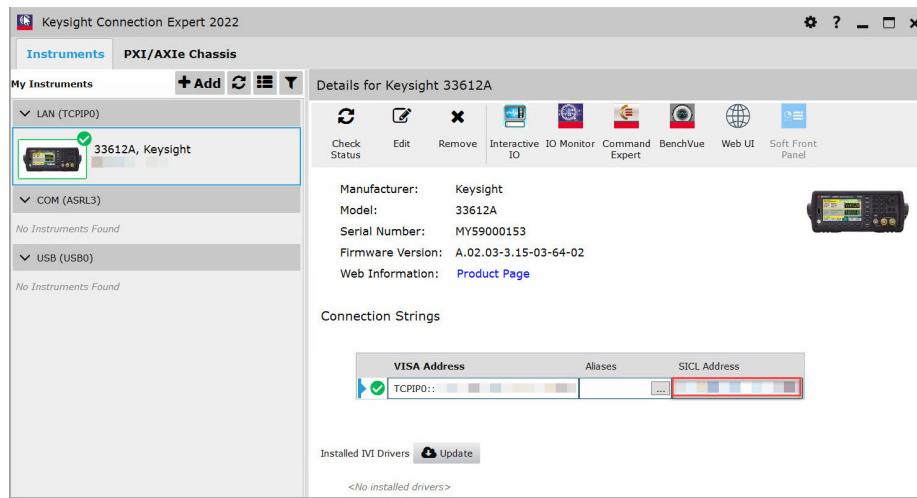

- d Once you verified the entered Hostname or IP Address, click **OK** to connect the instrument. The Keysight Connection Expert window appears with the **Instruments** tab selected. On the left pane, under **My Instruments**, the connected instrument name displays with the check mark encircled in green indicating that the instrument is connected to your PC remotely on the LAN. The details of the connected instrument displays on the right pane.

Figure 12 Validating Instrument Connection

- 5 Copy the **SICL Address** (as highlighted in the above figure) of the connected instrument to the clipboard, as you will need it later to configure this instrument in the application. To know more about configuring external instruments in the application, refer to the “External Instruments” section in the “Setting Up the Test Environment” topic of the *Keysight D9010ETHC Ethernet Test Application Online Help*.

- 6 Close the Keysight Connection Expert window.

## Starting the Ethernet Compliance Test Application

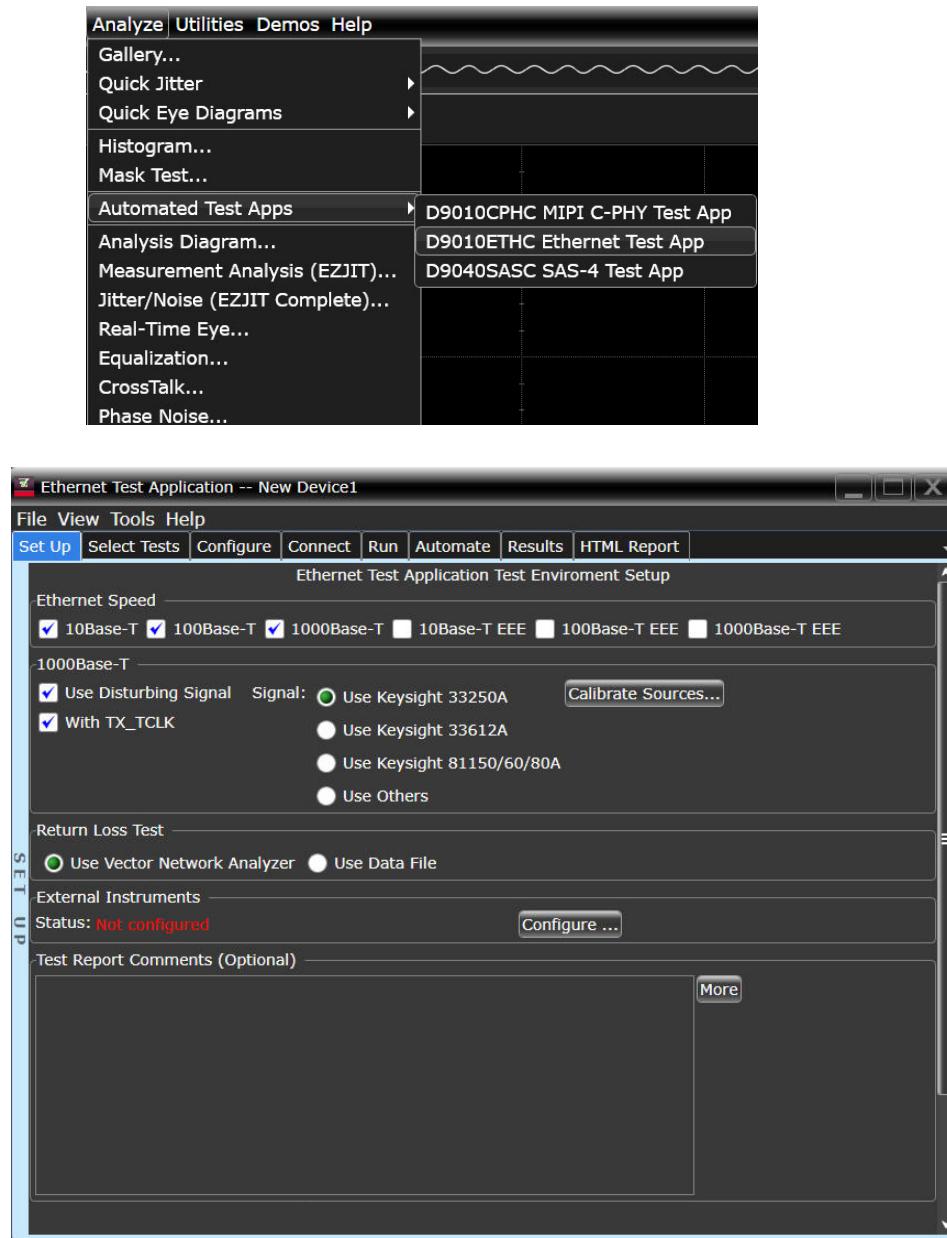

- 1 From the Infiniium oscilloscope's main menu, choose **Analyze > Automated Test Apps > D9010ETHC Ethernet Test App**.

Figure 13 The Ethernet Compliance Test Application

**NOTE**

If Ethernet does not appear in the Automated Test Apps menu, the Ethernet Compliance Test Application has not been installed (see [Chapter 2](#), “Installing the Ethernet Compliance Test Application”). Or, one or more licenses required to run the Ethernet Test Application are not installed on the Oscilloscope. You may also discover missing license information by launching the Test Application under the Analyze > Unlicensed Apps menu of the Infiniium Application. During startup, the Test Application displays a detailed license message.

[Figure 13](#) shows the Ethernet Compliance Test Application main window. The task flow pane and the tabs in the main pane show the steps you take in running the automated tests:

| Tab          | Description                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Up       | Lets you select the Ethernet standards being tested. Lets you select whether or not a disturbing signal is used for testing 1000 Base-T. Lets you configure and calibrate external equipment. Lets you select the type of return loss test to run.                         |

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |

| Configure    | Lets you configure test parameters. The information appears in the HTML report.                                                                                                                                                                                            |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Automation   | Lets you construct scripts of commands that drive execution of the application.                                                                                                                                                                                            |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

### Online Help Topics

For information on using the Ethernet Compliance Test Application, see its online help (which you can access by choosing Help>Contents... from the application’s main menu).

The Ethernet Compliance Test Application’s online help describes the following:

- Starting the Ethernet Compliance Test Application

- Creating or Opening a Test Project

- Setting Up the Test Environment

- Setting Up InfiniiSim

- Setting Up the Precision Probe/Cable

- Selecting Tests

- Configuring Tests

- Connecting the Oscilloscope to the DUT

- Running Tests

- Automating the Application

- Viewing Results

- Viewing/Exporting/Printing the HTML Test Report

- Understanding the Report

- Saving Test Projects

- User-Defined Add-Ins

- Controlling the Application via a Remote PC

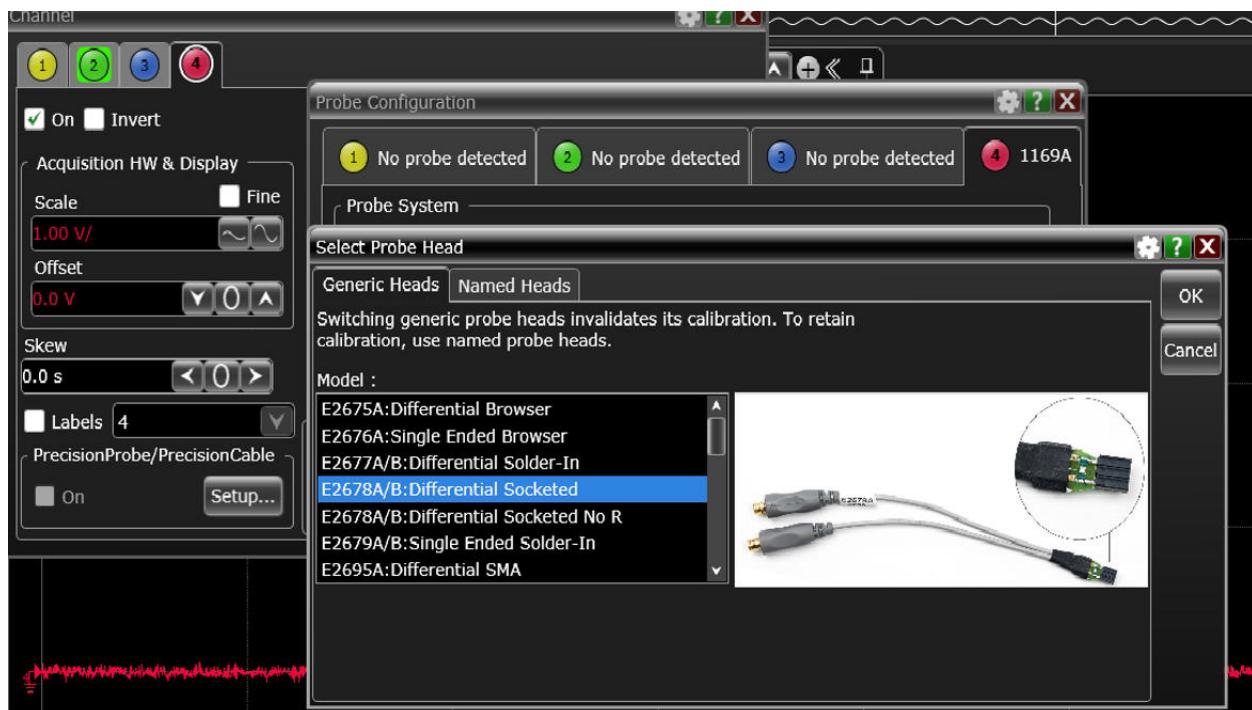

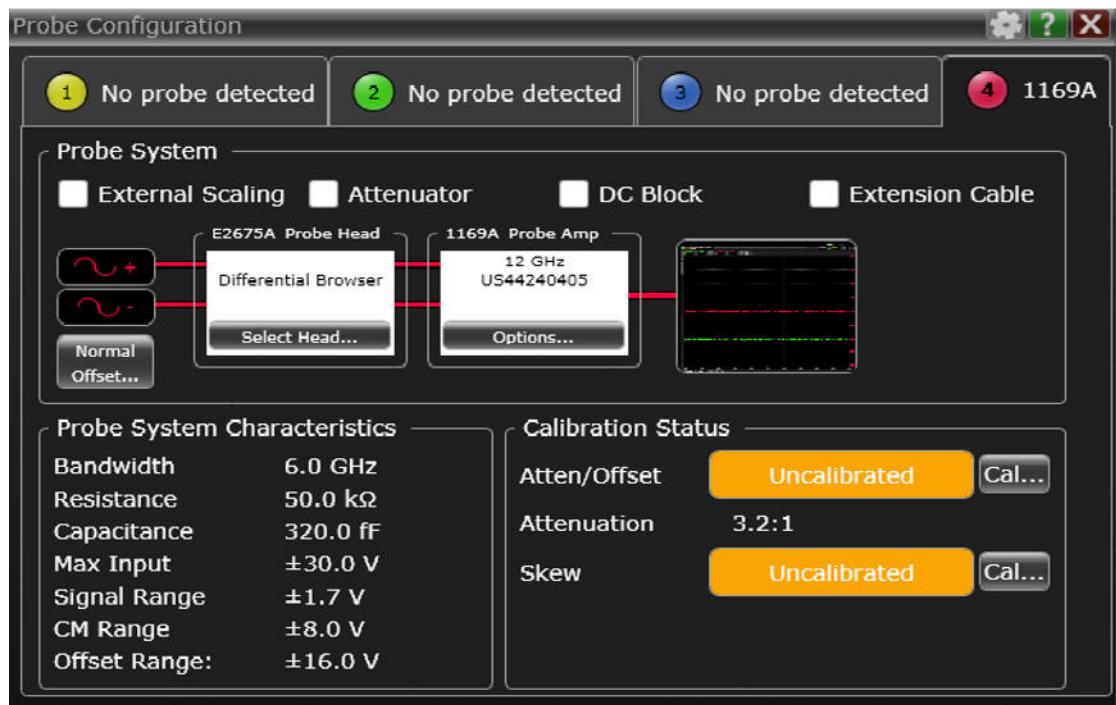

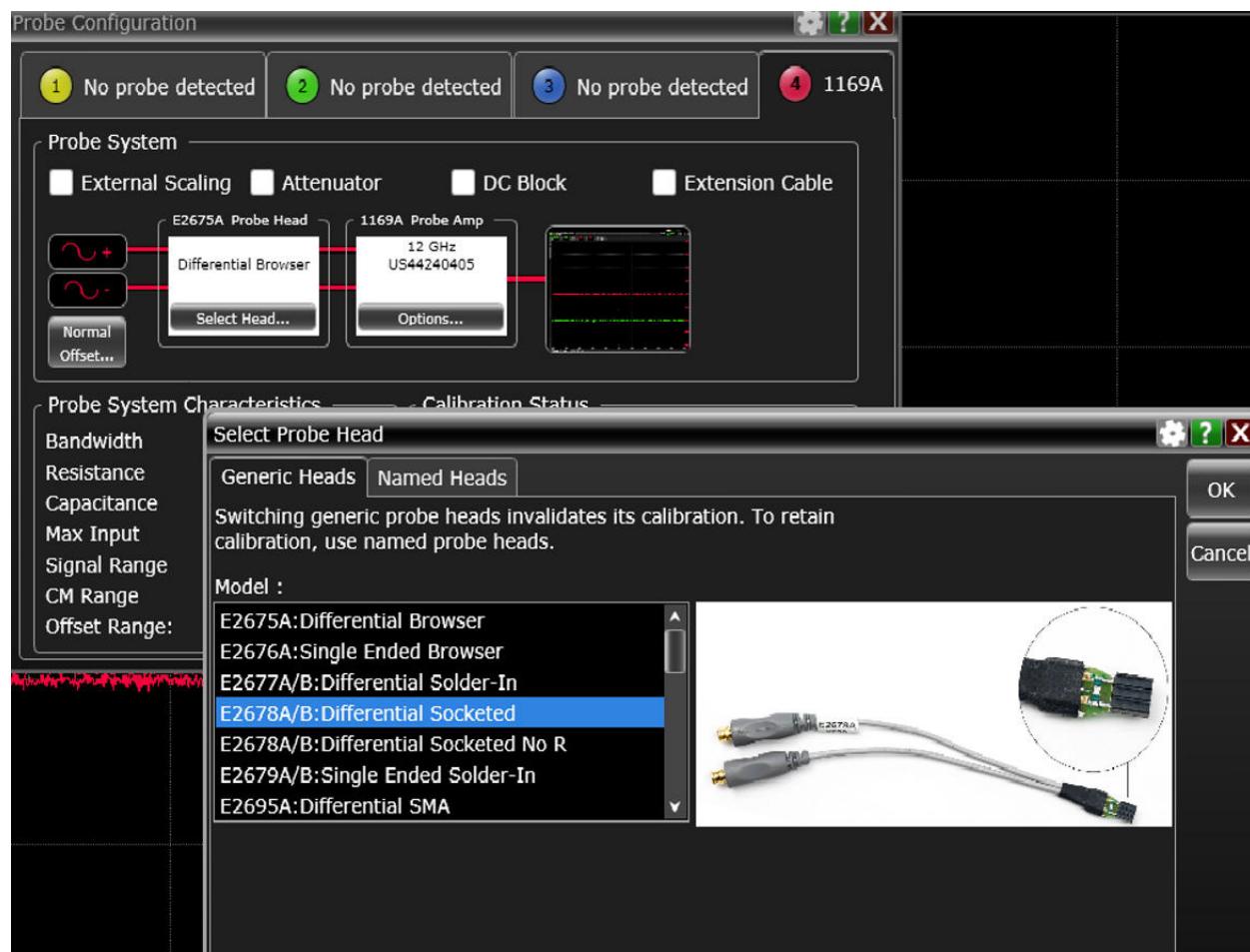

## Selecting the Probe Head

Probes are generally detected automatically, but most probe heads are not. Therefore, you must set up probe heads manually most of the time. Before running the tests ensure that the probe head is selected correctly.

Perform the steps on the next page to manually configure the probe head.

- 1 Select the channel that is connected to the probe.

- 2 In the **Probe Configuration** dialog, click **Select Head**.

3 Select the correct probe head.

## 4 1000 Base-T Tests

|                                                 |    |

|-------------------------------------------------|----|

| Probing for Test Mode 1 and Test Mode 4 /       | 42 |

| Test Mode 1 /                                   | 52 |

| Test Mode 4 /                                   | 61 |

| MDI Common Mode Output Voltage /                | 63 |

| Jitter Tests with TX_TCLK, DUT in MASTER Mode / | 67 |

| Jitter Tests with TX_TCLK, DUT in SLAVE Mode /  | 75 |

| MDI Return Loss /                               | 94 |

This section provides the Methods of Implementation (MOIs) for 1000 Base-T tests using an Infiniium oscilloscope, Infiniimax probes, and the Ethernet Compliance Test Application.

## Probing for Test Mode 1 and Test Mode 4

### Without Disturbing Signal Probing for Test Mode 1 and Test Mode 4

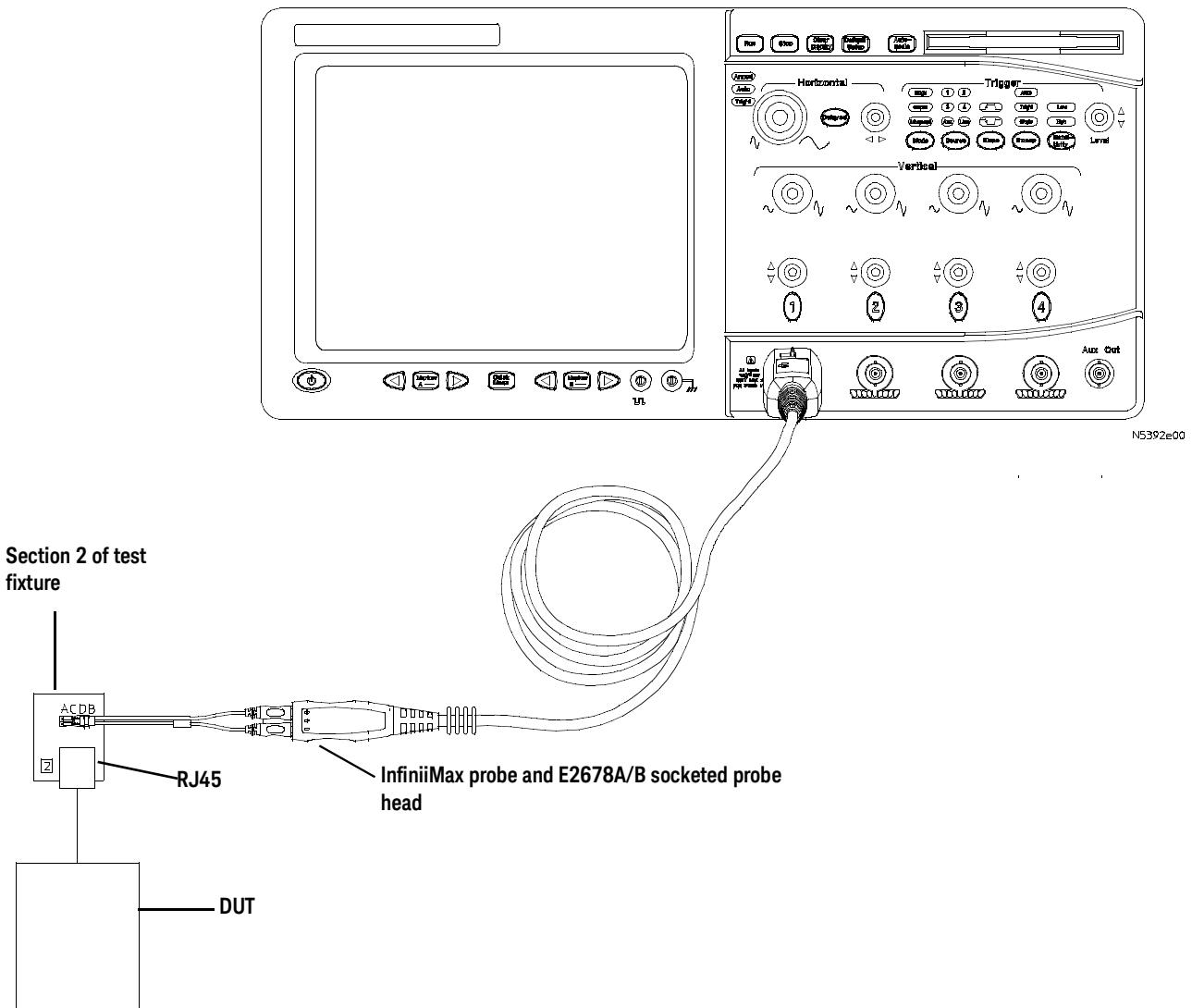

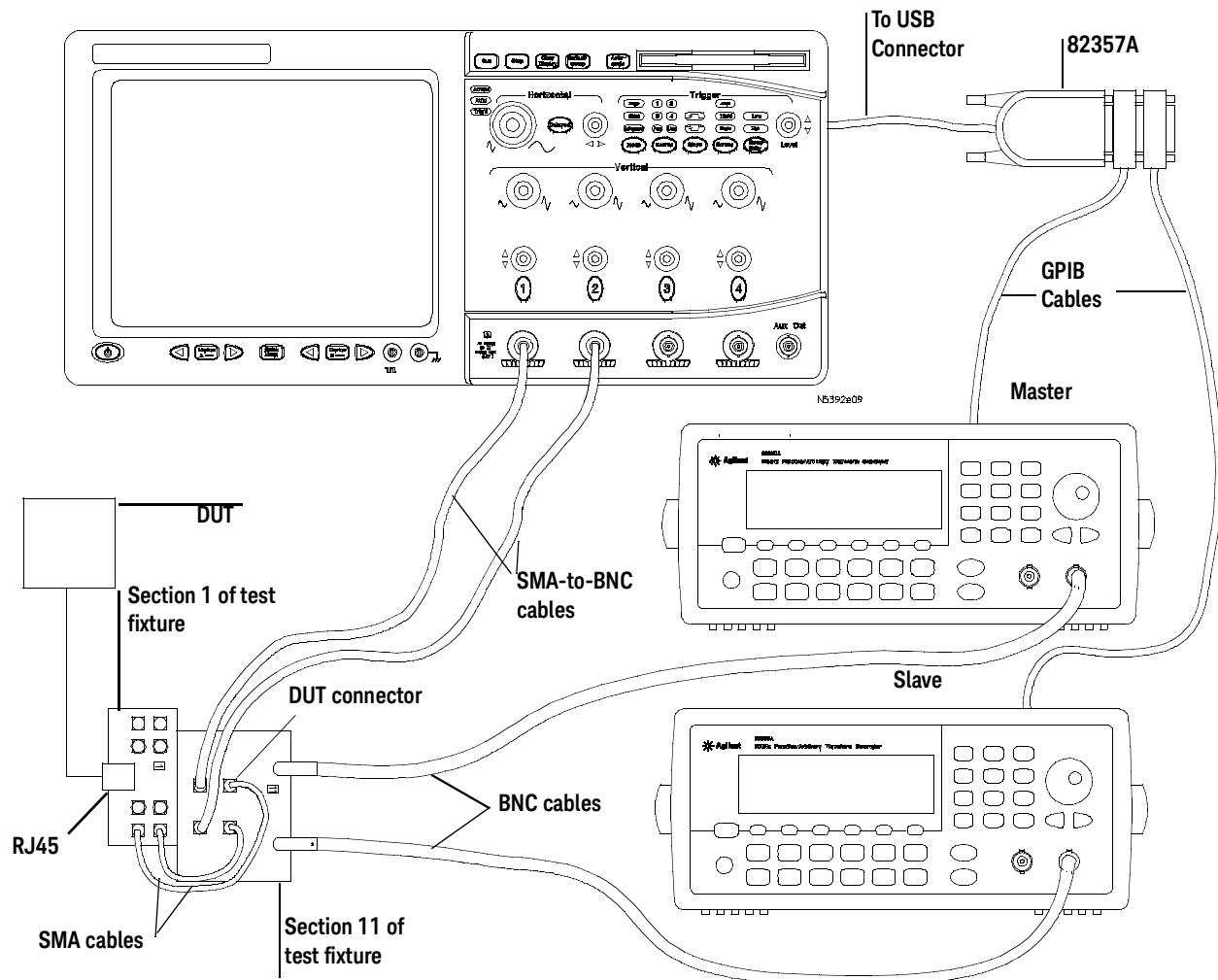

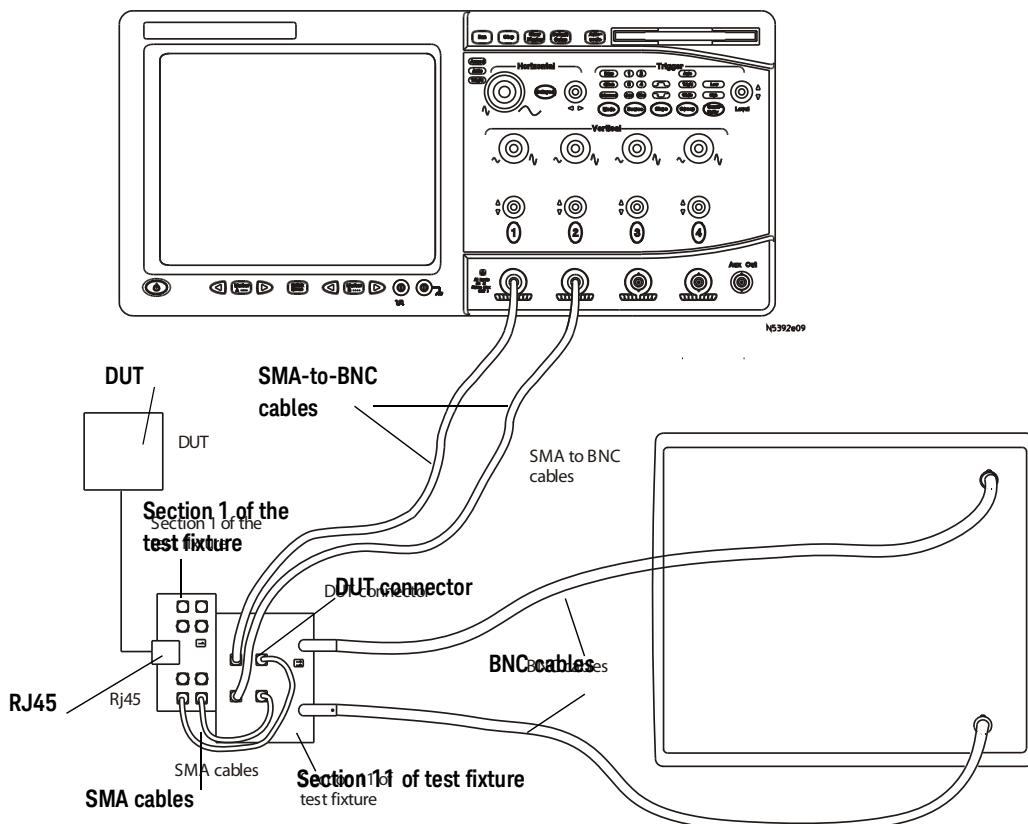

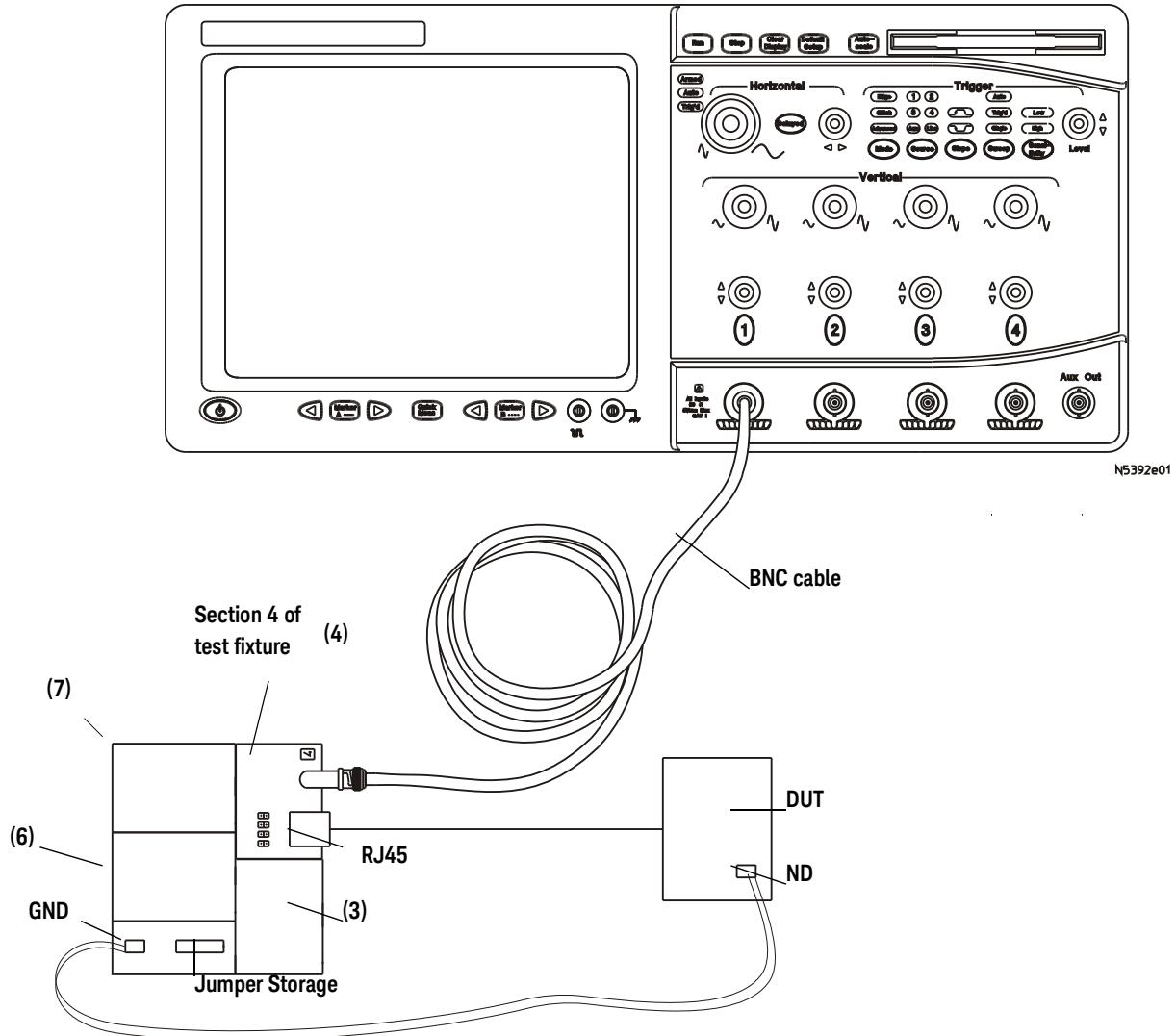

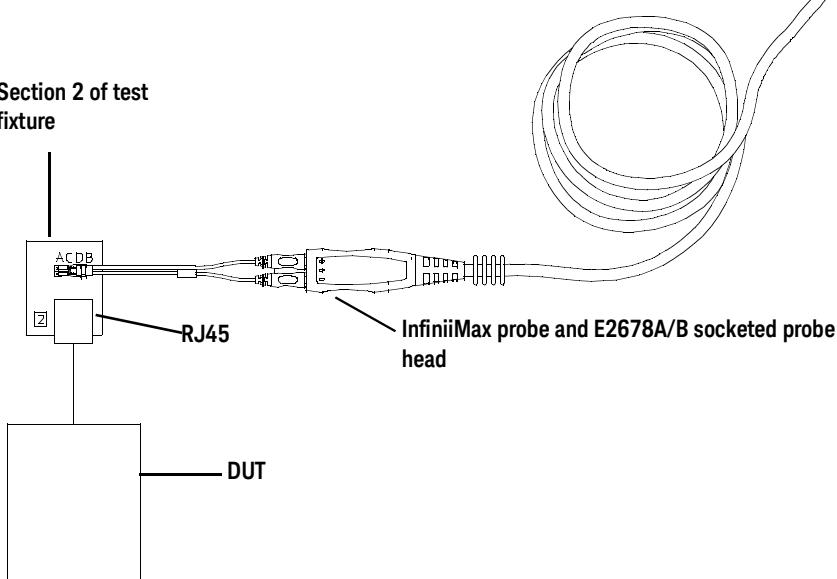

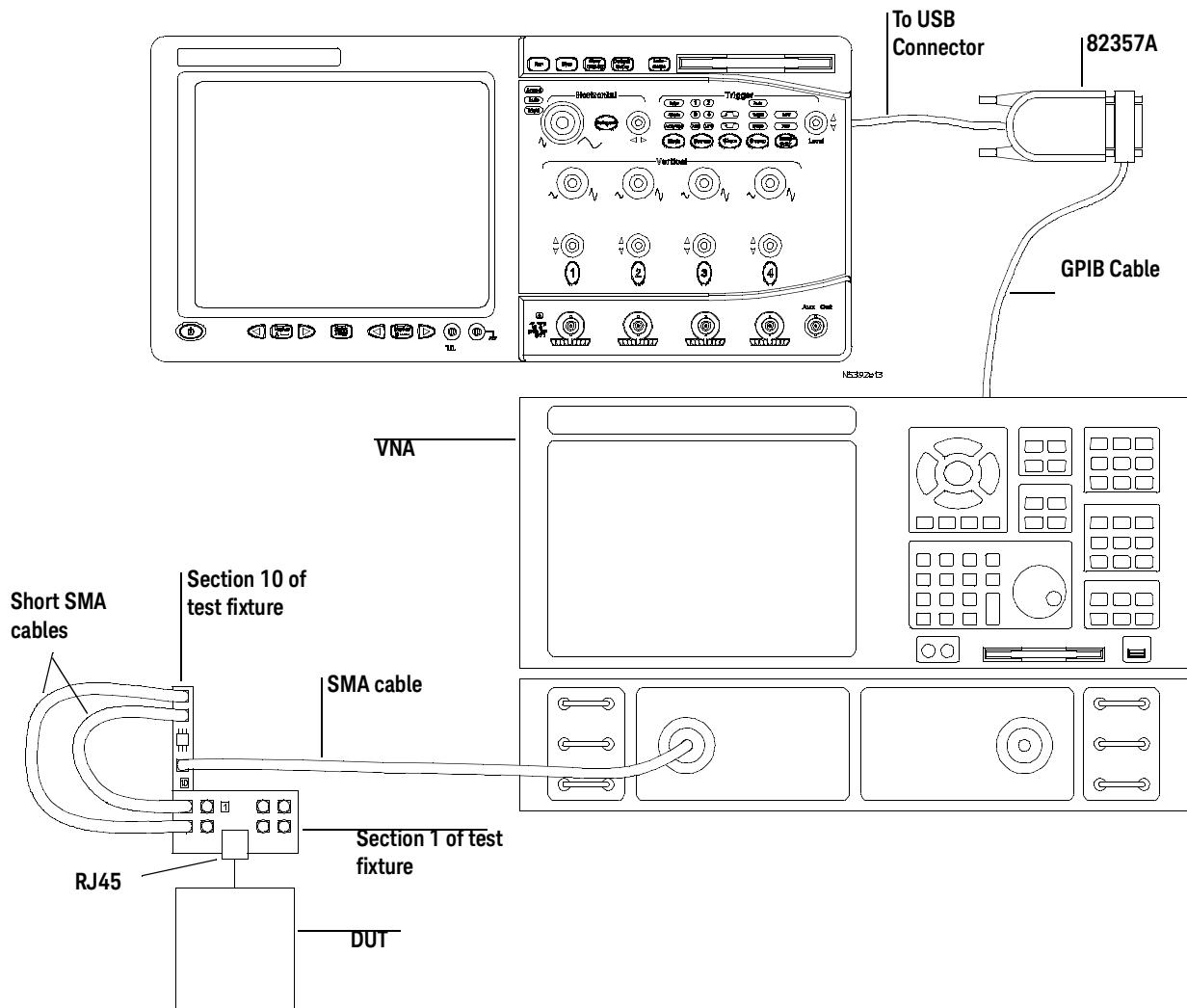

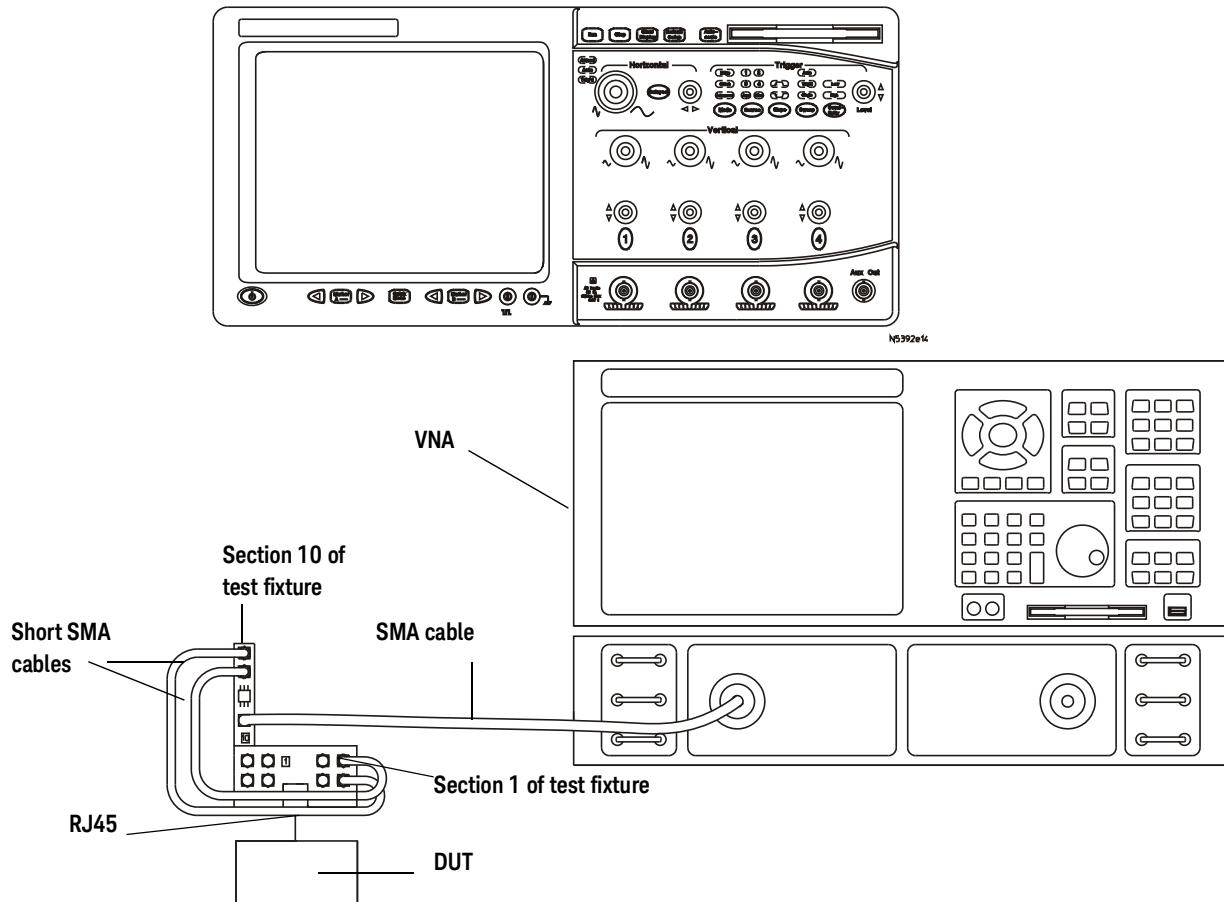

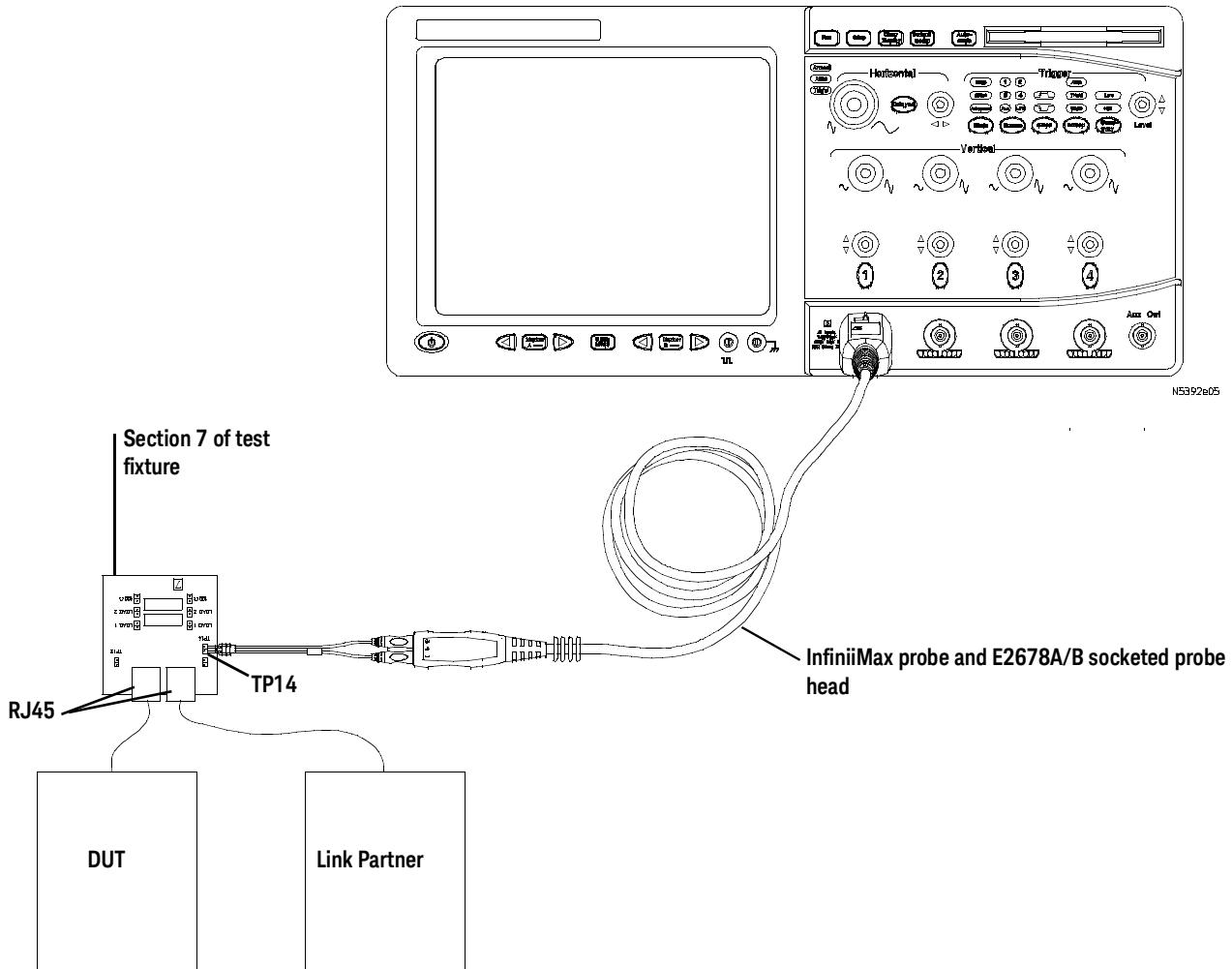

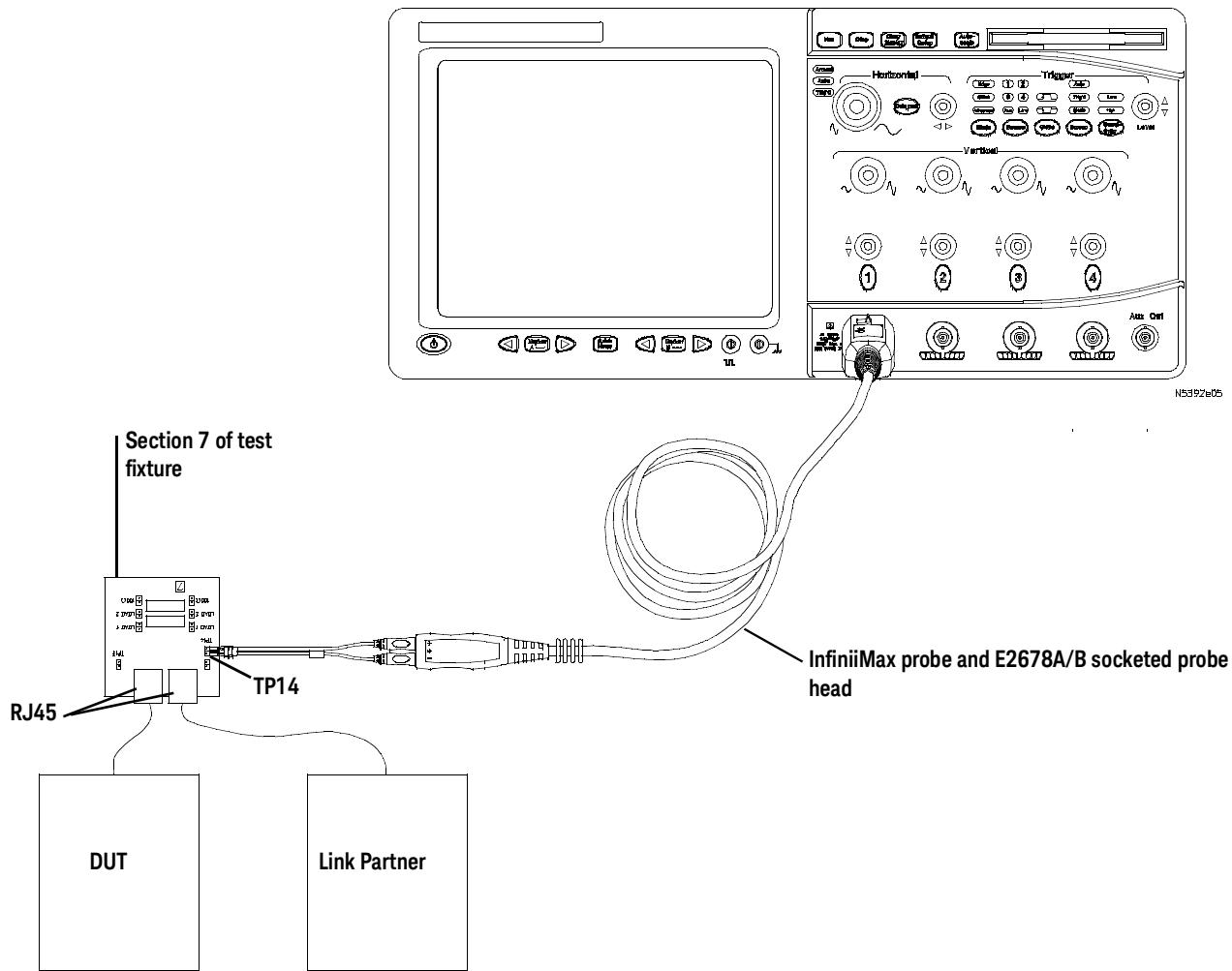

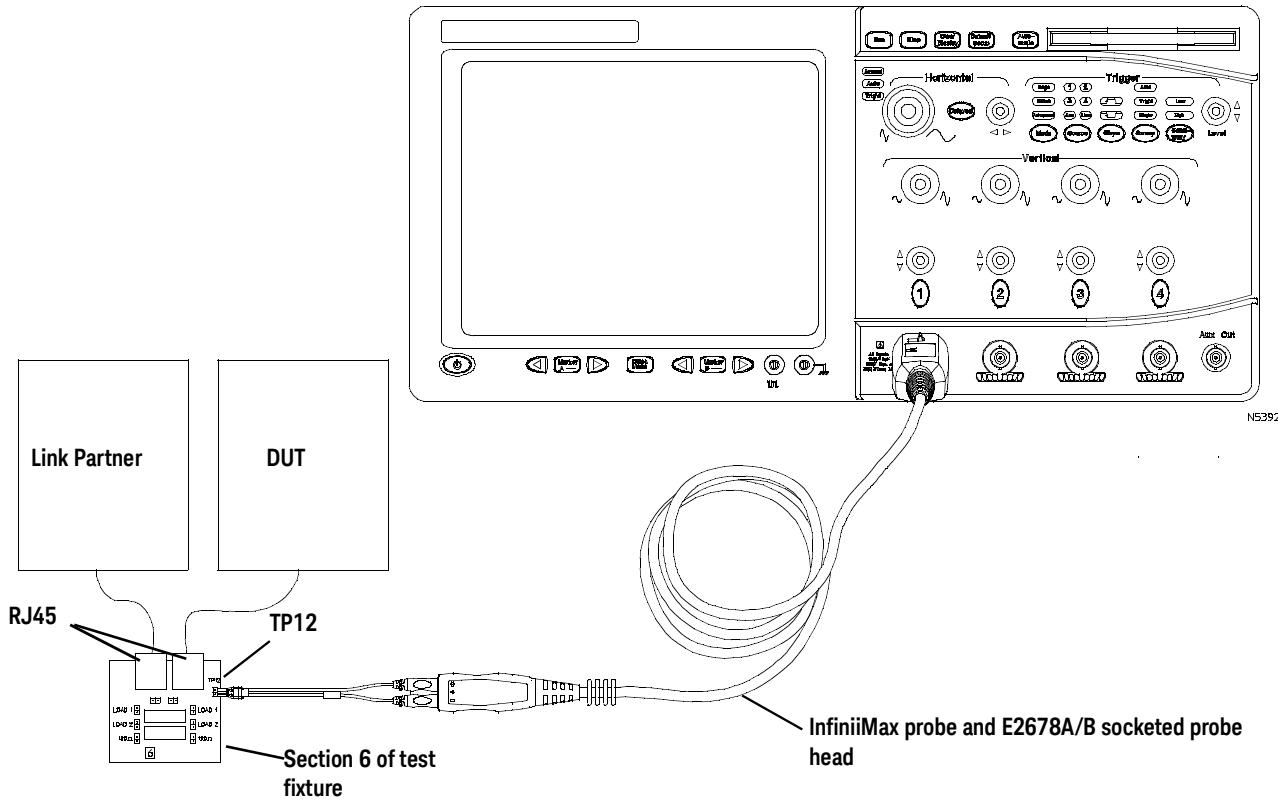

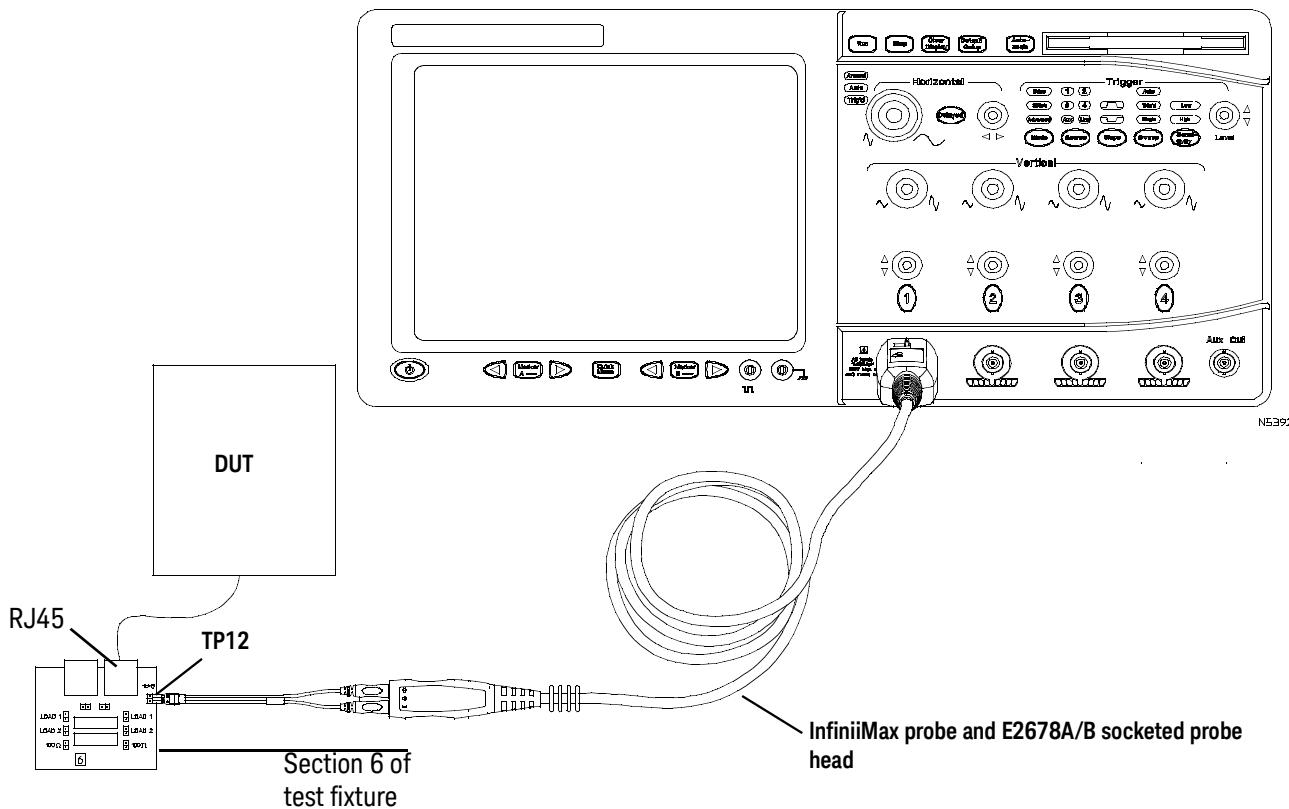

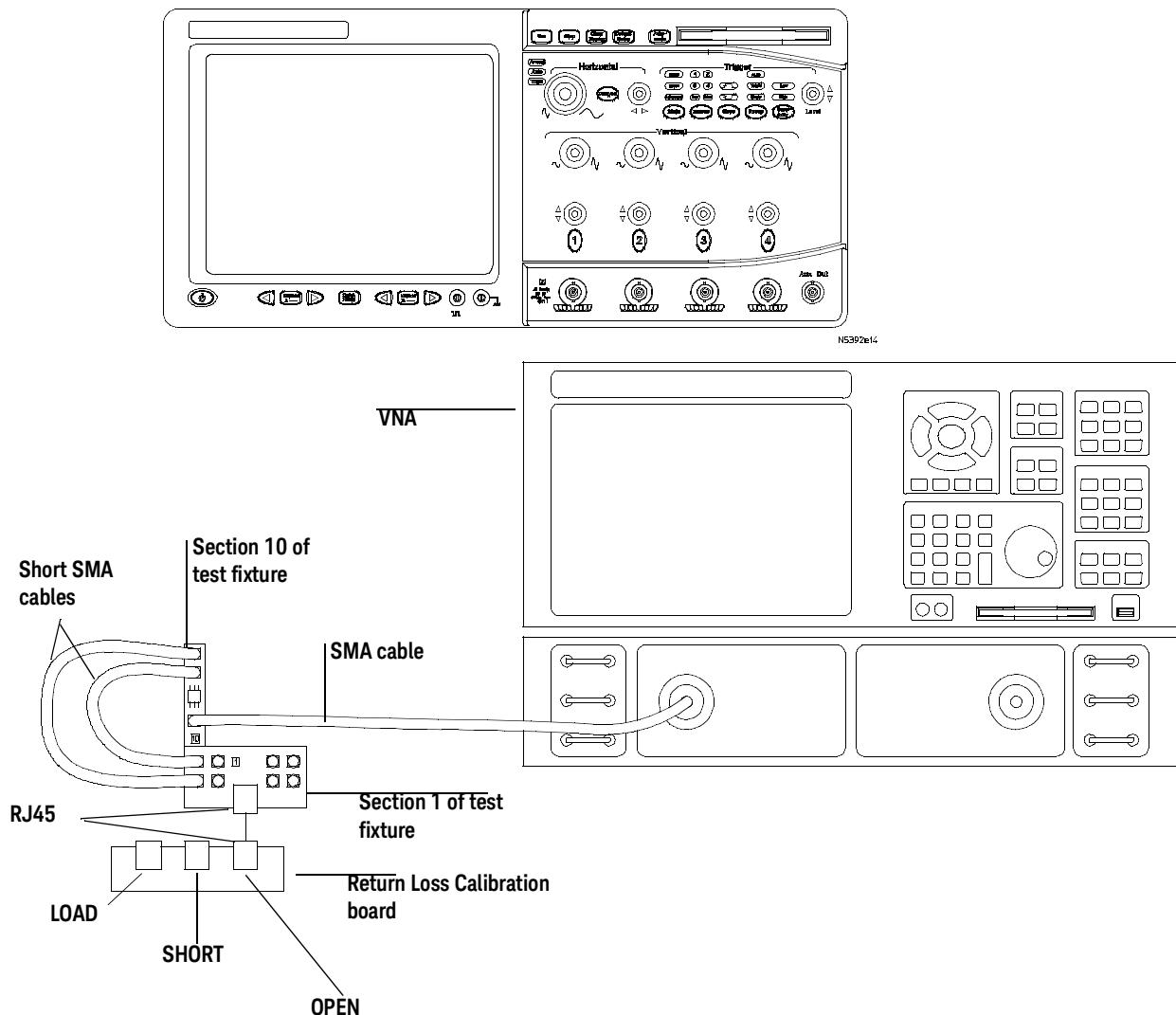

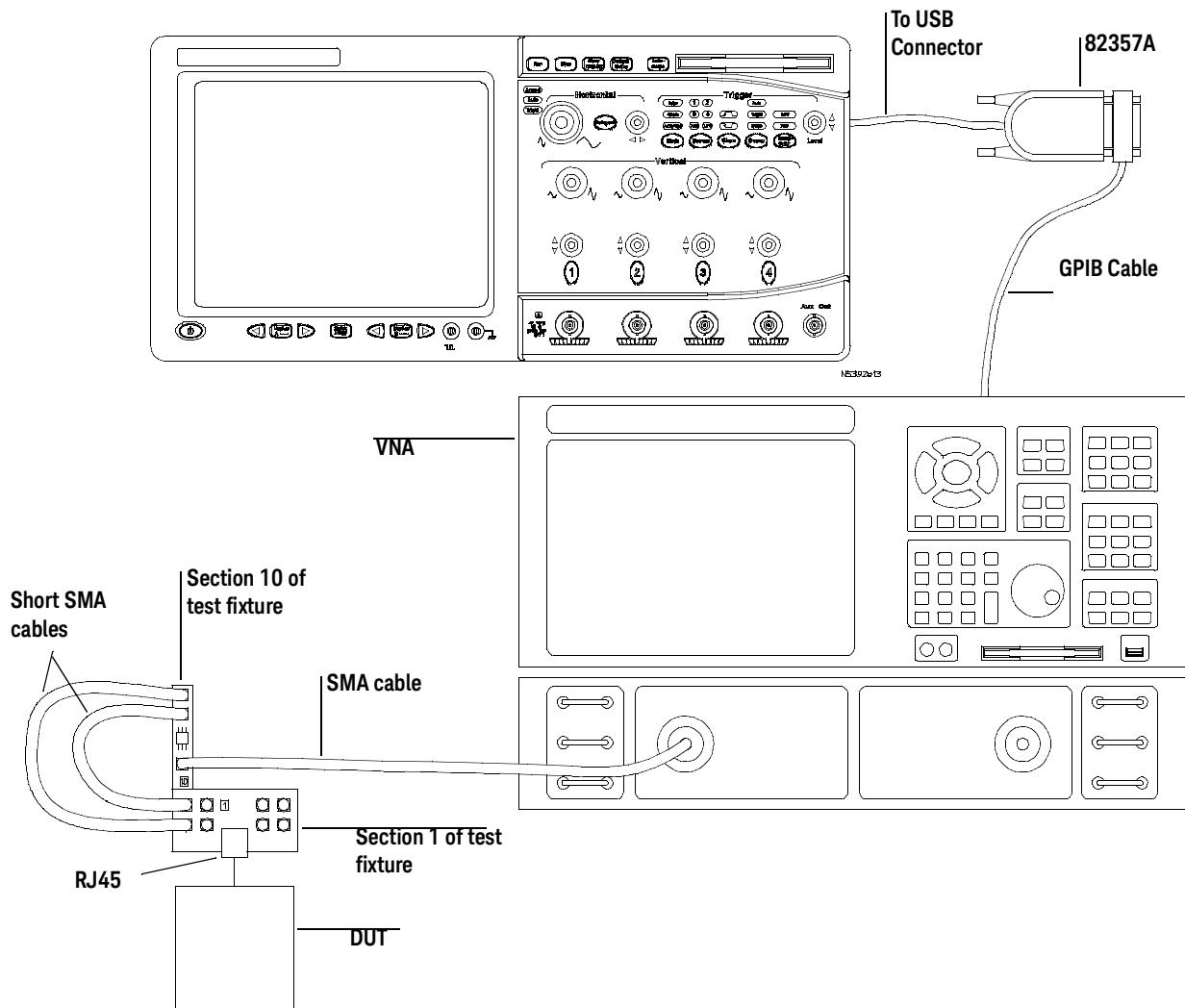

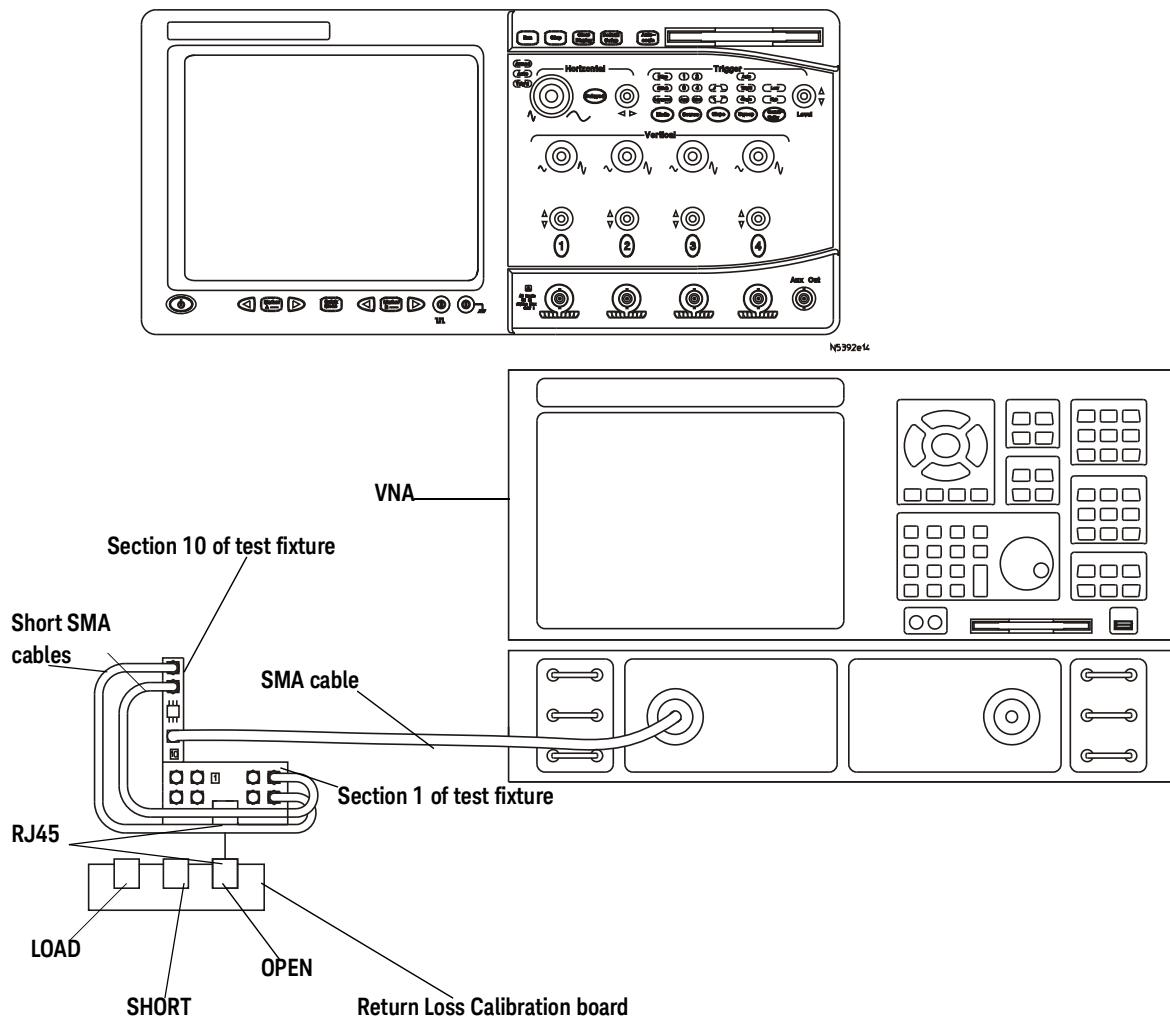

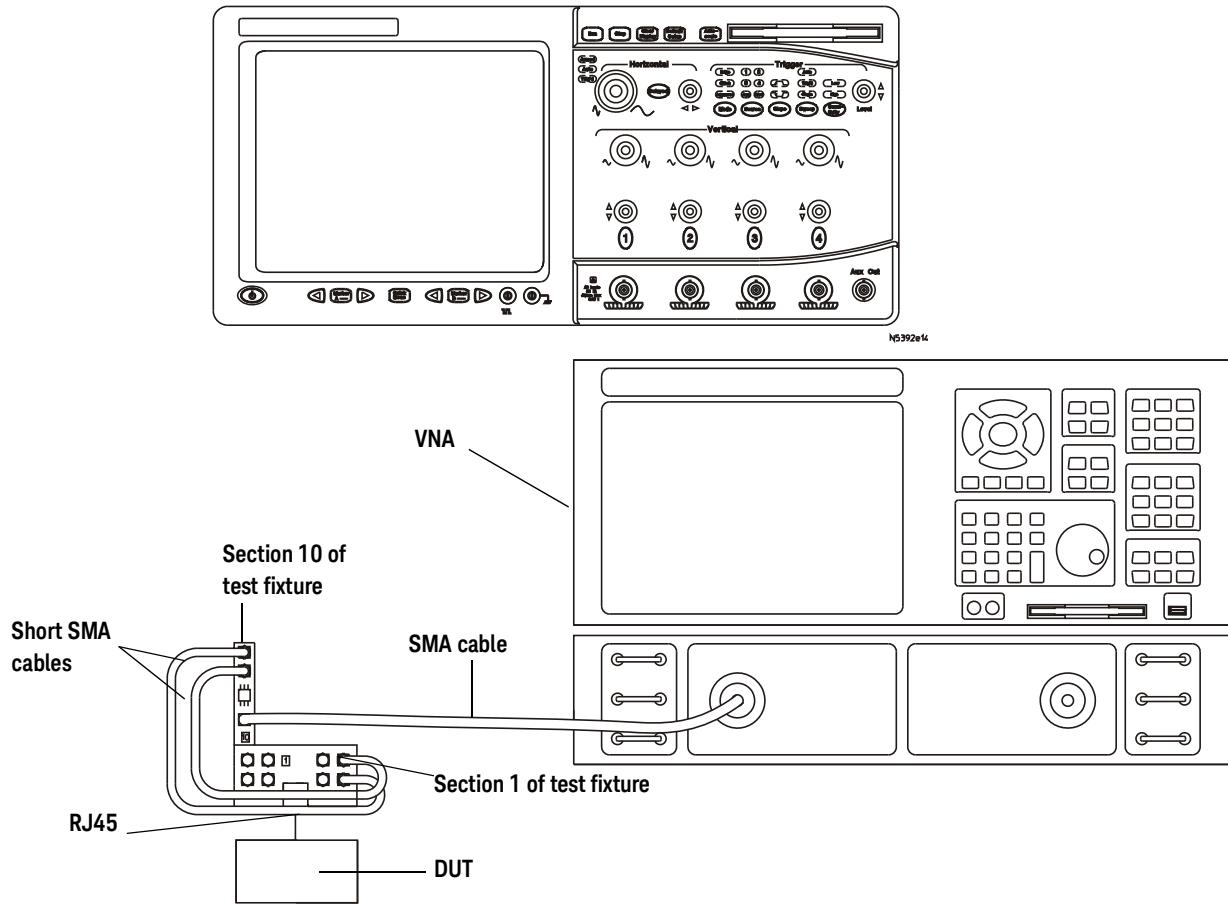

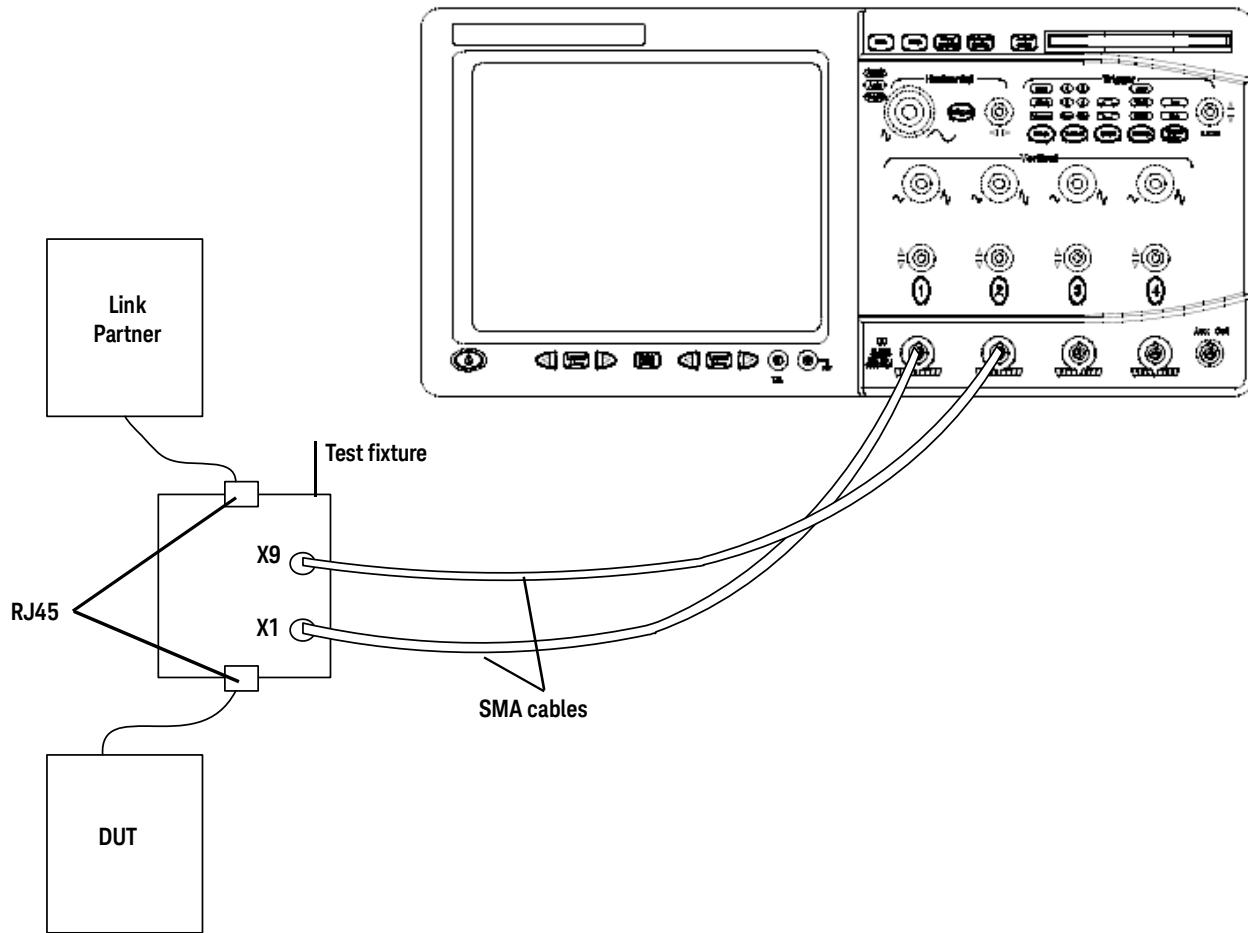

When performing 1000 Base-T Mode 1 tests, the Ethernet Compliance Test Application will prompt you to make the proper connections (also shown in [Figure 14](#)).

Figure 14 Probing for 1000 Base-T Test Mode 1 Tests

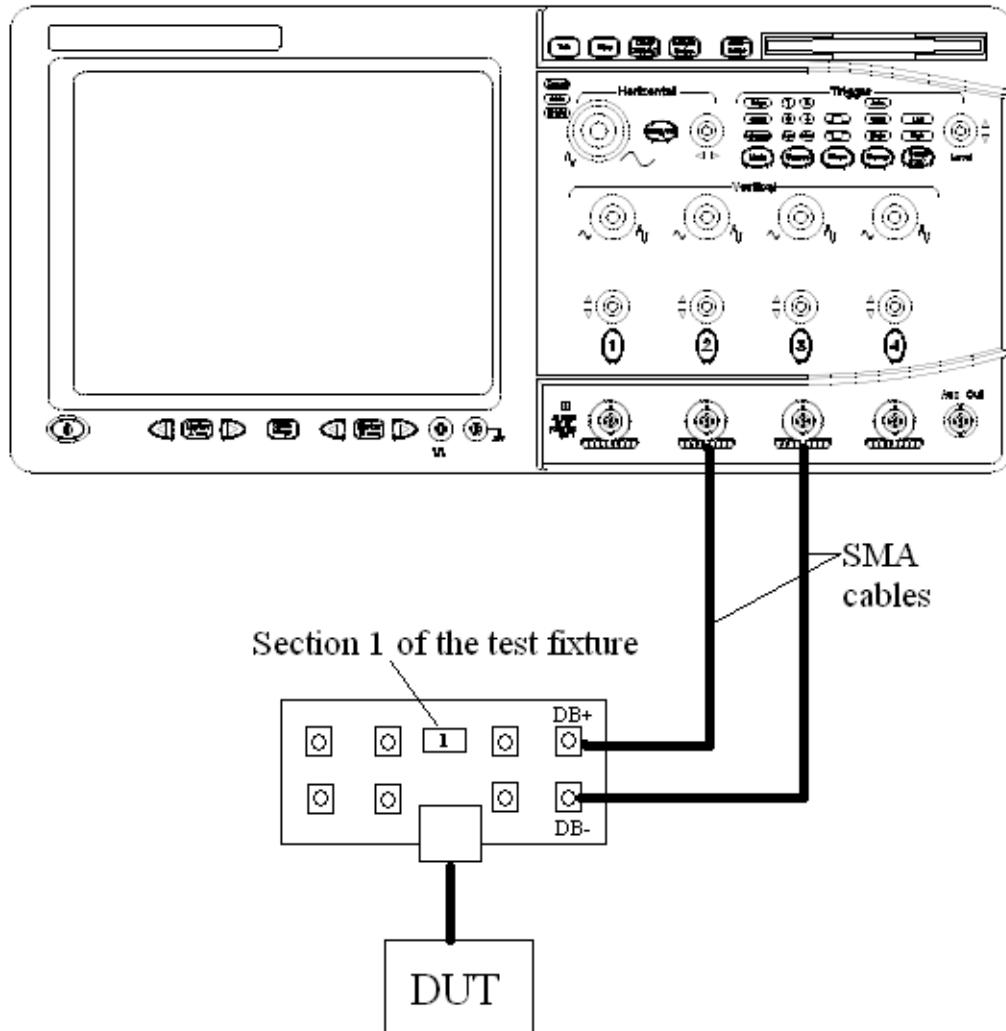

- 1 Connect the DUT to the RJ45 connector on section 1 of the Ethernet test fixture using a short straight-through UTP cable.

- 2 Connect an InfiniiMax probe with the E2678A/B socketed probe head to the test point for the pair you are testing (A, B, C, or D), and to the oscilloscope channel which is selected as the "DUT Data" channel in the user interface's "Configure" tab.

- 3 Ensure correct polarity of the probe head.

- 4 Ensure that the DUT is transmitting the appropriate “Test Mode 1” signal as indicated in the user interface.

You can use any oscilloscope channel for the DUT Data probe connection. You identify the channel used for DUT Data in the “Configure” tab of the Ethernet Compliance Test Application. (The channel shown in [Figure 14](#) is just an example.)

For more information on the InfiniiMax probe amplifiers and differential probe heads, see [Appendix 10, “InfiniiMax Probing,”](#) starting on page 227.

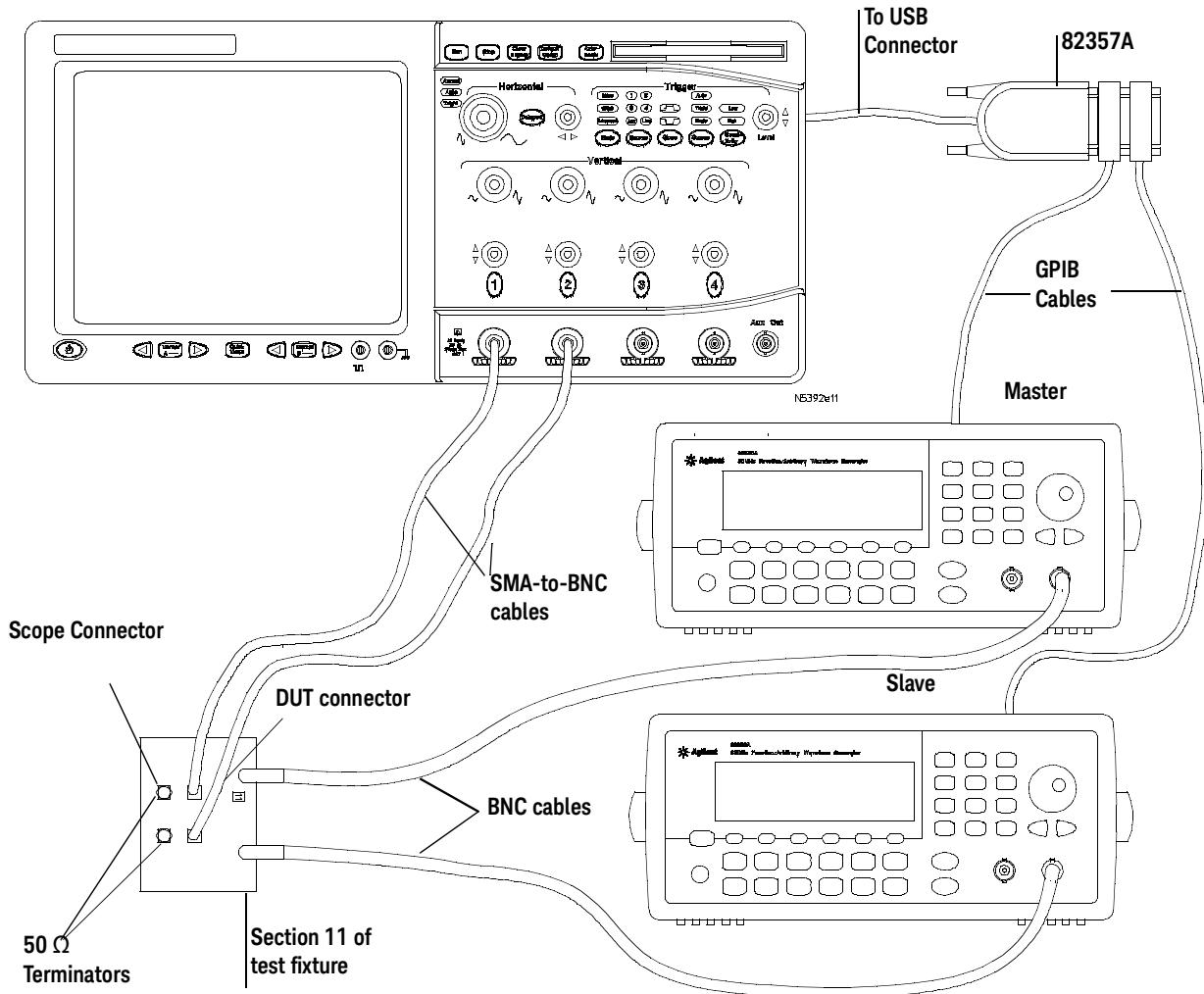

#### Calibration Setup for the 33612A Disturbing Signal Source

Before running disturbing signal tests, the 33612A generators must be calibrated. Connect the equipment as shown in [Figure 15](#).

Figure 15 Calibration Setup for the 33612A Disturbing Signal Source

### Performing the Calibration for the 33612A Disturbing Signal Source

- 1 Click the **Set Up** tab.

- 2 Click the **Calibrate Sources** button to start the calibration process.

- 3 If the system is not physically configured to perform the calibration, the application prompts you to change the physical configuration.

### Calibration Setup for the 81150A Disturbing Signal Source

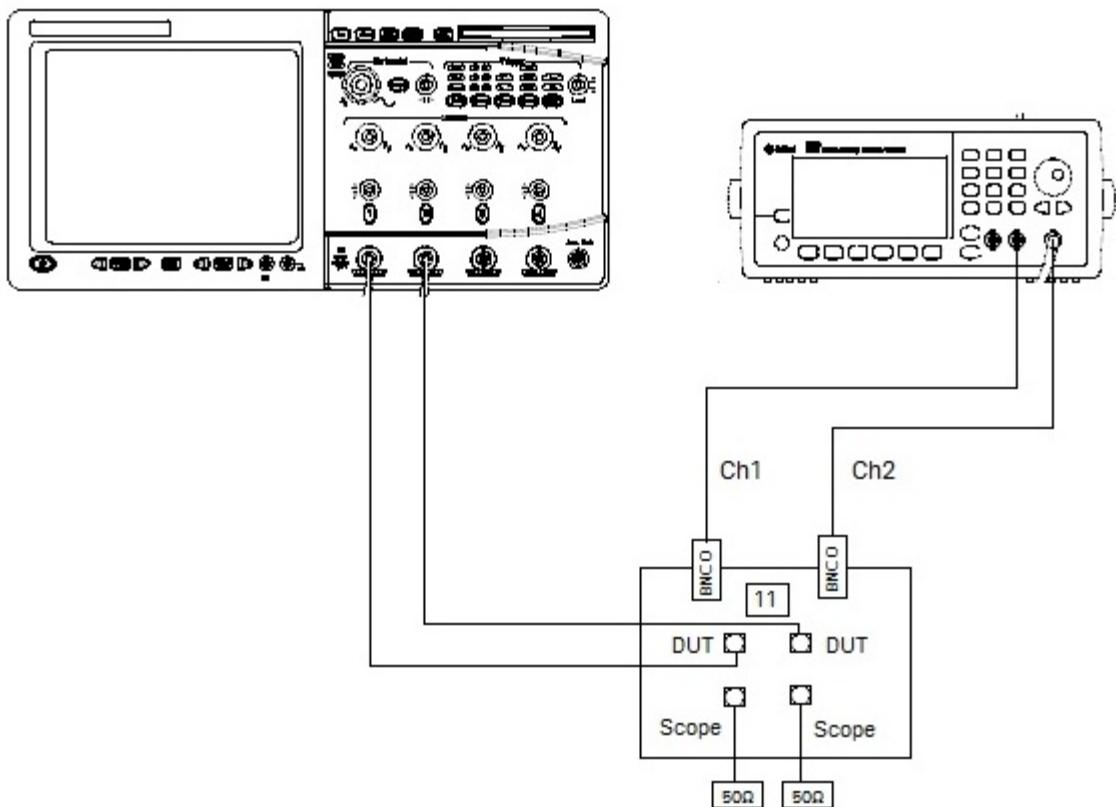

Before running disturbing signal tests, the 81150A generators must be calibrated. Connect the equipment as shown in [Figure 16](#).

Figure 16 Calibration Setup for the 81150A Disturbing Signal Source

### Performing the Calibration for the 81150A Disturbing Signal Source

- 1 Click the **Set Up** tab.

- 2 Click the **Calibrate Sources** button to start the calibration process.

- 3 If the system is not physically configured to perform the calibration, the application prompts you to change the physical configuration.

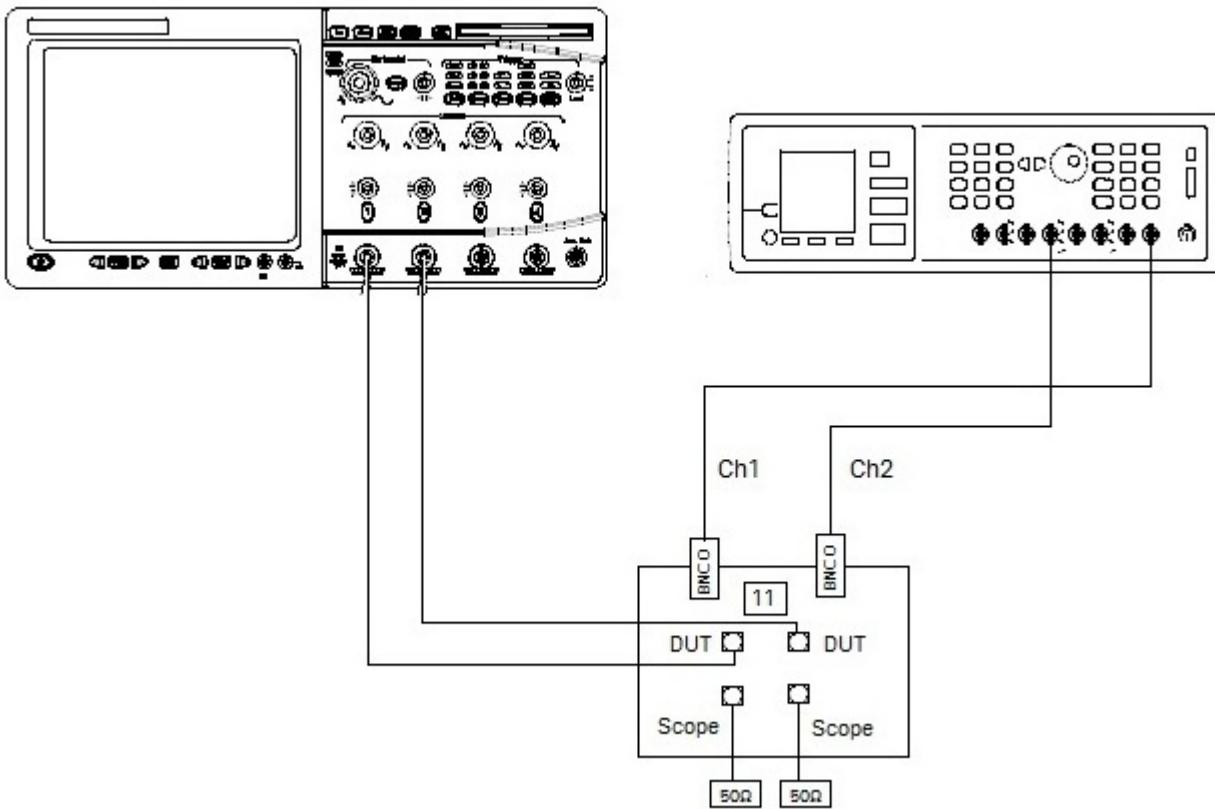

#### Calibration Setup for the 33250A Disturbing Signal Source

Before running disturbing signal tests, the 33250A generators need to be calibrated. Connect the equipment as shown in [Figure 17](#), “Calibration Setup for the 33250A Disturbing Signal Source,” on page 45 and [Figure 18](#), “Rear Panel Cable Connections for the 33250A Generators,” on page 46.

Figure 17 Calibration Setup for the 33250A Disturbing Signal Source

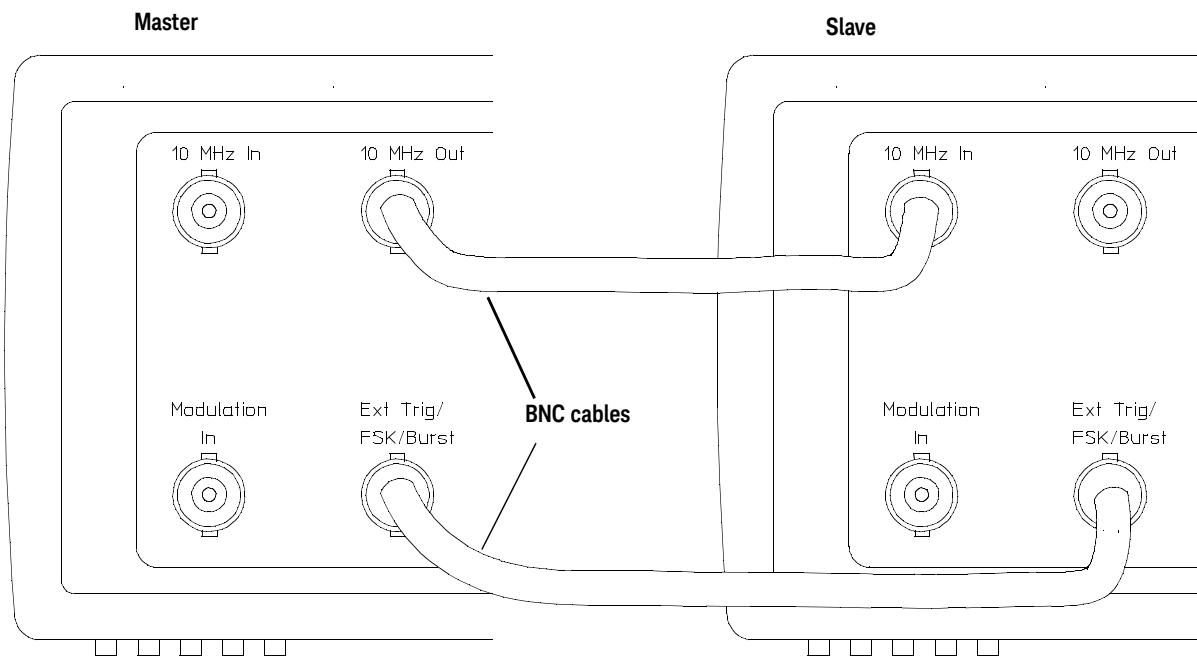

### 33250A Generator Setup

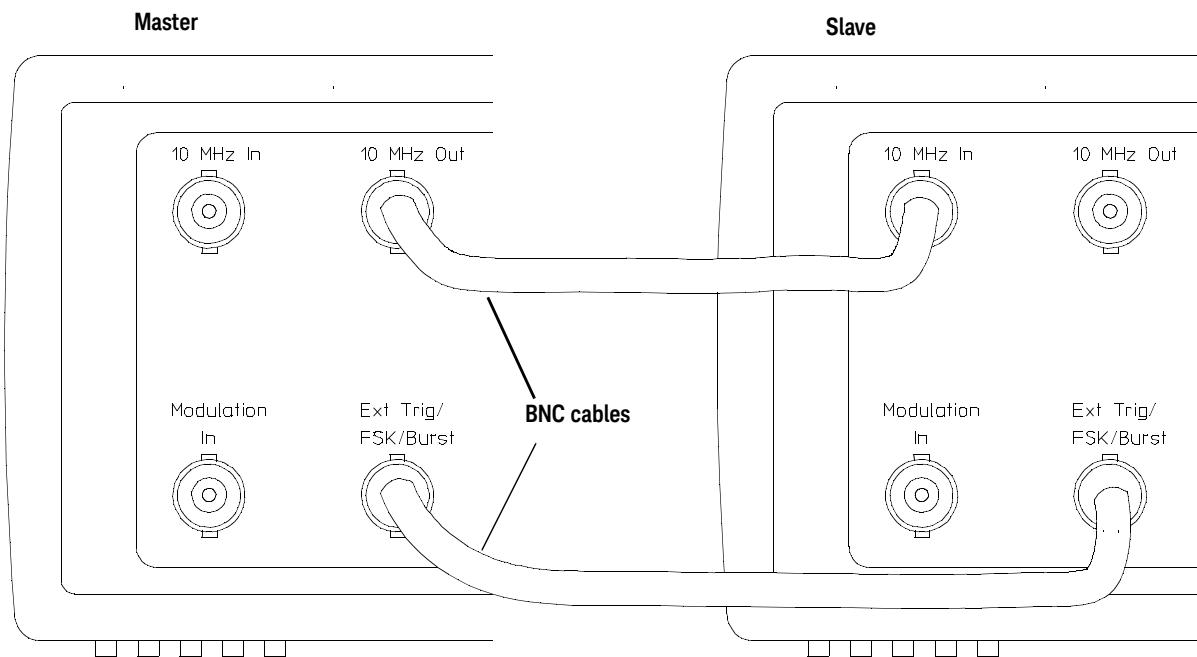

Figure 18 Rear Panel Cable Connections for the 33250A Generators

### Performing the Calibration

- 1 Click the **Set Up** tab.

- 2 Click the **Calibrate Sources** button to start the calibration process.

- 3 If the system is not physically configured to perform the calibration, the application prompts you to change the physical configuration.

Disturbing Signal Probing Setup for Test Mode 1 and Test Mode 4 Using the 33250A Signal Generators

Figure 19 Probing and Cable Connections for Test Mode 1 and Test Mode 4 Using the 33250A Signal Generators

### 33250A Generator Setup

Figure 20 Rear Panel Cable Connections for the 33250A Generators

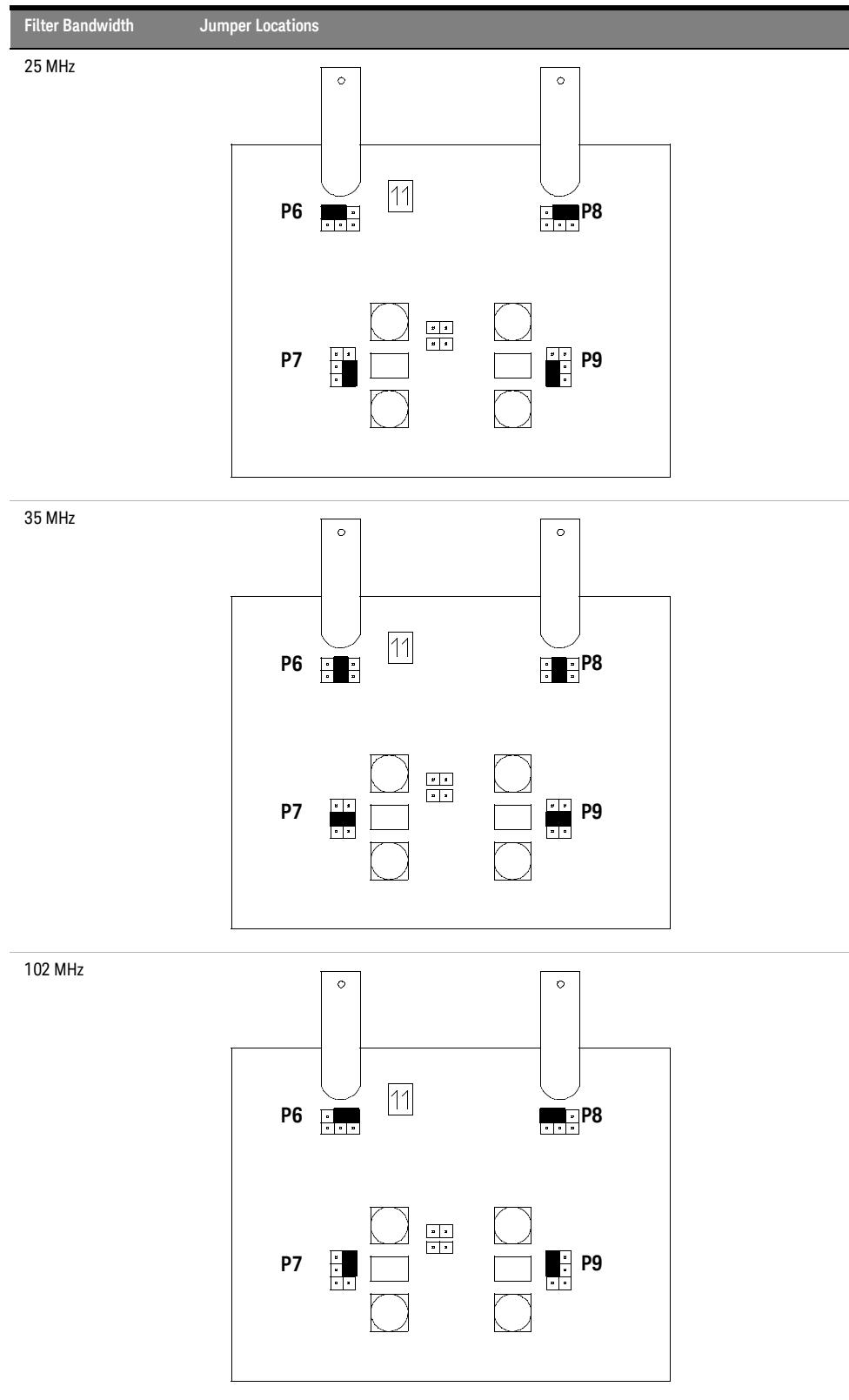

## Jumper Positions for Test Fixture Section 11

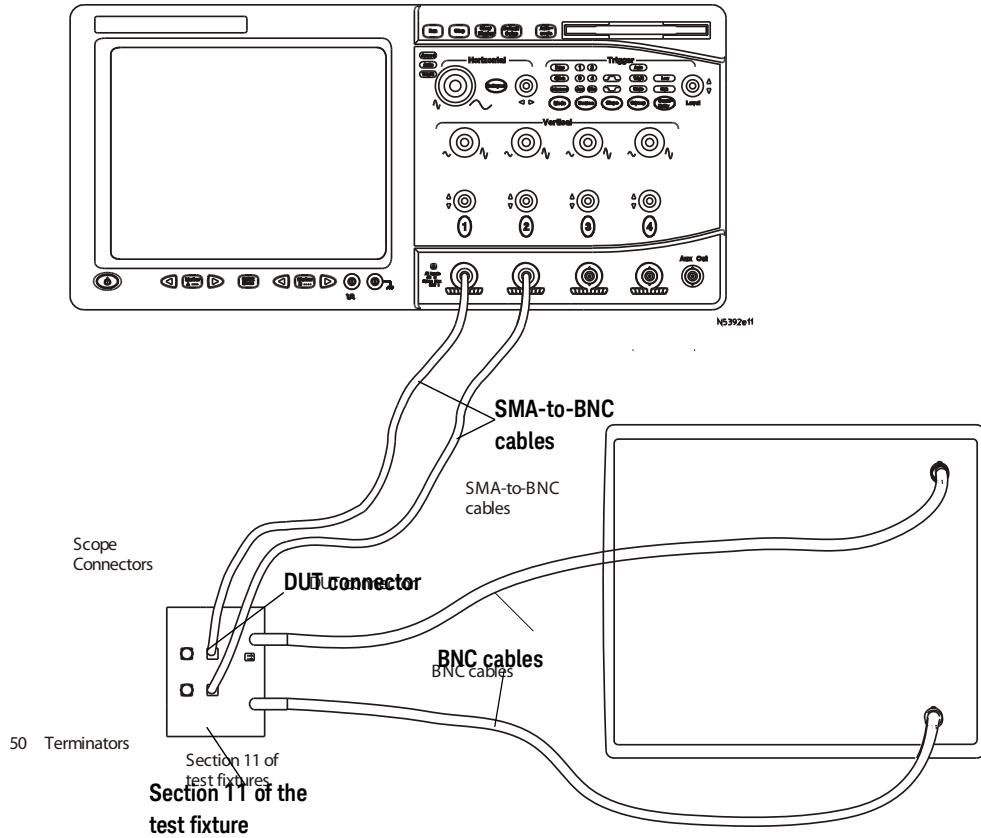

Before running disturbing signal tests, the disturbing signals need to be calibrated. Connect the equipment as shown in [Figure 21, “Calibration Setup the for Non-33250A Disturbing Signal Source,”](#) on page 50 and calibrate the source for Test Mode 1 and Test Mode 4 tests.

Figure 21 Calibration Setup the for Non-33250A Disturbing Signal Source

### Performing the Calibration

- 1 Select the appropriate filter configuration. Refer to [Table 14, “Disturbing Signal Source Settings,”](#) on page 51.

- 2 Set the source to output a differential signal with an amplitude of  $V_d$  and a frequency of  $F_d$ . Refer to [Table 14](#) on page 51.

- 3 Use autoscale feature of the oscilloscope to display the signal.

- 4 Use the oscilloscope to measure the amplitude and frequency, adjust the disturbing signal source, if needed, to generate an output signal with an amplitude of  $V_d$  and a frequency of  $F_d$ . Refer to [Table 14](#) on page 51.

- 5 Phase difference between the differential signal must be exactly 180 degrees. Adjust the phase if required.

- 6 Save the source configuration for later use.

**Table 14** Disturbing Signal Source Settings

| Test Mode   | Filter configuration                  | $F_d$      | $V_d$ |

|-------------|---------------------------------------|------------|-------|

| Test Mode 1 | 35 Mhz (see <a href="#">page 48</a> ) | 31.25 Mhz  | 1.4 V |

| Test Mode 4 | 25 Mhz (see <a href="#">page 48</a> ) | 20.833 Mhz | 2.7 V |

Note:  $V_d$  is denoted as the amplitude at each channel

Disturbing Signal Probing Setup for Test Mode 1 and Test Mode 4 Using Non-33250A Signal Generators

Figure 22 Probing and Cable Connections for Test Mode 1 and Test Mode 4 Using the Non-33250A Signal Generators

Recall the configuration that you have saved during the previous calibration steps, for each test mode. Run the test.

## Test Mode 1

### Peak Output Voltage Tests

These tests measure the output voltage of points A, B, C, and D of the Test Mode 1 signal at the MDI. This test uses section 2 of the Ethernet test fixture, and applies a 2 MHz high-pass filter in software after acquiring the data. These measurement are made for all 4 pairs (A, B, C and D)

The allowable ranges for these measurements are as follows:

**Table 15 Allowable Ranges for Peak Output Voltage Measurements**

| Point on Test Mode 1 Signal | Allowable Range                                                                       | Description                                                                                                                                                                                           |

|-----------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Point A                     | 0.67 V to 0.82 V                                                                      | Absolute value of Peak A is 0.75 V +/- 0.83 dB                                                                                                                                                        |

| Point B                     | Peak B  between 0.67 V and 0.82 V                                                     | Absolute value of Peak B is 0.75 V +/- 0.83 dB                                                                                                                                                        |

| Difference A,B              | $100 * [abs( Peak B  - 1/2 * ( Peak A  +  Peak B ))] / (1/2 * ( Peak A  +  Peak B ))$ | The absolute value of the peak of the waveforms at points A and B shall differ by less than 1% from the average of the absolute values of the peaks of the waveform at points A and B. <sup>[1]</sup> |

| Point C                     | <2% of $1/2 * ( Peak A  +  Peak B ) / 2$                                              | Absolute value of Peak C is within 2% of <sup>[1]</sup> the average amplitude of Peaks A and B <sup>[1]</sup>                                                                                         |

| Point D                     | <2% of $1/2 * ( Peak A  +  Peak B ) / 2$                                              | Absolute value of Peak D is within 2% of <sup>[1]</sup> the average amplitude of Peaks A and B <sup>[1]</sup>                                                                                         |

<sup>[1]</sup> NOTE: The specified tolerance for this measurement is extremely tight. If this test fails, consult the vertical gain accuracy of your oscilloscope before you draw any conclusions about conformance.

### Reference

[1] IEEE 802.3-2018, Subclause 40.6.1.2.1.

### Probing Setup

Refer to ["Without Disturbing Signal Probing for Test Mode 1 and Test Mode 4"](#) on page 42. This probing configuration is used for all 1000 Base-T Test Mode 1 Signal Tests.

### Device Configuration

- 1 Configure the DUT to output the Test Mode 1 signal.

Using your PHY vendor's provided method, set the DUT's GMII register bits 9.15, 9.14, 9.13 to the values 0, 0, 1 respectively.

- 2 Ensure that the DUT is transmitting the proper signal as indicated in the connection instructions provided in the user interface.

### Performing the Test

- 1 Ensure this test is checked to run in the "Select Tests" tab.

- 2 Run the test.

- 3 If the system is not physically configured to perform this test, the application will prompt you to change the physical configuration. When you have completed these instructions, click the “Connection Completed” button and resume the test run.

- 4 The test will:

- Verify that the correct test signal is present on the configured “DUT Data” channel

- Capture the waveform around Point A, B, C, or D depending on the Test

- Apply a 2 MHz high-pass filter to this waveform

- Measure the Peak voltage of the waveform at this point.

### NOTE

If you have selected “ALL” as the 1000 Base-T, Test Pair (in the “Configure” tab), all 4 pairs will be tested in sequence. You will be prompted to move the probe to the test point for each test pair in turn, and this measurement will be repeated at each of these test points. If you want to debug a particular pair, select the individual pair you wish to test. Note that for full compliance testing, the specification requires testing all 4 pairs. At the result screen, 4 trials tabs are shown at the bottom left of the screen. Each trial tab shows the result of each test pair. For example, Trial 1 contains Test Pair BI\_DA result, Trial 2 contains Test Pair BI\_DB result and so on.

### Algorithm Discussion

Reference [1] defines the peak differential output voltage and level accuracy specifications for a 1000 Base-T device at the physical medium attachment (PMA) sublayer to Media Dependent Interface (MDI). The Peak Voltage tests verify that the Peak Voltages of points A, B, C, and D of the Test Mode 1 signal at the MDI are within the specified range.

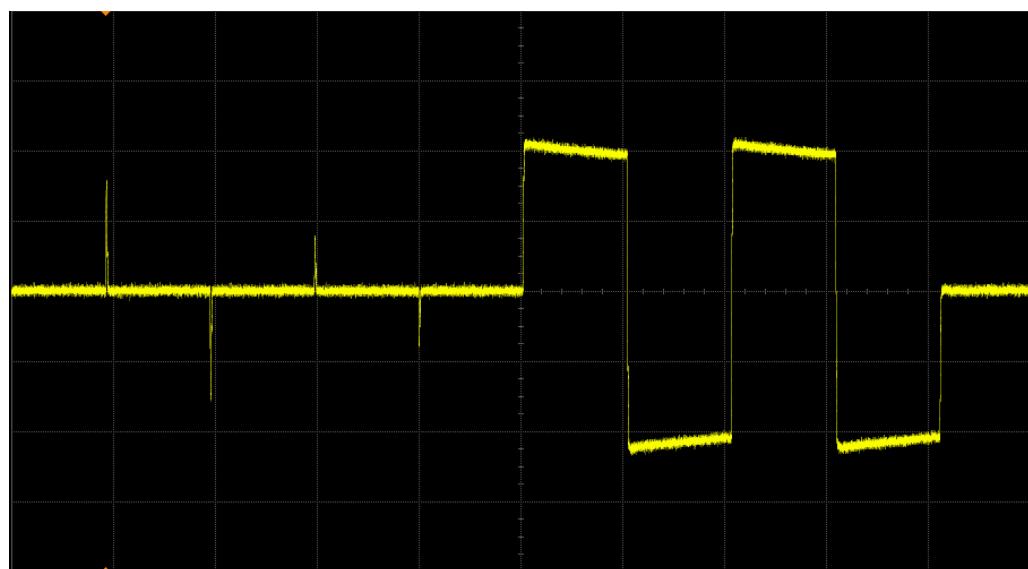

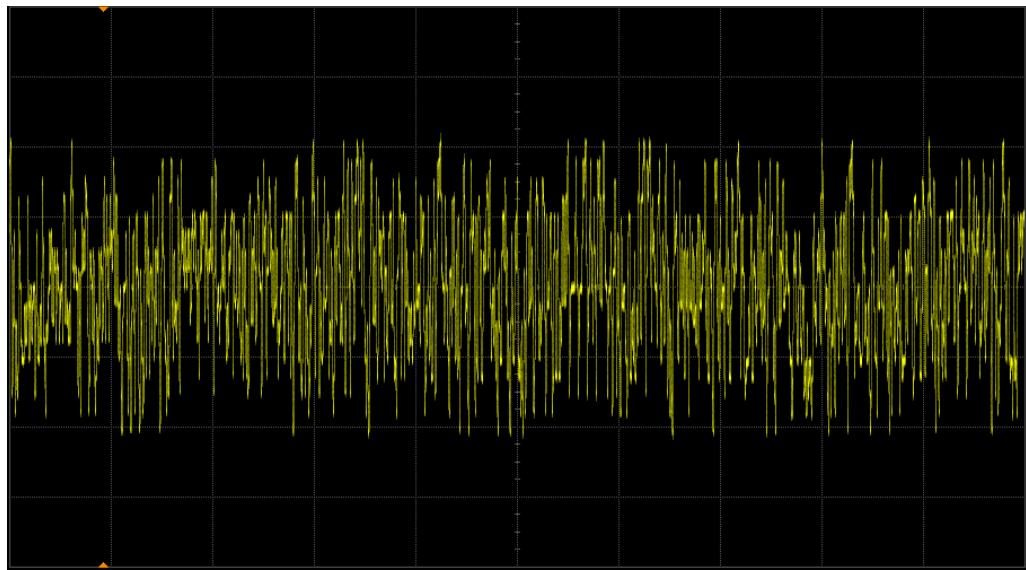

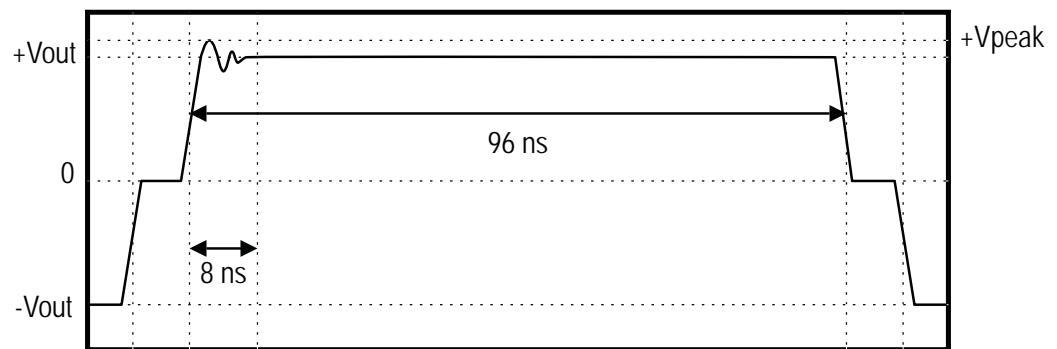

The oscilloscope triggers on the appropriate point (A, B, C, D) of the Test Mode 1 signal, as defined in [Figure 23](#). The tests verify that the absolute value of the peak voltage at A and B are in the range of 0.67 V to 0.82 V (0.75 V +/- 0.83 dB). Additionally, the ideal value for the absolute value of the peak voltage at points C and D is one half the average of the peak voltage at points A and B. We measure the absolute value of the peak voltage at points C and D and ensure that they deviate no more than 2% from this ideal voltage.

Figure 23 Example of Transmitter Test Mode 1 Waveform (1 Cycle)

## Trigger Averaging Notes

Reference <sup>[1]</sup> allows the use of trigger averaging to reduce measurement noise and increase measurement resolution; however, the specification does not provide any constraints on how much averaging may be used.

## NOTE

In general, averaging may also reduce the effects of real signal variations.

A user-configurable amount of averaging is used. One hundred twenty-eight (128) averages are used by default to reduce the effect of noise on the measurement. You may wish to decrease this number to increase the effects of random signal variations. You may also wish to increase this number to further reduce the effects of noise and increase measurement resolution.

## Performing Automated versus Manual Measurements for Peak Output Voltage

When you perform the Peak Output Voltage Measurements of points A, B, C, and D of the Test Mode 1 signal on a 1000 Base-T device, you will note the following differences when running Automated measurements (using the Keysight D9010ETHC Ethernet Compliance Test Application) versus performing Manual measurements (using the Keysight Infinium Application on the Oscilloscope):

- 1 Observation – When performing Automated measurements, the Oscilloscope does not display the averaging process on the waveform whereas during Manual measurements, you can visualize the averaging process running on the Oscilloscope screen.

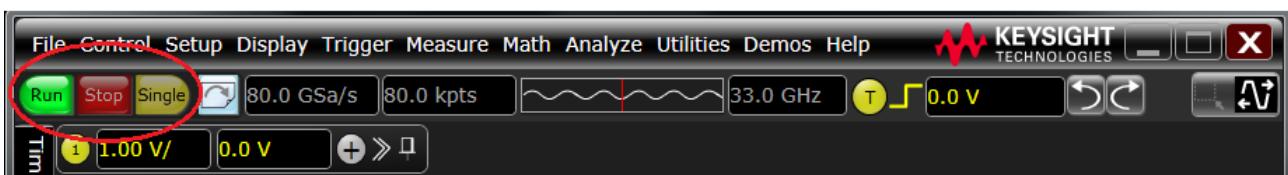

- During Automated measurements using the Keysight D9010ETHC Ethernet Compliance Test Application, the Test Application sends a :DIGITIZE command to the Oscilloscope, which invokes a special mode of data acquisition. This command (similar to repeatedly using the **SINGLE** button on the Oscilloscope as shown in Figure 24) initializes the selected channels or functions, then acquires them according to the current oscilloscope settings. When all waveforms are completely acquired, the oscilloscope is stopped. When averaging, it is necessary to know when the average count has been reached. The :SINGLE command (or pressing the **SINGLE** button) does not average. The Keysight D9010ETHC Ethernet Compliance Test Application triggers the :DIGITIZE command to acquire and perform the complete number of averages required for the measurements. This operation of averaging runs in the background and the Oscilloscope screen is not updated until all the averaged waveforms are acquired.

- During Manual measurements using the Keysight Infinium Application, when you click the **Run** button on the Oscilloscope, as shown in Figure 24, you can visualize the entire process of averaging being performed on the Oscilloscope screen.

Figure 24 Manual Measurement Control buttons on the Infinium Application

Refer to the Keysight Infinium Oscilloscopes Programmer's Guide for detailed information about the Oscilloscope commands mentioned above.

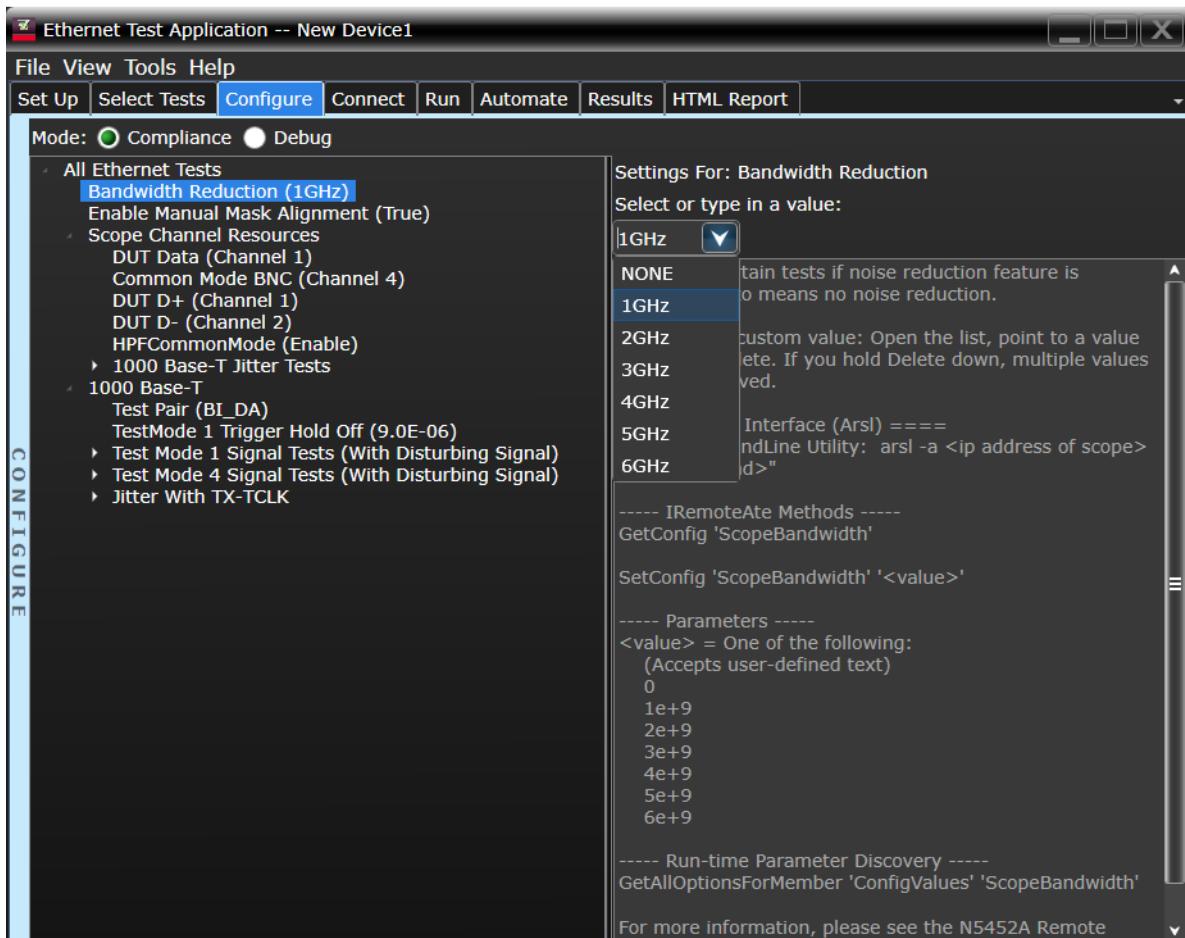

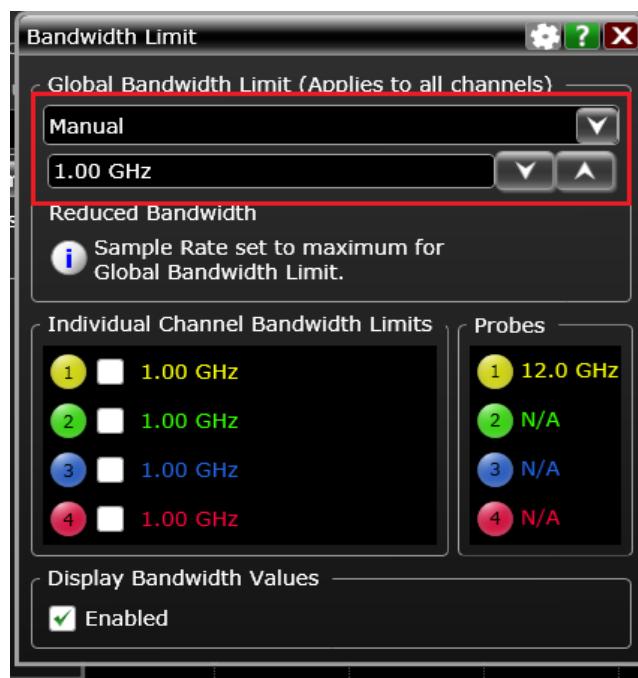

- 2 Applying Bandwidth limit for averaging – When performing Automated measurements, the Keysight D9010ETHC Ethernet Compliance Test Application applies a default Bandwidth Reduction Low-Pass Filter of 1GHz limit to reduce noise whereas during Manual measurements,

no default bandwidth limit is applied, which means that any noise in the signal is also factored in for the measurements performed manually on the Keysight Infinium Application. This may result in mismatch of resulting average values in the Automated and Manual methods.

To avoid any mismatch in averaging results between Automated versus Manual methods, you may do one of the following:

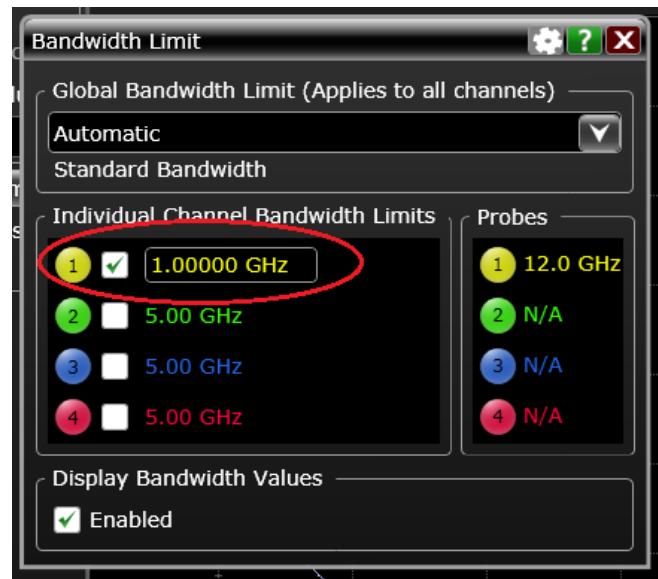

- Disable the **Bandwidth Reduction** option on the Ethernet Compliance Test Application to match with the Bandwidth Limit setting on the Keysight Infinium Application.

- i In the Ethernet Compliance Test Application, click the **Configure** tab.

- ii Select **Bandwidth Reduction**. Notice that by default, the limit is set to **1GHz**.

- iii From the drop-down options that appear on the right pane, select **NONE** to disable noise reduction.

Figure 25 Configuration option for Bandwidth Reduction

- Modify the Bandwidth Limit setting on the Keysight Infiniium Application to match the value configured for the Bandwidth Reduction option in the Ethernet Compliance Test Application (which is set to the default limit of 1 GHz or you may change the value as shown in [Figure 25](#) for performing automated measurements).

- i In the Infiniium Application, click **Setup > Bandwidth Limit...**

- ii Set the **Global Bandwidth Limit (Applies to all channels)** to **Manual**.

- iii Set the frequency value to match the value set for the **Bandwidth Reduction** option in the Compliance Test Application.

Figure 26 Setting Global Bandwidth Limit on Infiniium Application for noise reduction

**NOTE**

If you set the Bandwidth Limit only on a specific channel by setting the **Global Bandwidth Limit (Applies to all channels)** to **Automatic**, you may see a greater variation between the resulting peak voltage values in automated versus manual measurements.

## Templates Tests

These tests ensure that the normalized waveform of the Test Mode 1 signal at points A, B, C, D, F, and H as measured at the MDI after being filtered by a 2 MHz high-pass filter, lies within the time domain template defined in Figure 40-26 of Reference <sup>[1]</sup>. This test uses section 2 of the Ethernet test fixture, and applies a 2 MHz high-pass filter in software after acquiring the data. These measurement are made for all 4 pairs (A, B, C, and D).

### Reference

[1] IEEE 802.3-2018, Subclause 40.6.1.2.3.

### Probing Setup

Refer to “[Without Disturbing Signal Probing for Test Mode 1 and Test Mode 4](#)” on page 42. This probing configuration is used for all 1000 Base-T Test Mode 1 Signal Tests.

### Performing the Test

- 1 Ensure this test is checked to run in the “Select Tests” tab.

- 2 Run the test.

- 3 If the system is not physically configured to perform this test, the application will prompt you to change the physical configuration. When you have completed these instructions, click the “Connection Completed” button and resume the test run.

- 4 The test will:

- Verify that the correct test signal is present on the configured “DUT Data” channel.

- Capture the waveform around Point A, B, C, D, F, or H depending on the Test.

- Apply a 2 MHz high-pass filter to this waveform.

- Normalize the waveform as indicated in [Table 16](#). NOTE: No other vertical adjustments are allowed as per the specification.

- Shift the waveform in time for the best fit to the specified mask.

- Capture a number of waveforms (user configurable in the “Configure” tab), testing each waveform against the specified mask, recording failures when they occur.

### NOTE

If you have selected “ALL” as the 1000 Base-T, Test Pair (under the “Configure” tab), all 4 pairs will be tested in sequence. You will be prompted to move the probe to the test point for each test pair in turn, and this measurement will be repeated at each of these test points. If you want to debug a particular pair, select the individual pair you wish to test. For full compliance testing, the specification requires testing all 4 pairs. At the result screen, 4 trials tabs are shown at the bottom left of the screen. Each trial tab shows the result of each test pair. For example, Trial 1 contains Test Pair BI\_DA result, Trial 2 contains Test Pair BI\_DB result and so on.

### Algorithm Discussion

Reference <sup>[1]</sup> describes the differential output template specifications for a 1000 Base-T device at the physical medium attachment (PMA) sublayer to Media Dependent Interface (MDI). These tests ensure that the normalized waveform of the Test Mode 1 signal at points A, B, C, D, F, or H as measured at the MDI after being filtered by a 2 MHz high-pass Filter, lies within the time domain template defined in Figure 40-26 of Reference <sup>[1]</sup>.

The oscilloscope triggers on the appropriate point (A, B, C, D, F, H) of the Test Mode 1 signal, as defined in [Figure 23](#). The software applies a 2 MHz high-pass filter to this waveform. The waveform is then normalized as follows:

**Table 16** How Waveforms are Normalized

| Point of Test Mode 1 Signal | Normalized by dividing by                                       |

|-----------------------------|-----------------------------------------------------------------|