# **Keysight PXIe Chassis Family**

M9010A, M9018B, M9019A

**USER GUIDE**

## Notices

#### © Keysight Technologies, Inc. 2024

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies, Inc. as governed by United States and international copyright laws.

#### Manual Part Number M9019-90003

#### Edition

Fifth Edition, April 2024

#### Published by

Keysight Technologies, Inc. 900 S. Taft Ave. Loveland, CO 80537 USA

#### Trademarks

PICMG<sup>®</sup>, Compact PCI<sup>®</sup> are registered trademarks of the PCI Industrial Computer Manufacturers Group.

$\text{PCI-SIG}^{(\!\!R\!)},\,\text{PCI Express}^{(\!\!R\!)},\,\text{and PCIe}^{(\!\!R\!)}$  are registered trademarks of PCI-SIG.

LabVIEW is a registered trademark of National Instruments

#### Sales and Technical Support

To contact Keysight for sales and technical support, refer to the support links on the following Keysight websites:

www.keysight.com/find/M9010A

www.keysight.com/find/M9018B

www.keysight.com/find/M9019A

(product-specific information and support, software and documentation updates)

www.keysight.com/find/assist (worldwide contact information for repair and service)

#### Declaration of Conformity

Declarations of Conformity for this product and for other Keysight products may be downloaded from the Web. Go to http://keysight.com/go/conformity and click on "Declarations of Conformity." You can then search by product number to find the latest Declaration of Conformity.

#### Technology Licenses

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS." AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDI-TIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WAR-RANTIES, EITHER EXPRESS OR IMPLIED, WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MER-CHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR OF ANY INFOR-MATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEP-ARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT SHALL CONTROL.

Keysight Technologies does not warrant third-party system-level (combination of chassis, controllers, modules, etc.) performance, safety, or regulatory compliance unless specifically stated.

# DFARS/Restricted Rights Notices

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Keysight Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

## Safety Information

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings or operating instructions in the product manuals violates safety standards of design, manufacture, and intended use of the instrument. Keysight Technologies assumes no liability for the customer's failure to comply with these requirements.

#### General

Do not use this product in any manner not specified by the manufacturer. The protective features of this product must not be impaired if it is used in a manner specified in the operation instructions.

#### Before Applying Power

Verify that all safety precautions are taken. Make all connections to the unit before applying power. Note the external markings described under "Safety Symbols".

#### Ground the Instrument

Keysight chassis' are provided with a grounding-type power plug. The instrument chassis and cover must be connected to an electrical ground to minimize shock hazard. The ground pin must be firmly connected to an electrical ground (safety ground) terminal at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

PXIe Chassis are for indoor use only.

Mains supply voltage fluctuations must not exceed  $\pm 10\%$  of the nominal supply voltage.

Transient overvoltages typically present on the Mains supply (installation CAT II)

#### Do Not Operate in an Explosive Atmosphere

Do not operate in the presence of flammable gases or fumes.

#### Do Not Operate Near Flammable Liquids

Do not operate the module/chassis in the presence of flammable liquids or near containers of such liquids.

#### Cleaning

Clean the outside of the Keysight module/chassis with a soft, lint-free, slightly dampened cloth. Do not use detergent or chemical solvents.

Do Not Remove Instrument Cover

Only qualified, service-trained personnel who are aware of the hazards involved should remove instrument covers. Always disconnect the power cable and any external circuits before removing the instrument cover.

#### Keep away from live circuits

Operating personnel must not remove equipment covers or shields. Procedures involving the removal of covers and shields are for use by servicetrained personnel only. Under certain conditions, dangerous voltages may exist even with the equipment switched off. To avoid dangerous electrical shock, DO NOT perform procedures involving cover or shield removal unless you are qualified to do so.

# DO NOT operate damaged equipment

Whenever it is possible that the safety protection features built into this product have been impaired, either through physical damage, excessive moisture, or any other reason, REMOVE POWER and do not use the product until safe operation can be verified by servicetrained personnel. If necessary, return the product to a Keysight Technologies Sales and Service Office for service and repair to ensure the safety features are maintained.

# DO NOT block the primary disconnect

The primary disconnect device is the appliance connector/power cord when a chassis used by itself, but when installed into a rack or system the disconnect may be impaired and must be considered part of the installation.

#### Do Not Modify the Instrument

Do not install substitute parts or perform any unauthorized modification to the product. Return the product to a Keysight Sales and Service Office to ensure that safety features are maintained.

#### In Case of Damage

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

## CAUTION

Do NOT block vents and fan exhaust: To ensure adequate cooling and ventilation, leave a gap of at least 50mm (2") around vent holes on both sides of the chassis.

Do NOT operate with empty slots: To ensure proper cooling and avoid damaging equipment, fill each empty slot with an AXIe filler panel module.

Do NOT stack free-standing chassis: Stacked chassis should be rackmounted.

All modules are grounded through the chassis: During installation, tighten each module's retaining screws to secure the module to the chassis and to make the ground connection.

## WARNING

Operator is responsible to maintain safe operating conditions. To ensure safe operating conditions, modules should not be operated beyond the full temperature range specified in the Environmental and physical specification. Exceeding safe operating conditions can result in shorter lifespan. improper module performance and user safety issues. When the modules are in use and operation within the specified full temperature range is not maintained, module surface temperatures may exceed safe handling conditions which can cause discomfort or burns if touched. In the event of a module exceeding the full temperature range, always allow the module to cool before touching or removing modules from the chassis.

## Safety and Regulatory Symbols

#### CAUTION

A CAUTION denotes a hazard. It calls attention to an operating procedure or practice that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING denotes a hazard. It calls attention to an operating procedure or practice, that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

Products display the following symbols:

Refer to manual for additional safety information.

Earth Ground.

Chassis Ground.

Alternating Current (AC).

Direct Current (DC).

Standby Power. Unit is not completely disconnected from AC mains when power switch is in standby position

Indicates that antistatic precautions should be taken.

Operate the PXIe chassis in the horizontal orientation. Do NOT operate this chassis in the vertical orientation.

The CSA mark is a registered trademark of the Canadian Standards Association and indicates compliance to the standards laid out by them. Refer to the product Declaration of Conformity for details.

Notice for European Community: This product complies with the relevant European legal Directives: EMC Directive and Low Voltage Directive

The Regulatory Compliance Mark (RCM) mark is a registered trademark. This signifies compliance with the Australia EMC Framework regulations under the terms of the Radio Communication Act of 1992.

## ICES/NMB-001

ICES/NMB-001 indicates that this ISM device complies with the Canadian ICES-001.

Cet appareil ISM est conforme a la norme NMB-001 du Canada.

This symbol represents the time period during which no hazardous or toxic substance elements are expected to leak or deteriorate during normal use. Forty years is the expected useful life of this product.

South Korean Class A EMC Declaration. this equipment is Class A suitable for professional use and is for use in electromagnetic environments outside of the home.

A 급 기기 (업무용 방송통신기자재) 이 기기는 업무용 (A 급 ) 전자파적합기 기로서 판 매자 또는 사용자는 이 점을 주 의하시기 바라 며 , 가정외의 지역에서 사용하는 것을 목적으 로 합니다.

Waste Electrical and Electronic Equipment (WEEE) Directive 2002/96/EC

This product complies with the WEEE Directive (2002/96/EC) marking requirement. The affixed product label (see below) indicates that you must not discard this electrical/electronic product in domestic household waste.

Product Category: With reference to the equipment types in the WEEE directive Annex 1, this product is classified as a "Monitoring and Control instrumentation" product.

Do not dispose in domestic household waste.

To return unwanted products, contact your local Keysight office for more information.

# Contents

## 1 Introduction to the PXIe Chassis

| Key Chassis Features                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Front Panel Trigger Ports                                                                                                                                                       |

| Interactive Block Diagram                                                                                                                                                       |

| Chassis Maintenance and Inspection17                                                                                                                                            |

| Static-safe Handling Procedures                                                                                                                                                 |

| System or Cable Interface Modules                                                                                                                                               |

| Using the M9021A PCIe Cable Interface Module with the M9018A/B $\ldots$ . 20                                                                                                    |

| Installing PXI Modules in the Chassis                                                                                                                                           |

| Avoiding Bent Pins23Methods to avoid bent pins23Periodic chassis inspection24How to inspect your chassis backplane for bent pins or debris24What to do if you find a bent pin24 |

| Chassis Front Panel LEDs                                     | 25 |

|--------------------------------------------------------------|----|

| Related Documentation                                        | 27 |

| Using the M9018A Chassis with the PXIe Chassis Family Driver | 28 |

| Additional changes from the M9018A to the M9018B             | 29 |

| Driver Behavior                                              |    |

| Summary                                                      | 29 |

| Chassis Related Products and Accessories                     | 31 |

#### 2 PXIe Chassis Management Capabilities

| Summary of Chassis Management Capabilities                 | . 34 |

|------------------------------------------------------------|------|

| Using the Soft Front Panel to Configure Chassis Parameters | . 34 |

| The Chassis Alarm Architecture                             | . 35 |

## 3 Chassis and Host Controller Power Up or Down Sequence

| Methods of powering up the chassis | 38 |

|------------------------------------|----|

| Power Up Sequencing                | 39 |

| Power Down Sequencing              | 39 |

| Performing a System Power Cycle    | 40 |

| Performing a Chassis Hard Reset    | 41 |

#### 4 Chassis Alarm Architecture

| Power-on Default Alarm Thresholds                            | 44 |

|--------------------------------------------------------------|----|

| Events Which Re-establish the Power-on Default Thresholds    | 47 |

| Relationship Between Alarm Occurred and the Front Panel LEDs | 47 |

| Soft Front Panel Alarm Thresholds                            | 48 |

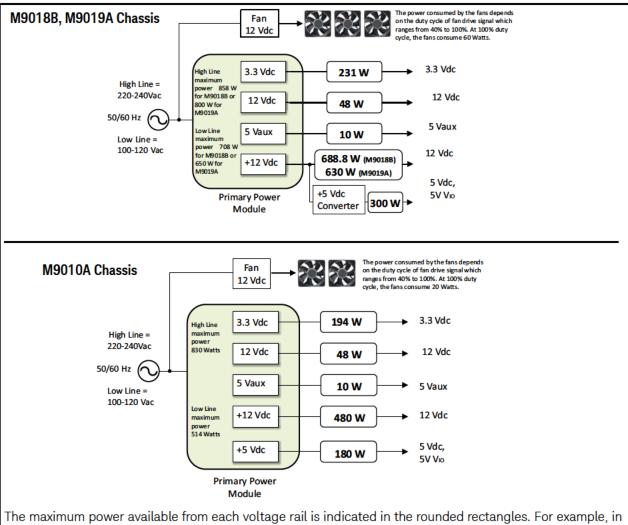

## 5 Power Supply Operation

| Power Supply Capacity5                           | 0  |

|--------------------------------------------------|----|

| Temperature Derating of the Primary Power Module | 50 |

| Power Calculator Spreadsheet                     | 50 |

| Over Temperature Protection                      | 52 |

| Over-current Protection5                         | 52 |

| Short Circuit Protection5                        | 53 |

| Internal Fuses                                   | 53 |

| Internal Fans                                    | 53 |

| Front Panel Power LED                            | 53 |

| Measuring the Main Voltage Rails Directly        | ;4 |

| Monitoring the Power Supply Rails                | ;4 |

| 6 Chassis Cooling and Rack Mounting              |    |

| Overview of chassis | cooling |  |  | . 59 |

|---------------------|---------|--|--|------|

|---------------------|---------|--|--|------|

| Monitoring the Chassis Temperature                    | 61 |

|-------------------------------------------------------|----|

| Monitoring Chassis Fan Speeds                         | 67 |

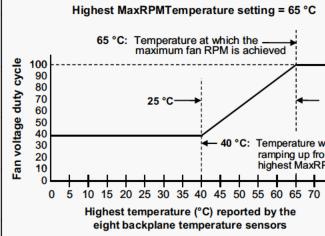

| Setting the Fan Speed vs. Chassis Temperature Profile | 67 |

| Default Minimum Fan Speed Threshold Limit             | 67 |

| Rack Mounting the Chassis.                            | 75 |

| Rack Mount Accessory Kits                             | 76 |

#### 7 10 MHz Reference Clock Source

## 8 Configuring the PXI Trigger Bus

| Chassis Trigger Lines.                                        | 84  |

|---------------------------------------------------------------|-----|

| Trigger Bus Segments                                          | 85  |

| Trigger Line Reservations and Routing                         | 85  |

| Persistent Versus Volatile Reservations                       |     |

| Example: Persistent Versus Volatile Reservations              |     |

| Configuring PXI Trigger Bus Connections                       | 88  |

| Front Panel Trigger Ports                                     | 89  |

| Trigger Port capability as a function of the firmware version | 89  |

| Trigger Port capability using Trigger Bridge 2018 firmware    | 92  |

| Front Panel Trigger Port Configuration Guidelines.            | 96  |

| Using KtMTrig Trigger Manager IVI Driver                      | 101 |

| Installation Requirements                                     | 101 |

| Supported Operating Systems:                                  |     |

| Shared Components                                             |     |

| VISA.NET                                                      |     |

| Uninstall                                                     | IUZ |

## 9 Multiple Chassis Operation

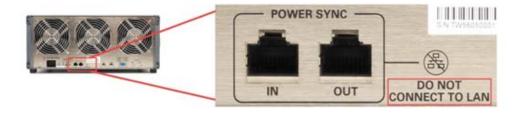

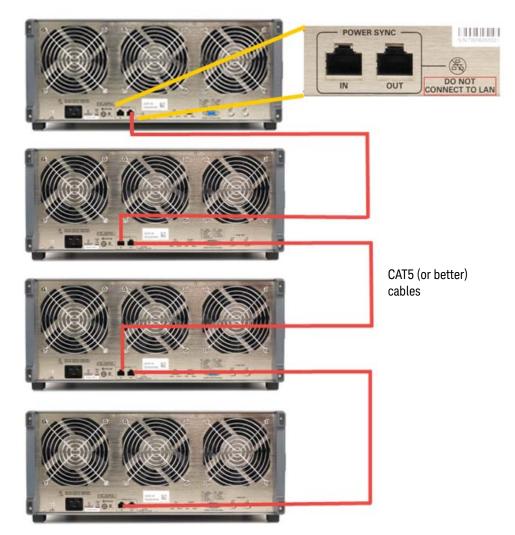

| Multiple Chassis Power Sync                                                                  | 106 |

|----------------------------------------------------------------------------------------------|-----|

| Power Sync Cabling                                                                           | 108 |

| Power Sync and Other Features                                                                | 109 |

| Chassis Rear Panel Inhibit Switch                                                            | 109 |

| Wake on LAN Signal                                                                           |     |

| Wake on PCIe                                                                                 |     |

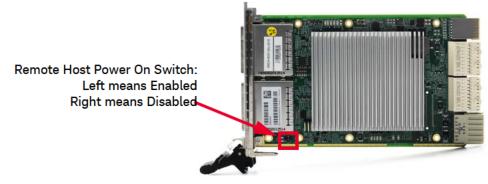

| Remote Power On with M9022A, M9023A, M9024A                                                  | 109 |

| Power Sync with Multiple PXIe Chassis                                                        | 110 |

| Connect Multiple $PXIe\xspace$ or $AXIe\xspace$ Chassis Together with a Single Controller? . | 111 |

## 10 PCIe Link Configuration

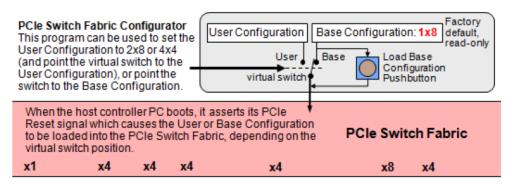

| Changing and Restoring the M9018 PCIe Switch Fabric Configuration | . 115 |

|-------------------------------------------------------------------|-------|

| Selecting a Link Configuration                                    |       |

| Using the PCIe Switch Fabric Configurator program                      | . 120 |

|------------------------------------------------------------------------|-------|

| Configuring the chassis to run at Gen 1 speeds                         | . 129 |

| Reconfiguration failure                                                | . 130 |

| Restoring operation after an interruption of the configuration process | . 130 |

| Restoring the Factory Default 1x8 Base Configuration                   | . 131 |

#### 11 Chassis Maintenance

| Chassis Firmware and Revision140                                   |

|--------------------------------------------------------------------|

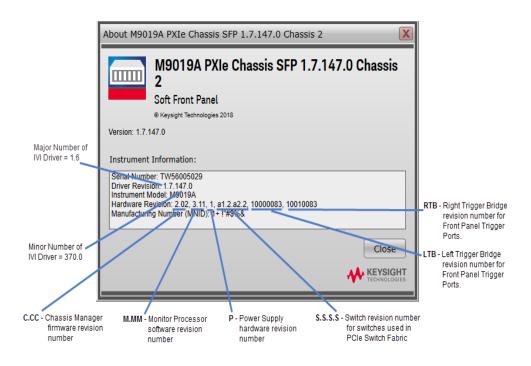

| Viewing the Chassis Revision Information Using the SFP140          |

| Viewing the Chassis Revision Information Using the IVI Drivers 141 |

| Updating Chassis Firmware                                          |

| Chassis Backplane Switches142                                      |

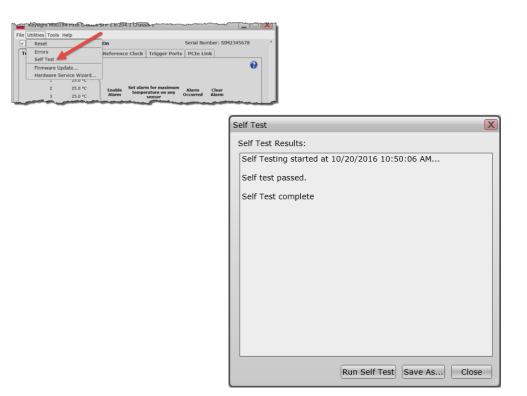

| Performing a Chassis Self Test144                                  |

| Performing Self Test using the Soft Front Panel                    |

| Performing Self Test using the IVI Drivers                         |

| Self Test Codes and Messages146                                    |

1 Index

PXIe Chassis Family User Guide

# 1 Introduction to the PXIe Chassis

Keysight provides three PXIe chassis in the PXIe Chassis Family:

- M9010A a Gen 3, 24 GB/s,10-Slot PXI chassis (www.keysight.com/find/M9010A)

- M9018B a Gen 2, 8GB/s, 18-Slot PXI chassis (www.keysight.com/find/M9018B)

- M9019A a Gen 3, 24 GB/s, 18-Slot PXI chassis (www.keysight.com/find/M9019A)

The PXIe chassis is the backbone of a PXIe system. These chassis have a high performance backplane providing PXI modules in the chassis the ability to communicate rapidly with one another and to PC. It also provides power and cooling for the modules.

The PXIe Chassis Family Driver supports five PXIe Chassis including the M9010A, M9018A, M9018B, M9019A, and M9043A. The M9018A is now discontinued, but still fully supported by the PXIe Chassis Family Driver. The M9018B is a drop-in replacement for the M9018A. The M9043A is only available as part of a Keysight solution. The M9043A has all the features of the M9019A plus an integrated High Frequency Reference clock. The High Frequency Reference clock features match those found in the M9300A, thus providing all the M9300A features without consuming a module slot.

| NOTE | For information on using M9018A, refer to the user documentation<br>available at www.keysight.com/find/M9018A. For information<br>regarding using the PXIe Family Chassis Driver with the M9018A,<br>see "Using the M9018A Chassis with the PXIe Chassis Family<br>Driver" on page 28.                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOTE | It is assumed that you have turned on the chassis system,<br>installed the Keysight IO Libraries Suite, the chassis drivers, and<br>the chassis Soft Front Panel. The <i>Keysight PXIe Chassis Family</i><br><i>Startup Guide</i> provides step-by-step guidance on turning on the<br>chassis system. |

## Key Chassis Features

The Keysight family of PXIe chassis is designed for easy integration into large systems containing multiple PXIe chassis and other, non-PXI instrumentation. The Keysight PXIe chassis have these key features:

- Up to 16 PXIe hybrid slots (the M9010A has 8 hybrid slots), 1 PXIe timing slot, and 1 PXIe system slot.

- 4U chassis with innovative cooling design.

- Ultra high performance PCIe interface

- -- The M9010A has Gen 3 PCIe with a two-link (x8, x16) system slot and x8 links to the hybrid/timing slots.

- -- The M918B provides configurable 2-Link (2x8) and 4-Link (4x4) plus M9021A configuration (1x8).

- -- The M9019A provides Gen 3 PCIe with a two-link (x8, x16) system slot and x8 links to the hybrid/timing slots.

- High data bandwidth (maximum 24 GB/s system and 8 GB/s slot-to-slot).

- Multi-chassis power-sequencing using rear panel RJ-45 connectors.

- Front panel external trigger input/output ports.

- One common driver supports IVI-C and IVI.NET for all three chassis (and the M9018A PXIe chassis).

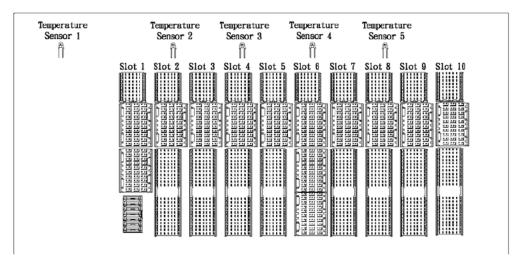

Figure 1 shows a front view of the M9019A chassis. The M9018B chassis is similar; the M9010A chassis is similar but has ten slots.

Figure 1 Keysight M9019A PXIe Chassis Front and Side View (The other chassis are similar)

The following figure shows the M9019A chassis rear panel. The M9018B chassis rear panel is similar; the M9010A chassis has two fans.

Figure 2 Keysight M9019A PXIe Chassis Rear and Side View (The other chassis are similar)

#### Front Panel Trigger Ports

Two front panel SMB trigger connectors connect to the PXI [0:7] backplane trigger bus in Trigger Bus Segment 1 and 2 in the M9010A chassis and Trigger Bus Segments 1, 2 and 3 in the M9018B and M9019A chassis. For information on using these two trigger ports, see "Front Panel Trigger Ports" on page 89.

Figure 3 Chassis Front Panel Trigger Ports (M9019A shown)

## NOTE

Make certain that your test system application is not running when you reconfigure these two trigger ports. Reconfiguring the ports may cause an unexpected pulse on the trigger port lines.

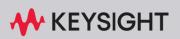

## Interactive Block Diagram

An interactive Block Diagram exists for all three chassis. This Block Diagram is usable for training and understanding how the chassis works. You can download the block diagram from:

www.keysight.com/find/pxi-blockdiagram

The Block Diagram and other information is available on the individual the web pages of the three PXIe chassis:

www.keysight.com/find/M9010A

www.keysight.com/find/M9018B

www.keysight.com/find/M9019A

## Chassis (Static) Block Diagram

Figure 4 Chassis (Static) Block Diagram

Keysight PXIe Chassis Family Startup Guide

## Chassis Maintenance and Inspection

## WARNING

These chassis are Safety Class 1 Products (provided with a protective earthing ground incorporated in the power cord). The mains plug shall only be inserted in a socket outlet provided with a protective earth contact. Any interruption of the protective conductor inside or outside of the product is likely to make the product dangerous. Intentional interruption is prohibited. Inspect the protective conductor periodically to ensure that it is uninterrupted.

- No operator serviceable parts inside. Refer servicing to qualified personnel.

- To prevent electrical shock, do not remove covers.

- To prevent electrical shock, disconnect the chassis power cord before cleaning. Use a dry cloth or one slightly dampened with water to clean the external case parts. Do not attempt to clean internally.

No periodic maintenance of the chassis is required. However, Keysight recommends monitoring the Primary Power Module (PPM) voltage rails, the chassis fan speeds, and the chassis firmware an ongoing basis:

- Power supply voltages The power supply voltages (5 Vdc, 5 Vaux, 12 Vdc, and –12 Vdc) should all be within ±5% (10% for 3.3 Vdc) of their nominal values. Keysight recommends checking the power rails at least yearly. The power rails are accessible on the rear panel DB-9 connector. See "Measuring the Main Voltage Rails Directly" on page 54.

- Fan speeds The chassis has fans located at the rear of the chassis. A low fan speed possibly indicates that a fan is wearing out or a fan blade is partially obstructed. Keysight recommends using the chassis Soft Front Panel to check the fan speeds yearly as well. See "Monitoring Chassis Fan Speeds" on page 67.

- **Chassis firmware** Keysight recommends that you periodically check to see if there is a chassis firmware revision available that is later than your chassis firmware revision. If so, it is suggested that you download and install the latest firmware revision available as described in "Updating Chassis Firmware" on page 141.

If a power supply voltage is out of tolerance or a fan speed is low, see the *Keysight PXIe Family Chassis Service Guide* for diagnostic information and troubleshooting tips.

#### CAUTION

The weight of an empty M9018B or M9019A PXIe chassis (no modules installed in the chassis) is approximately 29.8 lbs (13.5 kg). Lift the chassis using a single side handle only when the total chassis weight (chassis plus installed modules) does not exceed 75 lbs (34.0 kg). Otherwise use both side handles to lift the chassis.

The M9010A chassis weighs 30.91 lbs (14.02 kg).

Installing modules in the chassis may increase its weight to a point where two people are required to lift the chassis. If two people are not available, use a mechanical lift to lift the chassis. The chassis should be transported using a rolling cart.

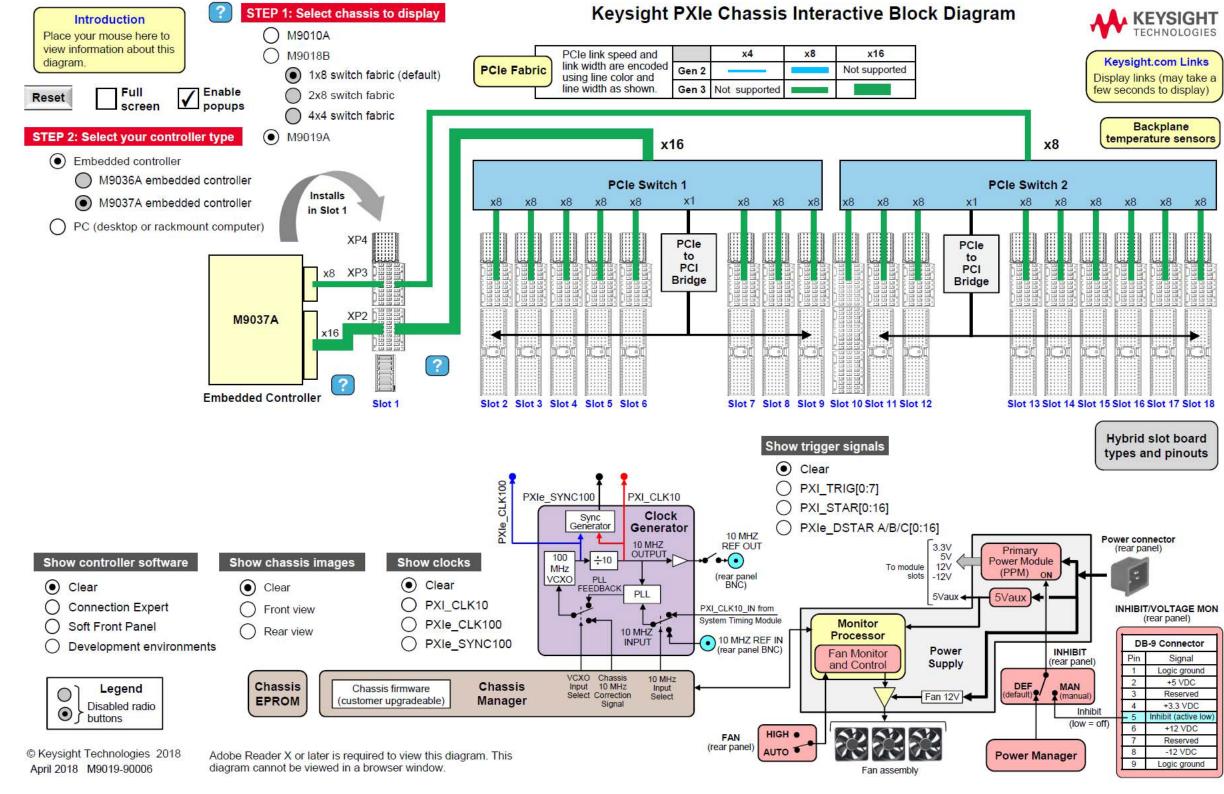

## Static-safe Handling Procedures

Electrostatic discharge (ESD) can damage or destroy electronic components. Use a static-safe work station to perform at work on electronic assemblies. The figure shows a static-safe work station using two types of ESD protection:

- Conductive table-mat and wrist-strap combination

- Conductive floor-mat and heel-strap combination

Both types, when used together, provide a significant level of ESD protection. Of the two, only the table-mat and wrist-strap combination provides adequate ESD protection when used alone. To ensure user safety, the static-safe accessories must provide at least 1 M $\Omega$  of isolation from ground.

## WARNING

DO NOT use these techniques for a static-safe work station when working on circuitry with a voltage potential greater than 500 volts.

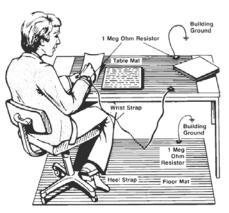

#### Terminology

The combination of the chassis, the host controller (and a PCIe cable if the host controller is a remote controller), and the chassis I/O software running on the host controller is referred to as a chassis system. The computer that controls the chassis is known as the host controller or system controller, and is shown at the top of the hierarchy in the following figure.

Figure 5 System Controller Types

The host controller can either be a remote controller or an embedded controller.

A **remote controller** can be a desktop PC or a rack mounted PC. The remote controller interfaces to the chassis with an M9048B or M9049A Host Adapter PCIe Interface modules (desktop adapter) installed in the PC, through a PCIe cable to an M9022A, M9023A, or M9024A PXIe System Interface Module installed in slot 1 of the chassis. The M9048A and M9021A can be used with the M9018A and M9018B chassis in Gen 2 mode.

An **embedded controller**, such as the Keysight M9037A Embedded Controller, is a small form-factor, Windows-based PC that is designed for installation in the system controller slot of the chassis (slot 1). An embedded controller consumes two or three expansion slots to the left of chassis slot 1.

#### NOTE

For a PC to serve as a remote controller, its BIOS must enumerate all the PCIe slots in the chassis. Many computers cannot enumerate a sufficient number of PCIe slots and may not work for your configuration.

Keysight provides the document Tested PC and PXI/AXIe Chassis Configurations, which lists the embedded, desktop and rack-mounted PCs that have been verified to enumerate the PCIe slots in the PXIe chassis. Use this document, available under the Document Library tab at www.keysight.com/find/pxi-chassis, to guide your selection of remote controller PCs.

## System or Cable Interface Modules

Make certain that you install the driver software for the M9022A, M9023A, or M9024A System Interface Modules. The M9021A Cable Interface module does not require a software driver.

Keysight's M9021A Cable Interface module can operate only with the 1x8 switch fabric found on the M9018A and M9018B chassis. The M9021A *cannot* be used with the M9010A and M9019A chassis – use the M9022A, M9023A, or M9024A System Interface Modules with any Keysight PXIe chassis.

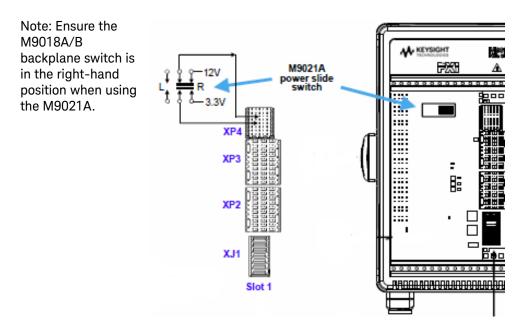

## Using the M9021A PCIe Cable Interface Module with the M9018A/B

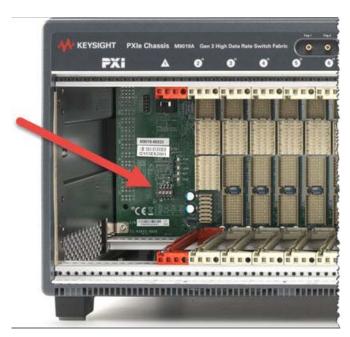

The M9021A PCIe Cable Interface module does not derive power from the chassis connector used by PXI embedded controllers. Instead, the modules use the top connector on the chassis backplane for its 3.3V and 12V power. However, a switch on the M9018A and M9018B chassis backplane must be set to supply those voltages to the connector.

The default position of the switch is to the left and does not supply the voltages to the connector. To use the M9021A Cable Interface module in Slot 1 of either chassis, you must move the slide switch to the right before installing the module.

## Installing PXI Modules in the Chassis

Recommended best practices to ensure proper and safe module operating conditions:

## CAUTION

PXI hard ware does not support "hot-swap" (changing modules while the chassis is powered on) capabilities. Before installing or removing a module into/from the chassis, power off the chassis to prevent damage to modules.

- Ensure proper chassis airflow is maintained

- Select a chassis that provides thermal protection if fans become inoperable or forced air cooling is obstructed

- Use slot blockers (Keysight Y1212A) and EMC filler panels (Keysight Y1213A) in empty module slots to ensure proper operating temperatures. The Keysight Y1214C Air Inlet kit (not for M9010A use) supplies additional cooling air from the front of the chassis. These accessories optimize module temperature performance and reliability of test system.

- Monitor the chassis temperatures and fan speeds to determine a balance of fan noise and cooling performance.

- Do not disable fans. Position chassis to allow plenty of space around chassis air intake and fan exhaust.

- Place the chassis in a horizontal position such as in a rack or on a bench.

- At environment temperatures above 45°C, set chassis fan speed to high.

The M9018B and M9019A chassis have multiple air intakes located at the lower sides, lower front, and chassis bottom. Do not block the air intakes or fan exhausts.

The M9010A chassis has two fans that pull air from the rear of the chassis and exhausts it out the front and top. Do not block the air intakes or fan exhausts.

WARNING Inserting modules into the chassis when it is in a vertical position increases the possibility of bending pins on the backplane and permanently damaging the chassis. It is recommended that you insert modules only with the chassis in a horizontal position, such as in a rack or on a bench. Once the modules are inserted and secured, the chassis may be used in a vertical position. However, before moving the chassis to the vertical position, install all the blanking plates to prevent debris falling onto the chassis and getting lodged in the backplane connectors.

- 1 Make sure that the line cord is plugged in to establish earth ground and that the chassis power switch is Off.

- 2 Ensure that the **Fan** switch (on the chassis rear panel) is set to AUTO and the **Inhibit** switch is set to DEF. Use AUTO unless you have a specific application that requires HIGH.

Chassis Rear Panel Fan and Inhibit Switches

- **3** Position the chassis to provide ample space around the chassis fan intake and exhaust vents. Blockage by walls or obstructions affects the airflow needed for cooling. Place the chassis in a horizontal position such as in a rack or on a bench.

- **4** Before inserting a module into the chassis, back the mounting screws out to ensure that there is no interference between the screws and the mounting rails.

- **5** Holding the module by the injector/ejector handle, slide it into an available PXI (or hybrid) slot.

- **a** Install the module into the slot of the chassis by placing the module card edges into the front module guides (top and bottom).

- **b** Ensure that the injector/ejector handle is pushed down in the unlatched (downward) position. Slide the module to the rear of the chassis.

- **c** Slide the module completely into the chassis. When you begin to feel resistance, lift up on the injector/ejector handle to fully inject the module into the chassis.

- 6 Secure all modules to the chassis using the module mounting screws. Use a #1 Pozidriv<sup>®</sup> or a slotted screw driver and torque to 5Lb-In (0.57N-m). Performance may suffer if the screws are not tightened properly.

- 7 Verify that the PXI chassis fans are operable and free of dust and other contaminants that may restrict airflow.

- **8** Install filler panels and slot blockers after installing the modules. Missing filler panels or slot blockers may disrupt air circulation in the chassis. The left-most slot does not accept a slot blocker.

- **9** If you are using a PCIe Cable Interface, connect the Cable Interface in the chassis to the PC host per the instructions that came with the Cable Interface.

10 Power up the PXI chassis.

11 If you are using a remote PC, reboot the PC host.

#### Avoiding Bent Pins

The chassis backplane contains hundreds of pins. These pins mate with the sockets on the module when you slide the module into the chassis. When you first insert the module, you insert it between the top and bottom rails. As you slide the module in, the side of the connectors touch to further align the module's connector over the pins. The final push to insert the module seats the pins tightly in the connectors.

Be aware that misuse can result in bent pins. If a chassis backplane has a single bent pin, it is possible that scope of the damage is limited to one slot. However, a bent pin can touch an adjacent pin, causing an electrical short that further damages all slots in the chassis. The impact of a bent pin can range from none, to subtle, to severe. A bent pin can cause unpredictable behavior in the chassis and the instruments. It can be very difficult to determine the root cause of this erratic behavior.

#### Methods to avoid bent pins

- Insert modules in horizontal chassis

Only insert modules in a chassis that is positioned horizontally, such as in a rack or on a bench. Do not stand the module on the floor and slide the modules in vertically. The mechanical engineering tolerances do not support quality alignment while the chassis is in the vertical position. Once the modules are secured and all blanking plates installed, the chassis can be used in a vertical position.

- Avoid open slots in a vertical chassis

If a chassis is positioned vertically and slots are open, it is easy for debris to fall onto the connector pins. If the slots are open, avoid the vertical position even if it is temporary while deploying the chassis. It is easy for debris to fall in unnoticed and lodge into the connectors.

- Do not use force

Use very gentle pressure when you slide in the modules. If there is an unusual restriction, pause and inspect. Pushing harder might bend a pin.

- Inspect before use

Prior to sliding a module into a slot, inspect the end of the connector for damage. Look at the holes into which the pins insert to ensure that the holes are empty. Look for scratches or groves in the plastic connector that might cause misalignment or hint at past damage. If you find damage, repair it before use.

Although rare, it is possible to spread damage with the use of a single defective module. If you have a module with an undetected damaged connector and move it from slot to slot or from chassis to chassis, you might be damaging every slot you slide the module into. Once a chassis' pins are damaged in that slot, it is possible to damage a good module by sliding it into one of the damaged slots.

#### Periodic chassis inspection

Depending on your use, you might never need to examine a chassis backplane for bent pins. Perhaps you assemble a system once and then it is never subsequently modified. This type of use does not require inspection. However, if your chassis use pattern is to have modules inserted and removed on a regular basis, and if it is done by many different people, you might find it beneficial to periodically inspect all of your chassis backplanes.

#### How to inspect your chassis backplane for bent pins or debris

Remove all the modules from the chassis. Remove power. Move the chassis to a well-lit bench and stand the chassis on end so that light shines down onto the backplane. Visually inspect all the pins on the backplane. Verify the pins are in straight rows. Look for discoloration resulting from an electrical short.

Look for and remove debris laying in the backplane connectors.

#### What to do if you find a bent pin

Send the chassis in for repair.

## Chassis Front Panel LEDs

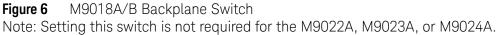

The chassis contains three LEDs on its front panel to the left of the ON/Standby (power) push button, as shown in the following figure.

Figure 7 Chassis Front Panel LEDs

The front panel LEDs, depending on whether they are off, on continuously, or flashing, provide important information on the status of the chassis, and should be monitored regularly. The following table lists each LED and describes the information it provides.

The M9010A has a protective algorithm to monitor the AC input current and automatically power-off if the AC input current goes above 8.5A. When automatically powered-off, the chassis will continually blink the power LED 3 times.

| LED<br>(color)      | Off                                                                                                                                                                                                                                                               | On Continuously                                                                                                                                                                                                                                                                                                                                                                                | Flashing                                                                                                                                                                                                                                                                                                                                                                                                                                                               | All three LEDs flash                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Temp LED<br>(amber) | This LED is off if<br>the chassis<br>temperatures are<br>OK. To allow you<br>to validate that<br>this LED is<br>working, the LED<br>is turned on for<br>the first three<br>seconds after the<br>chassis is<br>powered up.                                         | This LED is never on continuously.                                                                                                                                                                                                                                                                                                                                                             | Indicates one or more<br>temperature sensors is<br>reporting a temperature above<br>the limit, either the 70°C<br>default limit or the user set<br>limit. The limit, if changed, is<br>reset back to 70°C at the next<br>chassis power cycle. If the<br>temperature condition causing<br>the flashing to occur is no<br>longer present, the<br>Temperature LED will turn off,<br>indicating that the chassis<br>temperatures are OK.                                   | All three LEDs on for 10<br>seconds and off for 1<br>second indicates that<br>the Monitor Processor,<br>which controls flashing<br>of the LEDs, has been<br>unable to communicate<br>with the Chassis<br>Manager. Refer to the<br><i>PXIe Chassis Family</i><br><i>Service Guide</i> for<br>troubleshooting<br>information.                                                                                                           |

| Fan LED<br>(green)  | Indicates that the<br>chassis is turned<br>off.<br>See the Keysight<br>PXIe Chassis<br>Family Service<br>Guide for details.                                                                                                                                       | Indicates all fans are<br>operating above the<br>minimum limit RPM.<br>The default minimum<br>limit for the M9010A is<br>900 RPM and for the<br>M9018B and M9019A<br>is 1200 RPM. The fan<br>speed minimum limit<br>can be changed in the<br>SFP or<br>programmatically. The<br>limit, if changed, is<br>reset back to the<br>default minimum limit<br>RPM at the next<br>chassis power cycle. | Indicates that one or more of<br>the fans are operating below<br>the minimum limit, either the<br>default minimum limit RPM or,<br>if changed, the user set<br>minimum limit.<br>If the fan speed condition<br>causing the flashing to occur<br>is no longer present, the Fan<br>LED will return to on<br>continuously.                                                                                                                                                | The Soft Front Panel<br>Identify On feature<br>allows you to identify<br>which chassis is<br>connected to the SFP<br>application. For<br>example, if you have<br>multiple M9019A<br>chassis in a system with<br>an SFP application<br>running for each<br>chassis, you can easily<br>identify with chassis is<br>connected to the<br>application. When you<br>click the Identify On<br>check box, all three<br>front panel LEDs (Fan, |

| Power LED<br>(blue) | Indicates that the<br>chassis is turned<br>off. If you attempt<br>to turn the<br>chassis on but the<br>Power LED<br>remains off, this<br>can indicate<br>several possible<br>problems<br>See the Keysight<br>PXIe Chassis<br>Family Service<br>Guide for details. | Indicates all supply<br>voltages are within<br>their limits. Factory<br>default limits are<br>±10% for 3.3V and<br>±5% for the other<br>power supply voltages.<br>The limits can be<br>changed in the SFP or<br>programmatically. The<br>limits, if changed, are<br>reset to factory default<br>at the next chassis<br>power cycle.                                                            | Indicates one or more of the<br>four supply voltages are<br>outside of their limits, either<br>the factory default limits or,<br>the user-set limits. Refer to<br>the Keysight PXIe Chassis<br>Family Service Guide for<br>troubleshooting suggestions. If<br>the power supply condition<br>causing the flashing to occur<br>is no longer present, the<br>Power LED returns to<br>continuously on state. See<br>note above about the M9010A<br>over-current protection | Temp, and Power) blink<br>at a 7 to 10 second rate<br>(50% duty cycle).                                                                                                                                                                                                                                                                                                                                                               |

## Related Documentation

The documentation listed below can be found on the chassis web pages below.

- Keysight PXIe Chassis Family Startup Guide

- Keysight PXIe Chassis Family User Guide

- Keysight M9019A PXIe Chassis Family Data Sheet

- Keysight M9022A/M9023A/M9024A PXIe System Interface Module Data Sheet

- *Tested PC and PXI/AXIe Chassis Configurations*. This document lists the PCs that have been verified to work with the PXIe family of chassis.

- PXIe Chassis Block Diagram (see http://www.keysight.com/find/pxi-blockdiagram)

- Multi-Chassis Designer Tool (see http://www.keysight.com/find/pxie-multichassis)

For the latest versions of these documents, visit the Keysight chassis web sites:

www.keysight.com/find/M9010A

www.keysight.com/find/M9018B

www.keysight.com/find/M9019A

Product specifications, available accessories, firmware and software may change over time. Check the Keysight product websites above or at www.keysight.com/find/pxi-chassis for the latest updates to the product software, guides, help files and data sheets.

## Using the M9018A Chassis with the PXIe Chassis Family Driver

The original M9018A PXIe chassis was provided with its own driver. This is called the legacy *AgM9018* driver (formerly *AgPxiPc* driver); the last version, released in 2015, was 1.5.80.1. The new M9018B, and the M9010A and M9019A PXIe chassis, are shipped with a new *PXIe Family Chassis* driver. This section describes how the M9018A and M9018B chassis inter-operate with the two different chassis drivers.

Figure 8 Keysight M9018A 18-slot PXIe Chassis

- The new M9018B PXIe chassis is a direct, drop-in replacement for the M9018A chassis and supports the legacy *AgM9018* driver. The *AgM9018* driver is also supplied as part of the *PXIe Chassis Family* driver.

- The first *PXIe Family Chassis* driver shipped in August 2016 and supports both the M9018A and the new M9018B chassis and the M9019A chassis. A newer version of the *PXIe Family Chassis* driver shipped in December 2016 and added support of the M9010A 10-slot chassis. The M9010A and M9019A chassis cannot use the legacy *AgM9018* Driver.

- Any application software created using the *AgM9018* driver will run without modification on the new M9018B chassis.

- The Soft Front Panel software installed as part of the new *PXIe Chassis Family* driver runs with all four chassis. You can run the legacy M9018A Soft Front Panel; it is located at:

#### C: /Program Files (x86)/Agilent/M9018/bin/AgPXIChassisSFP.

- Your compiled M9018A application programs using the legacy *AgM9018* driver will work without recompiling because the legacy driver is included with the new *PXIe Chassis Family* driver.

- However, application software compiled to control the M9018A will not control the M9010A or M9019A chassis. To control these chassis, you must use the new 1.6.3.1 (or later) drivers. Application software compiled for the M9018A will control the M9018B but only for the M9018A features.

## NOTE

Both the M9018A and M9018B support a Gen2 PCIe link speed. The M9010A and M9019A support a Gen3 PCIe link speed.

## Additional changes from the M9018A to the M9018B

The following new features exist in the M9018B but not in the older M9018A:

- Replaceable Power Supply in the M9018A is not compatible with the M9018B or M9019A.

- The two front panel trigger ports (TRIG 1 and TRIG 2)

- Rear panel Power Sync feature.

- Manual control of the 10MHz Reference Clock.

- Reference Clock alarm for the clock phase lock loop transition to unlock.

- Monitoring of the +5V\_STANDBY supply (also known as the 5Vaux supply).

#### Driver Behavior

The following behaviors describe what may happen when using an M9018B chassis with the AgM9018 driver.

- When an M9018B is used with the legacy *AgM9018* driver (version 1.5.80.1) environment in Keysight's IO Libraries Suite Connection Expert Instrument View tab, it appears as an "M9018A." However, in the Connection Expert Chassis View tab, it shows as an "M9018B.

- When an M9018B is used with the older *AgM9018* driver (version 1.5.80.1) environment, the Host PC's Windows Device Manager lists the chassis as an "M9018A" instead of an "M9018B."

- Using the *PXIe Chassis Family* driver Fabric Configuration Utility, restores that same internal M9018B data field to its original factory value of M9018B.

You can observe that the M9018B is self identifying as an M9018A, if you run self-test and get the error 541, or if you run the SFP or IO Library Connection Expert and notice that the software is reporting the chassis as an M9018A.

#### Summary

The M9018B chassis may report as an "M9018A" in some situations, but that set of situations will change depending on the use of the *AgM9018* driver 1.5.80.1 vs the *PXIe Chassis Family* driver.

The new M9018B will work in environments as a drop in replacement for the M9018A running the *AgM9018* driver (version 1.5.80.1). When using the *AgM9018* driver, the M9018B will show up as an M9018A in the following situations:

- IO Libraries Connection Expert Instrument Tab

- Windows Device Manager

However, the M9018B will show up as an M9018B in IO Libraries Suite Connection Expert Chassis tab

If you use the *AgM9018* 1.5.80.1 version of the PXIe Fabric Configuration utility on the M9018B to change the fabric, it will have a side effect of also changing a data field inside the M9018B from M9018B to M9018A. After that change, the above mentioned screens will now contain M9018A instead of M9018B. This change will persist until the PXIe Fabric Configuration utility from the *PXIe Chassis Family* driver is used to change the fabric in the M9018B. If you don't need to change the fabric, but want to get the M9018B to self identify correctly, then change the fabric to something you don't want and then change it back to the fabric you want.

## Chassis Related Products and Accessories

The following table lists products related to the PXIe family of chassis and chassis accessories. Information on these parts can be found by starting at www.keysight.com/find/pxi-chassis.

## Table 2Chassis Accessories

|             | Keysight Model<br>Number | Description                                                                                                                 |

|-------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Related     | M9037A                   | PXIe Embedded Controller: Intel i7, 4 GB RAM, 240 GB SSD                                                                    |

| Products    | M9048A                   | PCle Desktop Adapter, single port (x8), Gen 2                                                                               |

|             | M9048B                   | PCIe Host Adapter: single port (x8), Gen 3                                                                                  |

|             | M9049A                   | PCIe Host Adapter: dual port (16), Gen 3                                                                                    |

|             | M9021A                   | PCIe Cable Interface Module, single port (x8), Gen 2<br>(use with M9018A or M9018B only)                                    |

|             | M9022A                   | PXIe System Interface Module: single port (x8), Gen 3                                                                       |

|             | M9023A                   | PXIe high performance System Interface Module: dual port<br>(x16) Gen 3                                                     |

|             | M9024A                   | PXIe high performance System Interface Module with connectivity expansion: two gigabit LAN, two USB 3.0, four USB 2.0, GPIB |

| Accessories | Y1212A                   | Slot Blocker Kit (M9010A, M9018A/B, M9019A)                                                                                 |

|             | Y1213A                   | PXI EMI Filler Panel Kit: 5 single-slot panels                                                                              |

|             | Y1214C                   | Air Inlet Module Kit<br>(not for use with M9010A 10-Slot chassis)                                                           |

|             | Y1215C                   | Flush mount rack kit (M9018A/B, M9019A)                                                                                     |

|             | Y1216B                   | Recess mount rack kit (M9018A/B, M9019A)                                                                                    |

|             | Y1217A                   | Rack mount rail kit (M9010A, M9018A/B, M9019A)                                                                              |

|             | Y1218A                   | Cable tray kit                                                                                                              |

|             | Y1270A                   | Front panel interfacing kit for 18-slot PXIe chassis                                                                        |

|             | Y1271A                   | Flush rack mount kit for M9010A chassis                                                                                     |

PXIe Chassis Family User Guide

2

# PXIe Chassis Management Capabilities

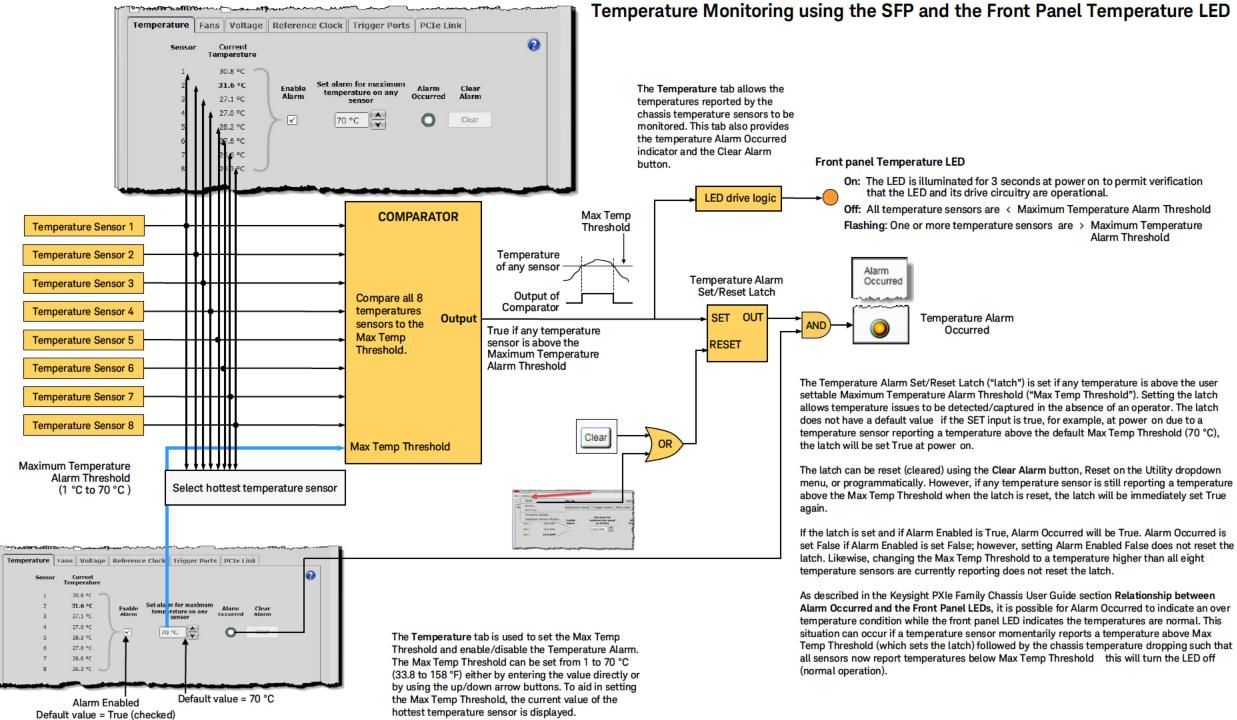

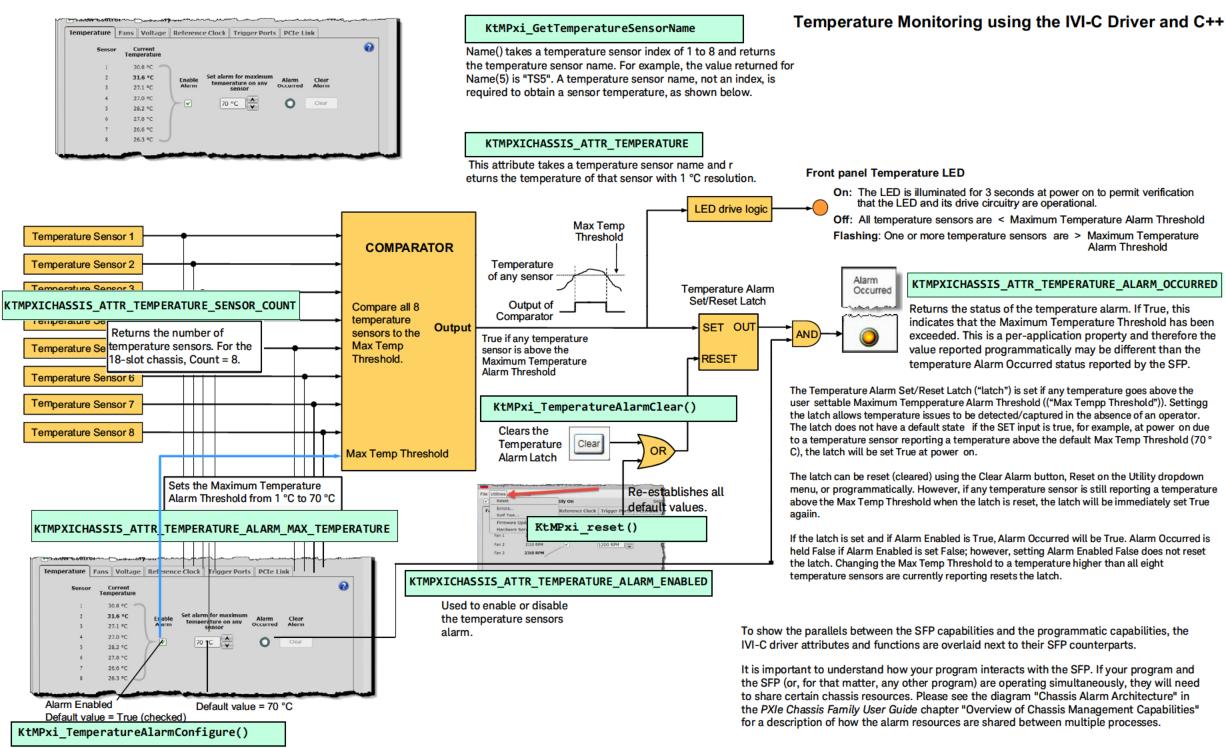

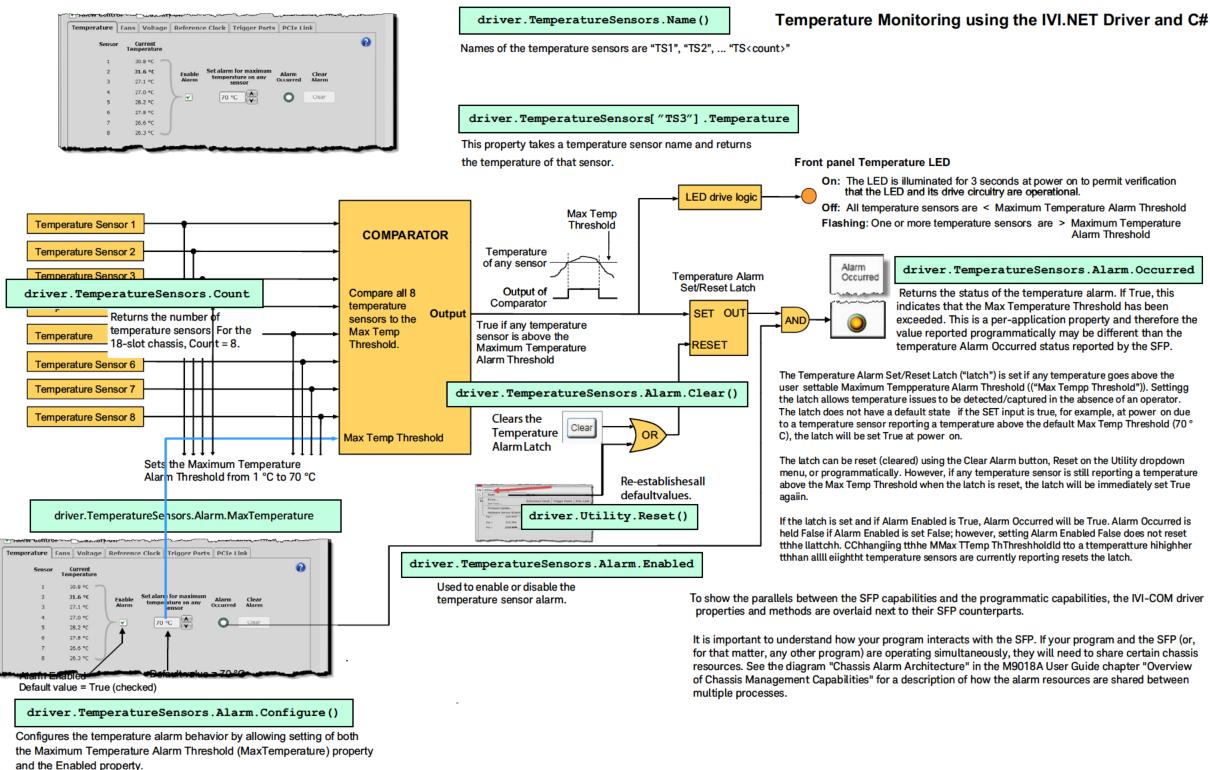

Keysight's PXIe chassis provide extensive management capabilities to allow you to monitor and control many aspects of the chassis operation. For example, you can monitor the temperatures reported by the air flow temperature sensors using the Soft Front Panel (SFP). Furthermore, you can use the SFP to set a minimum temperature alarm threshold such that an alarm will be generated if the temperature of any temperature sensor exceeds the threshold.

In addition to using the SFP to monitor and control the chassis, you can develop programs to monitor and control the chassis. Keysight provides IVI (Interchangeable Virtual Instrument, see www.ivifoundation.org) drivers for the chassis. To support the most popular programming languages and development environments, Keysight offers both the IVI-C and IVI.NET drivers. There are no IVI.COM drivers. See the IVI Foundation website for a description of these drivers. Keysight also provides a LabVIEW driver for the chassis.

Keysight recommends that you use the Soft Front Panel to learn the chassis management capabilities. Because the programmatic capabilities largely parallel the capabilities provided by the SFP, learning the SFP first provides a basis for learning how the IVI.NET and IVI-C drivers interface to the chassis. In support of this approach, each chassis management capability is first described by a diagram showing how that chassis management capability is accessed using the SFP.

NOTE

Do not uninstall the **KtMPxiChassis IVI.NET Driver 1.x.xxx**, **KtMPxiChassis IVI-C Driver 1.x.xxx**, **KtMTrig IVI.NET Driver 1.x.xxx**, or **KtMTrig IVI-C Driver 1.x.xxx** files without also uninstalling the Keysight PXIe Chassis Family driver.

## Summary of Chassis Management Capabilities

The chassis provides the following management capabilities:

- Viewing the chassis hardware and firmware revision information

- Monitoring the fan speed. This monitoring capability includes the ability to set a fan speed threshold such that, if any fan speed falls below the threshold, an alarm is generated. If a fan stops completely, the chassis shuts down.

- Monitoring the chassis temperature sensors. This monitoring capability includes the ability to set a temperature threshold such that, if the temperature reported by any sensor rises above the threshold, an alarm is generated.

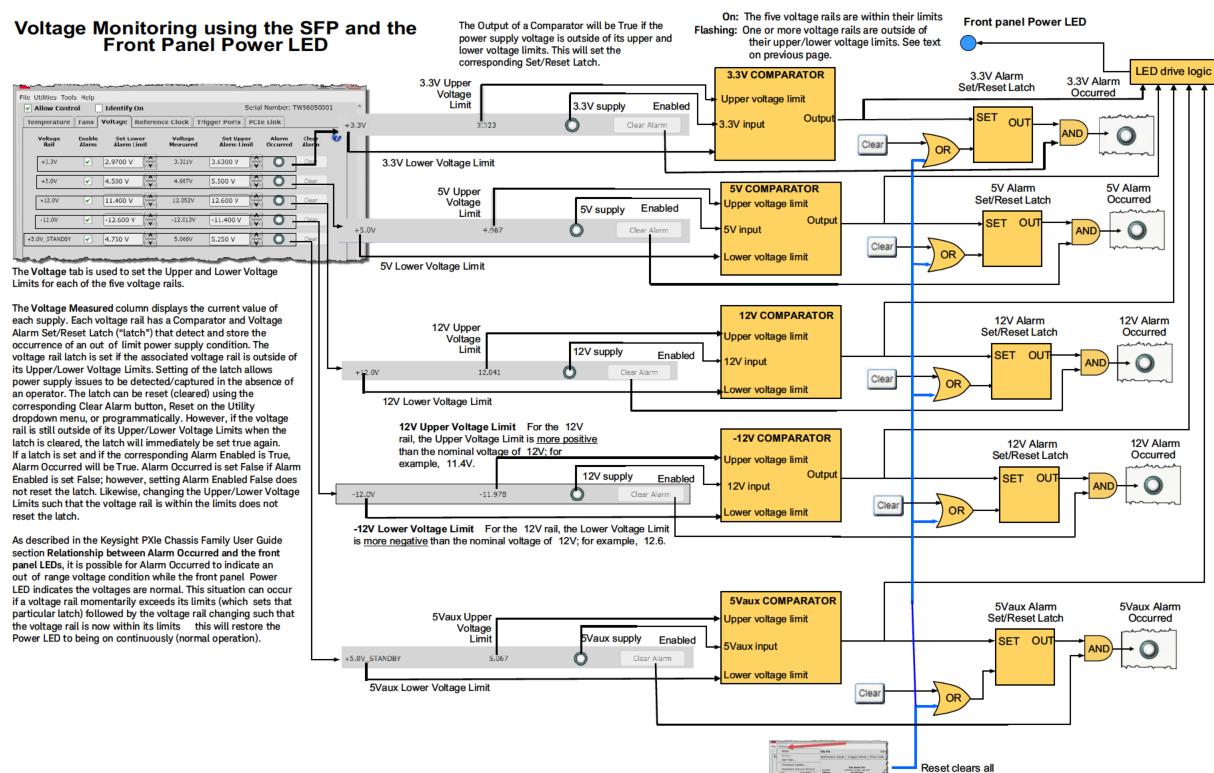

- Monitoring the Primary Power Module (PPM) rails: 3.3 Vdc, 5 Vdc, 12 Vdc, -12 Vdc and 5Vaux (5.0VSTAND-BY). This monitoring capability includes the ability to set upper and lower voltage limits around each voltage rail such that, if a voltage rail falls outside of its limits, an alarm is generated.

- Monitoring and manually selecting the 10 MHz reference clock source.

- Configuring the front panel external trigger ports (TRIG 1 and TRIG 2) inputs/outputs.

- Configuring and monitoring the parallel trigger bus signals in PXI-9 standard (not available in the Soft Front Panel, use the Keysight IO Libraries Suite).

- Executing a chassis self test.

## Using the Soft Front Panel to Configure Chassis Parameters

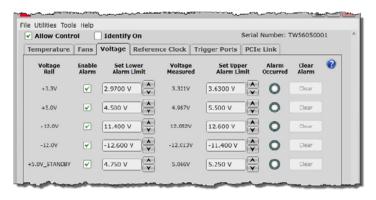

In order to use the Soft Front Panel (SFP) to configure the chassis, the SFP **Allow Control** check box shown in the following image must be checked. This check box, which applies to all tabs of the SFP, is provided to prevent unintentional changing a chassis parameter.

| Utilit es Jui | 5 Help                 |                    |                                  |              |               |

|---------------|------------------------|--------------------|----------------------------------|--------------|---------------|

| Allow Contr   | ol 🗌 Iden              | tify On            |                                  | Serial Numbe | r: SIM2345678 |

| emperature    | Fans Volta             | ge Reference Clock | Trigger Ports                    | PCIe Link    |               |

| Senso         | Current<br>Temperature | e                  |                                  |              | 0             |

|               |                        |                    |                                  |              |               |

| 1             | 25.0 °C                | $\gamma$           |                                  |              |               |

| 1             | 25.0 °C<br>25.0 °C     |                    | rm for maximum<br>erature on anv | Alarm C      | ear           |

Figure 9 SFP Allow Control Check Box

## The Chassis Alarm Architecture

The chassis provides eight alarms to assist you in monitoring the chassis. For example, you can set a temperature alarm threshold such that, if a chassis temperature sensor reports a temperature above the threshold, an alarm is generated. Alarms can be set and monitored using either the SFP or programmatically. The eight alarms are:

- Five voltage rails (+3.3 V, +5 V, +12 V, -12 V, 5.0V\_STANDBY) either higher or lower than specified thresholds.

- Chassis air temperature higher than specified threshold.

- Fan Speed slower than specified threshold.

- 10 MHz Reference Clock changed.

#### NOTE

If a fan stops completely, the chassis shuts down.

Chapter 4, "Chassis Alarm Architecture" describes the chassis alarm architecture, including the functionality that is provided in hardware and the functionality that is provided in software. The chapter also describes how alarms operate if multiple processes are using the same alarm.

PXIe Chassis Family User Guide

3

# Chassis and Host Controller Power Up or Down Sequence

This chapter describes the chassis and host controller PC power up and power down sequences. In order for the chassis and the host controller PC to interoperate correctly, they must be powered up and down in specific sequences. Furthermore, the PC must be restarted in certain situations after the chassis is powered up. If these sequences are not followed, the PC may not be able to access the chassis or the modules in the chassis.

NOTE

The chassis has three power states: Powered up, powered down, and unplugged. When powered up, the chassis is fully operational. When powered down, the Primary Power Module (described in "Power Supply Operation" on page 49) is turned off, but 5 Vaux is available to the Monitor Processor and the modules. When unplugged, the chassis is completely unpowered. Unless otherwise stated, the chassis is presumed to be plugged in, and is changing power states between powered up and powered down.

NOTE

When you press the chassis power-on button, if the chassis does not power up and the front panel LEDs do not light, it is possible for the chassis to be in a safety shutdown state. Remove the chassis AC power cord from the chassis for one minute. Reconnect the power cord and turn on the chassis again. If it still does not power on, refer to the *Keysight PXIe Family Chassis Service Guide*.

In brief, the host controller PC should be off whenever the chassis is powering up or down. Because chassis modules are not hot-swappable, chassis modules should only be installed in or removed from the chassis when it is powered down.

The following description of power up and power down sequences apply only to using an external host controller PC. They do not apply to an embedded controller (such as the Keysight M9037A) installed in the chassis because the embedded controller and chassis are powered together.

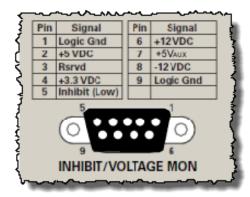

### Methods of powering up the chassis

The method of powering up the chassis depends on the position of the INHIBIT rear panel switch, which can be set to the DEF (default) position or to the MAN (manual) position. These two methods are shown on the interactive block diagram and work as follows:

- INHIBIT switch in the DEF position In this position, the front panel power push button is used to switch the chassis between ON and Standby–hence, this push button is known as the ON/Standby push button. Using this push button requires that a module is installed in the system controller slot (slot 1). This can be a module such as the Keysight M9021A, M9022A, M9023A, M9024A PXIe System Interface Module or an embedded controller.

- INHIBIT switch in the MAN position In this position, the Inhibit signal on the rear panel DB-9 connector controls chassis power. The chassis is powered up by applying a logic high signal (or allowing the pin to float) to the Inhibit signal. When the Inhibit signal is pulled to logic ground, the chassis is in Standby (off except for 5Vaux, an auxiliary power supply).

Keysight recommends leaving the INHIBIT switch in the DEF position when connecting the AC power cord to the chassis. After inserting the power AC power cord, then move the INHIBIT switch to the MAN position. Use of the ON/Standby push button to power up the chassis is assumed unless otherwise noted.

Figure 10 Chassis Rear Panel Inhibit Switch and DB-9 Connector

See "Power Sync and Other Features" on page 109 for information on the multiple chassis Power Sync feature.

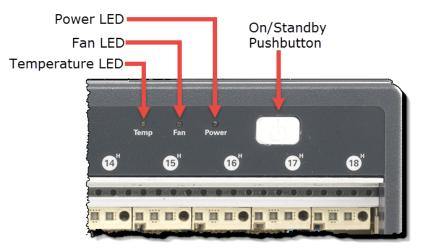

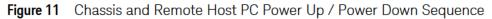

### Power Up Sequencing

When powering up the system, the chassis must be powered up first. After powering up the chassis, you should wait at least three seconds before turning on the PC. The chassis front panel temperature LED, which is on for three seconds after the chassis is powered up, provides a convenient way to measure this delay, as shown below.

NOTE

It is always advisable to boot the PC a second time to ensure that the PC properly enumerates all of the modules within the chassis.

### Power Down Sequencing

The PC should be shut down before the chassis is powered down. This will prevent the chassis, as it is being powered down, from disrupting operation of the PC.

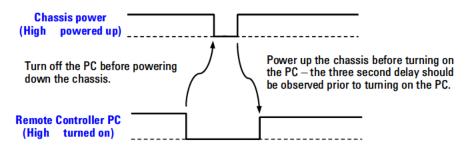

# Performing a System Power Cycle

For a system with a remote controller PC, system restart or power cycle refers to the power sequence shown in the following image. The remote controller PC is turned off followed by the chassis being powered down for at least one second. The chassis is then powered up followed by turning on the PC.

**NOTE:** When the chassis is powered down using the front panel ON/Standby pushbutton or the **Inhibit** signal on the rear panel DB-9 connector, the chassis is still connected to AC power. Therefore, the 5Vaux (auxiliary) supply is powered, and is supplying power to components such as the Monitor Processor. The other chassis supplies 10.3v, UV, 12V, and -12V) are not powered.

Figure 12 Power Sequence for a System Restart

If the chassis contains an embedded controller, a system power cycle consists simply of power cycling the chassis, which will also power cycle the embedded controller.

### Performing a Chassis Hard Reset

A chassis hard reset refers to powering down the chassis and then disconnecting it from AC power. A hard reset is required in response to a few self test failures as described in "Self Test Codes and Messages" on page 146. As previously noted, when the chassis is connected to AC power, the 5Vaux supply is powered, and is supplying power to certain chassis components, such as the Monitor Processor. Performing a hard reset ensures that power is removed from all chassis components.

To perform a chassis hard reset, AC power must be removed from the chassis for a minimum of 30 seconds. This ensures that the 5Vaux supply is completely powered down. The entire sequence is shown in below image.

Figure 13 Power Sequence for a Chassis Hard Reset

In essence, a chassis hard reset is a system power cycle that includes unplugging the chassis from AC power after the chassis is powered down.

PXIe Chassis Family User Guide

# 4 Chassis Alarm Architecture

The chassis provides eight alarms to assist you in monitoring the chassis. For example, you can set a temperature alarm threshold such that, if a chassis temperature sensor reports a temperature above the threshold, an alarm will be generated. Alarms can be set and monitored programmatically and by using the Soft Front Panel (SFP). The eight alarms are:

- Five voltage rails (+3.3 V, +5 V, +12 V, -12 V, 5.0V\_STANDBY) are either lower than expected or higher than specified thresholds

- Chassis air temperature is higher than the specified threshold

- Fan Speed is slower than the specified threshold

- 10 MHz Reference Clock changed

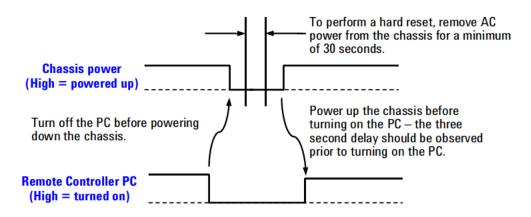

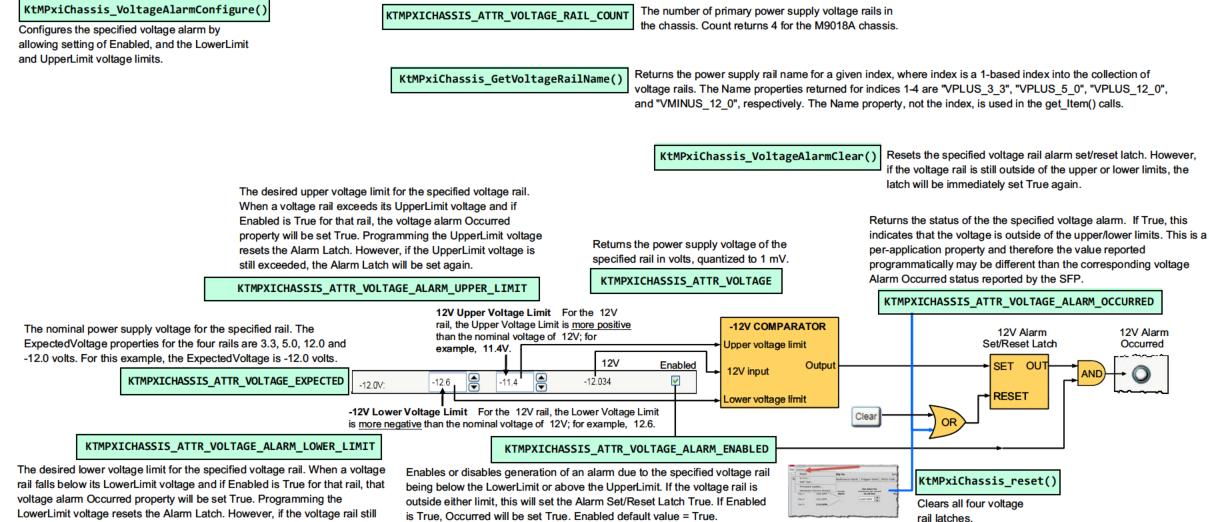

Figure 14 on page 45 describes the chassis alarm architecture, including identifying the functionality that is provided in hardware and the functionality that is provided in software. The figure also describes how alarms operate if multiple processes are using the same alarm.

#### NOTE

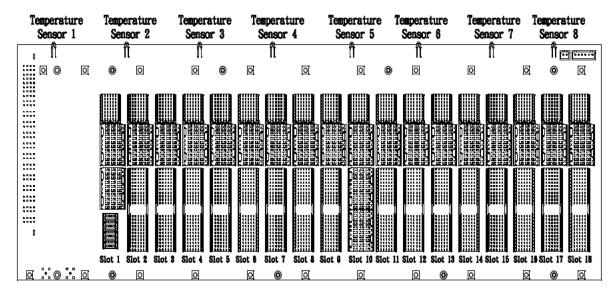

The M9018B and the M9019A both have eight temperature sensors in the chassis. The M9010A has five temperature sensors.

The M9018B and M9019A have a default minimum fan speed of 1200 RPM, but it is 900 RPM for the M9010A.

# Power-on Default Alarm Thresholds

This section summarizes the power-on default values of the chassis alarm thresholds as well as the valid range over which the alarm thresholds can be set.

The phrase "power-on default" means that, regardless of how the thresholds are changed while power is applied, the thresholds return to factory-defined default values when the chassis power is cycled. For example, if you use the SFP to set the Minimum Fan Speed Alarm Threshold to 500 RPM, this setting will not persist through a power cycle; the Minimum Fan Speed Alarm Threshold will be restored to the power-on default limit RPM value when the chassis is power cycled.

#### Table 3 Power-on Default Alarm Thresholds for the M9010A, M9018B, and M9019A Chassis

| Threshold                         |                         | Default Threshold                          | Settable Range                                      |  |  |

|-----------------------------------|-------------------------|--------------------------------------------|-----------------------------------------------------|--|--|

| Minimum Fan Speed Alarm Threshold |                         | 900 RPM for M9010A.<br>1200 RPM for other. | 1 to 10,000 RPM                                     |  |  |

| Maximum Temp                      | erature Alarm Threshold | 70 °C                                      | 1 to 70 °C                                          |  |  |

| 3.3V Rail                         | Upper Voltage Limit     | 3.630V (3.3V + 10%)                        | nominal value +0.01% up to<br>nominal value + 20%   |  |  |

|                                   | Lower Voltage Limit     | 2.970V (3.3V - 10%)                        | nominal value -0.01% down to<br>nominal value -20%  |  |  |

| 5V Rail <sup>1</sup>              | Upper Voltage Limit     | 5.25V                                      | nominal value +0.01% up to<br>nominal value + 20%   |  |  |

|                                   | Lower Voltage Limit     | 4.75V                                      | nominal value -0.01% down to<br>nominal value - 20% |  |  |

| 12V Rail                          | Upper Voltage Limit     | 12.6V                                      | nominal value +0.01% up to<br>nominal value +20%    |  |  |

|                                   | Lower Voltage Limit     | 11.4V                                      | nominal value -0.01% down to<br>nominal value -20%  |  |  |

| –12V Rail                         | Upper Voltage Limit     | -11.4V                                     | nominal value +0.01% up to<br>nominal value + 20%   |  |  |

|                                   | Lower Voltage Limit     | -12.6V                                     | nominal value -0.01% down to<br>nominal value -20%  |  |  |

| +5.0V <sub>aux</sub> <sup>2</sup> | Upper Voltage Limit     | 5.25 V                                     | nominal value +0.01% up to<br>nominal value + 20%   |  |  |

|                                   | Lower Voltage Limit     | 4.75 V                                     | nominal value -0.01% down to<br>nominal value - 20% |  |  |

<sup>1</sup> Note that the 5V rail initially has voltage limits of  $\pm$ 5% around the nominal value. However, the IVI driver will expand the 5V limits to  $\pm$ 10%. Because the PXIe chassis SFP uses the IVI.NET driver, the SFP also expands the 5V limits to  $\pm$ 10%

$^2$  In the PXIe Chassis Family Soft Front Panel, the +5V  $_{\rm aux}$  is shown as +5.0V\_STANDBY.

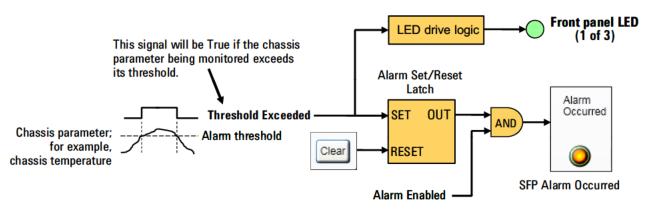

### **Chassis Alarm Architecture**

#### Alarm operation

The chassis has these eight alarms: 1. Fan speed alarm

- 2. Temperature alarm

- 3. +3.3V alarm

- 4. +5V alarm 5. +12V alarm

- 6. -12V alarm

- 7. 5Vaux alarm

- 8. 10 MHz reference clock changed alarm

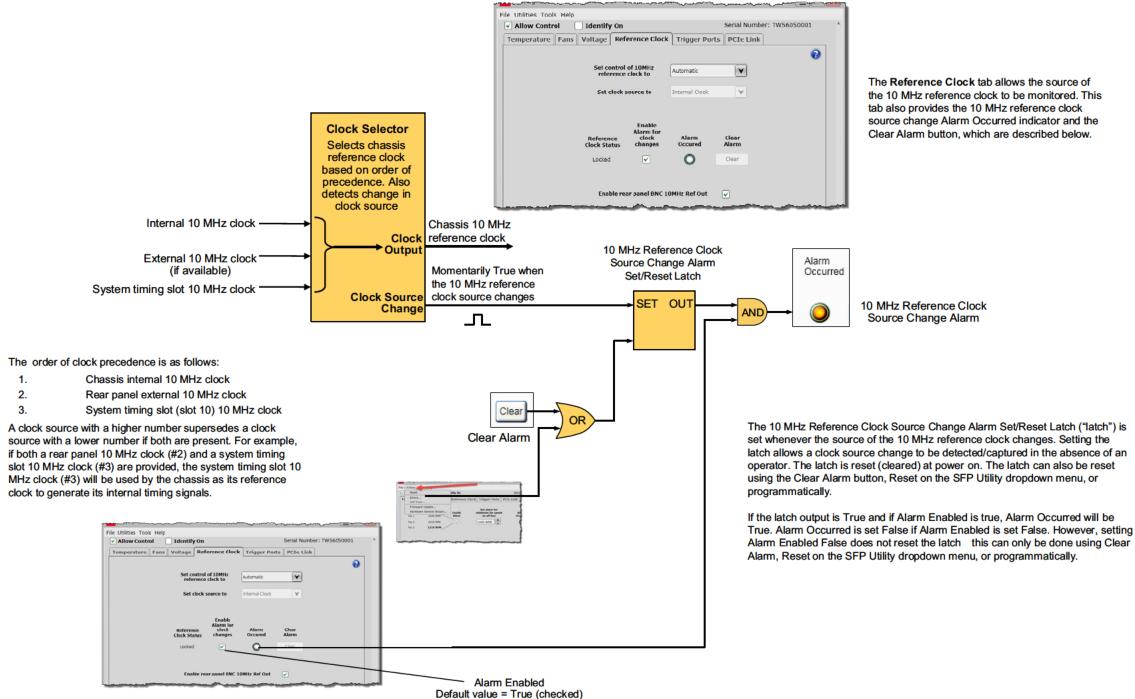

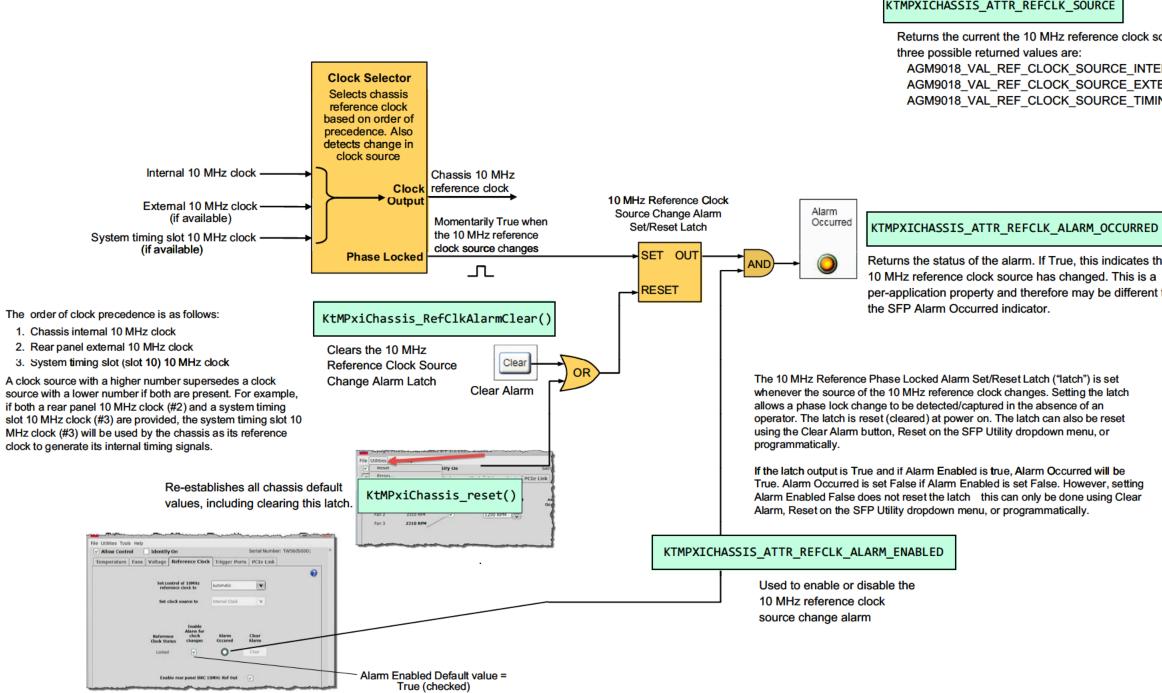

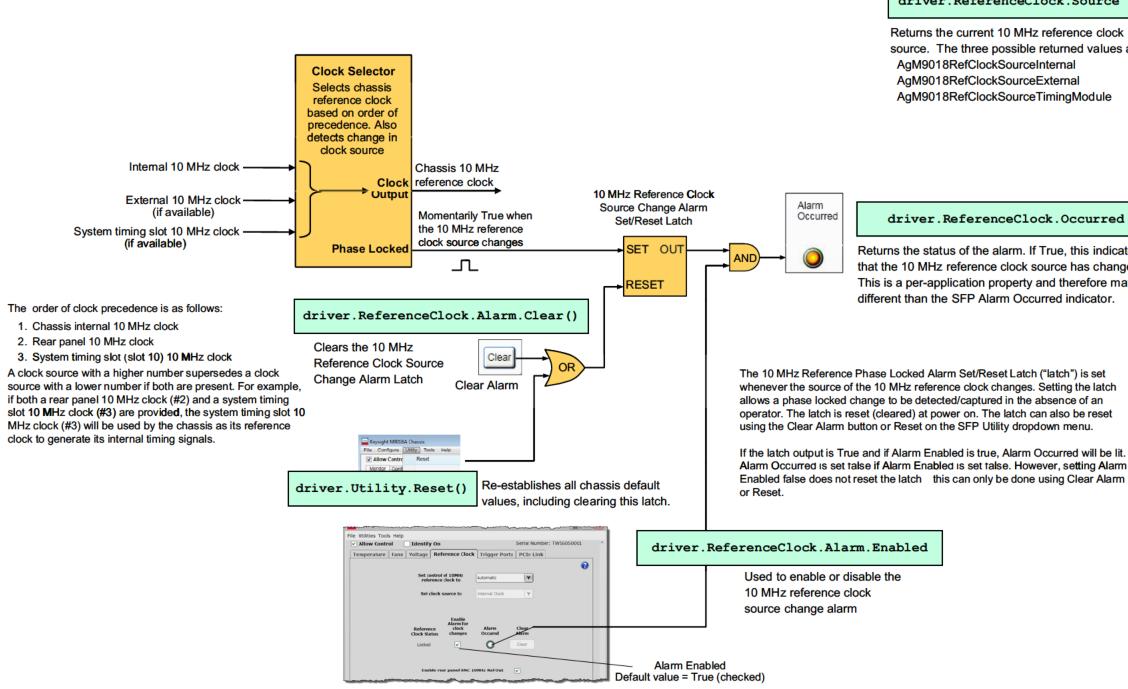

Each alarm has an Alarm Set/Reset Latch ("latch") - please see the figure below for an example of one latch . Each of the eight latches is set if its associated alarm threshold is exceeded. In the case of the fan speed alarm, exceeded means that at least one fan speed is *lower* than the Minimum Fan Speed Alarm Threshold. Similarly, a power supply rail that has exceeded its alarm threshold means that its voltage is outside of the range defined by the upper and lower voltage limits.

Setting of the latches allows alarm conditions to be detected/captured in the absence of an operator. The latch OUT does not have a default value-if the SET input is true (for example, at power-on due to a fan speed being below the default Minimum Fan Speed Threshold of 1200 RPM), the fan alarm latch OUT will be set True at power-on.

Each latch can be reset (cleared) using its associated Clear Alarm button on the SFP. Reset on the SFP Utility dropdown menu will reset all eight latches. However, if any alarm threshold is still exceeded when the latch is reset, the latch will be immediately set true again.

If the latch output is True and if the SFP Alarm Enabled is true, Alarm Occurred will be lit on the SFP. Alarm Occurred is set false if Alarm Enabled is set false. However, setting Alarm Enabled false does not reset the latch-this can only be done using Clear Alarm or Reset. Likewise, changing the corresponding alarm threshold to a value such that the alarm limit is no longer being exceeded does not reset the latch.

#### Interactions between programs using the chassis alarms

It is important to understand how your IVI.NET or IVI-C program interacts with the SFP alarms -- or, for that matter, with any program(s) that use the alarms. Programs that are operating simultaneously need to share certain alarm resources. Each of the eight alarms has one instance of the Set/Reset Latch and each alarm has an OR gate feeding into the latch - these elements represent hardware in the chassis. For discussion purposes, the Fan Speed Alarm Set/Reset Latch will be used as an example. The chassis contains one Fan Speed Alarm Set/Reset Latch, which all processes share.

The elements which provide inputs to the yellow-colored hardware elements are also singular and shared. For example, there is only one Minimum Fan Speed Alarm Threshold. If the threshold is set using the SFP and is then set to a different value using the IVI.NET driver, the last-set threshold will be in effect.

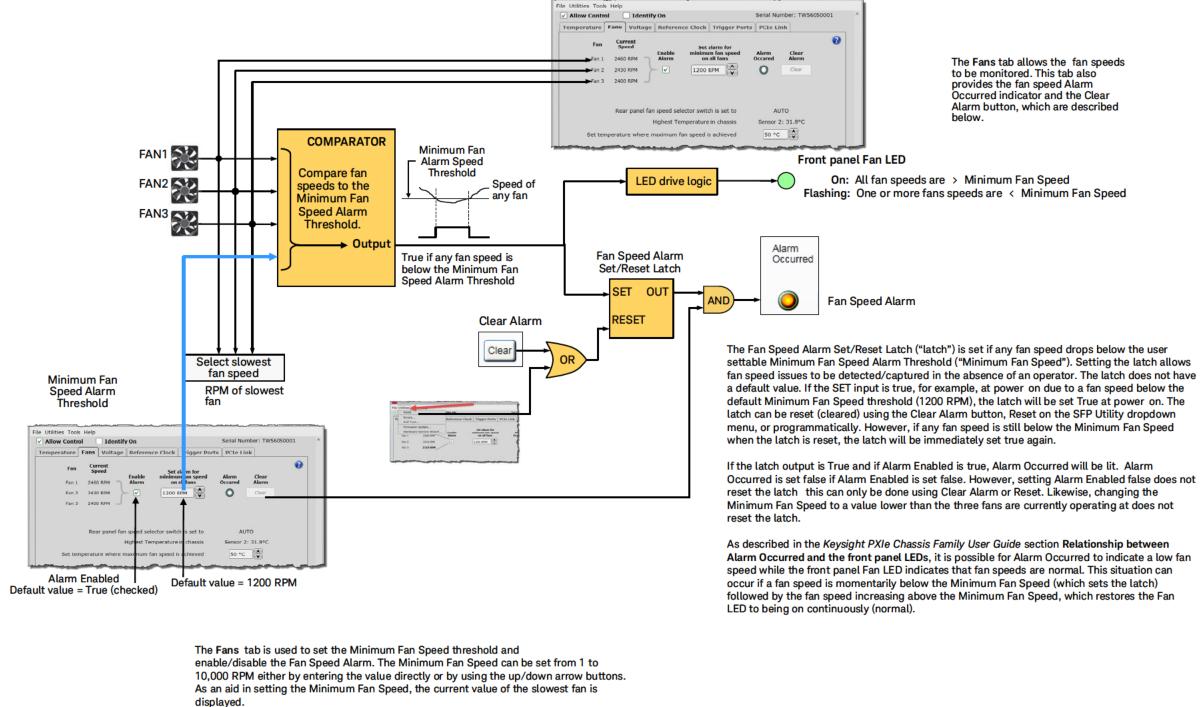

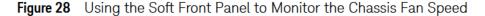

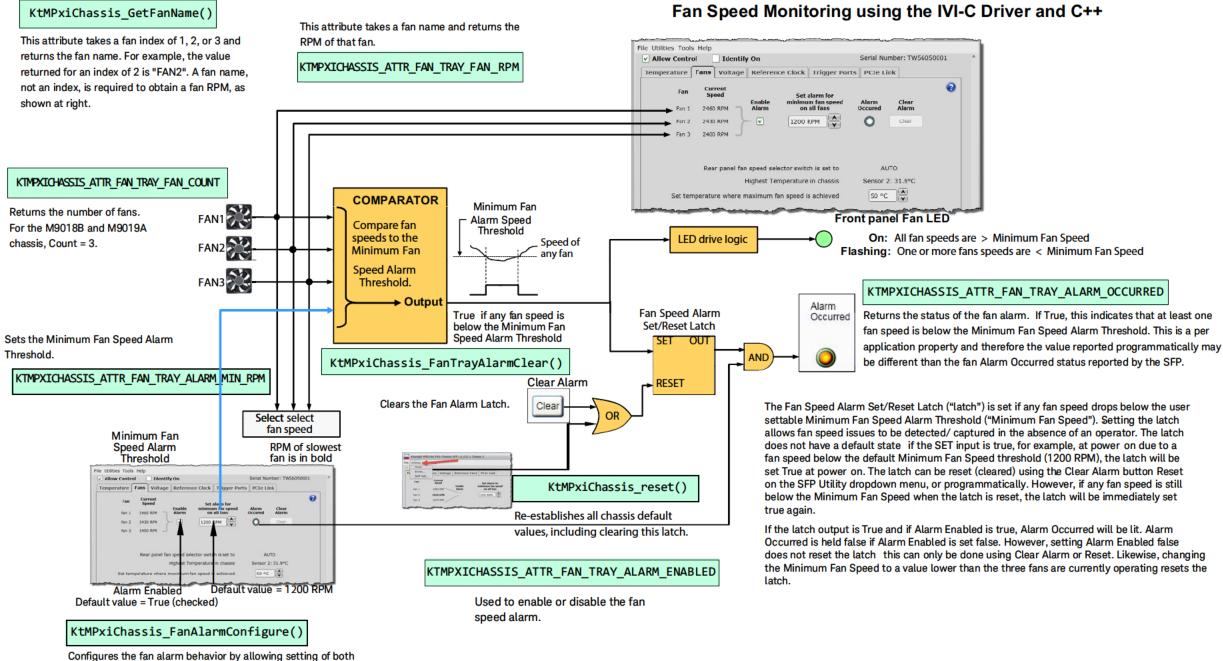

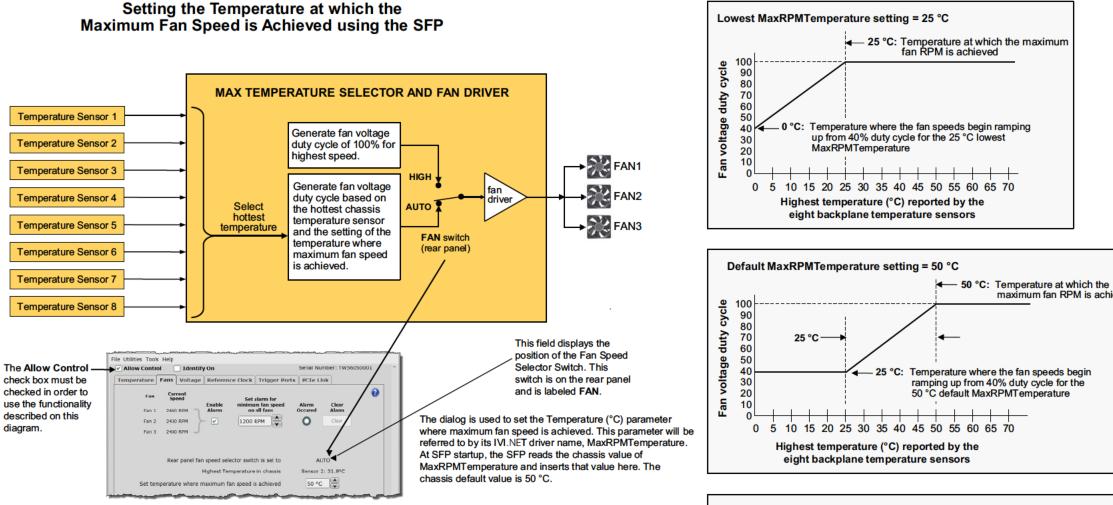

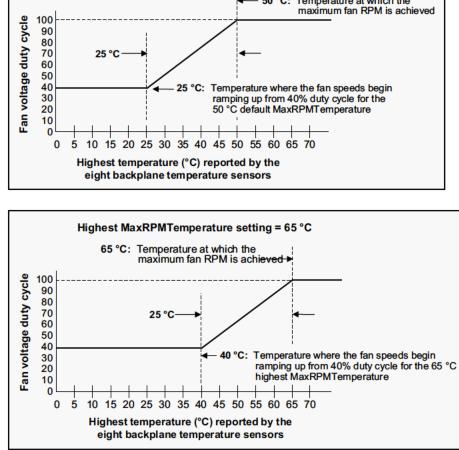

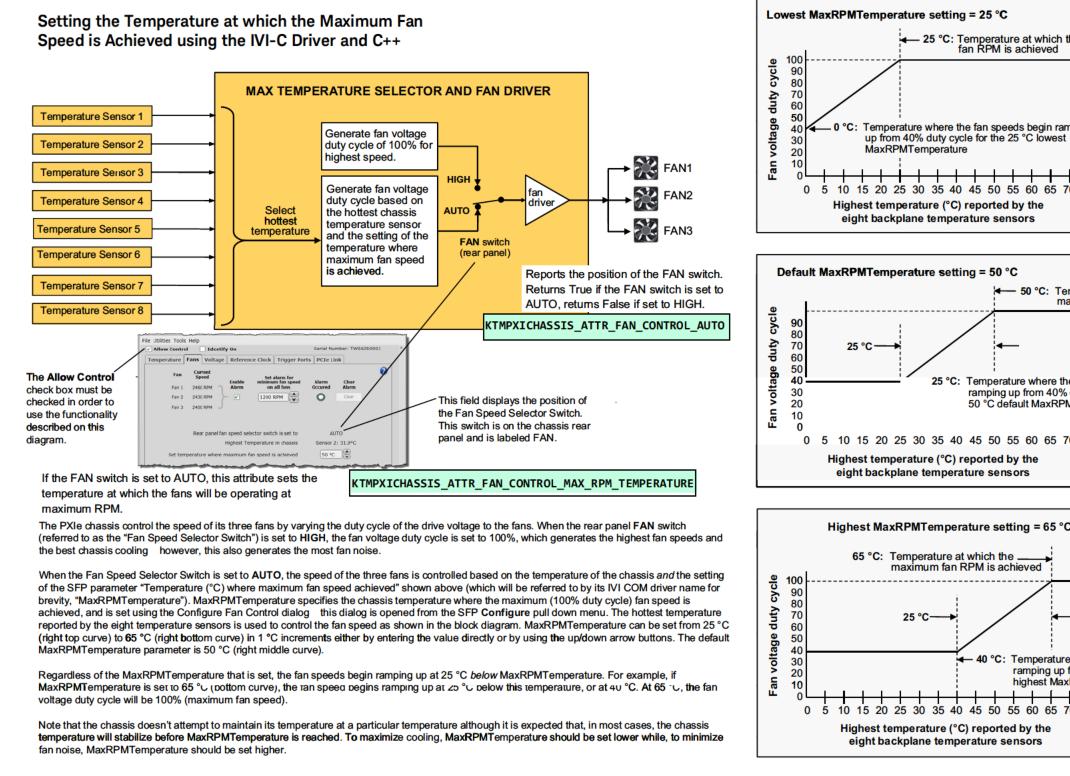

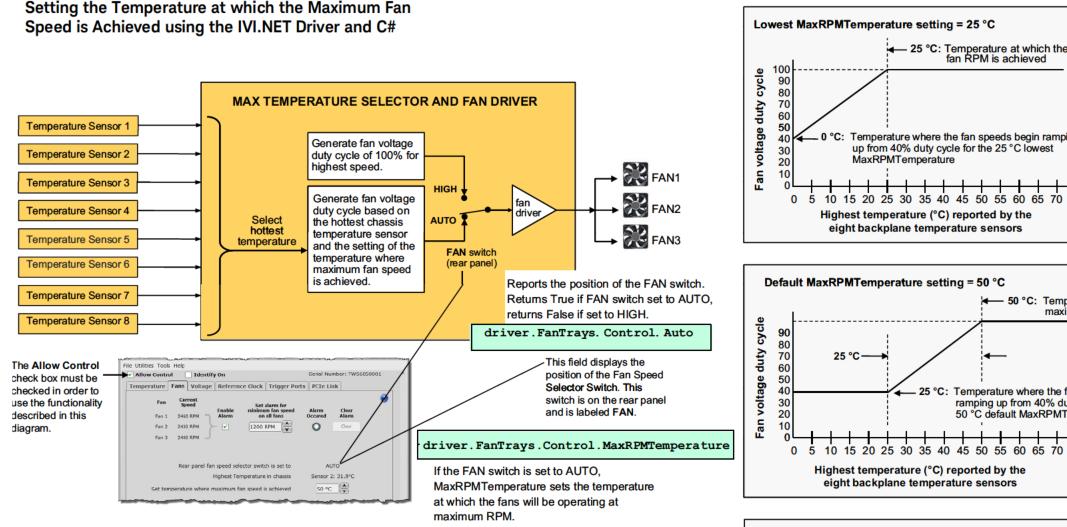

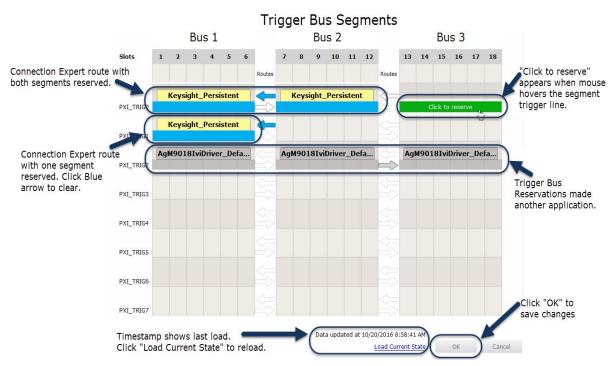

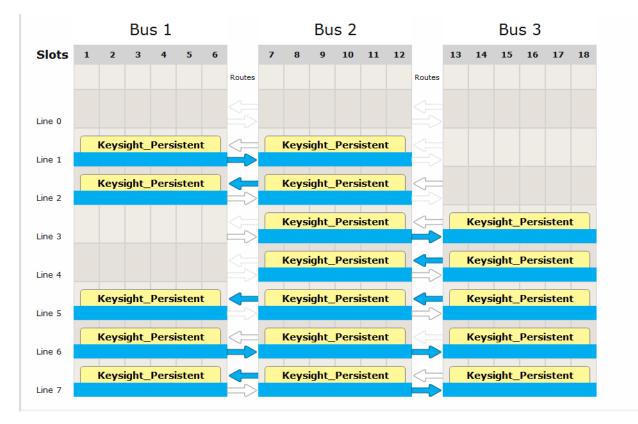

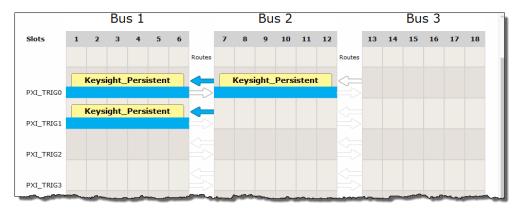

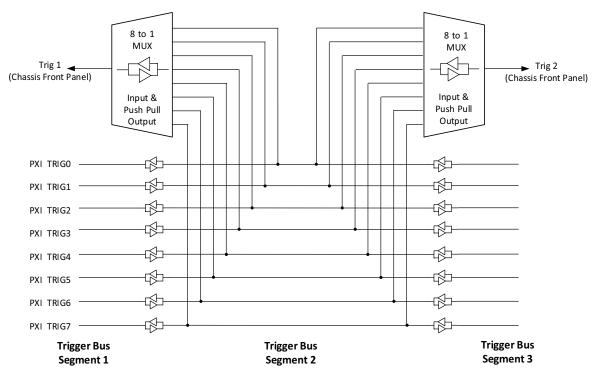

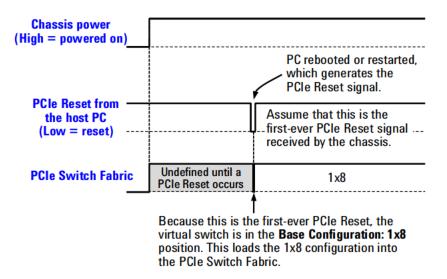

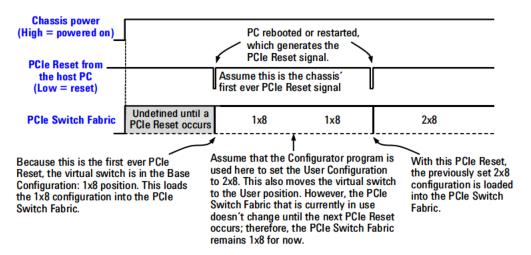

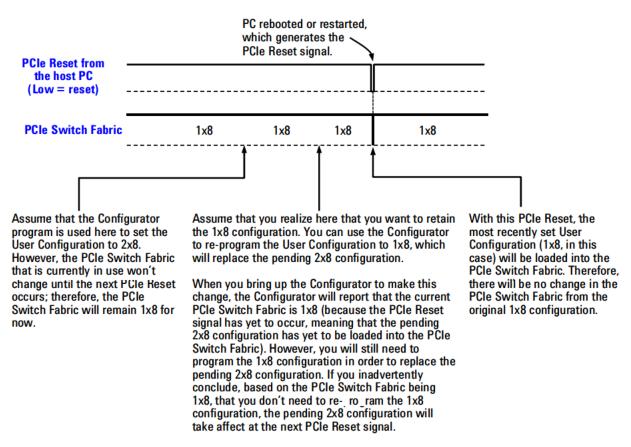

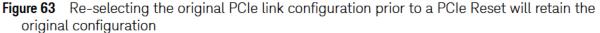

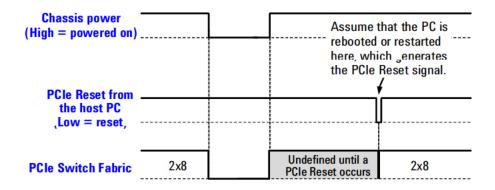

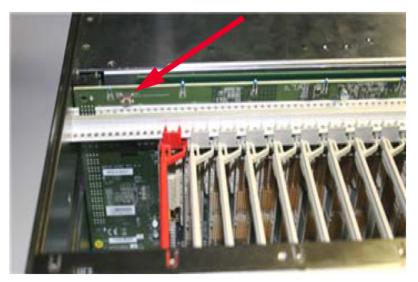

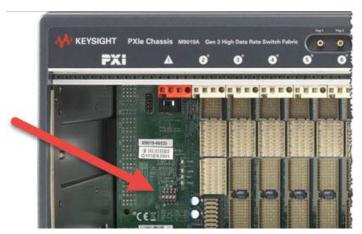

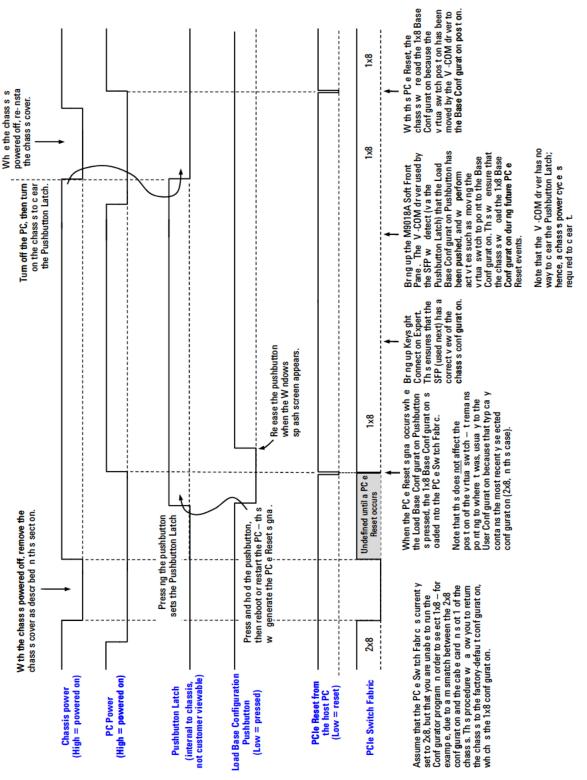

NOTE: To keep the SFP in sync with any changes that have been made programmatically to their shared resources, the SFP polls the relevant chassis parameters and updates its display accordingly. For example, if your program changes the Minimum Fan Speed Alarm Threshold, the new value will be reflected on the SFP Configure Alarms tab (if the SFP is running, of course) within one second. If your application program is running in an environment where the SFP is also running and if chassis parameters are being changed using the SFP, your program can likewise poll the relevant parameters in order to detect if they have been changed by the SFP user.