## このドキュメントについて

このドキュメントは、アジレント・テクノロジー ウェブサイトによって、お客様に製品のサポートをご提供するために公開しております。印刷が判読し難い箇所または古い情報が含まれている場合がございますが、ご容赦いただけますようお願ひいたします。

今後、新しいコピーが入手できた場合には、アジレント・テクノロジー ウェブサイトに追加して参ります。

## 本製品のサポートについて

この製品は、既に販売終了またはサポート終了とさせていただいている製品です。弊社サービスセンターでは、この製品の校正は実施できる可能性があります（修理部品が不要な場合など）が、その他のサポートはご提供いたしかねます。誠に恐縮ではございますが、ご理解願います。

なお、この製品に関するその他の情報や、代替製品情報などは、弊社 電子計測 ウェブサイト <http://www.agilent.co.jp/find/tm> にて、できるだけご提供しておりますので、ご利用ください。

## 訂正のお願い

本文中に「HP」または「YHP」とある語句を、「Agilent」と読み替えてください。

また、「横河・ヒューレット・パッカード株式会社」、「日本ヒューレット・パッカード株式会社」とある語句は、それぞれ、「アジレント・テクノロジー株式会社」と読み替えてください。

ヒューレット・パッカード社の電子計測、自動計測、半導体製品、ライフライフサイエンスのビジネス部門は、1999年11月に分離独立してアジレント・テクノロジー社となりました。

社名変更に伴うお客様の混乱を避けるため、製品番号の前に付されたブランドのみ

HPからAgilent へと変更しております。

(例: 旧製品名 HP 8648は、現在 Agilent 8648として販売いたしております。)

Agilent Technologies

---

## Service Guide

### Agilent Technologies

- **81130A 400/660 MHz Pulse/Pattern Generator Mainframe**

- **81131A 400 MHz, 3.8V Output Frontend**

- **81132A 660 MHz, 2.5V Output Frontend**

### Agilent Technologies

Part No. 81130-91060

Edition E0600

## Contents

### NOTICE

1. Installation

Please refer to ..

Repair Strategy ...

2. Troubleshooting

Please refer to

Initial Tests ...

Power Supply Tests ...

Selftests ...

Test Points

Self Test Messages ...

Register Usage ...

Verify Installation ...

3. Block Diagram / Block Theory

of ...

81101A

81104A                   81105A

81110A                   81111A/81112A

81130A                   81131A/81132A

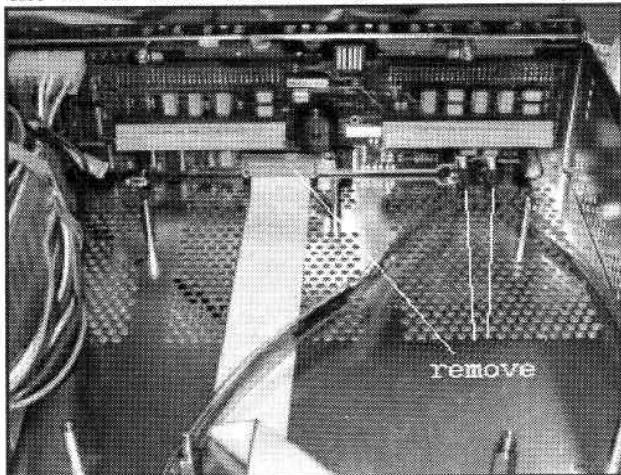

4. Exchanging the Boards

- Warning

- Caution

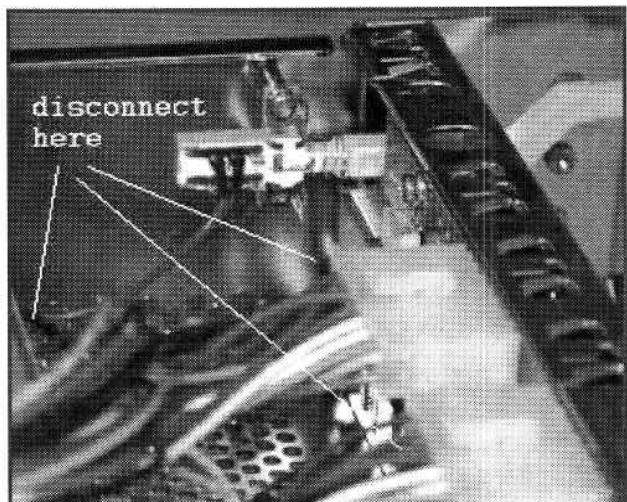

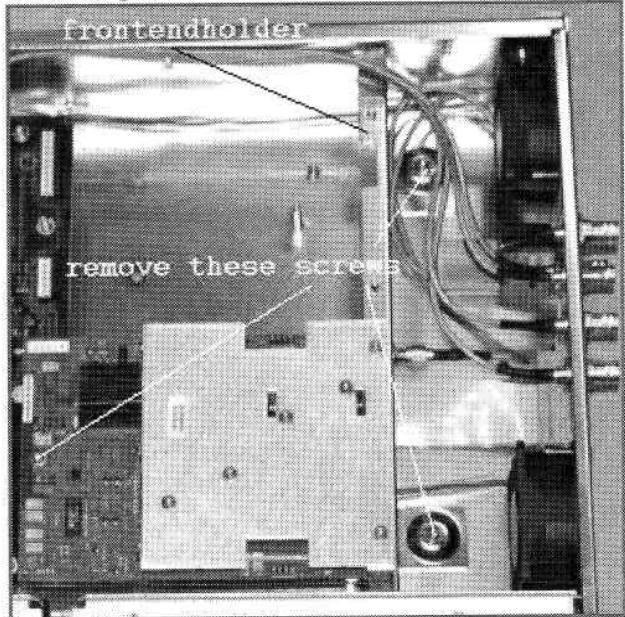

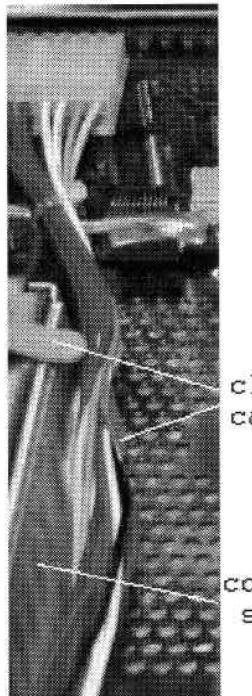

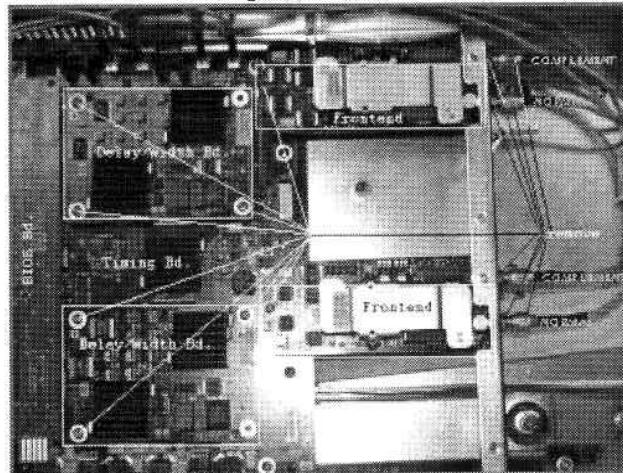

Removing the Boards ...

What to do with the Boards ...

Installing the Boards ...

5. Assembly-level Parts Lists

81101A, 81104A, 81110A and 81130A

Replaceable Assemblies

- List of Exchange Assemblies

- List of Non Exchange Assemblies

Board Exchange Information Sheet

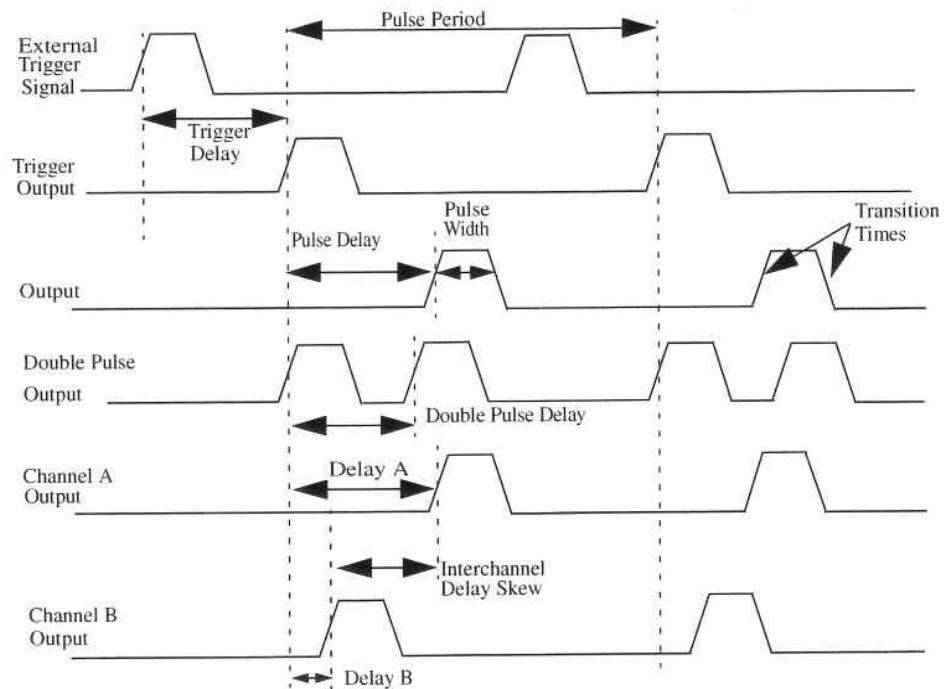

6. Definition of Terms

7. Performance Tests

**NOTICE**

**Copyright**

© 1998 Agilent Technologies 1999, 2000.

Agilent Technologies Deutschland GmbH

Herrenberger Str. 130

71034 Boeblingen

Germany

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies Inc. as governed by United States and international copyright laws.

**Notice**

The material contained in this document is subject to change without notice. Agilent Technologies makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

**Warranty**

This Agilent Technologies product has a warranty against defects in material and workmanship for a period of three years from date of shipment. During the warranty period, Agilent Technologies will, at its option, either repair or replace products that prove to be defective. For warranty service or repair, this product must be returned to a service facility designated by Agilent Technologies. The Buyer shall pay Agilent Technologies round-trip travel expenses. For products returned to Agilent Technologies for warranty service, the Buyer shall prepay shipping charges to Agilent Technologies and Agilent Technologies shall pay shipping charges to return the product to the Buyer. However, the Buyer shall pay all shipping charges, duties and taxes for products returned to Agilent Technologies from another country. Agilent Technologies warrants that its software and firmware designated by Agilent Technologies for use with an instrument will execute its programming instructions when properly installed on that instrument. Agilent Technologies does not warrant that the operation of the instrument software, or firmware, will be uninterrupted or error free.

**Limitation of Warranty**

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of the environmental specifications for the product, or improper site preparation or maintenance. No other warranty is expressed or implied. Agilent Technologies specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

**Exclusive Remedies**

The remedies supplied are the Buyer's sole and exclusive remedies. Agilent Technologies shall not be liable for any direct, indirect, special, incidental, or consequential damages, whether based on contract, tort or any other legal theory.

**Certification**

Agilent Technologies certifies that this product met its published specifications at the time of shipment. Agilent Technologies further certifies that its calibration measurements are traceable to the United States Institute of Standards and Technology, to the extent allowed by the Institute's calibrating facility, and to the calibration facilities of other International Standards Organization members.

#### **Services and Support**

Agilent Technologies provides superior education, consulting, and technical support services.

Product maintenance agreements and other customer assistance agreements are available for Agilent Technologies products on the Web.

Product-specific support information by model number, product category or key term you can find on the Web.

For any assistance, contact your nearest Agilent Technologies Service Office.

#### **Assistance**

Any adjustment, maintenance, or repair of this product must be performed by qualified personnel. Contact your customer engineer through your local Agilent Technologies Service Center. You can find your local T&M service contact on the Web at.

## **Safety Information**

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the instrument. Agilent Technologies Inc. assumes no liability for the customer's failure to comply with these requirements.

#### **General**

This product is a Safety Class 1 instrument (provided with a protective earth terminal). The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

Capacitors inside the instrument may retain a charge even if the instrument is disconnected from its source of supply.

All Light Emitting Diodes (LEDs) used in this product are Class 1 LEDs as per IEC 60825-1.

#### **Environmental Conditions**

This instrument is intended for indoor use in an installation category II, pollution degree 2 environment. It is designed to operate at a maximum relative humidity of 95% and at altitudes of up to 2000 meters. Refer to the specifications tables for the ac mains voltage requirements and ambient operating temperature range.

#### **Before Applying Power**

Verify that the product is set to match the available line voltage, the correct fuse is installed, and all safety precautions are taken. Note the instrument's external markings described under in Safety Symbols1 below.

#### **Ground the Instrument**

To minimize shock hazard, the instrument chassis and cover must be connected to an electrical protective earth ground. The instrument must be connected to the ac power mains through a grounded power cable, with the ground wire firmly connected to an electrical ground (safety ground) at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

#### **Fuses**

Only fuses with the required rated current, voltage, and specified type (normal blow, time delay, etc.) should be used. Do not use repaired fuses or short-circuited fuse holders. To do so could cause a shock or fire hazard.

**Do Not Operate in an Explosive Atmosphere**

Do not operate the instrument in the presence of flammable gases or fumes.

#### **Do Not Remove the Instrument Cover**

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made only by qualified service personnel.

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

**Safety Symbols**

Caution (refer to accompanying documents)

Protected conductor symbol.

In the manuals:

**WARNING**

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in personal injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

**CAUTION**

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, or the like, which, if not correctly performed or adhered to could result in damage to or destruction of part or all of the product. not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

## Installation

---

Please refer to the Quick Start Guide and the Reference Guide

see Manuals

---

### Using the Instrument..

Please refer to the Quick Start Guide and the Reference Guide

see Manuals

### Repair Strategy...

Repair by exchange Boards/Assies is provided for the

Agilent 81100 Pulse/Pattern Generator Family.

These Boards/Assies are not repairable in the field and

the Assy Exchange Program is used!

Exchange Part is the complete Board/Assy.

Serial Numbers (Mainframe and Channels) stays with the customer.

Please refer to Chapter 4, Exchanging the Modules

and Chapter 5, Assembly-level Parts List

## Troubleshooting

Please refer to the model's Reference Guide,

p/n **811xx-91021**

for more information on Warnings and Errors.

In addition refer to Section,

```

|CONFIG| Screen - Selftest

Chapter 2 - Programming Reference

- :SYST:ERR?

- :SYST:WARN?

- :SYST:WARN:STR?

- :SYST:WARN:BUFF?

```

### Initial Tests ...

There could be a number of reasons why the instrument shows no signs of operation. If the instrument appears to be dead, proceed as indicated below.

Connect the AC Line Power Cord to the instrument's rear main power inlet.

Switch the Power Switch to **ON**

If the display is 'working', proceed with Selftests.

If the display stays dark, do the following

PRELIMINARY CHECKS

```

|

* Is AC Line Power available?

->   N      Provide AC Line Power!

|

Y

|

* Is AC Line properly connected?

->   N      Connect AC Line Power!

|

Y

|

* Is AC Line Fuse OK?

->   N      Change AC Line Fuse!

|

Y

|

* Is the Display 'working' now? FANs running?

->   N      Proceed Power Supply Tests

|

Y

|

* Proceed with Selftests

```

### Power Supply Tests ...

There are three fans on the rear of the unit. Are they running?

The **Power Supply Module** do have a fan of it's own.

Check if this fan is running!

If not, follow the procedure to open the unit

in Chapter Exchanging the Boards.

The two cable sets (A, B) coming out of the power supply module are connected to the Mother/CPU Bd. and to the left and right of the connectors A, B there are Test Points to measure the voltages!

## Power Supply Voltages

| output voltage | variations       |

|----------------|------------------|

| +5 V           | +.25 V / -.125 V |

| +5 VA          | +.5 V / -.3 V    |

| +12 V          | +.6 V / -.36 V   |

| -12 V          | -.6 V / +.36 V   |

| -5.2 V         | -.26 V / +.156 V |

| -2 V           | -.1 V / +.1 V    |

| +24 V          | +1.2 V / -.72 V  |

## Selftests ...

The **Power-Up Selftest** runs the following tests:

- Interface

- uProcessor

- ROM

- RAM

- Modules

- uP Selftest Failure Messages -

- Module Selftest Failure Messages -

If this test fails you can press the HELP key to see a list of the specific error messages resulting from the test. If the list is longer than the single screen, use the cursor key

Note that a long error list can result from a single initial

Note that a long error list can result from a single initial error. Therefore, begin to solve problems starting with the first

Therefore, begin to solve problems starting with the first message in the list and after the problem is cleared run the Selftest again.

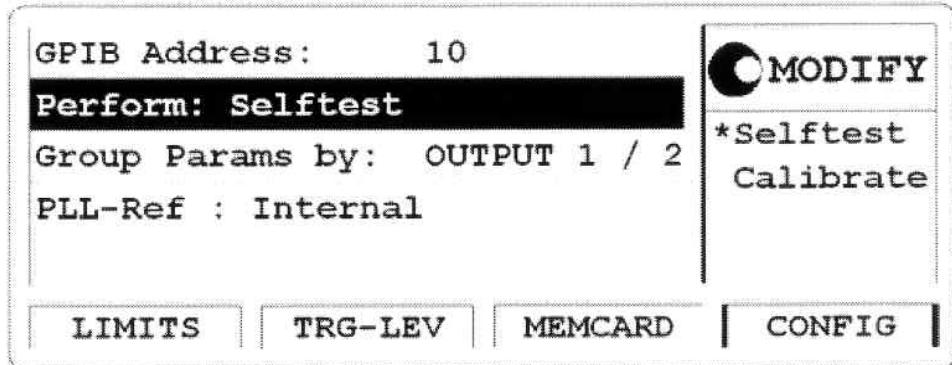

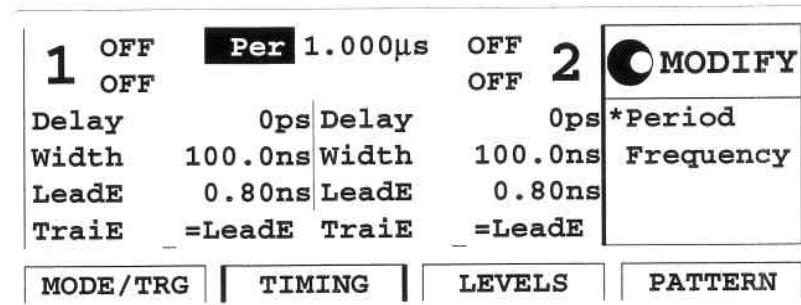

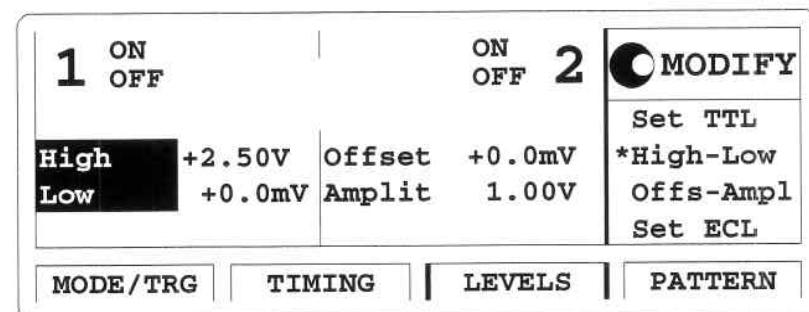

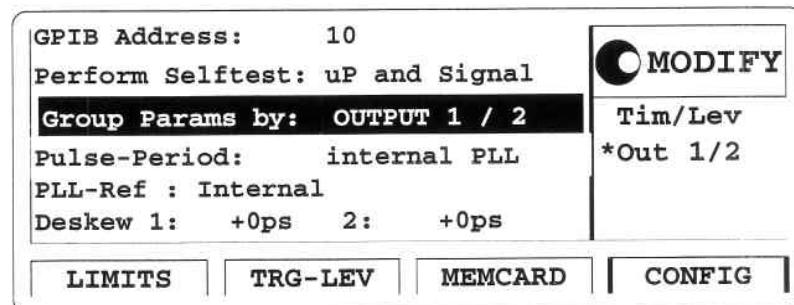

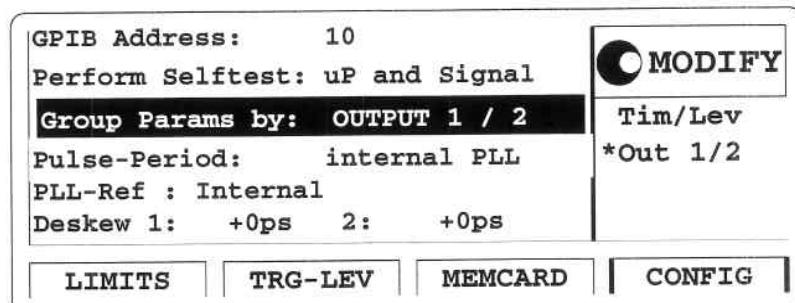

The 81100 Family has an **additional built-in selftest**. From the initial setup of the 811xxA select MORE |CONFIG| screen and set up as follows:

Above is the CONFIG screen of the 81110A.

(The 81101A/81104A screen do not show the capability to

Calibrate the unit.)

(The 81101A screen do not show the capability to

Group Params by: OUTPUT)

Press **ENTER** and wait till the Selftest ends.

In this test some additional tests to the above shown tests are done!

If the Selftest fails, a flashing **E** is displayed. Press **HELP** to see the list of error messages.

Together with the Performance Test and the Applications info a confidence level of >96% can be assumed. This is because not all possible settings and functions could be done and checked.

For every error message there are troubleshooting tips given in this chapter. If none of these hints may help, there might be a problem with address decoding or the data bus drivers.

After a problem is cleared run *Selftest* again.

The unit tests the following components in the listed order:

1. comparator of clock input

2. comparator of external input

3. PLL

4. period divider of FPGA on Timing Board (\*)

5. data-in register of TIGER-ICs

- (6. pattern memory)

7. strobe out

8. trigger out

9. Frontends

10. VCOs of TIGER-ICs

(\*) Test #4 is not done during power up.

The following block schematic shows the

#### Test Points

of the above listed tests.

There are several possible causes for a failed test. A faulty element may produce a long error list. In the following, there is a list of some components, that affect different tests at the same time:

| faulty components        | affected tests                                                                |

|--------------------------|-------------------------------------------------------------------------------|

| ADC circuit              | Clock In, Ext. In, PLL, Strobe Out, Trigger Out, Low/High Level               |

| Threshold DAC            | Clock In, Ext. In                                                             |

| Clock Input circuit      | Clock In, Strobe Out                                                          |

| PLL circuit              | PLL, Period Divider                                                           |

| Period TIGER IC          | Period TIGER, Pattern RAM, Strobe Out, Trigger Out, Low/High Level, VCOs      |

| Delay/Width TIGER IC     | Delay TIGER, Width TIGER, Low/High Level, VCOs                                |

| Period FPGA(Timing Brd.) | VCOs                                                                          |

| Hardware register 0      | Clock In, Ext. In, PLL, Strobe Out, Trigger Out, Low/High Level               |

| Hardware register 1      | Clock In, Ext. In, Pattern RAM, Strobe Out, Trigger Out, Low/High Level, VCOs |

| Hardware register 2      | Strobe Out, Trigger Out                                                       |

| Hardware register 3      | Strobe Out, Trigger Out, Low/High Level, VCOs                                 |

| Hardware register 4      | Clock In, Ext. In, Period Divider                                             |

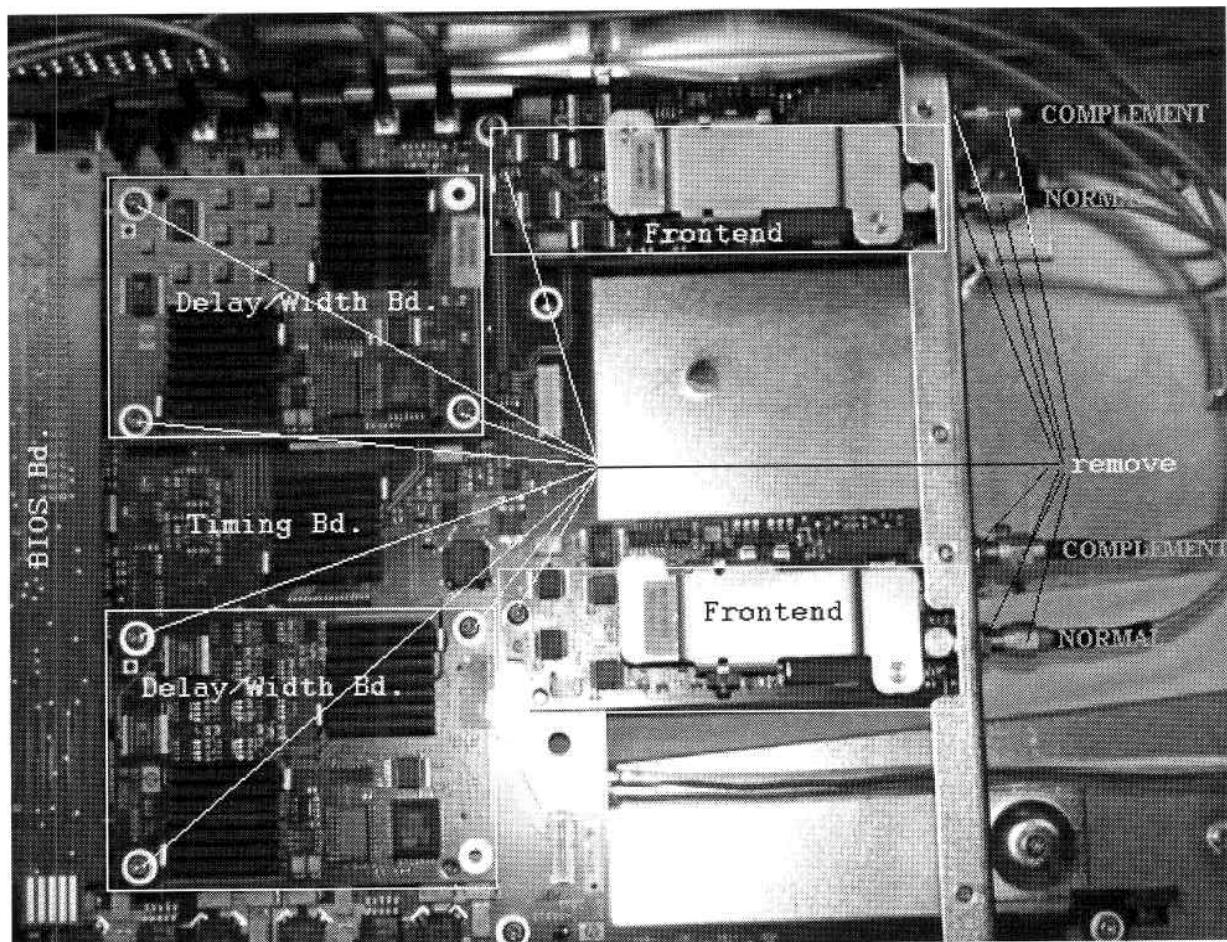

#### Replacing Boards

Before replacing any board, make sure that the unit is calibrated properly and check the Power Supply.

If there are error messages concerning different boards, begin with the first error and try to fix it with the tips given in 'Error Description' and look in the above table.

#### Replacing Timing Board

Replace Timing Board, if only some of the following components fail:

Clock Input comparator, External Input comparator, PLL, Period divider, Period TIGER IC, Pattern RAM, Strobe Out, Trigger Out, VCO 0 or 1

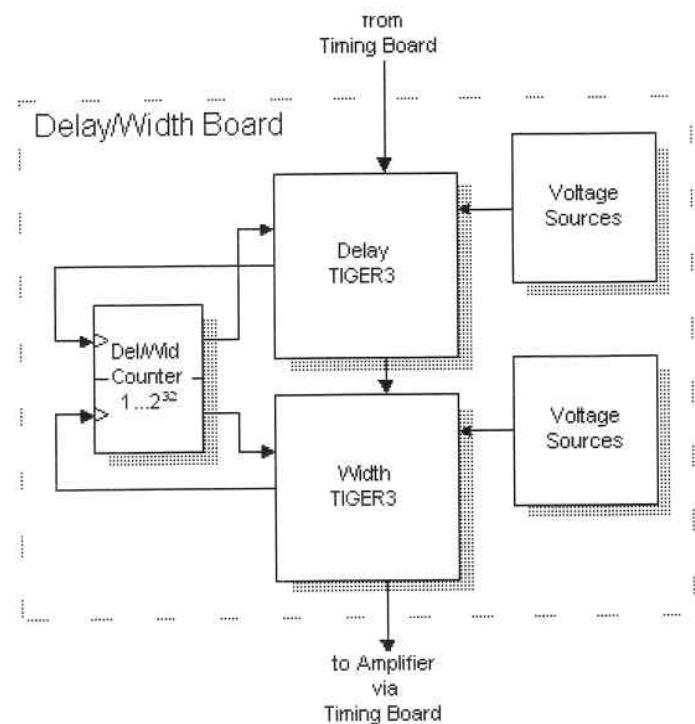

Replacing Delay-Width Board

Replace Delay-Width Board of the channel displayed in the error message, if only some of the following components fail:

Delay TIGER, Width TIGER, VCO  $\geq 2$

A Delay-Width Board should only be replaced together with its corresponding Frontend Board.

Replacing Frontend Board

Replace Frontend Board of the channel displayed in the error message, if only the following tests fail:

Low/High Level

A Frontend Board should only be replaced together with its corresponding Delay-Width Board.

For replacing boards, follow the procedure in Chapter Exchanging the Boards.

### **Self Test Messages ...**

A complete list of all Self Test Messages can be found [here](#).

### **Register Usage ...**

The 81100 Firmware uses the Standard Event Status, Operation Status, and Questionable Status registers for reporting instrument status, in accordance with the SCPI standard. The following lists the bits used in each register, and what they are used for:

Register:            STANDARD EVENT STATUS REGISTER        Bit: 7

This bit is set every time the instrument is powered on.

Register:            STANDARD EVENT STATUS REGISTER        Bit: 0

This bit is set in response to the \*OPC command

Register:            OPERATION STATUS REGISTER        Bit: 1

This condition is set whenever the instrument starts changing its output signals.

Register:            OPERATION STATUS REGISTER        Bit: 1

This condition is cleared whenever the instrument has finished changing its output signals, the external signals are stable now.

Register:            OPERATION STATUS REGISTER        Bit: 2

This condition is set whenever the instrument starts changing its range.

Register:            OPERATION STATUS REGISTER        Bit: 2

This condition is cleared whenever the instrument has finished changing its range, the external signals are stable now.

Register:            OPERATION STATUS REGISTER        Bit: 4

This condition is set whenever the instrument starts a frequency measurement.

Register:            OPERATION STATUS REGISTER        Bit: 4

This condition is cleared whenever the instrument has finished a frequency measurement, the measurement result can be obtained now.

Register:            QUESTIONABLE STATUS REGISTER        Bit: 0

Set/clear the QUESTIONable STATus bit for VOLtage.

Register:            QUESTIONABLE STATUS REGISTER            Bit: 1

Set/clear the QUESTIONable STATus bit for CURRent.

Register:            QUESTIONABLE STATUS REGISTER            Bit: 2

Set/clear the QUESTIONable STATus bit for TIME.

Register:            QUESTIONABLE STATUS REGISTER            Bit: 5

Set/clear the QUESTIONable STATus bit for VOLTage.

---

**Verify Installation ...**

After replacing a board do a complete Performance Test

(and follow the Applications info) to make sure the unit

is working within specification (with all features).

## Troubleshooting

---

### Self Test Messages ...

Possible self test messages are:

- Microprocessor Selftest Failure Messages -

GPIB: **-330, Self-test failed;**

**Selftest error: Microprocessor board failed**

Local: **Selftest error: Microproc. board failed**

Hardware on the (Firmware-)uProcessorboard doesn't work.

GPIB: **-330, Self-test failed;**

**ROM test failed**

Local: **ROM test failed**

Flash Eeprom's test failed on (Firmware-)uProcessorboard

GPIB: **-330, Self-test failed;**

**RAM test failed**

Local: **RAM test failed**

Static RAM's test failed on (Firmware-)uProcessorboard

GPIB: **-330, Self-test failed;**

**Crystal Reference for uP lost**

Local: **Crystal Reference for uP lost**

A loss of crystal reference has been detected and the VCO is running at approximately half of maximum speed, determined from an internal voltage reference.

Normally the external crystal frequency is VCO reference.

GPIB: **-330, Self-test failed;**

**VCO for uP has not locked**

Local: **VCO for uP has not locked**

VCO is enabled, but has not yet locked. Normally VCO has locked on to the desired frequency.

GPIB: **-330, Self-test failed;**

**Unexpected Reset of uP**

Local: **Unexpected Reset of uP**

The reset was caused by

- the powerup reset circuit

- the software watchdog circuit

- the system protection submodule halt monitor

- a loss of frequency reference to the clock submodule

- the test submodule

Normally the last reset was caused by an external signal or by the CPU executing a reset instruction.

GPIB: **-330, Self-test failed;**

**Internal Serial Device Bus failed**

Local: **Internal Serial Device Bus failed**

Internal serial device bus traffic over feedback path has failed.

- Module Selftest Failure Messages -

**Clock Input comparator test failed**

The test of the clock input comparator failed.

Possible cause:

External clock input connected to signal source.

Voltage comparator out of order

Hardware registers 0, 1 and/or 4 out of order

Threshold DAC out of order

ADC circuit not working correctly

Description of this test:

The impedance of the clock input is set to 50 Ohm.

Comparator is enabled.

Threshold is set to its minimum (0x0000).

It is checked, if the measured signal is equal to a logical '0'. (V\_ADC value is smaller than 1470.)

Threshold is set to its maximum (0x0FFF).

It is checked, if the measured signal is equal to a logical '1'. (V\_ADC value is greater than 1470.)

Troubleshooting:

Make sure, that nothing is connected to clock input.

Check impedance of clock input.

(Hardware register 1 may also be faulty.)

Check whether clock input comparator is enabled.

(Hardware register 4 may also be faulty.)

Check threshold.

Check comparator output.

Check V\_ADC value.

(Hardware register 0 may also be faulty.)

**Ext. Input comparator test failed**

The test of the external input comparator failed.

Possible cause:

External input connected to signal source.

Voltage comparator out of order

Hardware registers 0, 1 and/or 4 out of order

Threshold DAC out of order

ADC circuit not working correctly

Description of this test:

The impedance of the external input is set to 50 Ohm.

Comparator is enabled.

Threshold is set to its minimum (0x0000).

It is checked, if the measured signal is equal to a logical '0'. (V\_ADC value is smaller than 1470.)

Threshold is set to its maximum (0x0FFF).

It is checked, if the measured signal is equal to a logical '1'. (V\_ADC value is greater than 1470.)

Troubleshooting:

Make sure, that nothing is connected to external input.

Check impedance of external input.

(Hardware register 1 may also be faulty.)

Check whether external input comparator is enabled.

(Hardware register 4 may also be faulty.)

Check whether external input comparator is enabled.

Check threshold.

Check comparator output.

Check V\_ADC value.(Hardware register 0 may also be faulty.)

**PLL test (internal xxxx MHz) failed**

The test of the PLL failed at the displayed internal PLL frequency (250 Mhz, 333 MHz, 500 MHz, 666 MHz, 1000 MHz).

Possible cause:

PLL IC out of order

VCO of PLL out of order

Missing internal reference frequency

Hardware register 0 out of order

ADC circuit not working correctly

Description of this test:

VCO of PLL is switched on, if it isn't already on.

Internal referencefrequency is selected.

PLL frequency is set to 250 MHz

(below itsminimum of 333 MHz).

It is checked,

if signal PLL\_LOW has its maximum level

(V\_ADC value > 1210) and

signal PLL\_HIGH has its maximum level

(V\_ADC value > 3180).

PLL frequency is set to its minimum of 333 MHz.

It is checked,

if signal PLL\_LOW has its minimum level

(V\_ADC value < 1210) and

signal PLL\_HIGH has its maximum level

(V\_ADC value > 3180).

```

PLL frequency is set to 500 MHz

(between its minimum of 333 MHz and maximum of 666 MHz).

It is checked,

if signal PLL_LOW has its minimum level

(V_ADC value < 1210) and

signal PLL_HIGH has its maximum level

(V_ADC value > 3180).

PLL frequency is set to its maximum of 666 MHz.

It is checked,

if signal PLL_LOW has its minimum level

(V_ADC value < 1210) and

signal PLL_HIGH has its maximum level

(V_ADC value > 3180).

PLL frequency is set to 1000 MHz,

beyond its maximum of 666 MHz.

It is checked,

if signal PLL_LOW has its minimum level

(V_ADC value < 1210) and

signal PLL_HIGH has its minimum level

(V_ADC value < 3180).

VCO of PLL is switched off, if it was off before

this selftest.

```

**Troubleshooting:**

```

Check internal reference frequency (10 Mhz).

(Hardware register 0 may also be faulty.)

Check PLL IC.

(Hardware register 0 may also be faulty.)

Check VCO of PLL.

(Hardware register 0 may also be faulty.)

Check signals PLL_LOW and PLL_HIGH.

Check V_ADC value.

(Hardware register 0 may also be faulty.)

```

**Period divider test failed**

The test of the period divider in the FPGA on the timing board failed.

Possible cause:

```

Counter 2 in FPGA out of order

MCLK divider out of order

PLL out of order

Hardware register 4 out of order

```

**Description of this test:**

```

VCO of PLL is switched on, if it isn't already on.

PLL frequency is set to 500 MHz.

MCLK divider factor is set to 64.

Counter mode of FPGA is enabled, counter 2 is used

as master for measurement.

A preset value of 0xFFFFFFFF is loaded for counter 2

and a reset for this counter is done.

Counting is started. ('start_count' bit is set.)

After 0.5 sec counting is stopped by disabling MCLK

divider.

It is checked, if the current contents of counter 2

is between 0xFF000000 and 0xFFFF0000.

MCLK divider is enabled and 'start_count' bit is unset.

The old preset value of counter 2 is reloaded and a

reset for this counter is done.

VCO of PLL is switched off, if it was off before this

selftest.

```

**Troubleshooting:**

```

If PLL test has failed before, go back to

troubleshooting for PLL.

Make sure, that the frequency at input of MCLK Divider

is 500 MHz and at output of MCLK Divider approximately

500 MHz / 64 = 7.8125 MHz.

```

**Period TIGER IC test failed**

**Delay TIGER IC test failed (ch. x)**

**Width TIGER IC test failed (ch. x)**

The test of the DATAIN-shift-register on the

Period/Delay/Width TIGER IC (channel x) failed.

Possible cause:

```

TIGER IC out of order

```

**Description of this test:**

The shift-in-register of the Period TIGER IC is tested first, if a delay-width board is available, the shift in register of the Delay and the Width TIGER ICs are checked afterwards.

Testing is done by comparing the shifted in value (0xA5A) with the read out value.

**Pattern RAM test failed**

The test of the pattern RAM failed.

**Possible cause:**

Pattern RAM out of order

Period TIGER IC out of order

Hardware register 1 out of order

**Description of this test:**

Period TIGER IC is enabled to access pattern RAM.

(Every read or write access to the RAM generates a clock edge which increments the burst counter. The burst counter generates the address signal for the RAM.)

Period TIGER IC is reseted.

Correct burst mode is selected.

Burst counter in TIGER IC is loaded with its maximum value.

Pattern RAM access is enabled.

The following data is written into RAM periodically

(all addresses are tested):

0x26, 0x6E, 0xA7, 0xEF, 0x30, 0x70, 0xB8, 0xF1, 0x09, 0x02,

0x4A, 0x83, 0xCB, 0x14, 0x5C, 0x95, 0xDD

Pattern RAM access is disabled.

Period TIGER IC is reseted.

Burst counter in TIGER IC is loaded with its maximum value.

Pattern RAM access is enabled.

Data is read from RAM and compared with the value written in before.

Pattern RAM access is disabled.

Period TIGER IC is disabled to access pattern RAM.

Period TIGER IC is reseted.

**Troubleshooting:**

Check whether pattern RAM is enabled and disabled.

(Hardware register 1 may also be faulty.)

Check whether addresses are changing.

Check Period TIGER IC.

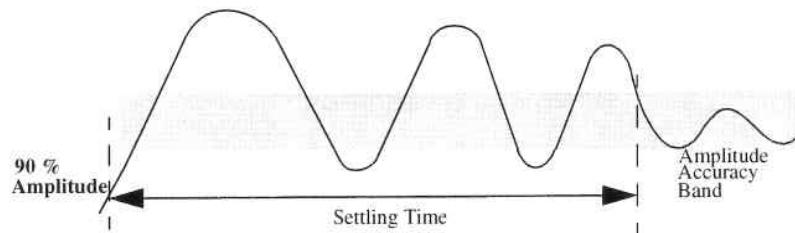

**Trigger and strobe Levels****Test Limits:**

| level mode | value | into 50 Ohm |             | into open   |             |

|------------|-------|-------------|-------------|-------------|-------------|

|            |       | lower limit | upper limit | lower limit | upper limit |

| TTL-LOW    | 0V    | -0.2V       | 0.5V        | -0.4V       | 1.0V        |

| TTL-HIGH   | 2.5V  | 2.1V        | 2.7V        | 4.2V        | 5.4V        |

| ECL-LOW    | -1.8V | -1.9V       | -1.5V       | -3.0V       | -2.0V       |

| ECL-HIGH   | -0.8V | -0.95V      | -0.7V       | -1.9V       | -1.4V       |

| CASS-LOW   | -1V   | -1.2V       | -0.8V       | -2.4V       | -1.6V       |

| CASS-HIGH  | 0V    | -0.2V       | 0.2         | -0.4V       | 0.4V        |

**Strobe Out test failed (TTL low)****Strobe Out test failed (TTL high)****Strobe Out test failed (ECL low)****Strobe Out test failed (ECL high)**

The test of the strobe out signal at the level given in brackets failed.

**Possible cause:**

Strobe output circuit out of order

Hardware register 0, 1, 2 and/or 3 out of order

Period TIGER IC not working

Clock input circuit not working

ADC circuit not working correctly

**Description of this test:**

Clock input impedance is set to 50 Ohm.

Clock input is enabled.

Period TIGER IC is set into reset.

uP trigger event is cleared.

Period TIGER IC is set into this mode:

clock source: External Clock

```

clock mode: Continuous

pulse type: Burst

trigger source: TRIGIN (uP)

clock edge: positive

arm edge: positive

formatter mode: RZ

burst length: 2

Reset of Period TIGER IC is released.

uP trigger event is set.

TTL mode is set.

A positive edge is generated by changing the

clock-in-threshold from 0x0000 to 0xFFFF.

(After setting 0x0000, there is a wait cycle

of 10.0 ms; after setting 0xFFFF, there is a wait

cycle of 1.0 ms.)

It is checked, if TTL high level is

see Test Limits

A positive edge is generated by changing the

clock-in-threshold from 0x0000 to 0xFFFF.

(After setting 0x0000, there is a wait cycle

of 1.0 ms; after setting 0xFFFF, there is a wait

cycle of 1.0 ms.)

It is checked, if TTL low level is

see Test Limits

ECL mode is set.

A positive edge is generated by changing the

clock-in-threshold from 0x0000 to 0xFFFF.

(After setting 0x0000, there is a wait cycle of 100.0 ms;

after setting 0xFFFF, there is a wait cycle of 1.0 ms.)

It is checked, if ECL high level is

see Test Limits

A positive edge is generated by changing the

clock-in-threshold from 0x0000 to 0xFFFF.

(After setting 0x0000, there is a wait cycle of 1.0 ms;

after setting 0xFFFF, there is a wait cycle of 1.0 ms.)

It is checked, if ECL low level is

see Test Limits

```

## Troubleshooting:

```

If clock input test has failed before, go back to

troubleshooting for clock input.

If only TTL errors or only ECL errors occur, check whether

TTL-ECL switch is working.

(Hardware register 2 may also be faulty.)

Check whether signal TRIGOUT_N is low (high) and TRIGOUT_C

is high (low) for low (high) level at strobe output

connector.

Check hardware register 3 for uP trigger event

(Signals UPTRIGN, UPTRIGC).

Check Period TIGER IC.

Check V_ADC value.

(Hardware register 0 may also be faulty.)

```

```

Trigger Out test failed (TTL low)

Trigger Out test failed (TTL high)

Trigger Out test failed (ECL low)

Trigger Out test failed (ECL high)

```

The test of the trigger out signal at the level given in

brackets failed.

## Possible cause:

```

Trigger output circuit out of order

Hardware register 0, 1, 2 and/or 3 out of order

External width mode of Period TIGER IC not working

ADC circuit not working correctly

```

## Description of this test:

```

Before starting this selftest, the TIGER ICs must be set

to external width mode.

TTL mode is set.

uP trigger event is cleared.

(There is a wait cycle of 100.0 ms afterwards.)

It is checked, if TTL low level is

see Test Limits

uP trigger event is set.

(There is a wait cycle of 1.0 ms afterwards.)

It is checked, if TTL high level is

see Test Limits

```

ECL mode is set.

uP trigger event is cleared.

(There is a wait cycle of 100.0 ms afterwards.)

It is checked, if ECL low level is

see Test Limits

uP trigger event is set.

(There is a wait cycle of 1.0 ms afterwards.)

It is checked, if ECL high level is

see Test Limits

Troubleshooting:

If only TTL errors or only ECL errors occur, check

whether TTL-ECL switch is working.

(Hardware register 2 may also be faulty.)

Check whether signal TRIGOUT\_N is low (high) and

TRIGOUT\_C is high (low) for low (high) level at strobe

output connector.

Check hardware register 3 for uP trigger event

(Signals UPTRIGN, UPTRIGC).

Check Period TIGER IC.

Check V\_ADC value.

(Hardware register 0 may also be faulty.)

**Low Lev error (no offs, xx ohm, ch. x)**

**High Lev error (no offs, xx ohm, ch. x)**

The test of the low/high level without offset and a source

impedance of xx ohm on Frontend (channel x) failed.

Possible cause:

Frontend out of order

Wrong calibration of Frontend

Hardware register 0, 1 and/or 3 out of order

External width mode of Period, Delay or Width

TIGER ICs not working

ADC circuit not working correctly

**Low Lev error(pos offs, xx ohm, ch. x)**

**High Lev error (pos offs, xx ohm, ch. x)**

**Low Lev error (neg offs, xx ohm, ch. x)**

**High Lev error (neg offs, xx ohm, ch. x)**

The test of the low/high level with positive/negative offset

and a source impedance of xx ohm on Frontend (channel x) failed.

Possible cause:

Frontend offset amplifier out of order

Frontend out of order

Wrong calibration of Frontend

Hardware register 0, 1 and/or 3 out of order

External width mode of Period, Delay or Width TIGER ICs

not working

ADC circuit not working correctly

Description of this test:

Before starting this selftest, the TIGER ICs must be set to

external width mode.

Depending on the channels being available, the Frontends

are tested according to their specific characteristics.

For every Frontend type the following procedures are done:

Parameters are set to measure high and low

level (offset = 0 V).

uP trigger event is cleared.

It is checked, if the low level voltage is in the allowed

range. (See below)

uP trigger event is set.

It is checked, if the high level voltage is in the allowed

range. (See below.)

Parameters are set to measure high and low level with a

positive offset of 1.0 V.

uP trigger event is cleared.

It is checked, if the low level voltage is in the allowed

range. (See below.)

uP trigger event is set.

It is checked, if the high level voltage is in the allowed

range. (See below.)

If a negative offset is tested:

Parameters are set to measure high and low level with a

negative offset of -1.0 V.

uP trigger event is cleared.

It is checked, if the low level voltage is in the allowed range. (See below.)

uP trigger event is set.

It is checked, if the high level voltage is in the allowed range. (See below.)

Common settings for every Frontend type:

termination voltage: 0.0 V

termination resistor: 50.0 Ohm

source impedance of connected Frontend: 50.0 Ohm

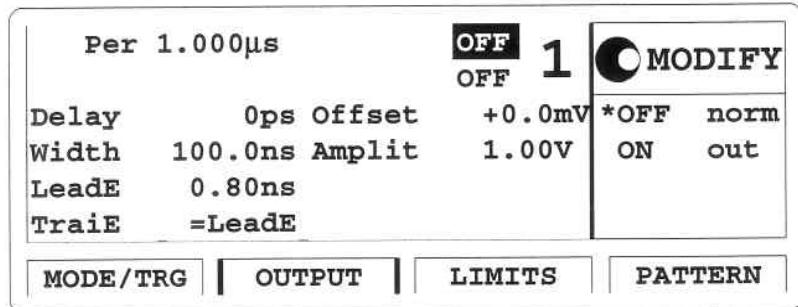

rise time: 5.0 ns (Exception: HP 81112A 0.8 ns)

fall time: 5.0ns (Exception: HP 81112A 0.8 ns)

Specific settings:

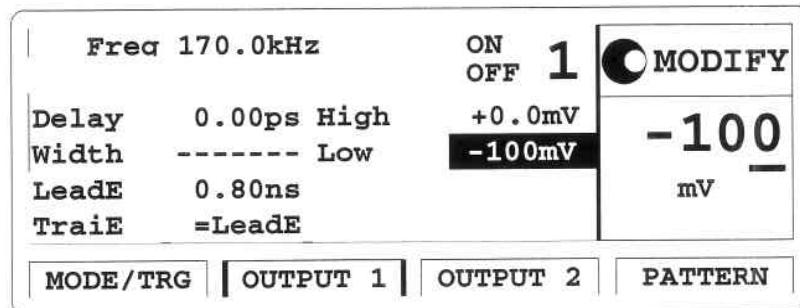

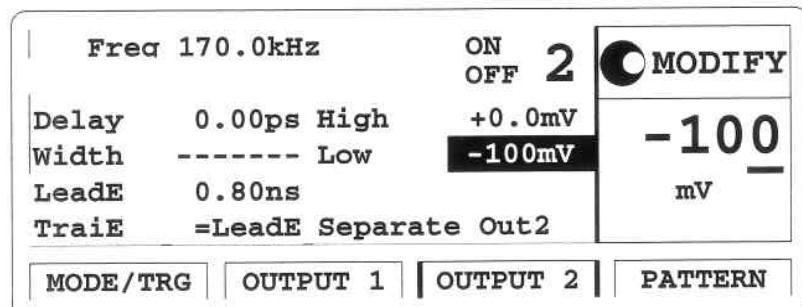

81101A/81105A/81111A 10 V

source impedance: 50.0 Ohm

test levels:

no offset:

-4.0 V (allowed: -4.3 V to -3.7 V)

4.0 V (allowed: 3.7 V to 4.3 V)

with pos. offset (1.0 V):

-3.0 V (allowed: -3.3 V to -2.7 V)

5.0 V (allowed: 4.6 V to 5.4 V)

with neg. offset (-1.0 V):

-5.0 V (allowed: -5.4 V to -4.6 V)

3.0 V (allowed: 2.7 V to 3.3 V)

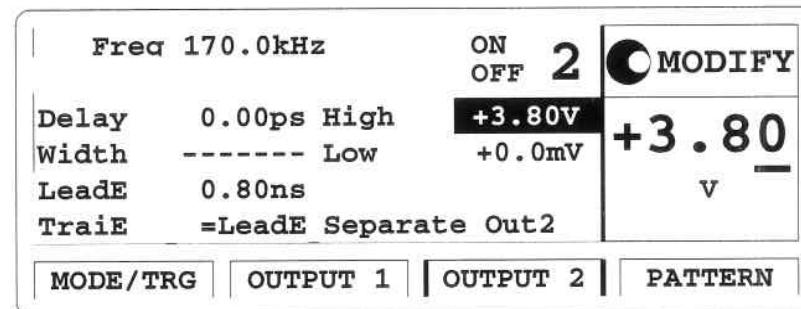

81112A/81131A 3.8 V

source impedance: 50.0 Ohm

test levels:

no offset:

-0.5 V (allowed: -0.62 V to -0.38 V)

0.5 V (allowed: 0.38 V to 0.62 V)

with pos. offset (1.0 V):

0.5 V (allowed: 0.38 V to 0.62 V)

1.5 V (allowed: 1.34 V to 1.66 V)

with neg. offset (-1.0 V):

-1.5 V (allowed: -1.66 V to -1.34 V)

-0.5 V (allowed: -0.62 V to -0.38 V)

81132A 2.5 V

source impedance: 50.0 Ohm

test levels:

no offset:

-0.5 V (allowed: -0.55 V to -0.45 V)

0.5 V (allowed: 0.45 V to 0.55 V)

with pos. offset (1.0 V):

0.5 V (allowed: 0.45 V to 0.55 V)

1.5 V (allowed: 1.35 V to 1.65 V)

with neg. offset (-1.0 V):

-1.5 V (allowed: -1.65 V to -1.35 V)

-0.5 V (allowed: -0.55 V to -0.45 V)

Troubleshooting:

Check calibration of Frontend (recalibrate it).

If only positive or negative offset failed, check offset amplifier.

Check internal termination of Frontend.

Check hardware register 3 for uP trigger event (Signals UPTRIGN, UPTRIGC).

Check TIGER ICs.

Check V\_ADC value. (Hardware register 0 may also be faulty.)

**VCO x failed test for 360MHz**

**VCO x failed test for 540MHz**

**VCO x failed test for 720MHz**

The VCO with internal number x failed the selftest at the lower frequency limit / operating frequency / upper frequency limit.

The VCOs are numbered as follows:

0 Period TIGER VCO 1

1 Period TIGER VCO 2

2 Delay TIGER VCO 1 (channel 2)

3 Delay TIGER VCO 2 (channel 2)

4 Width TIGER VCO 1 (channel 2)

5 Width TIGER VCO 2 (channel 2)

```

6      Delay TIGER VCO 1 (channel 1)

7      Delay TIGER VCO 2 (channel 1)

8      Width TIGER VCO 1 (channel 1)

9      Width TIGER VCO 2 (channel 1)

```

Possible cause:

VCO uncalibrated

corresponding TIGER IC not working

corresponding DAC not working

FPGA on the timing board not working

(measurement failed)

PLL not working (measurement failed)

Hardware register 1 out of order

Description of this test:

VCO of PLL is switched on, if it isn't already on.

Depending on the Delay-Width Boards being available,

the VCOs in the TIGER ICs are tested. (Description of

VCO-test (see below.)

The Period TIGER is tested last.

(Description of VCO-test see below.)

VCO of PLL is switched off, if it was off before this

selftest.

The test of a VCO is done in the following way:

TIGER IC is set into reset.

TIGER IC is set into this mode:

|                 |              |

|-----------------|--------------|

| clock source:   | Internal VCO |

| clock mode:     | Continuous   |

| pulse type:     | Pulses       |

| trigger source: | TRIGIN (uP)  |

| clock edge:     | positive     |

| arm edge:       | positive     |

| formatter mode: | RZ           |

| burst length:   | 1            |

External divider is disabled.

Internal period divider factor is set to 64.

Oscillator is enabled for calibration.

Reset of TIGER IC is released.

Pulses are started by triggering the Period TIGER IC

with the uP trigger event.

It is checked, if the measured frequencies are in the

allowed ranges:

|         |         |          |                    |

|---------|---------|----------|--------------------|

| tested: | 360 MHz | allowed: | 342 MHz to 378 MHz |

| tested: | 540 MHz | allowed: | 513 MHz to 567MHz  |

| tested: | 720 MHz | allowed: | 684 MHz to 756MHz  |

External divider is enabled.

Troubleshooting:

If PLL test has failed before, go back to troubleshooting

for PLL.

Check whether external divider of the corresponding

TIGER IC is disabled.

Check hardware register 3 for uP trigger event.

Check if Period FPGA (frequency measurement) is working

correctly.

Check corresponding TIGER IC.

[Complete Listing of Firmware ERRORS + Description](#)

[Complete Listing of BIOS ERRORS + Description](#)

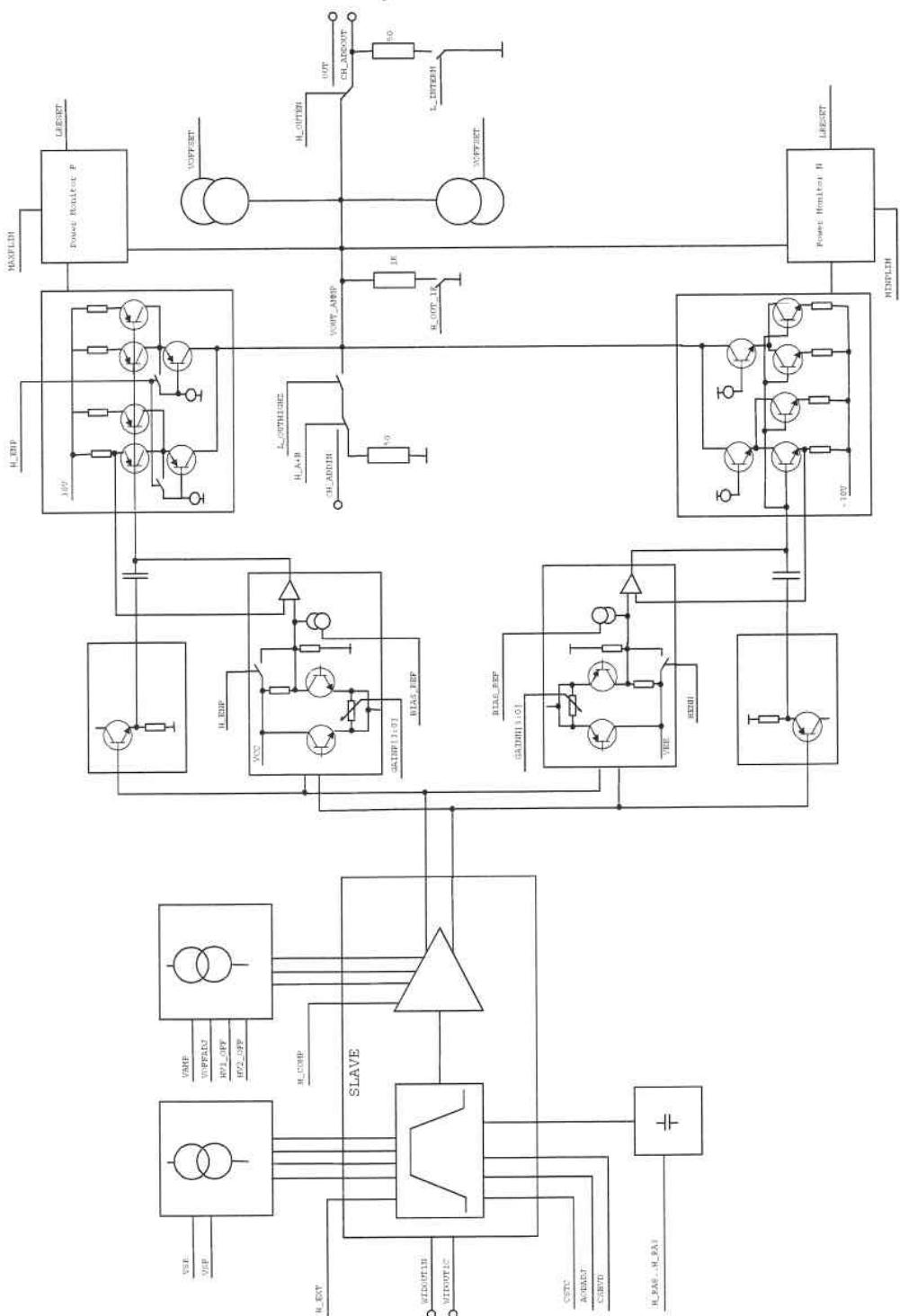

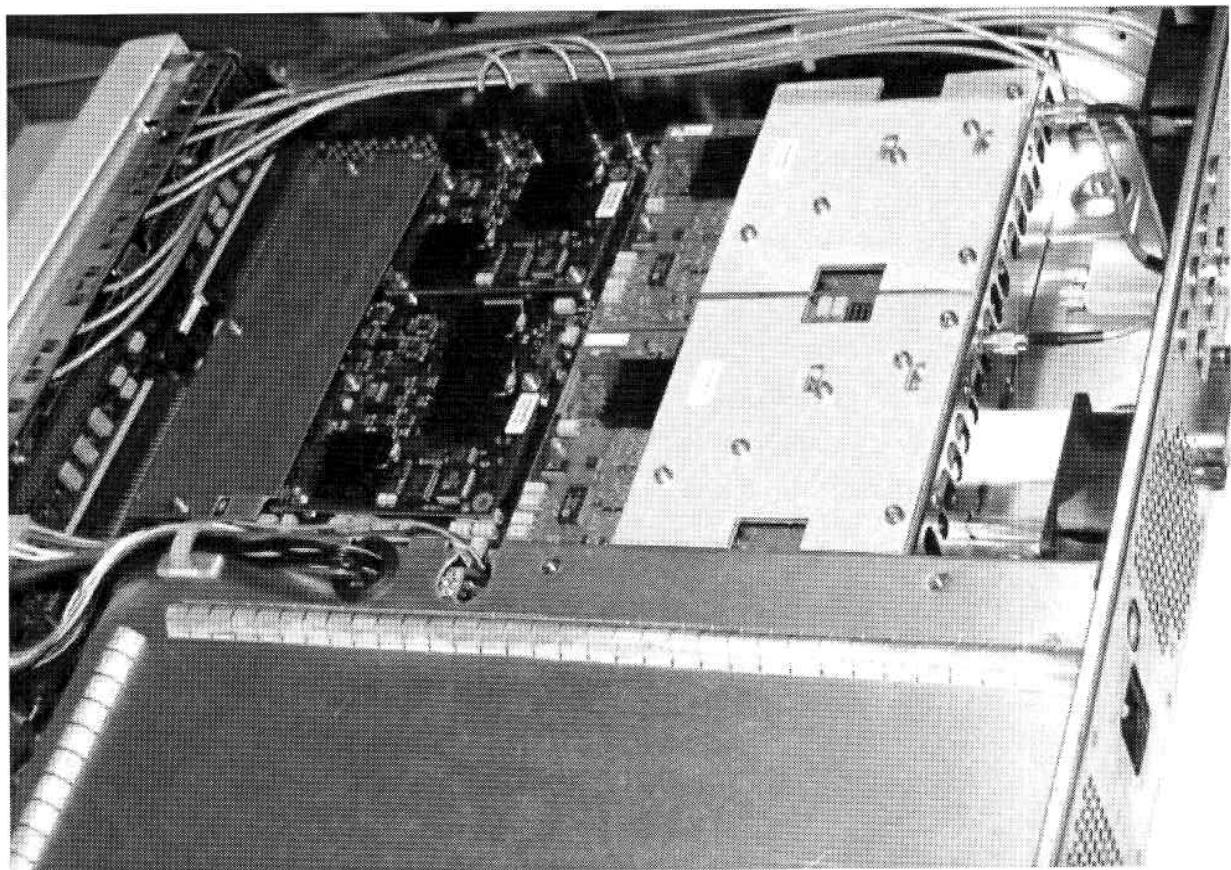

## Block Theory

---

- a. **µProcessor Board**

- b. **Timing Board**

- c. **Output Channels**

- d. **Power Supply**

## Block Theory

### 3 a

## uProcessor Board

---

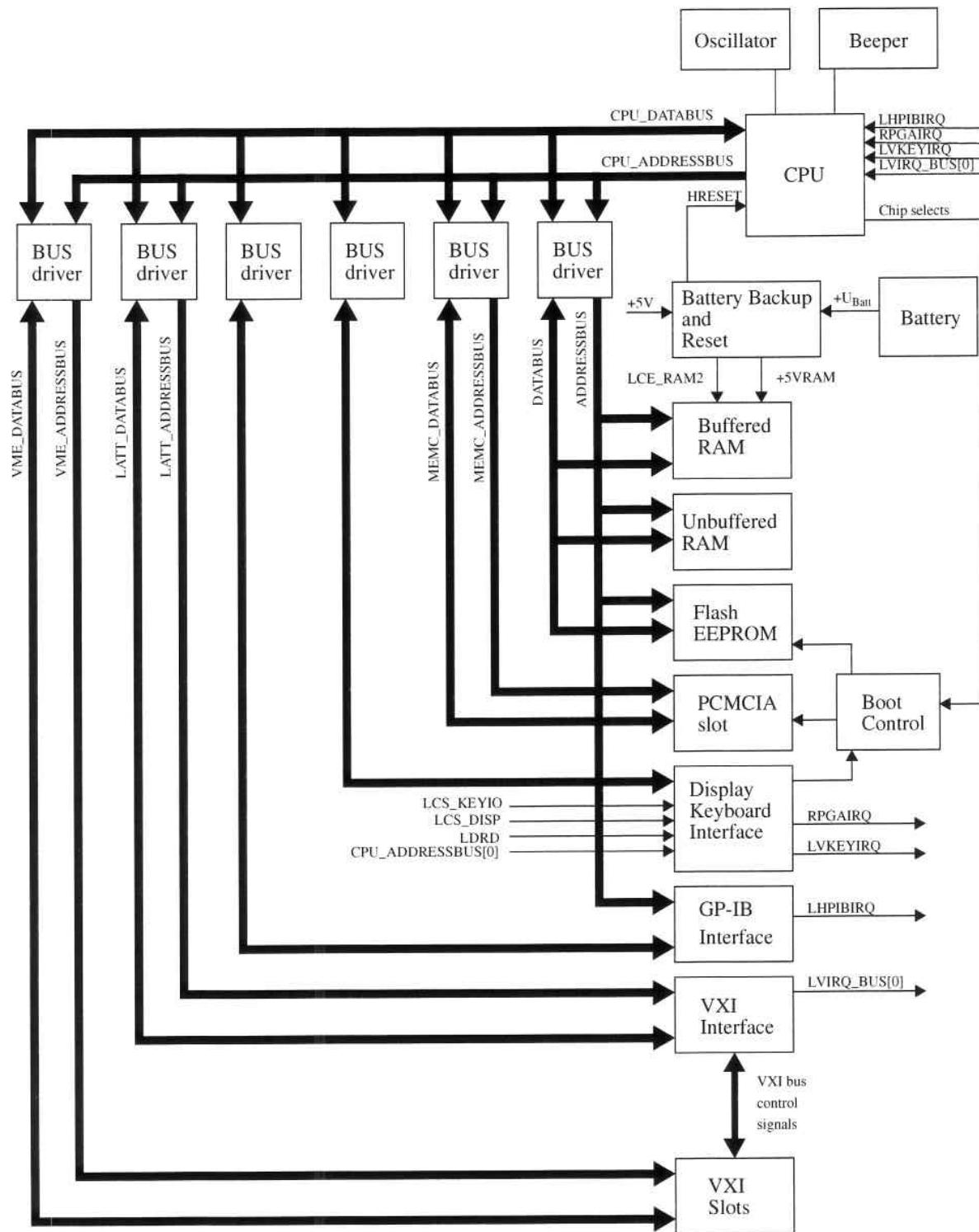

### General

The uProcessor Board controls the 811xxA. It receives data from Flash-EEPROM and battery-backed Static RAM, the Keyboard and the GPIB interface. It communicates with the boards in the instrument through the VXI-Interface. The uP. Bd. is designed around the MC 68331 Microprocessor

Functional units are:

- CPU - Motorola 68331 running at 16.7MHz

- 2MB Flash-EEPROM

- 256KB unbuffered RAM

- 256KB buffered RAM

- Battery, Battery Backup and Reset

- Beeper

- Oscillator

- GPIB interface

- PCMCIA slot for use with memory cards up to 2MB

- Display and Keyboard interface

- VXI interface

- 2 VXI slots

### Features

- GPIB programmable

- Interface - same as in Agilent 8110A

(display and keyboard are the same, new version of RPG board required)

- Address space of Flash-EEPROM and PCMCIA card can be exchanged on startup by pressing a special key combination ('1' & '3'), to allow easy software update (CPU running on memory card!).

---

### Block Diagram

Functional Units on the uP Board ...

The Microprocessor PC Board's functional units, and what they are for:

|                                |                                                                                                                                                                                         |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Battery Backup and Reset       | Sets conditions during power-up                                                                                                                                                         |

| Battery                        | Supports the Static RAMs when the instrument is not powered                                                                                                                             |

| Beeper                         | Gives an audible warning tone and makes a 'click' when a key is pressed                                                                                                                 |

| Boot Control                   | Decides whether to boot the Microprocessor from the flash EPROMs or from the Memory Card                                                                                                |

| Oscillator                     | Provides clock pulses for the Microprocessor                                                                                                                                            |

| GPIB Interface                 | For accessing the instrument externally<br>- uploading and downloading of data,<br>- or for control                                                                                     |

| Display and Keyboard Interface | Interface to the display, keyboard and Rotary Pulse Generator (RPG)                                                                                                                     |

| PCMCIA slot                    | Allows the usage of PCMCIA memory cards.<br>The memory card contains battery-backed RAMs containing different firmware and store/recall data settings to that held in the Flash EEPROMs |

| Flash EEPROMs                  | Contains the firmware that is used to specify and control the instrument.                                                                                                               |

| Buffered RAM                   | Contains data that is regularly changing, but has to be persistent when the power is down.                                                                                              |

| Unbuffered RAM                 | Contains data that is regularly changing, but may be lost when the power is down.                                                                                                       |

| VXI Interface                  | Controls the VXI/VME bus, used to access the instrument specific modules.                                                                                                               |

| VXI Slots                      | Two slots to plug in the instrument specific VXI modules.                                                                                                                               |

### **Detailed Description ...**

#### **Battery Backup and Reset**

When power is applied to the Microprocessor Board, the timer (formed by U4 and associated components) holds down the MPU Reset line for a period exceeding 100ms. This allows time for a general MPU reset and a longer period for the MPU clock PLL to stabilise. One half of the Static RAMs (Buffered RAM) are backed up by the battery when the instrument is switched OFF and during reset. U4 disconnects the battery and enables the Power Supply Voltage via Q1 when the instrument is switched ON and after reset.

(This section is on schematic sheet 1.)

#### **Beeper**

The beeper is directly driven by the MPU and inverter U32. An MPU high output level is inverted to low by U32 for the other pin of the beeper. The reverse applies when the MPU output goes low. The MPU pin toggling is driven by the firmware which provides a number of frequencies for the beeper.

(This section is on schematic sheet 1.)

#### **Boot Control**

If the front panel keys '1' and '3' are pressed during switch-on, the system is booted from the Memory Card instead of the Flash EEPROMs. Gate U33 combines the two keyboard signals and sets D-Flipflop U5. Data from the Flipflop controls the multiplexer U3, which generates the correct chip selects for the Flash EEPROMs and the memory card out of the corresponding chip selects from the MPU.

During MPU reset the general-purpose IO lines are regarded as input lines. After reset they are configured as required (by taking low certain lines on the MPU Databus) because they are used as mode select lines for the general IO lines.

In this case, line 4 and line 9 are set to low by U32.

(This section is on schematic sheet 1.)

#### **Display and Keyboard Interface**

##### *Display Enabling*

This description does not cover the Display Unit, which can be considered as a replaceable unit.

The Display is blanked at system initialization to prevent displaying of random information. It is activated by writing to U27 to set signal LDISPBL.

Shift register U2 controlling U34/U43 provides correct setup and hold times between Read/Write and valid Data Bus. Additionally, the software waits 2ms between Read/Write cycle.

Resistors R13 - R15 reduce overshoot.

(This section is on schematic sheet 1.)

##### *Buffering*

Buffer U51 restores data rise and fall times due to RFI filtering. The main reason for buffering is to disable the data bus if used by other circuits inside the shielded case, thus minimising RFI.

(This section is on schematic sheet 2.)

#### **Keyboard**

Whenever a key is pressed an interrupt is generated by gate U36. U28 sequentially latches data to produce 4 columns with a 'travelling' low level. If a key is pressed it connects a column to one of 8 rows formed by the inputs to latch U23. By reading the 12 bit 'word' thus formed, the MPU can calculate which key was pressed, as each key has a unique row-column combination.

(This section is on schematic sheet 4.)

#### **Rotary Pulse Generator**

This description does not cover the RPG, which can be considered as a replaceable unit.

U33 buffers the RPG interrupt signal. U33 also provides the MPU with a buffered directional signal.

(This section is on schematic sheet 1.)

#### **GPIB Interface**

U22 divides the system clock frequency by 4 to produce the GP-IB clock at approximately 4.2MHz. U24 is the GP-IB controller. The LDRD (Low Data Read) signal is inverted by U44 to become HDRD (High Data Read). The Databus is buffered by U23. Data and control lines are buffered by U25 and U26.

(This section is on schematic sheet 4.)

#### **Oscillator**

The MPU is clocked by an internal PLL oscillator, using an external crystal. The crystal oscillates at 32.768kHz, producing final operating frequencies of 8.38MHz during reset and 16.78MHz during normal operation. The crystal, Y1, is tuned by R11/R12 and C2, C3.

(This section is on schematic sheet 1.)

#### **PCMCIA Slot**

This description does not cover the Memory Card, which can be considered as a replaceable unit.

Buffering of address and data busses is provided by U53 - U55.

(These sections are on schematic sheet 2 and sheet 6.)

#### **Flash EEPROMs**

These EEPROMs contain the current version of the firmware used in the instrument, but can be superceded by firmware stored on a memory card, which can take precedence at Bootup. The MPU can download a copy of the firmware in the memory card to the Flash EEPROMs.

(This section is on schematic sheet 3.)

#### **Static RAMs**

These RAMs contain data that varies during operation.

U18 - U21 contain data that must be retained, such as configuration information. These RAM ICs are battery-backed to retain data during reset or after switch off. U14 - U17 are not battery-backed.

(This section is on schematic sheet 2.)

**VXI-Slots**

*Buffering*

The address- and databus is buffered by U8 - U10.

The control signals on the VXI bus are buffered by U11.

*Control Signals*

The control signals for the VXI bus are generated by the

VXI-Interface (U29).

(This section is on schematic sheet 2 and sheet 7.)

**VXI-Interface**

The VXI-Interface implements the required control signal

protocol for the VXI bus. The required data and address lines

are buffered by U10 to avoid the programmable logic device to

block the MPU if the programmed image is corrupt.

A completed access to the VXI bus is reported to the MPU by

driving LDSACK1 to low. If the device on the VXI bus doesn't

respond correctly, the cycle is aborted by the MPU's internal

timeout generation.

The programming of U29 is done via U30. The access to U30 is

enabled/disabled by signal LLATT\_PROG (directly from the MPU).

The enabling/disabling of U30 avoids accidentally erasing of U29.

(This section is on schematic sheet 5.)

## 1.0 uProcessor Block Diagramm

3 b

## **Block Theory, Timing Boards**

---

I. 81101A, 81104A, 81110A

II. 81130A

## Block Theory

### 3 b I

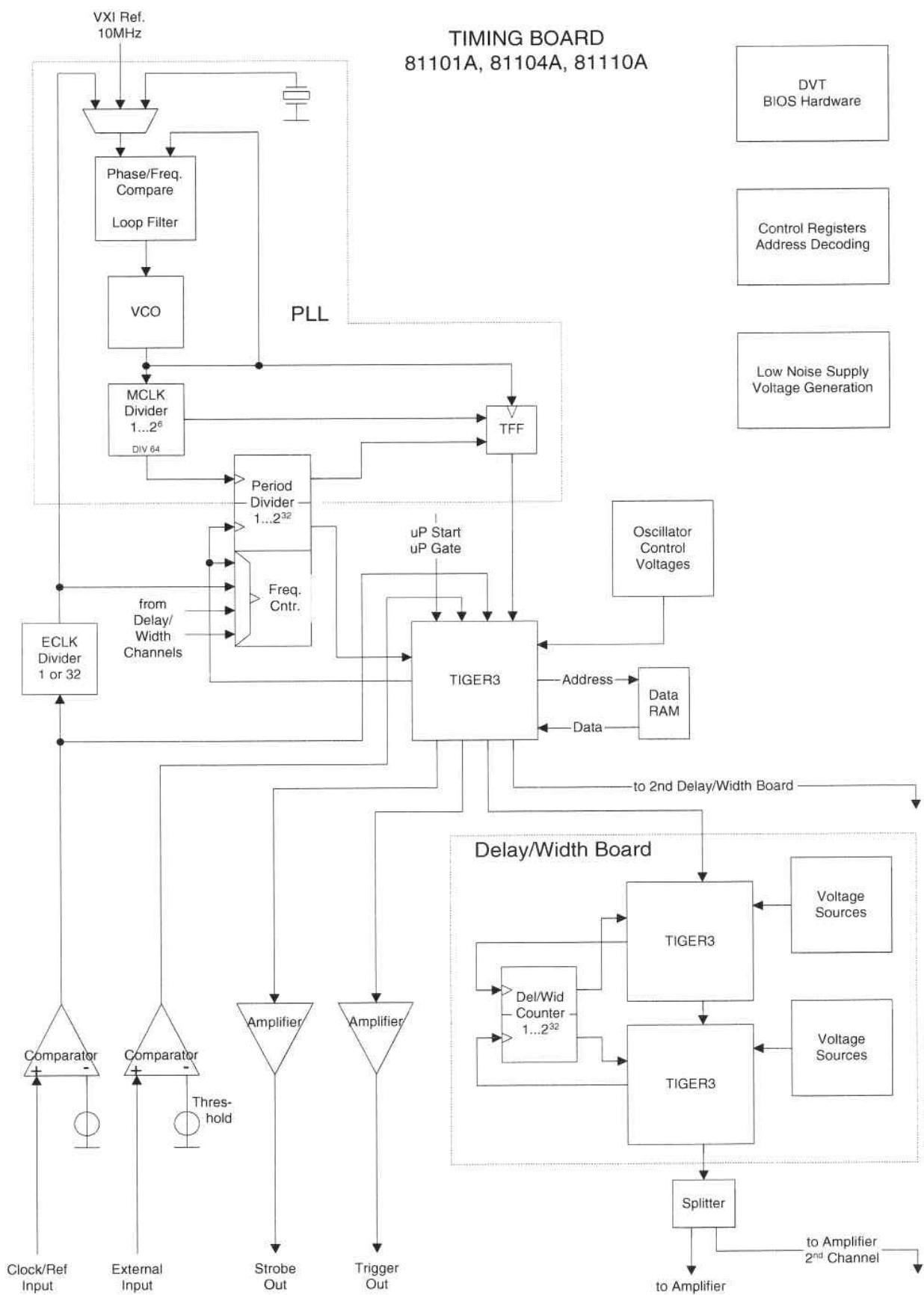

## Timing Board 81101A, 81104A, 81110A

### General

The main task of the Timing Board is to generate the period signal, which drives the Delay/Width Board. The heart of the Timing Board is a timing generator IC (TIGER3 : TIMing GEnerator 3<sup>rd</sup> generation), which is basically an astable oscillator when it is running without external drive or triggering, or a monostable oscillator when triggered from the PLL or a source external to the Timing Board. Triggering from the PLL provides greater period accuracy and stability. Voltage sources and counters control the period of the TIGER3 output signals. TIGER3 is also capable of producing a specified number of pulses, called a burst.

Functional units are:

- Clock/Reference Input

- External Input

- Strobe Output

- Trigger Output

- ECLK Divider

- PLL

- TIGER3

- Data RAM

- Oscillator Control Voltages

- Low noise supply voltage generation

- DVT BIOS hardware

- Address decoding, control registers and Cal-EEPROM

### Block Diagram

### Detailed Description ...

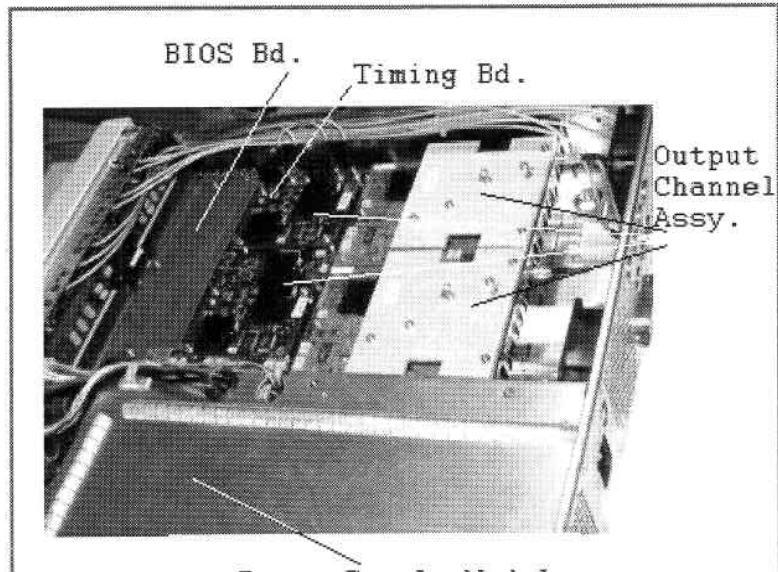

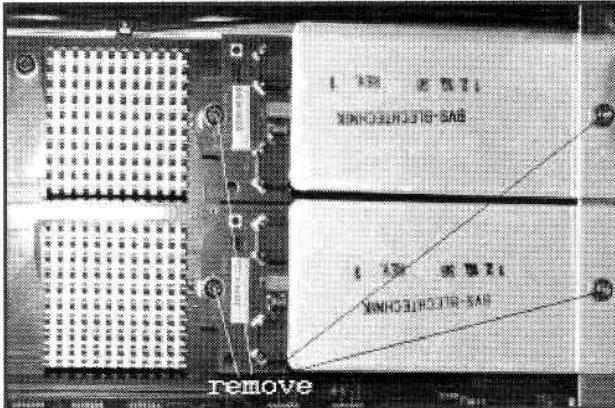

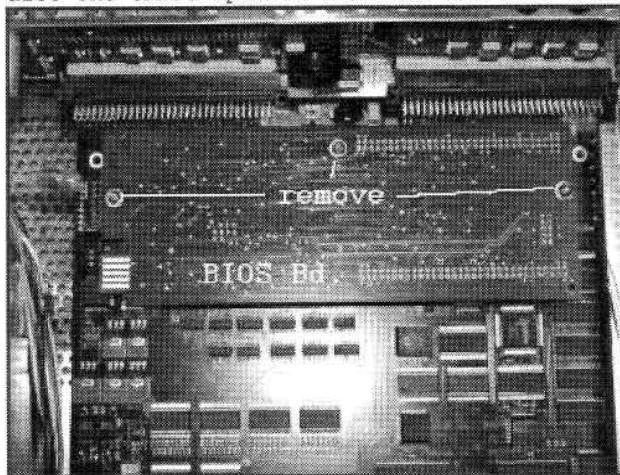

#### DVT BIOS Hardware (Sheets 1 to 4)

The DVT BIOS hardware has the function to interface between the VXI-Bus and the module specific hardware on the Timing Board. This interface is accomplished via a local processor. This board is realized as a plug-in board to the Timing Board. The complete VXI-interface-hardware is located near the J1-connector on the board.

The board has buffers to the VXI-Bus, the module hardware and a FPGA. The FPGA does the arbitration between the local CPU and the VXI-Bus, contains the VXI-Bus configuration registers and other VXI-Bus specific functions.

The BIOS Board consists of the MC68331 CPU, SRAM, Flash-EEPROM, buffers to the Timing Board, interfaces to an emulator, terminal and an EEPROM-load and debugging tool.

**Address Decoding, Control Register and Cal-EEPROM** (Sheets 5 and 6)

This functional unit provides all address signals, write- and read-strobes, reset signals and registered control signals, which are necessary to control the Timing Board, the Delay/Width Boards and the Amplifier Boards.

The Cal-EEPROM stores the calibration tables of the Period Tiger, ADC circuit, input-threshold DAC's.

At switch-on the Processor reads the calibration tables and keeps it in its local RAM. For debug/service it is possible to suppress the usage of the calibration data from the EEPROM, by shortening the pins 1 and 2 of J5 during the startup phase.

#### **Low Noise Supply Voltage Generation**

All VXI supply voltages (-24V, -12V, -5.2V, -2V, +5V, +12V, +24V) are LC-filtered at the board input (Sheet 2) by 3.3 $\mu$ H inductors and 22 $\mu$ F or 10 $\mu$ F Tantalum capacitors. These filters are especially useful to suppress power-supply noise (in the region of about 100kHz up to 1MHz). Ceramic capacitors are distributed all over the board to suppress high frequency noise.

For noise sensitive devices, especially the oscillators and their controlling circuits, linear regulators (Sheet 12) generate additional voltages. These voltages are

VCC\_OSC (+8.3V, U401),

VEE\_OSC (-8.3V, U402),

+20VVCO (U407),

VP\_PLL (+6.3V, U408, Q403),

+10VVCO (U408, Q405),

-4.8V\_TG (U404, Q402).

The TTL I/O interface of the Tiger uses +3.5V, generated by U403 and Q404.

The amplifiers need +31V and -31V. The DC/DC converter circuits of U501 and U551 with surrounding components generate these voltages.

The +31V is realized by generating an offset voltage of approximately 7V out of the +12V power supply. This offset voltage is added to the +24V supply voltage. The same principle is used for the -31V. Thereby it is to observe that the DC/DC converters U501/U551 regulate its output voltage so that they receive a positive feedback voltage of 1.25V. With the +31V this is achieved by two resistors that divide the output voltage. This is not possible with the -31V since this voltage is negative. Therefore a current mirror circuit made up of Q552, Q553 and Q554 is used to invert the polarity of the feedback voltage.

#### **External Input** (Sheet 14 and 16)

A signal at the external input can start, stop or gate the period generator. In external width mode the period and width of the signal from the external input are maintained.

The external input circuit converts the input voltage to an ECL signal

The external input signal enters through connector J602. The input impedance is either 500 $\Omega$  if relay K602 is closed or about 10k $\Omega$  (high impedance) if the relay is open.

The high-speed comparator U601 has an input threshold voltage of 0V and an input voltage range of about +/-3V, so the external input signal must be attenuated and level-shifted. Diodes CR605 to 607 prevent the comparator from hazardous voltages. A resistor/capacitor network and the threshold generation (U603,

U604) attenuate and shift the input signal.

The threshold voltage is generated and adjusted by the DAC U603 and the operational amplifiers U604. To prevent that the internal threshold voltage causes any damage to the connected external signal source it is compensated to a level of 0V regarding the input connector J602 using the operational amplifier U605.

**Clock/Reference Input** (Sheet 14 and 16)

The Clock/Ref. input can be used as reference clock for the PLL (5MHz or 10MHz nom.) or as external clock source.

The Clock/Reference input circuit works in exactly the same way as the external input.

**Strobe Output** (Sheet 15)

The Strobe output amplifier converts the differential ECL-level strobe signal of the Tiger IC to an either TTL or ECL compatible single ended output. In Burst mode Tiger delivers one pulse per burst and in pattern mode a user-defined NRZ pattern.

Diodes CR705 shift the Tiger output signal to a lower level, which drives the differential amplifier Q710/Q711.

When TTL levels are selected, the signal LTTLHECLSTR switches transistors Q708 and Q712 on and so sets the highlevel to about 5V (unloaded output) and the amplitude current to approximately 100mA. This gives a highlevel of 2.5V and a lowlevel of 0V with an external 500hm-termination resistor connected to ground.

In ECL level mode transistors Q708 and Q712 are off, so the amplitude current is reduced to 36mA and the highlevel voltage is about -1.6V if the output is unloaded. When the output is terminated with 500hm to ground the highlevel is -0.8V and the lowlevel is -1.8V.

If in ECL level mode the output is terminated with 500hm to ground and the transistor Q711 is off, a current flows from ground through the termination resistor and the resistors R734 to R738 to the voltage source made of transistor Q709 and the surrounding network of resistors and diodes. This happens vice versa if transistor Q710 is off. Since this voltage source cannot sink current a current load is mandatory. This function is achieved by transistor Q714 and the resistor R730 which form a current source that is switched on by the transistor Q712 in ECL level mode.

**Trigger Output** (Sheet 15)

The Trigger output sends one RZ pulse (50% dutycycle) per generated period. The trigger amplifier circuit is identical to the Strobe output.

**External Clock Divider** (Sheet 10)

The divider is build from a 8bit counter and a 2-to-1 multiplexer to select divide factor 1 or 32. The divide factor 32 is used to measure an external frequency larger than 10MHz with the FPGA U104.

For lower frequencies the divide ratio is 1.

**Phase Locked Loop PLL** (Sheet 9)

The PLL consists primarily of a RF oscillator (Y302) with a frequency range of 330MHz to 670MHz, a PLL frequency synthesizer chip (U302) and a loop filter.

The oscillator sends its output signal AC-coupled to an ECL-splitter circuit U305, which converts the single ended signal into two differential ECL signals, one for phase-frequency-compare and one to a divider. U306 and surrounding components regulate the dutycycle of the splitter output to 50%.

A flipflop divides the output of the 20MHz-reference oscillator Y301 by two. The multiplexer U301 allows selecting from 3 different reference sources:

- the VXI reference,

- an external reference clock,

- the internal reference.

The selected reference clock is applied to the PLL IC U302.

Inside the IC the clock signal is passed through a reference divider. A second divider processes the output from the VCO (Splitter), and the two divided signals are phase-frequency-compared, producing an output voltage.

This signal is filtered with the active integrator circuit U303 and some passive components. A LC low-pass-filter suppresses the unwanted spectral components. U 304 limits the range of the output voltage of the loop filter to about 0V to 12V, a range suitable for tuning the VCO to frequencies between 330MHz and 670MHz. An ECL divider and a cascaded divider in FPGA U104 divide the second output signal of splitter U305 to 1mHz up to 330MHz. The arrangement of the circuits (U353-356, U104) is such, that the output signal has always 50% dutycycle.

#### **TIGER3 (Sheet 7)**

The TIGER (TIming GEneratoR) has 4 signal inputs:

- mPTRIG from the CPU

- EXTIN from external input

- MCLK\_DIV from the PLL

- ECLK\_PerTG from Clock input

The inputs can start, stop or gate the TIGER oscillator. mPTRIG and EXTIN can also start, stop or gate the PLL clock or the clock signal from the Clock/Reference input by enabling or disabling the clock path through the TIGER IC.

The TIGER has 4 used signal outputs:

- TRIGDEL1 drives Delay/Width board 1

- TRIGDEL2 drives Delay/Width board 2

- TRIGOUT drives the Trigger Output

- STROUT drives the Strobe Output

TRIGOUT and STROUT levels are ECL compatible, while the TRIGDEL outputs are open collector outputs which generate a swing of about 300mV when externally terminated to Ground.

The TIGER has a burst counter which allows generating a counted number of pulses (1 to 65536). Instead of putting out pulses the TIGER can also send a pattern stream. The pattern comes from an external high speed BiCMOS RAM, which is addressed from the TIGER burst counter.

The TIGER is programmed from the CPU with a 3 wire serial interface. The signals SDATA0, SHFTCLKPERTG and WRCLKPERTG are LVCMOS compatible.

The TIGER has 2 internal oscillators to allow range free period, delay or width sweeps. DAC's and operational amplifiers generate differential control voltages for the oscillators. The control voltages are in an range of about -0.8V to -3.2V.

The TIGER oscillators are temperature sensitive, which means they change oscillation frequency with temperature. To compensate that behavior additional DAC's and a temperature diode on the TIGER IC generate a compensation voltage, which is added to the control voltage.

#### **Data RAM (Sheet 7)**

The 32kByte fast SRAM is loaded from the CPU via bus driver U103. The address lines always are driven from the TIGER IC. At every read or write access of the CPU to the RAM the burst counter of the TIGER increments automatically. So no additional address driver for the RAM is necessary.

In pattern mode the TIGER reads the data from the RAM through its RAMD inputs. Resistors R107 to R114 limits the highlevel on the datalines to a level that is save for the TIGER LVCMOS inputs.

#### **Oscillator Control Voltages (Sheet 8)**

The control voltage sources control the period of the TIGER oscillators. They deliver a voltage in the range of -0.8V to -3.2V. The voltages are arranged as differential pairs to suppress common mode disturbances. 12bit Digital-to-Analog converters U201A/B and operational amplifiers U202...204 set the voltage level.

Because the TIGER oscillator changes its oscillation frequency with temperature the temperature of the TIGERs is sensed with on-chip temperature diode. The diodes are biased with a 100mA constant current. The current source is build with U209. A portion of this temperature voltage is added to the control voltages to compensate the temperature drift. Because the drift differs from part to part the DAC's U201C/D set the appropriate level of compensation.

## Block Theory

### 3 b II

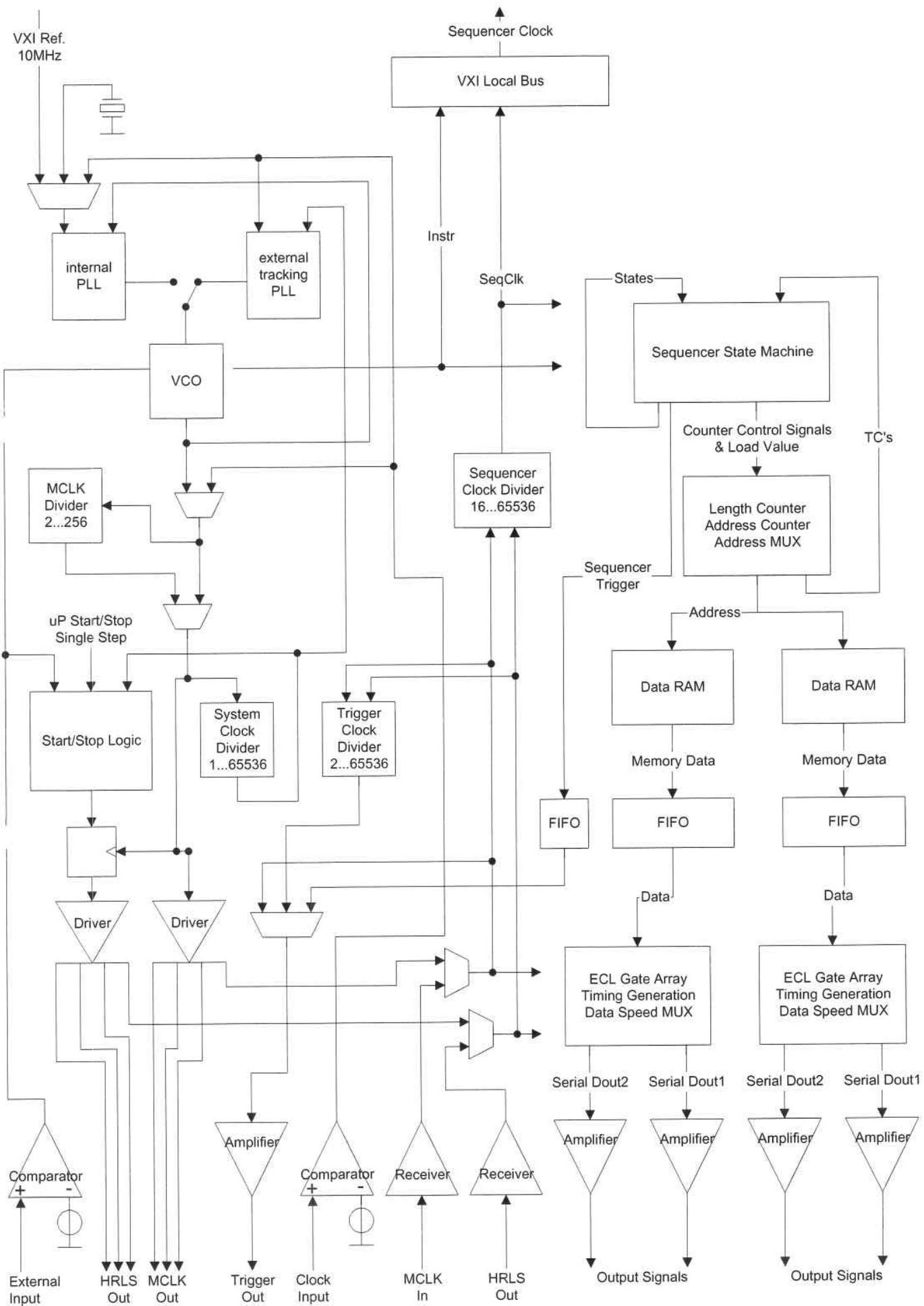

## Timing Board 81130A

---

### General

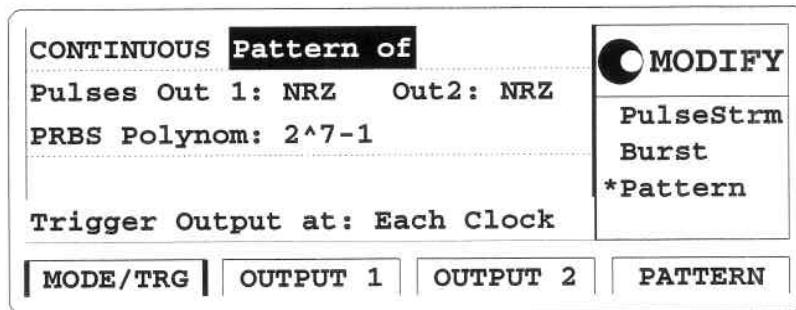

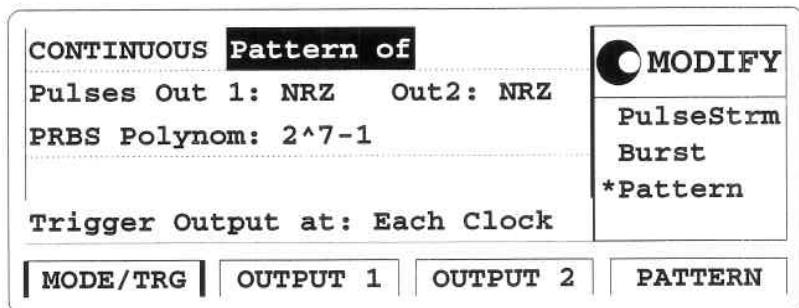

The module generates two parallel clock and/or data streams. Data streams comprise user memory data and memory based PRBS. Additionally a trigger output signal is provided.

Tasks of the Timing Board are:

- Generate a period signal

- Generate a sequence of data patterns

- Multiplex these parallel data to a high-speed serial data-stream

- Format the data-stream with delay and pulse-width

- Generate a trigger output signal

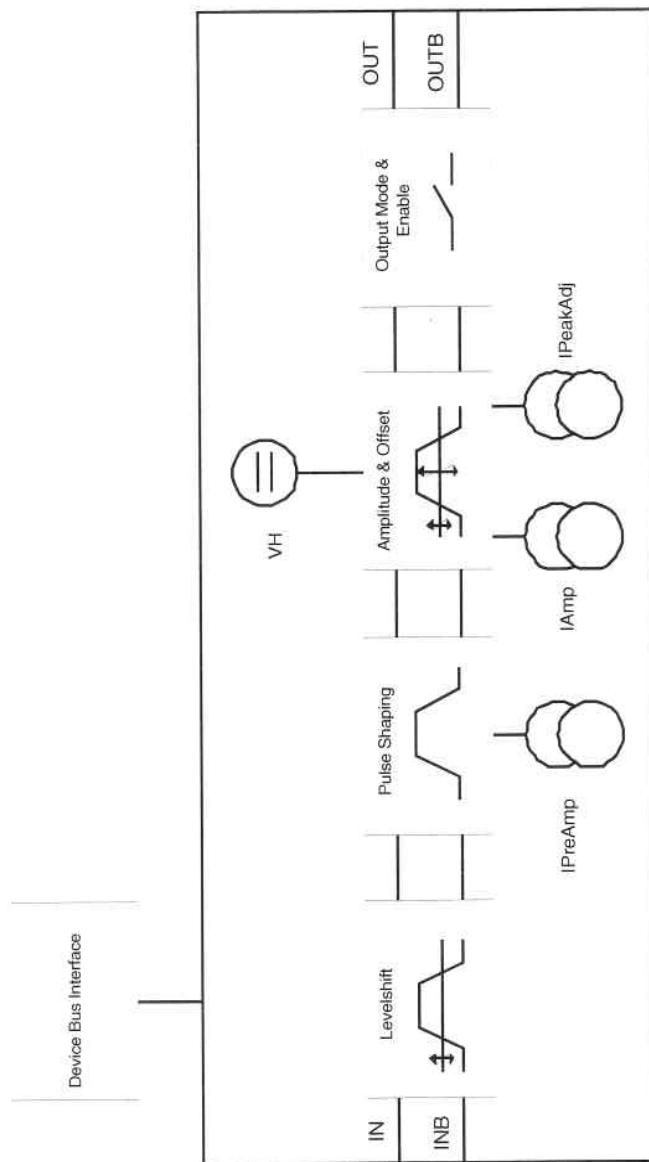

Functional units are:

- External Input

- Clock/Reference Input

- MCLK and HRLS Input and Outputs

- Trigger Output

- MCLK Divider

- PLL

- System Clock Divider

- Start/Stop Logic

- Trigger Clock Divider and MUX

- Sequencer Clock Divider

- Sequencer

- Data RAM

- Timing ECL Gate Array

- Low noise supply voltage generation

- DVT BIOS hardware

- Address decoding, control registers and Cal-EEPROM

---

Block Diagram

Detailed Description ...

**DVT BIOS Hardware** (Sheets 1 to 4)

The DVT BIOS hardware has the function to interface between the VXI-Bus and the module specific hardware on the Timing Board. This interface is accomplished via a local processor. This board is realized as a plug-in board to the Timing Board. The complete VXI-interface-hardware is located near the J8-connector on the board.

The board has buffers to the VXI-Bus, the module hardware and a FPGA. The FPGA does the arbitration between the local CPU and the VXI-Bus, contains the VXI-Bus configuration registers and other VXI-Bus specific functions.

The BIOS Board consists of the MC68331 CPU, SRAM, Flash-EEPROM, buffers to the Timing Board, interfaces to an emulator, terminal and an EEPROM-load and debugging tool.

**Address Decoding, Control Register and Cal-EEPROM**

(Sheets 5 and div.)

This functional unit provides all address signals, write- and read-strobes, reset signals and registered control signals, which are necessary to control the Timing/Data Board, and the Amplifier Boards.

The Cal-EEPROM stores the calibration tables of the

Timing ECL Gate Array,

ADC circuit,

Trigger levels,

Input-threshold and termination voltage DAC's.

At switch-on the Processor reads the calibration tables and keeps it in its local RAM.

**Low Noise Supply Voltage Generation** (Sheets 24 and div.)

All VXI supply voltages (-12V, -5.2V, -2V, +5V, +12V, +24V) are LC-filtered at the board input (Sheet 2) by 3.3 $\mu$ H inductors and 47 $\mu$ F or 1 $\mu$ F Tantalum capacitors. These filters are especially useful to suppress power-supply noise (in the region of about 100kHz up to 1MHz). Ceramic capacitors are distributed all over the board to suppress high frequency noise.

For noise sensitive devices, especially the oscillators and their controlling circuits, linear regulators generate additional voltages.

These voltages are

VCC\_OSC (+7.8V, U419, Q416),

VEE\_PLL (-8.3V, U631),

+20VVCO (+20V, U630),

VP\_PLL (+6.3V, U420, Q414),

VCC\_OSC (+10V, U419, Q415),

VCC\_SW (+5V, U420, Q419).

The data SRAM's and parts of the address decoding use +3.5V, generated by U553 and Q550.

**External Input** (Sheet 24 and 25)

A signal at the external input can start, stop or gate the period generator.

The external input circuit converts the input voltage to an ECL signal. The external input signal enters through connector J304. The input impedance is 50 Ohm.

The high frequency components of the input signal are attenuated and AC coupled to the non-inverting comparator input. The low frequency components are also attenuated, inverted by U351 and coupled to the inverting input of the comparator. U351 also adds the threshold voltage.

Diodes CR359 to 363 prevent the comparator from hazardous voltages.

The threshold voltage is generated and adjusted by the DAC U416 and the operational amplifiers U417.

**Clock/Reference Input** (Sheet 14 and 16)

The Clock/Ref. input can be used as reference clock for the PLL (1, 2, 5 or 10MHz nom.) or as external clock source.

The Clock/Reference input signal is AC coupled to the input of the comparator. There is no DC path. So no threshold generation is needed, the comparator threshold is 0V. Diodes CR350 and 364 prevent the comparator from hazardous voltages

**Phase Locked Loop PLL** (Sheets 14, 18 and 19)

The internal PLL consists primarily of a RF oscillator (U101) with a frequency range of 330MHz to 670MHz, a PLL frequency synthesizer chip (U807) and a loop filter.

The oscillator sends its output signal AC-coupled to an ECL-splitter circuit U102, which converts the single ended signal into two differential ECL signals, one for phase-frequency-compare and one to a divider. U104 and surrounding components regulate the dutycycle of the splitter output to 50%.

A flip-flop divides the output of the 20MHz-reference oscillator Y800 by two. The multiplexer U810 allows selecting from three different reference sources:

the VXI reference,

an external reference clock,

the internal reference.

The selected reference clock is applied to the PLL IC U807. Inside the IC the clock signal is passed through a reference divider. A second divider processes the output from the VCO (Splitter) and the two divided signals are phase-frequency-compared, producing an output current. The current/charge is proportional to the phase difference between the compared signals. When the phase difference is zero the output current is also zero.

This signal is filtered with the active integrator circuit U808 and some passive components. A LC low-pass-filter suppresses the unwanted spectral components. U304 limits the range of the output voltage of the loop filter to about 0V to 12V, a range suitable for tuning the VCO to frequencies between 330MHz and 670MHz.

The external tracking PLL also uses oscillator U101. Phase comparator U800 compares the signal from the external clock input and the clock from the system clock counter. The output signal from the comparator is filtered by U801, U806, U804 and surrounding components. The gain of the filter is variable with the switches U803 and U805. This is necessary for the PLL to work stable with different external clock speeds.

To decide how to set the gain switches the frequency of the external clock input can be measured by the ASIC U127. For high frequencies the clock has to be divided by counter U123.

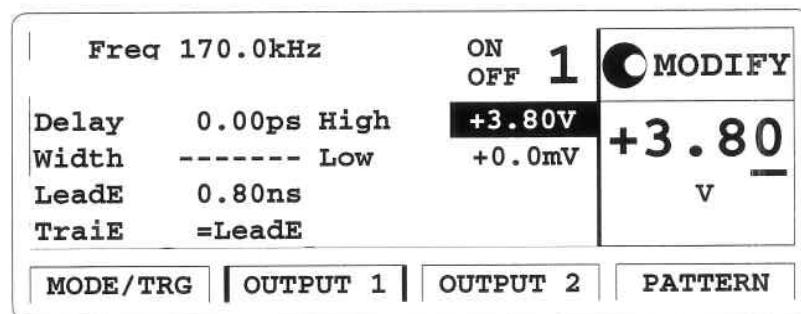

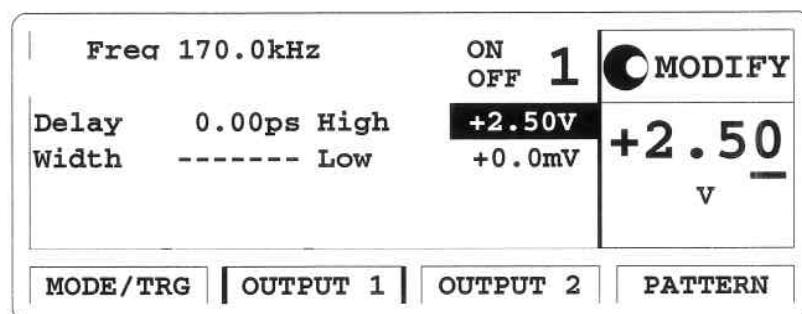

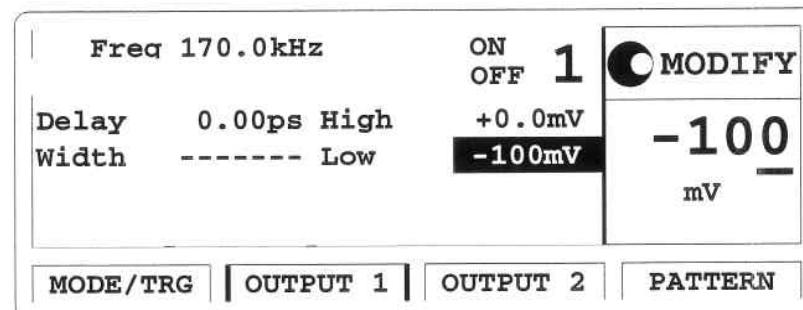

**MCLK Divider** (Sheet 14)

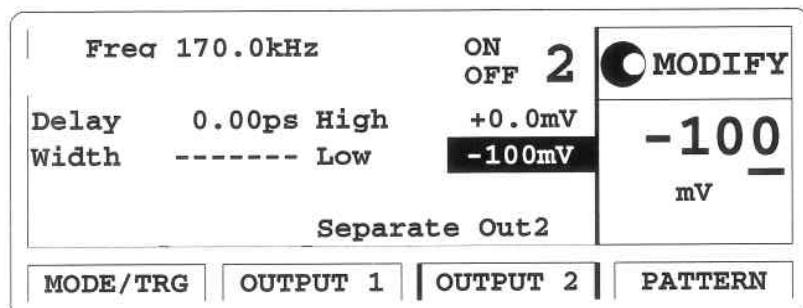

For data output frequencies lower than 170kHz the MCLK has to be divided. Counter U107 and flip-flop U108 allow division up to 512 while maintaining a dutycycle of the output signal of 50%. Multiplexer U103 selects if a divided or undivided MCLK will be distributed.

**System Clock Divider** (Sheet 15)

The System Clock divider has 2 reasons:

First it divides the MCLK so that the tracking PLL is able to synchronize the MCLK frequency onto an external clock signal (See PLL description).

Second it generates the Clock for Start/Stop circuitry.

The divider is built from two cascaded 8bit counters (U112/113) and a following flip-flop (U110), all 3 components are clocked by the MCLK. Again a multiplexer (U111) selects between divided and undivided clock.

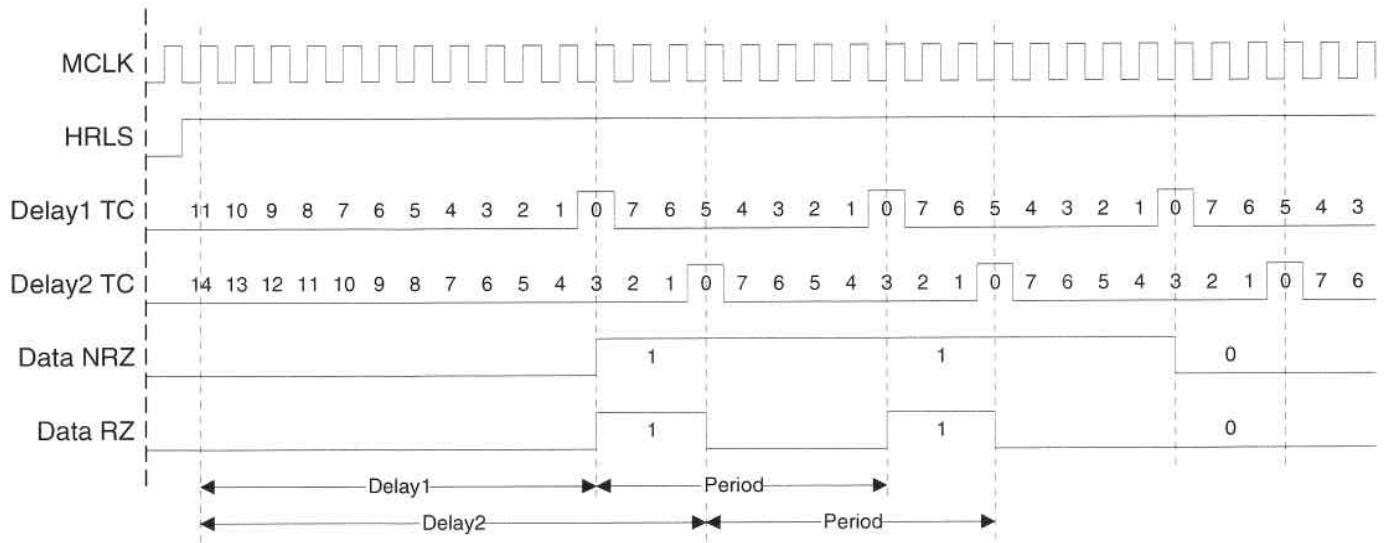

**Start/Stop Logic** (Sheet 20)

The timing system of the 81130A board uses a non-startable MCLK.

This is to increase the accuracy of the timing system, because units with a startable clock system tend to decrease the pulselwidth/period of the first few output-cycles.

So to start the system another signal, called HRLS (High Run Low Stop), enables clock processing at the end of the clock

distribution tree. HRLS is distributed in parallel with the MCLK. The  $\mu$ P or a signal at the external input can start, stop or gate pulse/data generation of the board. Because these signals are asynchronous they have to be synchronized to the board clock. This is done in two steps, first synchronizing to the System Clock (U812/813/815) and then to the MCLK (U817).

#### **MCLK and HRLS Inputs and Outputs**

The MCLK and HRLS signals have to be distributed. ECL-splitter circuits U820 and U821 generate 8 copies of these signals. The data generation section is running with one of these signals, but can run with an external HRLS and MCLK signal also. Two other splitter-circuits (U822/823) generate more copies for use in the data generation section of the board.

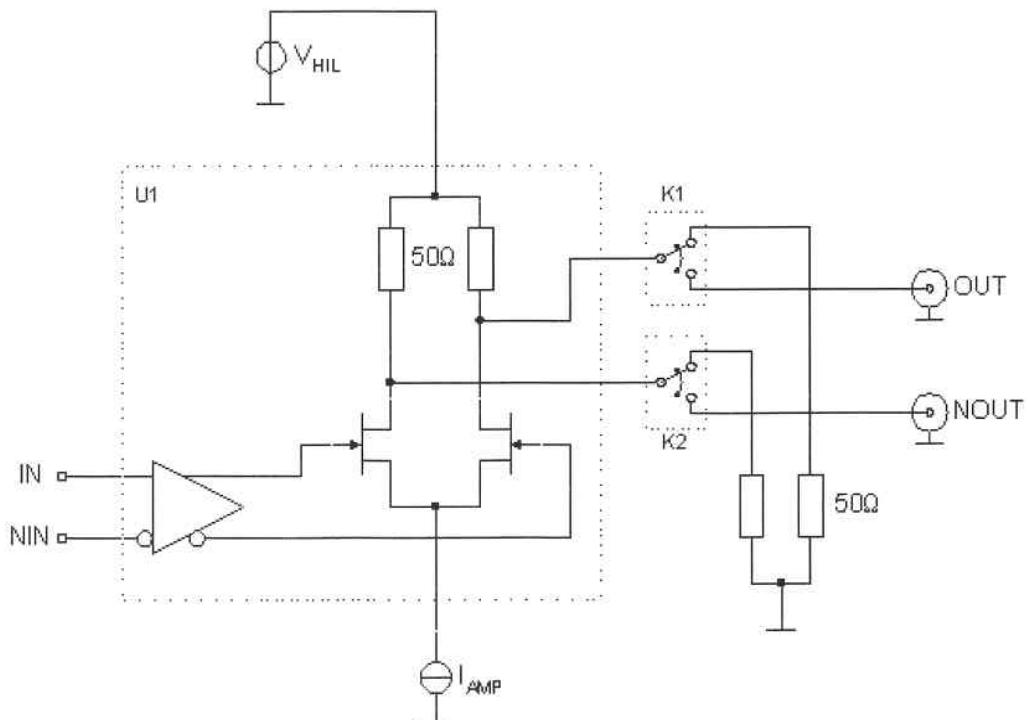

#### **Trigger Divider and Output (Sheets 22 and 23)**

The trigger output generates either a periodical clock signal or a sequence trigger signal.

Counters U406 and U407 divide the MCLK signal to generate the periodical clock signal. The divider ratio can be in the range of 1 to 65536 (16-bit divider). Multiplexer U403 selects between divide ratio 1, 2 or variable or sequence trigger.

The board sequencer generates a sequence trigger signal, which is written into the FIFO U600 (sheet 9). In this trigger mode the trigger counter generates the read clock for the FIFO. After levelshifting and retiming of the data it is coupled to the MUX U403.

The output signal of that MUX drives the trigger amplifier, which is composed of a splitter buffer U412, levelshifting diodes CR400 and CR401 and two differential amplifiers build mainly of transistors Q401 to Q404.

The trigger amplifier has variable output levels. DAC U414 and current sources U422/Q405 and U422/Q406 generate the amplitude current. DAC U414 and U415/Q407/Q408 generate the highlevel voltage.

#### **Sequencer Clock Divider**

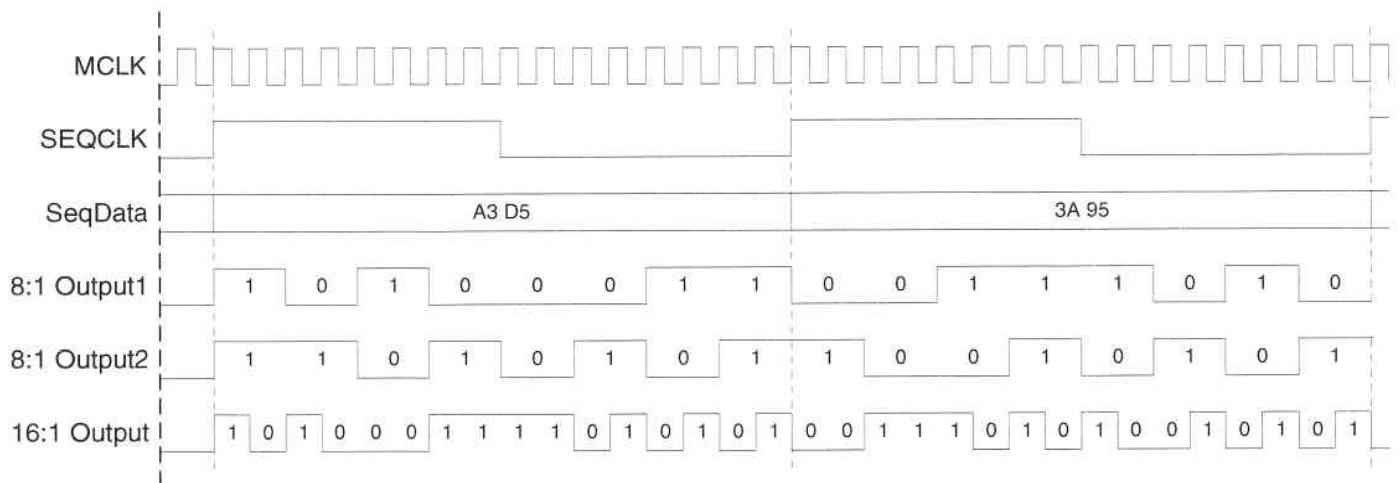

The sequencer (description see below) has an upper operating frequency limit of 42MHz. So it cannot run with the MCLK signal directly. The sequencer clock counter, build with U116, U117 and U122, is gated by HRLS and divides the MCLK by a minimum ratio of 16. The maximum divide ratio is 65536 (16 bit).

#### **Sequencer**

The basic architecture of the cell sequencer is a Moore state machine

Basically the state machine is implemented with memory (SRAM) with the address lines used as inputs. The outputs of the memory are the outputs of the state machine. Some of the outputs are fed back to inputs; they are called state bits and represent the test state. Depending on the test state the state machine can have different reactions to the inputs. Inputs and outputs are clocked into registers, so reactions take place at defined time stamps.

##### **Sequencer Inputs:**

- 3 TC outputs of the counter CPLD

- 7 state bits

- $\mu$ P-event

- external event

##### **Sequencer Outputs:**

- 7 control signals for the counters

- 21 load bits for the counters

- 7 state bits

- a  $\mu$ P interrupt bit

- trigger signal

The Counter CPLD comprises three 20bit counter. Each counter

generates a TC signal at a counter value of 100000hex. The TC propagates through another register in the MUX PLD, so that the sequencer receives a TC at 100001hex.

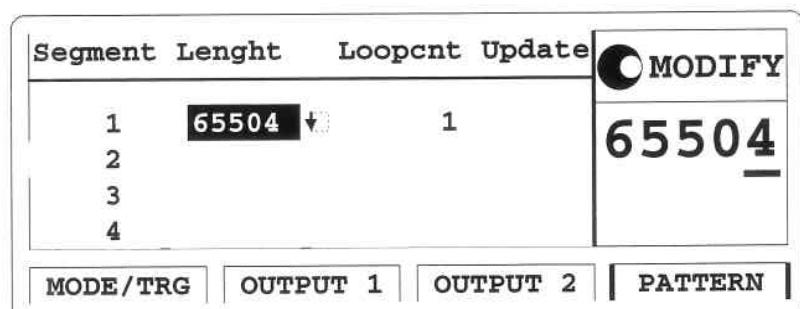

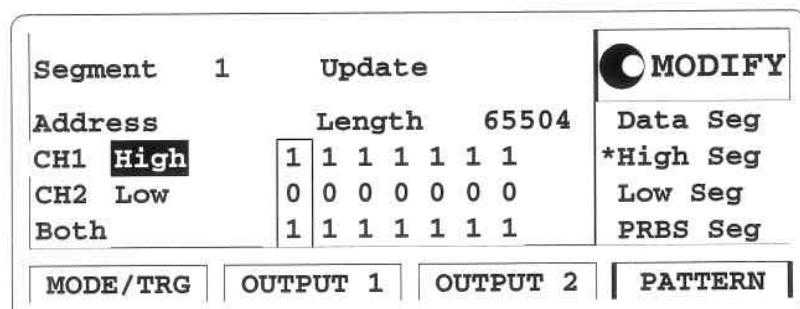

One counter counts the length of address segments, a second counter counts loops, and the third counter is the address counter, which generates the address for the data RAM. The address counter has a special shadow register where it can store the actual count value in case it is loaded. The value of the shadow register can be reloaded into the counter under control of the sequencer.

Because all counters get their load value from the same inputs just one counter can be loaded at a time (except the counters shall be loaded with the same value).

Every counter has 2 control inputs, load-enable and count-enable (LD and CE), that determine whether the counter stops, counts or loads a new value.

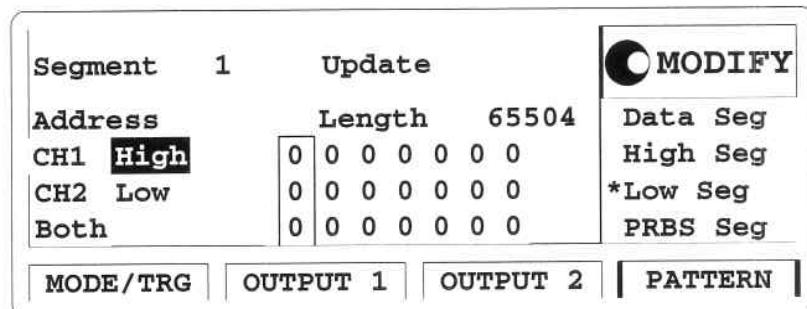

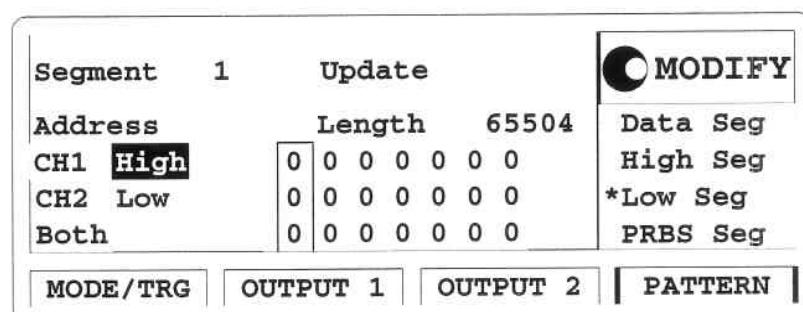

#### **Data RAM and FIFO's ((Sheets 9 and 10)**

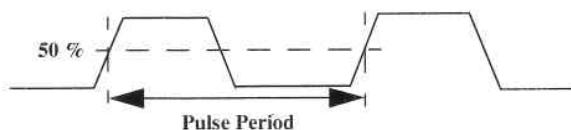

The Data RAM (64k\*16, U601/621) contains the user pattern. It is addressed from the Counter CPLD. Because the RAM is just 64k words deep only 16 of the 20 address bits are used. The RAM is upgradable to 256k.