# Keysight D9030DDRC DDR3 Compliance Test Application

Methods of Implementation

# **Notices**

© Keysight Technologies 2021

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### Software Version

Version 2.70.0.0 or greater

#### Edition

November 2021

Available in electronic format only

Keysight Technologies 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE. IN FUTURE EDITIONS. FURTHER. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES. EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN. INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS **COVERING THE MATERIAL IN THIS** DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

# **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

#### Safety Notices

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# DDR3 Compliance Test Application — At A Glance

The Keysight D9030DDRC DDR3 Compliance Test is a DDR3 (Double Data Rate 3) test solution that covers electrical, clock, and timing parameters of the JEDEC (Joint Electronic Device Engineering Council) specifications. The software helps you in testing all the un-buffered DDR3 device under test (DUT) compliance, with the Keysight Infiniium oscilloscopes.

There are 2 main categories of test modes:

- Compliance Tests These tests are based on the DDR3 JEDEC compliance specifications and are compared to corresponding compliance test limits.

- Custom Tests These tests are not based on any compliance specification. The primary use of these tests is to perform signal debugging.

#### The DDR3 Compliance Test:

- Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- · Automatically checks for proper oscilloscope configuration.

- · Automatically sets up the oscilloscope for each test.

- · Allows you to determine the number of trials for each test, with the new multi trial run capability.

- Provides detailed information of each test that has been run. The result of maximum 64 worst trials can be displayed at any one time.

- Creates a printable HTML report of the tests that have been run.

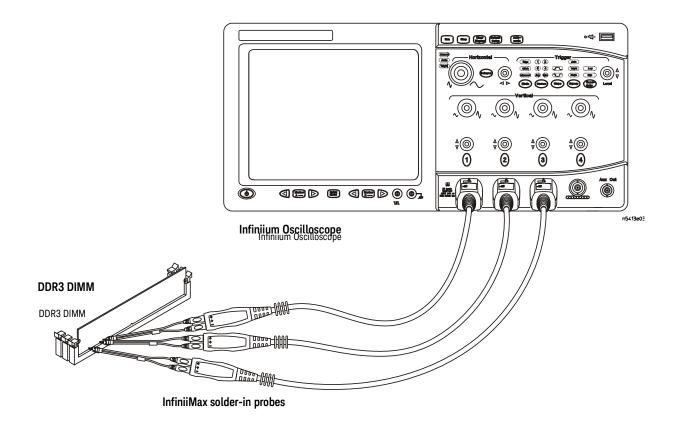

The minimum number of probes required for the tests are:

- · Clock tests 1 probe

- Electrical tests 3 probes

- · Timing tests 3 probes

- Custom tests 3 probes

#### NOTE

The tests performed by the DDR3 Compliance Test are intended to provide a quick check of the physical layer performance of the DUT. These testing are not a replacement for an exhaustive test validation plan.

DDR3 SDRAM electrical, clock and timing test standards and specifications are described in the *JEDEC* document. For more information, please refer to the JEDEC web site at <a href="https://www.jedec.org">www.jedec.org</a>.

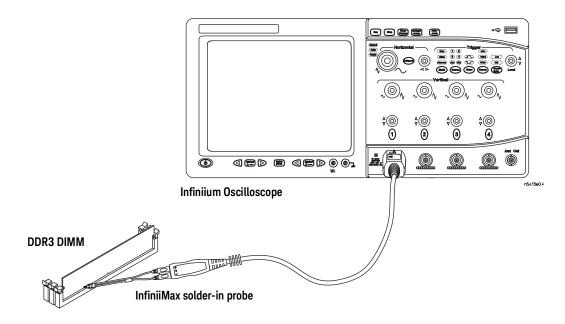

#### Required Equipment and Software

In order to run the DDR3 automated tests, you need the following equipment and software:

- D9030DDRC DDR3 Test Application software

- · Use one of the following Oscilloscope models:

- Keysight DSO9000A-Series, DSO90000A-Series and DSOX90000A / Q / Z / V-Series

Oscilloscopes with a minimum bandwidth of 8.0 GHz (recommended) for accurate

measurements. For faster speed grade devices, a minimum bandwidth of 13.0 GHz

bandwidth is recommended.

- Keysight UXR Oscilloscope

- · Keysight MXR Oscilloscope

- The minimum version of Infiniium oscilloscope software (see the D9030DDRC test application release notes).

- D9030DDRC DDR3 Compliance Test Application software license

- RAM reliability test software.

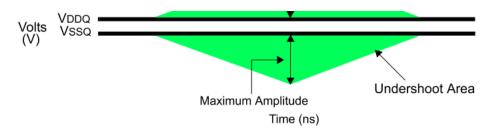

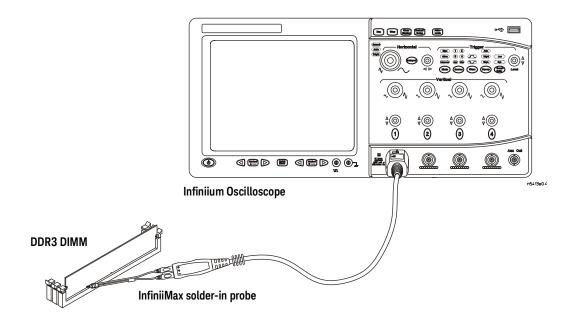

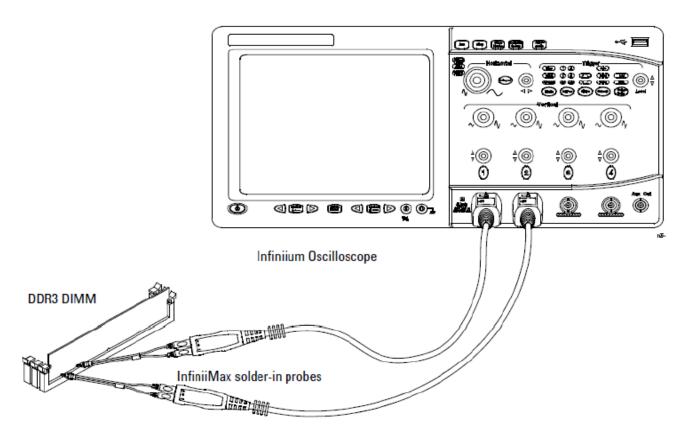

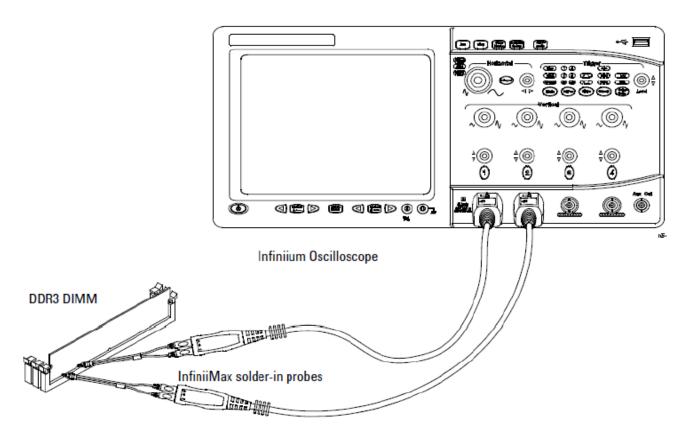

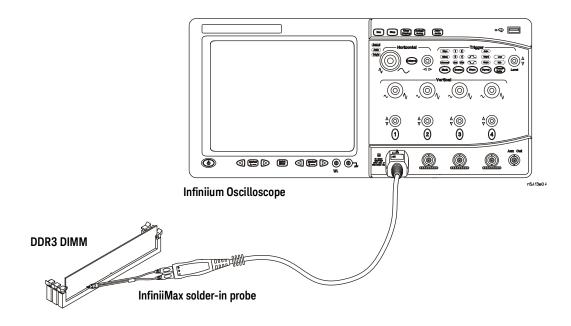

- 1169A/B, 1168A/B, 1134A/B, 1132A/B or 1131A/B InfiniiMax probe amplifiers.

- N5381A/B or E2677A/B differential solder-in probe head, N5425A/B ZIF probe head or N5426A ZIF tips, E2678A/B differential socketed probe head.

- Any computer motherboard system that supports DDR3 memory.

- Keyboard, qty = 1, (provided with the Keysight Infiniium oscilloscope)

- Mouse, qty = 1, (provided with the Keysight Infiniium oscilloscope)

- Precision 3.5 mm BNC to SMA male adapter, Keysight p/n 54855-67604, qty = 2 (provided

- with the Keysight 54855A and 80000B series oscilloscopes)

- 50-ohm Coax Cable with SMA Male Connectors 24-inch or less RG-316/U or similar, qty = 2, matched length

- · Keysight also recommends using a second monitor to view the compliance test application.

NOTE Keysight D9030DDRC DDR3 Compliance Test Application supports MXR oscilloscope.

Below are the required licenses:

- D9030DDRC DDR3 Compliance Test Application license.

- E2688A Serial Data Analysis and Clock Recovery software license.

Following table displays the sampling rates for Keysight 90000 X-Series oscilloscope and UXR-Series oscilloscope:

Table 1 Sampling Rates for 90000X-Series Oscilloscope and UXR-Series Oscilloscope

| Keysight 90000 X-Series Oscilloscope Sampling Rates | Keysight UXR -Series Oscilloscope Sampling Rates |

|-----------------------------------------------------|--------------------------------------------------|

| MAX (Default)*                                      | MAX (Default)*                                   |

|                                                     | 128 GSa/s                                        |

| 80 GSa/s                                            | 64 GSa/s                                         |

| 40 GSa/s                                            | 32 GSa/s                                         |

| 20 GSa/s                                            | 16 GSa/s                                         |

| 10 GSa/s                                            | 08 GSa/s                                         |

<sup>\*</sup> The MAX sampling rate values are different for 90000X-Series and UXR-Series oscilloscope. For 90000X-Series, the MAX value is 80 GSa/s, and for UXR-Series, the MAX value is 128 GSa/s.

#### In This Book

This manual describes the tests that are performed by the DDR3 Compliance Test in more detail; it contains information from (and refers to) the *JEDEC specifications*, and it describes how the tests are performed.

- Chapter 1, "Installing the DDR3 Compliance Test Application" shows how to install and license the automated test application software (if it was purchased separately).

- Chapter 2, "Preparing to Take Measurements" shows how to start the DDR3 Compliance Test and gives a brief overview of how it is used.

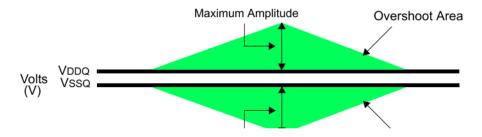

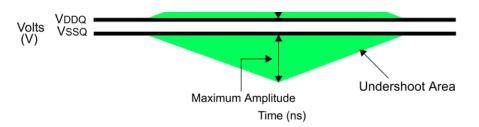

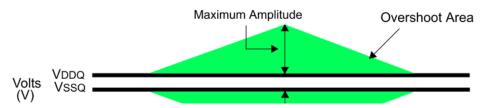

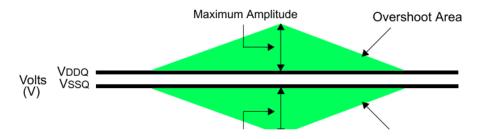

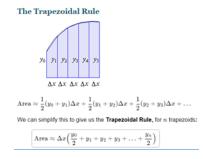

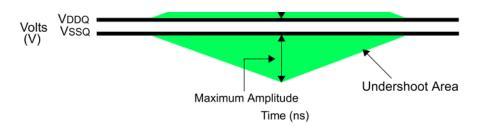

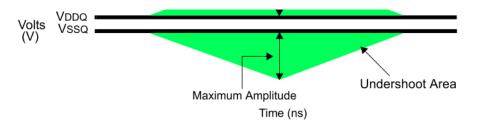

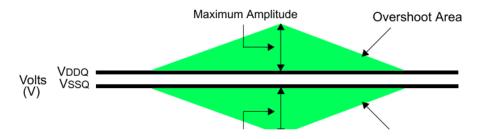

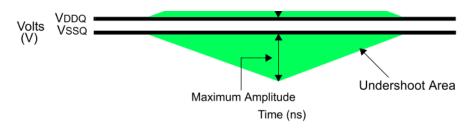

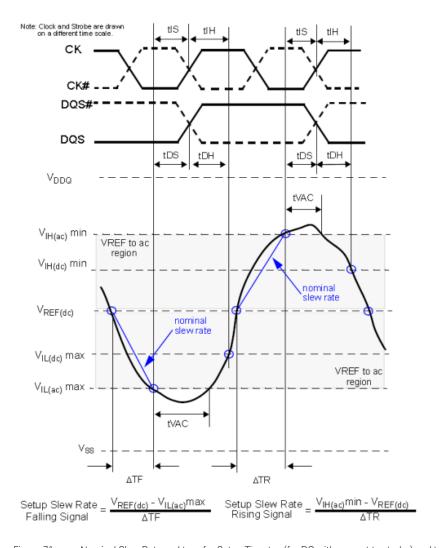

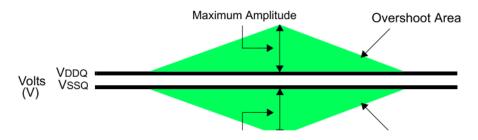

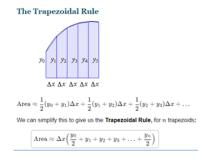

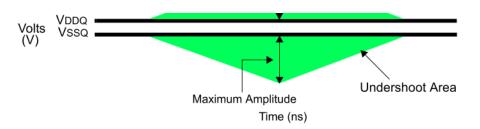

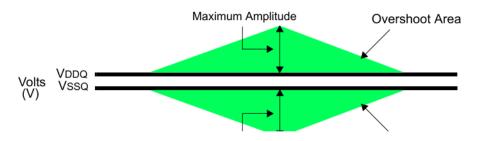

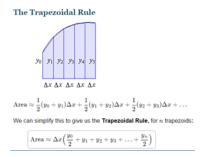

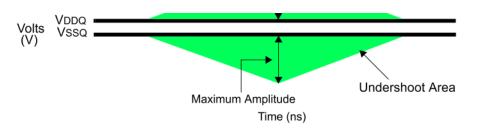

- Chapter 3, "Clock Plus Tests Group" describes the V<sub>SEH</sub> and V<sub>SEL</sub> tests for Clock Plus signals and the AC overshoot and undershoot tests probing and method of implementation.

- Chapter 4, "Clock Minus Tests Group" describes the V<sub>SEH</sub> and V<sub>SEL</sub> tests for Clock Minus signals and the AC overshoot and undershoot tests probing and method of implementation.

- Chapter 5, "Clock Plus and Minus Cross Point Tests Group" describes the V<sub>IX</sub> test for Clock Plus and Minus Point.

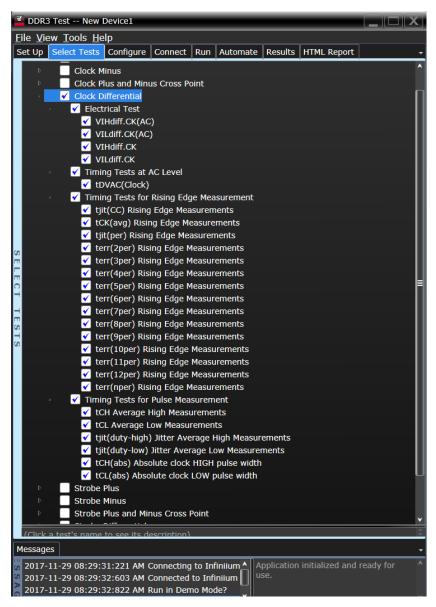

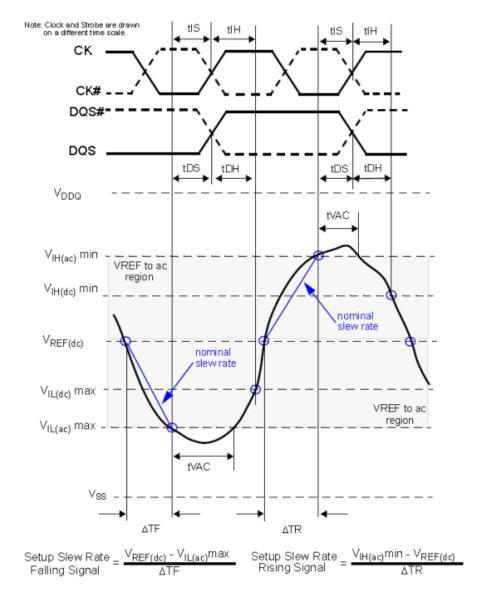

- Chapter 6, "Clock Differential Tests Group" shows how to run various Electrical Test, Timing Tests at AC Level, Timing Tests for Rising Edge Measurement and Timing Tests for Pulse Measurement.

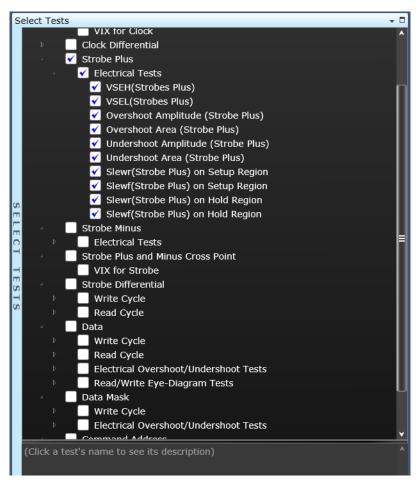

- Chapter 7, "Strobe Plus Tests Group" describes the V<sub>SEH</sub> and V<sub>SEL</sub> tests for Strobe Plus signals

and the AC overshoot and undershoot tests probing and method of implementation.

- Chapter 8, "Strobe Minus Tests Group" describes the V<sub>SEH</sub> and V<sub>SEL</sub> tests for Strobe Minus signals and the AC overshoot and undershoot tests probing and method of implementation.

- Chapter 9, "Strobe Plus and Minus Cross Point Tests Group" describes the V<sub>IX</sub> test for strobe plus and minus point.

- Chapter 10, "Strobe Differential Tests Group" shows how to run various Electrical Test and Timing Tests.

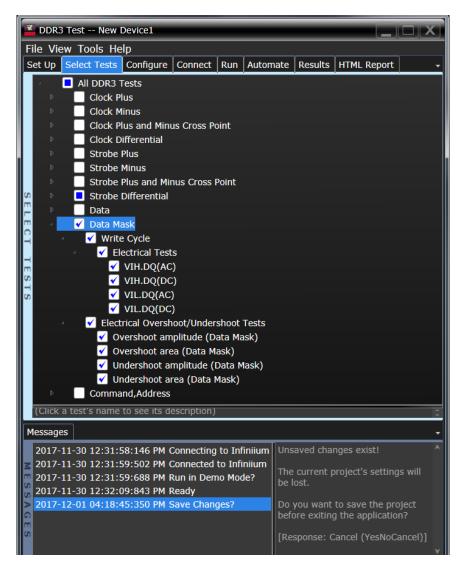

- · Chapter 11, "Data Tests Groups" shows how to run various Write Cycles and Read Cycles.

- · Chapter 12, "Data Mask Tests Group" describes how to run the data mask timing tests.

- Chapter 13, "Command, Address Tests Group" describes the command and address timing tests

which include the address and control input setup time as well as the address and control input

hold time.

- · Chapter 14, "Chip Select Tests Group" describes how to run the chip select tests.

- · Chapter 15, "Clock Enable Tests Group" describes how to run the clock enable tests.

#### See Also

- The D9030DDRC DDR3 Compliance Test's Online help, which describes:

- D9030DDRC DDR3 Automated Testing—At a Glance

- Starting the D9030DDRC DDR3 Test Application

- · Creating or Opening a Test Project

- Setting Up the Test Environment

- Selecting Tests

- Configuring Tests

- Verifying Physical Connections

- Running Tests

- Configuring Automation in the Test Application

- · Viewing Results

- Viewing HTML Test Report

- Exiting the Test Application

- Additional Settings in the Test App

# Contents

DDR3 Compliance Test Application — At A Glance In This Book 7 1 Installing the DDR3 Compliance Test Application **Installing the Software** 18 Installing the License Key 19 Using Keysight License Manager 5 19 Using Keysight License Manager 6 20 22 2 Preparing to Take Measurements Calibrating the Oscilloscope 24 Starting the DDR3 Compliance Test Application 25 Correlation between Signal Group and PUT Signal requirements for test availability 30 3 Clock Plus Tests Group **Probing for Clock Plus Tests** 50 Test Procedure 51 52 **Electrical Tests** VSEH(Clock Plus) 52 54 VSEL(Clock Plus) Overshoot Amplitude / Area for Clock Plus Tests Undershoot Amplitude / Area for Clock Plus Tests 59 SlewR on Setup Region 61 62 SlewF on Setup Region SlewR on Hold Region 63 SlewF on Hold Region 64 4 Clock Minus Tests Group **Probing for Clock Minus Tests** 66

Test Procedure 67

**Electrical Tests**

VSEH(Clock Minus)

VSEL(Clock Minus)

68

68 70

Overshoot Amplitude / Area (Clock Minus) 72

|   | Undershoot Amplitude / Area (Clock Minus) 75 SlewR on Setup Region 77 SlewF on Setup Region 78 SlewR on Hold Region 79 SlewF on Hold Region 80                                                                                                                               |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | Clock Plus and Minus Cross Point Tests Group                                                                                                                                                                                                                                 |

|   | Probing for Clock Plus and Minus Cross Point Tests 82  Test Procedure 82                                                                                                                                                                                                     |

|   | VIX for Clock 84                                                                                                                                                                                                                                                             |

|   | VIXCA for Clock 86                                                                                                                                                                                                                                                           |

| 6 | Clock Differential Tests Group                                                                                                                                                                                                                                               |

|   | Probing for Clock Differential Tests 88  Test Procedure 89                                                                                                                                                                                                                   |

|   | Electrical Tests 91  VIHdiff.CK(AC) 91  VILdiff.CK(AC) 93  VIHdiff.CK(DC) 95  VILdiff.CK(DC) 97  VIHdiff.CK 99  VILdiff.CK 100                                                                                                                                               |

|   | Timing Tests at AC Level 102<br>tDVAC(Clock) 102                                                                                                                                                                                                                             |

|   | Timing Tests for Rising Edge Measurement 103  tjit(CC) Rising Edge Measurement 103  tCK(avg) Rising Edge Measurement 105  tjit(per) Rising Edge Measurement 108  tERR(nper) Rising Edge Measurement 110  tCK(abs) Rising Edge Measurement 114                                |

|   | Timing Tests for Pulse Measurement 115  tCH(avg) Average High Measurement 115  tCL(avg) Average Low Measurement 117  tJIT(duty-high/low) Jitter Average High/Low Measurements 119  tCH(abs) Absolute clock HIGH pulse width 121  tCL(abs) Absolute clock LOW pulse width 123 |

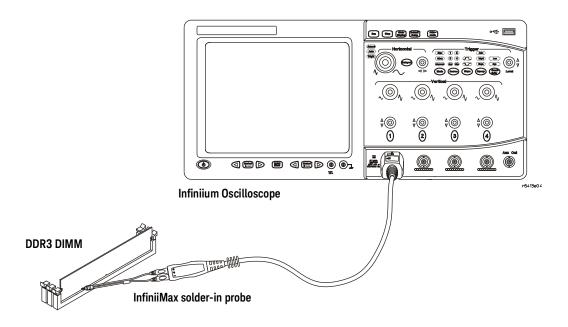

#### 7 Strobe Plus Tests Group

### **Probing for Strobe Plus Tests** 126

Test Procedure 127

#### Electrical Tests 128

VSEH(Strobes Plus) 128 VSEL(Strobes Plus) 130

Overshoot Amplitude / Area (Strobes Plus) 132 Undershoot Amplitude / Area (Strobes Plus) 135

SlewR on Setup Region 138

SlewF on Setup Region 139

SlewR on Hold Region 140

SlewF on Hold Region 141

#### 8 Strobe Minus Tests Group

#### Probing for Strobe Minus Tests 144

Test Procedure 145

#### Electrical Tests 146

VSEH(Strobes Minus) 146 VSEL(Strobes Minus) 148

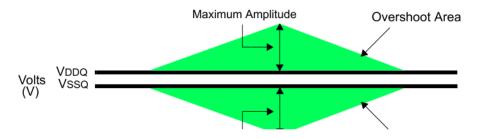

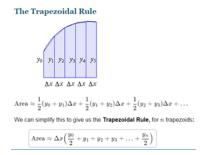

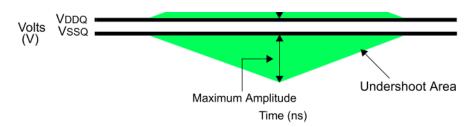

Overshoot Amplitude/Area (Strobes Minus) 150 Undershoot Amplitude/Area (Strobes Minus) 153

SlewR on Setup Region 156

SlewF on Setup Region 157

SlewR on Hold Region 158

SlewF on Hold Region 159

#### 9 Strobe Plus and Minus Cross Point Tests Group

#### **Probing for Strobe Plus and Minus Cross Point Tests** 162

Test Procedure 163

VIX for Strobe 164

VIXDQ - Strobe Cross Point Voltage Test 166

#### 10 Strobe Differential Tests Group

#### **Probing for Strobe Differential Tests** 170

Test Procedure 170

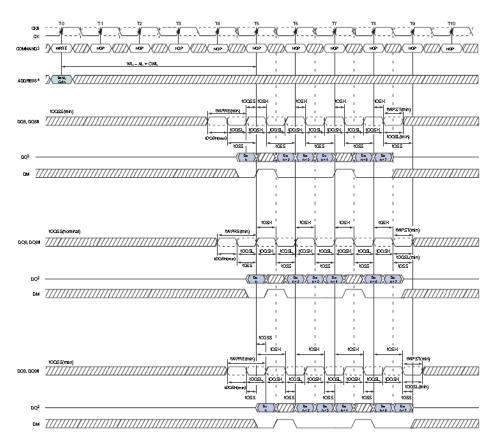

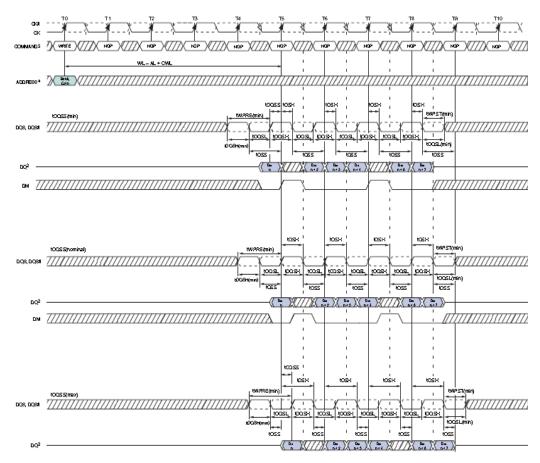

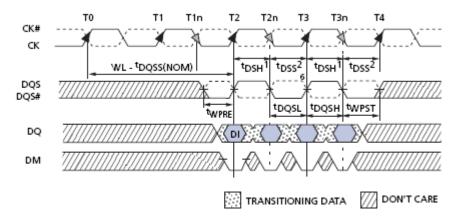

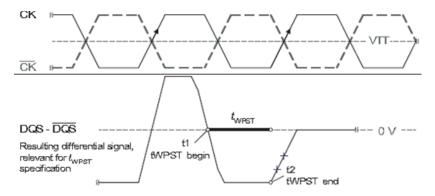

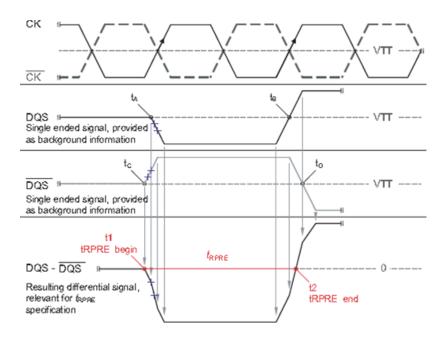

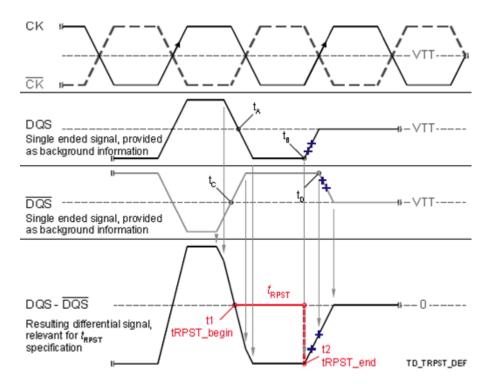

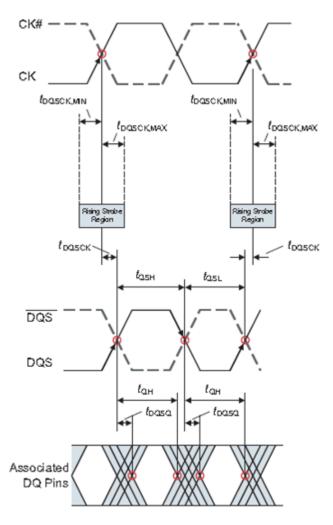

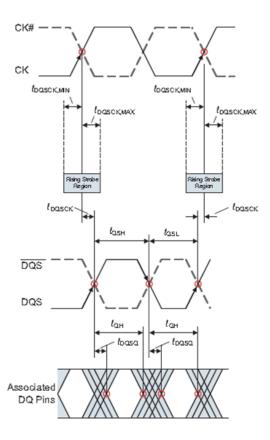

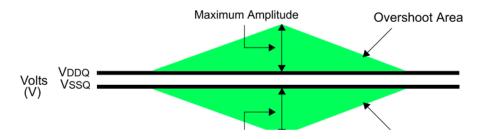

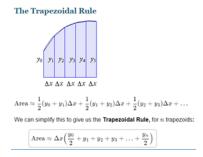

#### **Write Cycle Electrical Tests** 172 VIHdiff.DQS(AC) 172 174 VILdiff.DQS(AC) VIHdiff.DQS (DC) 176 VILdiff.DQS (DC) 178 VIHdiff.DQS 180 VILdiff.DQS 182 **Write Cycle Timing Tests** 184 tDQSS 184 tDQSH 186 tDQSL 188 tDSS 190 tDSH 192 tWPRE 194 tWPST 196 tDVAC(Strobe) 198 **Read Cycle Electrical Tests** 199 VOHdiff(AC) 199 201 VOLdiff(AC) 203 SRQdiffR 205 SRQdiffF 207 **Read Cycle Timing Tests** tHZ(DQS) 207 tHZ(DQS) for Low Power 209 tLZ(DQS) 211 tLZ(DQS) for Low Power 213 tRPRE 215 tRPST 217 tQSH 219 tQSL 220 tDQSCK 221

#### 11 Data Tests Groups

# **Probing for Data Tests** 224

Test Procedure 225

#### **Write Cycle Electrical Tests** 227 VIH.DQ(AC) 227 229 VIH.DQ(DC) VIL.DQ(AC) 232 VIL.DQ(DC) 235 237 SlewR on Setup Region 238 SlewF on Setup Region 239 SlewR on Hold Region 240 SlewF on Hold Region 241 **Write Cycle Timing Tests** tDS(base) 241 244 tDH(base) 247 tDS-Diff(derate) tDH-Diff(derate) 256 tDIPW 265 tVAC(Data) 267 **Read Cycle Electrical Tests** 268 VOH(AC) 268 270 VOH(DC) VOL(AC) 272 274 VOL(DC) SRQseR 276 278 SRQseF **Read Cycle Timing Tests** 280 280 tHZ(DQ) tLZ(DQ) 282 tHZ(DQ) for Low Power 284 tLZ(DQ) for Low Power 286 288 tDQSQ tQH 290 292 **Electrical Overshoot/Undershoot Tests** Overshoot Amplitude/Area (Data) 292 Undershoot Amplitude/Area (Data) 295 297 Read/Write Eye-Diagram Tests 297 User Defined Real-Time Eye Diagram Test For Read Cycle User Defined Real-Time Eye Diagram Test For Write Cycle 299

302

#### Keysight D9030DDRC DDR3 Compliance Test Application Methods of Implementation

Test Procedure

**Probing for Data Mask Tests**

303

12 Data Mask Tests Group

#### **Electrical Tests** 304 VIH.DQ(AC) 304 306 VIH.DQ(DC) VIL.DQ(AC) 308 VIL.DQ(DC) 310 312 SlewR on Setup Region 313 SlewF on Setup Region SlewR on Hold Region 314 SlewF on Hold Region 315 **Timing Tests** 316 tDS(base) 316 319 tDH(base) 322 tDS-Diff(derate) tDH-Diff(derate) 331 tDIPW 340 342 tVAC(Data Mask) **Electrical Overshoot/Undershoot Tests** 343 Overshoot Amplitude/Area (Data Mask) 343

# 13 Command, Address Tests Group

# **Probing for Command, Address Tests** 350

Undershoot Amplitude/Area (Data Mask)

346

Test Procedure 350

#### **Electrical Tests** 352 352 VIH.CA(AC) VIH.CA(DC) 354 VIL.CA(AC) 356 VIL.CA(DC) 358 360 SlewR on Setup Region SlewF on Setup Region 361 SlewR on Hold Region 362 363 SlewF on Hold Region Overshoot Amplitude/Area (Command, Address) 364 Undershoot Amplitude/Area (Command, Address) 367

403

#### **Timing Tests** 369 tIS(base) 369 372 tIH(base) tIS(derate) 374 tIH(derate) 382 tISCA(base) 391 393 tIHCA(base) tISCA(derate) 395 397 tIHCA(derate) tIPW 399 tIPWCA 401 tVAC(CA) 402 **Eye-Diagram Tests** 403 User Defined Real-Time Eye Diagram Test For Command Address

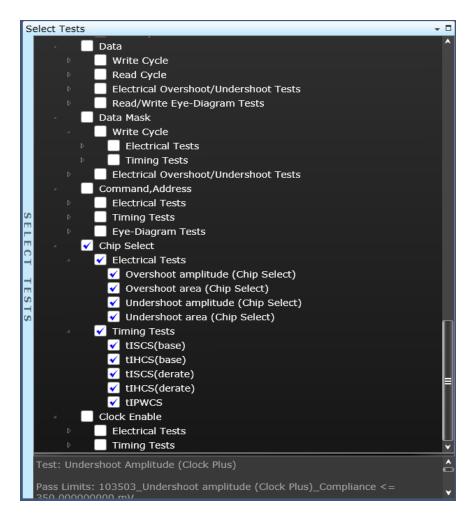

#### 14 Chip Select Tests Group

#### Probing for Chip Select Tests 406

Test Procedure 407

Electrical Test 408

Overshoot Amplitude/Area (Chip Select Tests) 408 Undershoot Amplitude/Area Chip Select Tests 410

Timing Test 412

tISCS(base) 412

tIHCS(base) 414

tISCS(derate) 416

tIHCS(derate) 419

tIPWCS 422

#### 15 Clock Enable Tests Group

#### **Probing for Clock Enable Tests** 426

Test Procedure 427

Electrical Test 428

Overshoot Amplitude / Area) (Clock Enable) 428 Undershoot Amplitude / Area (Clock Enable) 430

Timing Tests 432

tCKE 432 tISCKE 434 tIHCKE 436 Contents

Keysight D9030DDRC DDR3 Compliance Test Application Methods of Implementation

# 1 Installing the DDR3 Compliance Test Application

Installing the Software / 18

Installing the License Key / 19

If you have purchased the D9030DDRC DDR3 Compliance Test Application separately, you need to install the software and license key.

# Installing the Software

- 1 Make sure you have the minimum version of Infiniium oscilloscope software (see the Keysight D9030DDRC DDR3 Compliance Test Application release notes) by choosing **Help > About Infiniium...** from the main menu.

- 2 To obtain the D9030DDRC, go to Keysight website: http://www.keysight.com/find/D9030DDRC.

- 3 The link for D9030DDRC will appear. Click on it and follow the instructions to download and install the application software.

# Installing the License Key

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

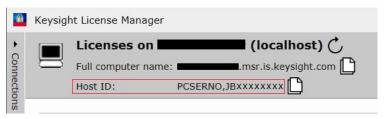

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

Figure 1 Viewing the Host ID information in Keysight License Manager 5

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

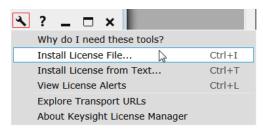

- 3 From the configuration menu, use one of the options to install each license file.

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to Keysight License Manager 5 Supporting Documentation.

#### 1

#### Using Keysight License Manager 6

To view and copy the Host ID from Keysight License Manager 6:

- 1 Launch Keysight License Manager 6 on your machine, where you wish to run the Test Application and its features.

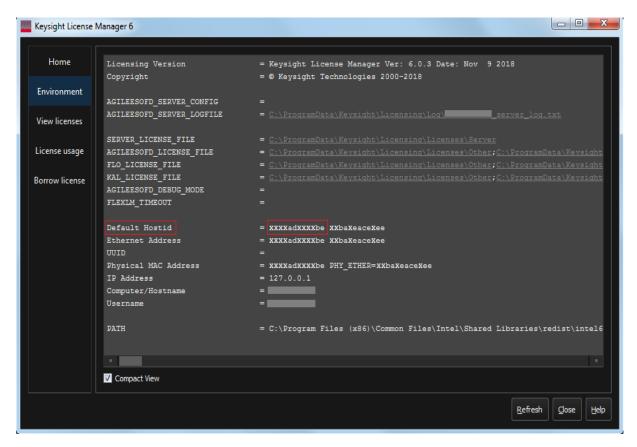

- 2 Copy the Host ID, which is the first set of alphanumeric value (as highlighted in Figure 3) that appears in the Environment tab of the application. Note that x indicates numeric values.

Figure 3 Viewing the Host ID information in Keysight License Manager 6

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

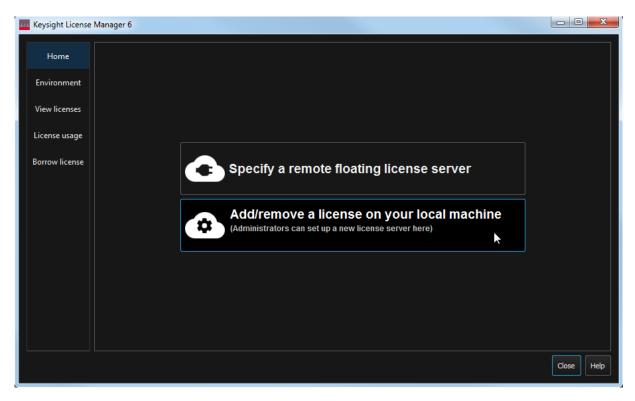

- 2 Launch Keysight License Manager 6.

- 3 From the Home tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to Keysight License Manager 6 Supporting Documentation.

1 Installing the DDR3 Compliance Test Application

Keysight D9030DDRC DDR3 Compliance Test Application Methods of Implementation

# 2 Preparing to Take Measurements

Calibrating the Oscilloscope / 24 Starting the DDR3 Compliance Test Application / 25 Correlation between Signal Group and PUT / 28 Signal requirements for test availability / 30

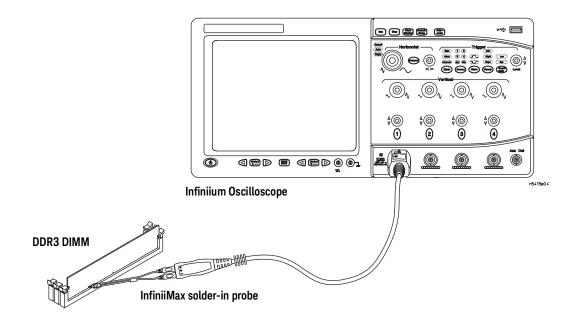

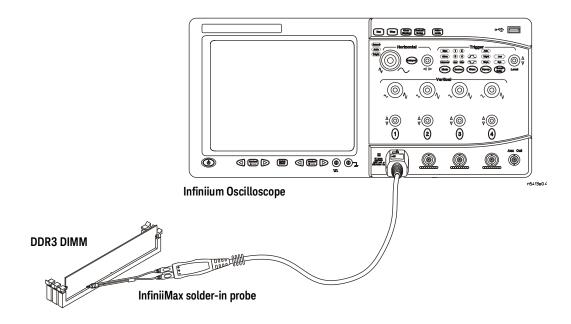

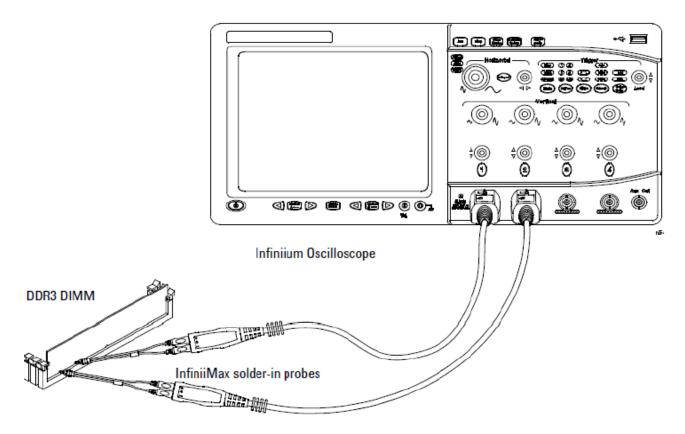

Before running the DDR3 automated tests, you should calibrate the oscilloscope and probe. No test fixture is required for this DDR3 application. After the oscilloscope and probe have been calibrated, you are ready to start the Keysight D9030DDRC DDR3 Compliance Test Application and perform the measurements.

# Calibrating the Oscilloscope

If you haven't already calibrated the Oscilloscope, refer to the documentation provided with the Oscilloscope model being used to perform tests.

NOTE

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the **Utilities** > **Calibration** menu.

NOTE

If you switch cables between channels or other oscilloscopes, it is necessary to perform cable and probe calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.

#### Starting the DDR3 Compliance Test Application

- 1 Ensure that the RAM reliability test software is running in the computer system where the Device Under Test (DUT) is attached. This software performs tests to all unused RAM in the system by producing a repetitive burst of read-write data signals to the DDR3 memory.

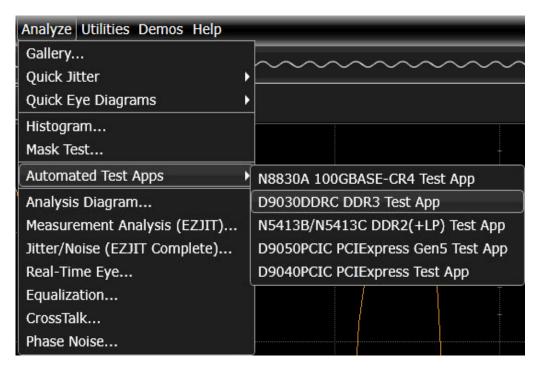

- 2 To start the Keysight D9030DDRC DDR3 Compliance Test Application: From the Infiniium oscilloscope's main menu, choose **Analyze** > **Automated Test Apps** > **D9030DDRC DDR3 Test App**.

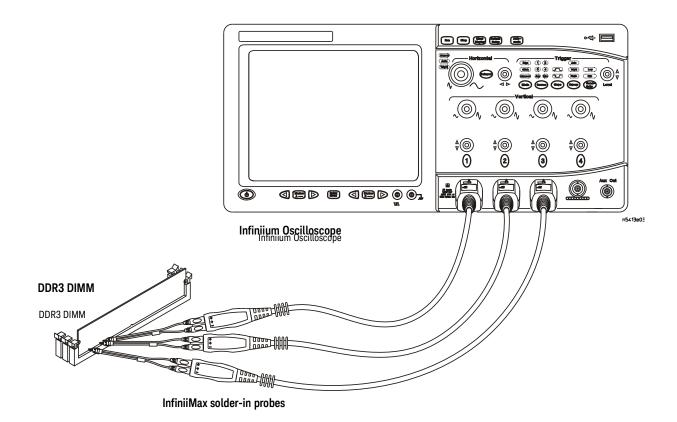

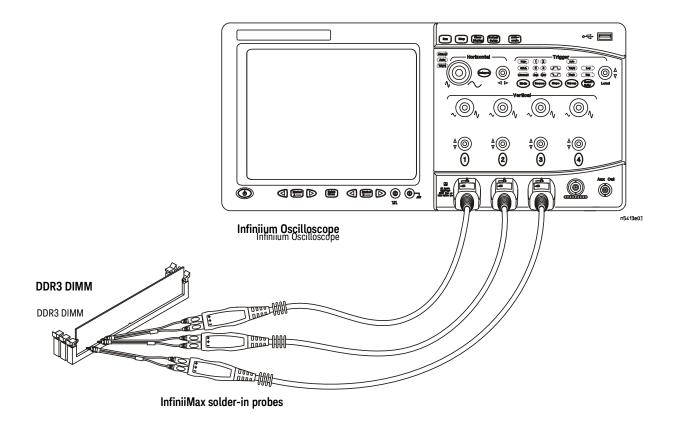

Figure 5 Infiniium oscilloscope's main menu

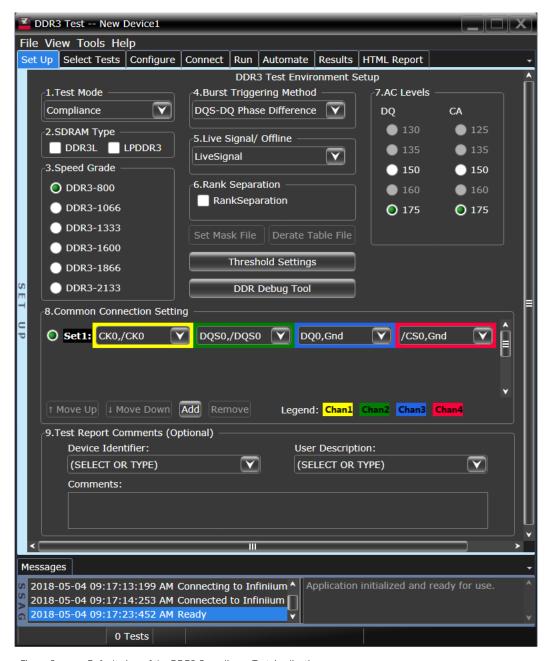

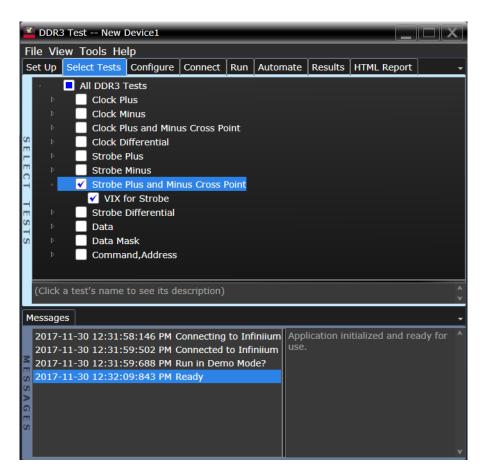

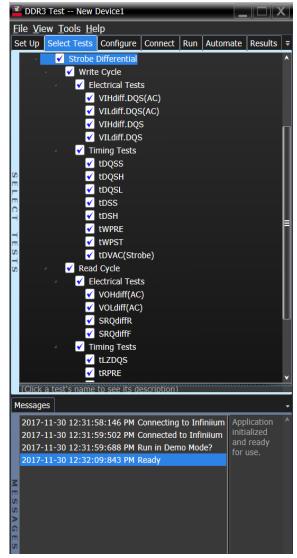

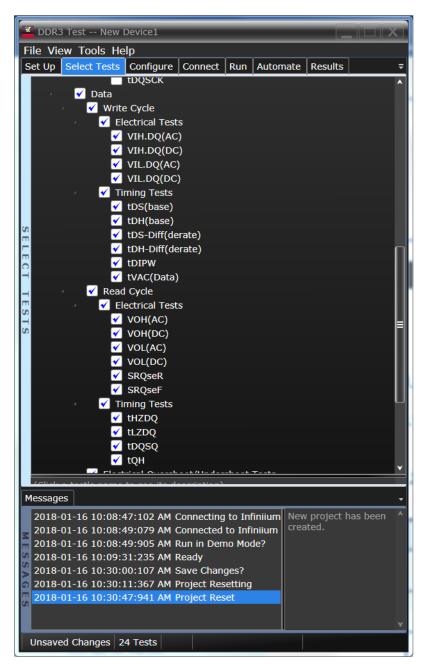

Figure 6 Default view of the DDR3 Compliance Test Application

NOTE

If the Keysight D9030DDRC DDR3Test App does not appear in the Automated Test Apps menu, then it has not been installed (see Chapter 1, "Installing the DDR3 Compliance Test Application")

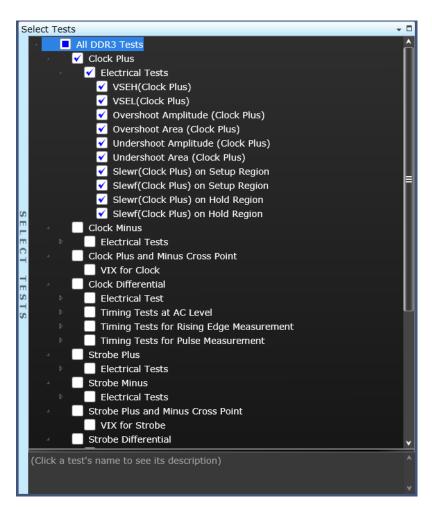

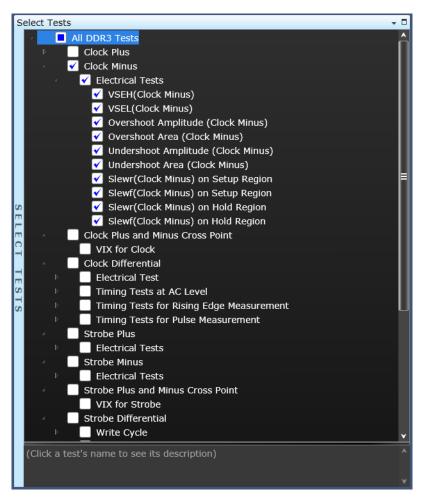

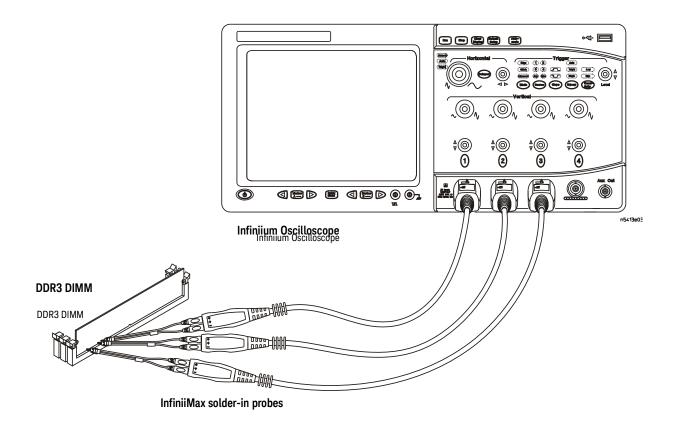

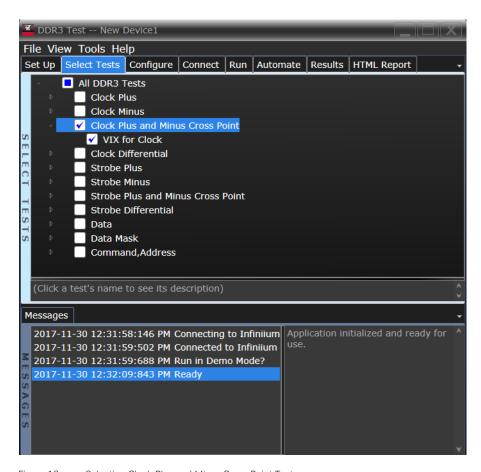

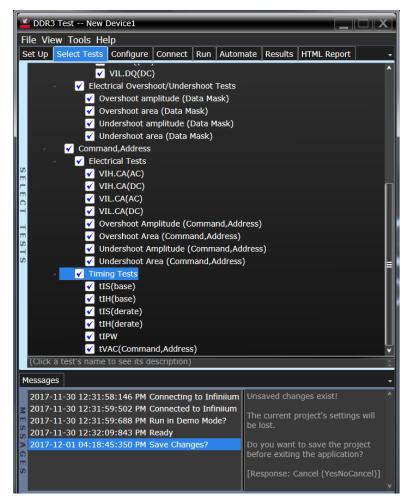

Figure 5 and Figure 6 show the DDR3 Compliance Test Application main window. The task flow pane, and the tabs in the main pane, show the steps you take in running the automated tests:

| Tab          | Description                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Up       | Lets you identify and set up the test environment, including information about the device under test.                                                                                                                                                                      |

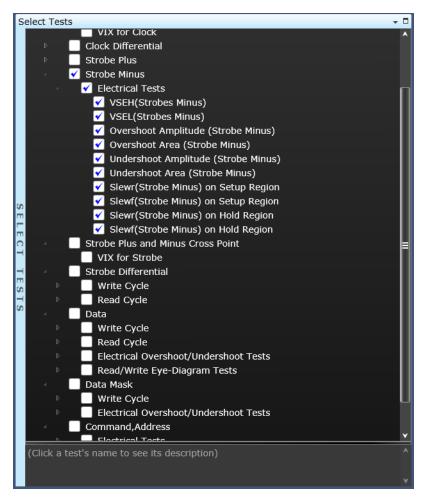

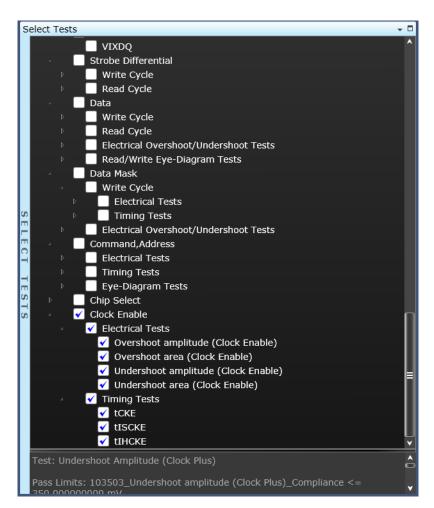

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |

| Configure    | Lets you configure test parameters. The information appears in the HTML report.                                                                                                                                                                                            |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests to be run.                                                                                                                                                                                |

| Run Tests    | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Automation   | Lets you construct scripts of commands that drive execution of the application.                                                                                                                                                                                            |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

# NOTE

When you close the DDR3 application, each channel's probe is configured as single-ended or differential depending on the last DDR3 test that was run.

# Correlation between Signal Group and PUT

Among the various options available under the **Set Up** tab of the Keysight D9030DDRC DDR3 Compliance Test Application, which filter the list of tests in the **Select Tests** tab; one of the features is the **Common Connection Setting**. Using this feature, when you select the Pin Under Test (PUT) that is connected to each Oscilloscope Channel, the Test Application displays one or more tests/test categories either as available or unavailable. **Table 2** and **Table 3** list the signal group for the corresponding PIN that you select using the **Common Connection Setting** feature.

The signal groups that are required to run various DDR3/DDR3L/LPDDR3 tests are:

- Clock Differential

- · Clock Plus

- Clock Minus

- Strobe Differential

- · Strobe Plus

- Strobe Minus

- Data

- Data Mask

- DDR3 CommandAddress

- DDR3\_CommandAddress\_ChipSelect

- LPDDR3\_CommandAddress

- · LPDDR3\_ChipSelect

- · LPDDR3\_ClockEnable

- · Not in Use (if a Channel does not have any test signal)

#### NOTE

The signal group "DDR3\_CommandAddress\_ChipSelect" is a subset of "DDR3 Command Address".

To make all such tests available, which require the signal group "DDR3\_CommandAddress", you may select either "DDR3\_CommandAddress" or "DDR3\_CommandAddress\_ChipSelect".

To make all such tests available, which require the signal group "DDR3\_Command\_Address\_ChipSelect" only, you must select only "DDR3\_CommandAddress\_ChipSelect". Selecting any other signal group will show such tests as unavailable.

Table 2 Correlation between Signal Group and selected PUT for DDR3/DDR3L tests

| Common Connection Setting PUT | Signal Type                  | Signal Group                   |

|-------------------------------|------------------------------|--------------------------------|

| Not_In_Use                    | NA                           | NotInUse                       |

| CK0,/CK0 to CK2,/CK2          | Clock_DCK0 to Clock_DCK2     | Clock Differential             |

| CKO,Gnd to CK2,Gnd            | Clock_SCKO to Clock_SCK2     | Clock Plus                     |

| /CKO,Gnd to /CK2,Gnd          | Clock_NCK0 to Clock_NCK2     | Clock Minus                    |

| DQS0,/DQS0 to DQS8,/DQS8      | Strobe_DDQS0 to Strobe_DDQS8 | Strobe Differential            |

| DQS0,Gnd to DQS8,Gnd          | Strobe_SDQS0 to Strobe_SDQS8 | Strobe Plus                    |

| /DQS0,Gnd to /DQS8,Gnd        | Strobe_NDQS0 to Strobe_NDQS8 | Strobe Minus                   |

| DQ0,Gnd to DQ71,Gnd           | Data_DQ0 to Data_DQ71        | Data                           |

| DM0,Gnd to DM7,Gnd            | DM_DM0 to DM_DM7             | Data Mask                      |

| /CS0,Gnd & /CS1,Gnd           | Control_NCS0 & Control_NCS1  | DDR3_CommandAddress_ChipSelect |

| BAO,Gnd to BA2,Gnd            | Control_BA0 & Control_BA2    |                                |

| /RAS,Gnd                      | Control_NRAS                 |                                |

| /WE,Gnd                       | Control_NWE                  |                                |

| /CAS,Gnd                      | Control_NCAS                 | DDR3_CommandAddress            |

| CKEO,Gnd & CKE1,Gnd           | Control_CKE0 & Control_CKE1  |                                |

| ODTO,Gnd & ODT1,Gnd           | Control_ODTO & Control_ODT1  |                                |

| A0,Gnd to A15,Gnd             | Address_A0 to Address_A15    |                                |

Table 3 Correlation between Signal Group and selected PUT for LPDDR3 tests

| Common Connection Setting PUT  | Signal Type                                    | Signal Group          |

|--------------------------------|------------------------------------------------|-----------------------|

| Not_In_Use                     | LP_NA_                                         | NotInUse              |

| CK_t,CK_c                      | LP_Clock_DCK                                   | Clock Differential    |

| CK_t,GND                       | LP_Clock_SCK                                   | Clock Plus            |

| CK_c,GND                       | LP_Clock_NCK                                   | Clock Minus           |

| DQS0_t,DQS0_C to DQS3_t,DQS3_c | LP_Strobe_DDQS0 to LP_Strobe_DDQS3             | Strobe Differential   |

| DQSO_t,GND to DQS3_t,GND       | LP_Strobe_SDQS0 to LP_Strobe_SDQS3             | Strobe Plus           |

| DQSO_c,GND to DQS3_c,GND       | LP_Strobe_NDQS0 to LP_Strobe_NDQS3             | Strobe Minus          |

| DQ0,GND to DQ31,GND            | LP_Data_DQ0 to LP_Data_DQ31                    | Data                  |

| DM0,GND to DM3,GND             | LP_DM_DM0 to LP_DM_DM3                         | Data Mask             |

| CS_n,GND                       | LP_Control_NCS                                 | LPDDR3_ChipSelect     |

| CKE,GND                        | LP_Control_CKE                                 | LPDDR3_ClockEnable    |

| CAO,GND to CA9,GND             | LP_CommandAddress_CA0 to LP_CommandAddress_CA9 | LPDDR3_CommandAddress |

# Signal requirements for test availability

Table 4 displays a comprehensive list of the tests that are made available for one or more signals that you can select in the Compliance Test Application, using the **Common Connection Setting** feature.

Table 4 Availability of tests based on required signals for SDRAM Types DDR3 & DDR3L

| Test Group Name                     | Test Group Category      | Available tests                                  | Required signals                                 |

|-------------------------------------|--------------------------|--------------------------------------------------|--------------------------------------------------|

|                                     |                          | VSEH(Clock Plus)                                 | Clock Plus                                       |

|                                     |                          | VSEL(Clock Plus)                                 | Clock Plus                                       |

|                                     |                          | Overshoot Amplitude / Area for Clock Plus Tests  | Clock Plus                                       |

| Clock Plus                          | Electrical Tests         | Undershoot Amplitude / Area for Clock Plus Tests | Clock Plus                                       |

| Clock I lus                         | Liectificat fests        | SlewR on Setup Region                            | Clock Plus                                       |

|                                     |                          | SlewF on Setup Region                            | Clock Plus                                       |

|                                     |                          | SlewR on Hold Region                             | Clock Plus                                       |

|                                     |                          | SlewF on Hold Region                             | Clock Plus                                       |

|                                     |                          | VSEH(Clock Minus)                                | Clock Minus                                      |

|                                     | Electrical Tests         | VSEL(Clock Minus)                                | Clock Minus                                      |

|                                     |                          | Overshoot Amplitude / Area (Clock Minus)         | Clock Minus                                      |

| Clock Minus                         |                          | Undershoot Amplitude / Area (Clock Minus)        | Clock Minus                                      |

| Clock Willias                       |                          | SlewR on Setup Region                            | Clock Minus                                      |

|                                     |                          | SlewF on Setup Region                            | Clock Minus                                      |

|                                     |                          | SlewR on Hold Region                             | Clock Minus                                      |

|                                     |                          | SlewF on Hold Region                             | Clock Minus                                      |

| Clock Plus and<br>Minus Cross Point |                          | VIX for Clock                                    | <ul><li>Clock Plus</li><li>Clock Minus</li></ul> |

|                                     |                          | VIHdiff.CK(AC)                                   | Clock Differential                               |

|                                     | Electrical Test          | VILdiff.CK(AC)                                   | Clock Differential                               |

| Clock Differential                  |                          | VIHdiff.CK                                       | Clock Differential                               |

|                                     |                          | VILdiff.CK                                       | Clock Differential                               |

|                                     | Timing Tests at AC level | tDVAC(Clock)                                     | Clock Differential                               |

| Test Group Name    | Test Group Category                             | Available tests                                             | Required signals                                                                                                          |

|--------------------|-------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                    | Timing Tests for<br>Rising Edge<br>Measurements | tjit(CC) Rising Edge Measurement                            | Clock Differential                                                                                                        |

|                    |                                                 | tCK(avg) Rising Edge Measurement                            | Clock Differential                                                                                                        |

|                    |                                                 | tjit(per) Rising Edge Measurement                           | Clock Differential                                                                                                        |

|                    |                                                 | tERR(nper) Rising Edge Measurement                          | Clock Differential                                                                                                        |

| Clock Differential |                                                 | tCH(avg) Average High Measurement                           | Clock Differential                                                                                                        |

|                    |                                                 | tCL(avg) Average Low Measurement                            | Clock Differential                                                                                                        |

|                    | Timing Tests for<br>Pulse Measurements          | tJIT(duty-high/low) Jitter Average High/Low<br>Measurements | Clock Differential                                                                                                        |

|                    |                                                 | tCH(abs) Absolute clock HIGH pulse width                    | Clock Differential                                                                                                        |

|                    |                                                 | tCL(abs) Absolute clock LOW pulse width                     | Clock Differential                                                                                                        |

|                    | Electrical Tests                                | VSEH(Strobes Plus)                                          | <ul> <li>Strobe Plus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                                                 | VSEL(Strobes Plus)                                          | <ul> <li>Strobe Plus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                                                 | Overshoot Amplitude / Area (Strobes Plus)                   | Strobe Plus                                                                                                               |

|                    |                                                 | Undershoot Amplitude / Area (Strobes Plus)                  | Strobe Plus                                                                                                               |

| Strobe Plus        |                                                 | SlewR on Setup Region                                       | <ul> <li>Strobe Plus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                                                 | SlewF on Setup Region                                       | <ul> <li>Strobe Plus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                                                 | SlewR on Hold Region                                        | <ul> <li>Strobe Plus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                                                 | SlewF on Hold Region                                        | <ul> <li>Strobe Plus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| Test Group Name                      | Test Group Category | Available tests                           | Required signals                                                                                                                                |

|--------------------------------------|---------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                     | VSEH(Strobes Minus)                       | <ul> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                      |

|                                      |                     | VSEL(Strobes Minus)                       | <ul> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                      |

|                                      |                     | Overshoot Amplitude/Area (Strobes Minus)  | Strobe Minus                                                                                                                                    |

|                                      |                     | Undershoot Amplitude/Area (Strobes Minus) | Strobe Minus                                                                                                                                    |

| Strobe Minus                         | Electrical Tests    | SlewR on Setup Region                     | <ul> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                      |

|                                      |                     | SlewF on Setup Region                     | <ul> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                      |

|                                      |                     | SlewR on Hold Region                      | <ul> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                      |

|                                      |                     | SlewF on Hold Region                      | <ul> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                      |

| Strobe Plus and<br>Minus Cross Point |                     | VIX for Strobe                            | <ul> <li>Strobe Plus</li> <li>Strobe Minus</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                      | Electrical Tests    | VIHdiff.DQS(AC)                           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>               |

| Strobe Differential                  |                     | VILdiff.DQS(AC)                           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>               |

| (Write Cycle)                        |                     | VIHdiff.DQS                               | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>               |

|                                      |                     | VILdiff.DQS                               | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>               |

| Test Group Name                      | Test Group Category | Available tests | Required signals                                                                                                                                          |

|--------------------------------------|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Timing Tests        | tDQSS           | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

|                                      |                     | tDQSH           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                                      |                     | tDQSL           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

| Strobe Differential<br>(Write Cycle) |                     | tDSS            | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

|                                      |                     | tDSH            | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

|                                      |                     | tWPRE           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                                      |                     | tWPST           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                                      |                     | tDVAC(Strobe)   | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

| Test Group Name     | Test Group Category | Available tests                                                                 | Required signals                                                                                                                                          |

|---------------------|---------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Electrical Tests    | VOHdiff(AC)                                                                     | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | VOLdiff(AC)                                                                     | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | SRQdiffR                                                                        | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | SRQdiffF                                                                        | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

| Strobe Differential | Timing Tests        | tLZ(DQS) /<br>tLZ(DQS) for Low Power /<br>tHZ(DQS) /<br>tHZ (DQS) for Low Power | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

| (Read Cycle)        |                     | tRPRE                                                                           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | tRPST                                                                           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | tQSH                                                                            | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | tQSL                                                                            | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                     |                     | tDQSCK                                                                          | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

| Test Group Name    | Test Group Category | Available tests       | Required signals                                                                                                                  |                                                                                                                                   |

|--------------------|---------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                    |                     | VIH.DQ(AC)            | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

|                    |                     |                       | VIH.DQ(DC)                                                                                                                        | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | VIL.DQ(AC)            | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

| Poto (Write Ovele) |                     | VIL.DQ(DC)            | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

| Data (Write Cycle) | Electrical Tests    | SlewR on Setup Region | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

|                    |                     | SlewF on Setup Region | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

|                    |                     | SlewR on Hold Region  | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

|                    |                     | SlewF on Hold Region  | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |                                                                                                                                   |

| Test Group Name    | Test Group Category | Available tests  | Required signals                                                                                                                  |

|--------------------|---------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                    | Timing Tests        | tDS(base)        | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | tDH(base)        | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| Data (Write Cycle) |                     | tDS-Diff(derate) | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| buta (White Gyele) |                     | tDH-Diff(derate) | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | tDIPW            | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | tVAC(Data)       | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    | Electrical Tests    | VOH(AC)          | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | VOH(DC)          | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| Data (Daad Cyala)  |                     | VOL(AC)          | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| Data (Read Cycle)  |                     | VOL(DC)          | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | SRQseR           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                    |                     | SRQseF           | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| Test Group Name                     | Test Group Category | Available tests                                           | Required signals                                                                                                                                          |

|-------------------------------------|---------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                     | Timing Tests        | tHZ(DQ)                                                   | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

| Data (Read Cycle)                   |                     | tLZ(DQ)                                                   | <ul> <li>Clock Differential</li> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank Separation is enabled)</li> </ul> |

|                                     |                     | tDQSQ                                                     | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                                     |                     | tQH                                                       | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

| Data (Electrical Over               | shoot/Undershoot    | Overshoot Amplitude/Area (Data)                           | ■ Data                                                                                                                                                    |

| Tests)                              |                     | Undershoot Amplitude/Area (Data)                          | - Data                                                                                                                                                    |

| Data (Read/Write Eye-Diagram Tests) |                     | User Defined Real-Time Eye Diagram Test For Read<br>Cycle | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

|                                     |                     | User Defined Real-Time Eye Diagram Test For Write Cycle   | <ul> <li>Strobe Differential</li> <li>Data</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul>                         |

| Test Group Name Test Group Category |                        | Available tests                       | Required signals                                                                                                                       |

|-------------------------------------|------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                     |                        | VIH.DQ(AC)                            | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     |                        | VIH.DQ(DC)                            | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     |                        | VIL.DQ(AC)                            | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     | Electrical Tests       | VIL.DQ(DC)                            | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

| Data Mask (Write<br>Cycle)          |                        | SlewR on Setup Region                 | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     |                        | SlewF on Setup Region                 | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     |                        | SlewR on Hold Region                  | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     |                        | SlewF on Hold Region                  | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     | Timing Tests           | tDIPW                                 | <ul> <li>Strobe Differential</li> <li>Data Mask</li> <li>DDR3_CommandAddress_ChipSelect (If Rank<br/>Separation is enabled)</li> </ul> |

|                                     | l Overshoot/Undershoot | Overshoot Amplitude/Area (Data Mask)  | Data Mask                                                                                                                              |

| Tests)                              |                        | Undershoot Amplitude/Area (Data Mask) | Data Mask                                                                                                                              |

| Test Group Name | Test Group Category | Available tests                                                | Required signals                                                                                           |

|-----------------|---------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                 |                     | VIH.CA(AC)                                                     | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | VIH.CA(DC)                                                     | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | VIL.CA(AC)                                                     | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | VIL.CA(DC)                                                     | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 | Electrical Tests    | SlewR on Setup Region                                          | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 | Elooti lout 100to   | SlewF on Setup Region                                          | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | SlewR on Hold Region                                           | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | SlewF on Hold Region                                           | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | Overshoot Amplitude/Area (Command, Address)                    | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

| Command,Address |                     | Undershoot Amplitude/Area (Command, Address)                   | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 | Timing Tests        | tlS(base)                                                      | <ul> <li>Clock Differential</li> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul> |

|                 |                     | tIH(base)                                                      | <ul> <li>Clock Differential</li> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul> |

|                 |                     | tlS(derate)                                                    | <ul> <li>Clock Differential</li> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul> |

|                 |                     | tlH(derate)                                                    | <ul> <li>Clock Differential</li> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul> |

|                 |                     | tIPW                                                           | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 |                     | tVAC(CA)                                                       | <ul> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul>                             |

|                 | Eye-Diagram Tests   | User Defined Real-Time Eye Diagram Test For<br>Command Address | <ul> <li>Clock Differential</li> <li>DDR3_CommandAddress, or<br/>DDR3_CommandAddress_ChipSelect</li> </ul> |

Table 5 Availability of tests based on required signals for SDRAM Type LPDDR3

| Test Group Name                     | Test Group Category                          | Available tests                                             | Required signals                                                                                         |

|-------------------------------------|----------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                     |                                              | VSEH(Clock Plus)                                            | Clock Plus                                                                                               |

| Cleak Dive                          | Flactuical Tasts                             | VSEL(Clock Plus)                                            | <ul> <li>Clock Plus</li> </ul>                                                                           |

| Clock Plus                          | Electrical Tests                             | Overshoot Amplitude / Area for Clock Plus Tests             | Clock Plus                                                                                               |

|                                     |                                              | Undershoot Amplitude / Area for Clock Plus Tests            | Clock Plus                                                                                               |

|                                     |                                              | VSEH(Clock Minus)                                           | Clock Minus                                                                                              |

| Olaska Miliana                      | Florida I Tooks                              | VSEL(Clock Minus)                                           | Clock Minus                                                                                              |

| Clock Minus                         | Electrical Tests                             | Overshoot Amplitude / Area (Clock Minus)                    | Clock Minus                                                                                              |

|                                     |                                              | Undershoot Amplitude / Area (Clock Minus)                   | Clock Minus                                                                                              |

| Clock Plus and Minus<br>Cross Point |                                              | VIXCA for Clock                                             | Clock Plus Clock Minus                                                                                   |

|                                     |                                              | VIHdiff.CK(AC)                                              | Clock Differential                                                                                       |

|                                     | Electrical Test                              | VILdiff.CK(AC)                                              | Clock Differential                                                                                       |

|                                     | Electrical lest                              | VIHdiff.CK(DC)                                              | Clock Differential                                                                                       |

|                                     |                                              | VILdiff.CK(DC)                                              | Clock Differential                                                                                       |

|                                     | Timing Tests at AC level                     | tDVAC(Clock)                                                | Clock Differential                                                                                       |

|                                     | Timing Tests for Rising<br>Edge Measurements | tCK(abs) Rising Edge Measurement                            | Clock Differential                                                                                       |

|                                     |                                              | tjit(CC) Rising Edge Measurement                            | Clock Differential                                                                                       |

| Clock Differential                  |                                              | tCK(avg) Rising Edge Measurement                            | Clock Differential                                                                                       |

|                                     |                                              | tjit(per) Rising Edge Measurement                           | Clock Differential                                                                                       |

|                                     |                                              | tERR(nper) Rising Edge Measurement                          | Clock Differential                                                                                       |

|                                     |                                              | tCH(avg) Average High Measurement                           | Clock Differential                                                                                       |

|                                     | Timing Tests for Pulse<br>Measurements       | tCL(avg) Average Low Measurement                            | Clock Differential                                                                                       |

|                                     |                                              | tJIT(duty-high/low) Jitter Average High/Low<br>Measurements | Clock Differential                                                                                       |

|                                     |                                              | tCH(abs) Absolute clock HIGH pulse width                    | Clock Differential                                                                                       |

|                                     |                                              | tCL(abs) Absolute clock LOW pulse width                     | Clock Differential                                                                                       |

|                                     |                                              | VSEH(Strobes Plus)                                          | <ul> <li>Strobe Plus</li> <li>Data</li> <li>LPDDR3_ChipSelect (If Rank Separation is enabled)</li> </ul> |

| Strobe Plus                         | Electrical Tests                             | VSEL(Strobes Plus)                                          | <ul> <li>Strobe Plus</li> <li>Data</li> <li>LPDDR3_ChipSelect (If Rank Separation is enabled)</li> </ul> |

|                                     |                                              | Overshoot Amplitude / Area (Strobes Plus)                   | Strobe Plus                                                                                              |

|                                     |                                              |                                                             |                                                                                                          |