# D9050DDRC DDR5 Test Application - Methods of Implementation

### **Notices**

### © Keysight Technologies 2023

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

### Trademarks

UNIX is a registered trademark of UNIX System Laboratories in the U.S.A. and other countries. Target is copyrighted by Thru-Put Systems, Inc.

### Version

Version 1.90.0.0

### Edition

November 2023

Available in electronic format only

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at

http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinguish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater

than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

### Safety Notices

### **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Contents

### 1 Overview

```

DDR5 Automated Testing—At a Glance / 8

Required Equipment and Software / 9

Hardware / 9

Software / 10

Licensing information / 10

Additional Licenses 10

In This Book / 11

See Also / 11

```

### 2 Installing the Test Application and Licenses

```

Installing the Test Application / 14

Installing the License Key / 15

Using Keysight License Manager 5 / 15

Using Keysight License Manager 6 / 16

```

### 3 Preparing to Take Measurements

```

Calibrating the Oscilloscope / 20

Starting the DDR5 Test Application / 21

Filtering tests in the DDR5 Test Application / 23

Connections for Compliance Tests / 25

```

### 4 Burst Data tests

```

READ Burst / 28

Test Availability Conditions / 28

tDQSCK / 28

tRPRE / 29

tRPST / 29

tLZDQS / 29

tHZDQS / 30

VOHdiff(AC) / 30

VOLdiff(AC) / 31

SRQdiffR / 31

SRQdiffF / 32

V<sub>OH(AC)</sub> / 32

VOH(DC) / 32

VOL(AC) / 33

VOL(DC) / 33

SRQseR / 34

SRQseF / 34

WRITE Burst / 35

Test Availability Conditions / 35

tDQS2DQ / 35

Write Eye Diagram / 37

tDSS / 39

tDSH / 39

tWPRE 2 / 40

tWPRE_3 / 40

tWPRE_4 / 41

tWPST_0_5 / 41

tWPST_1_5 / 42

tDQSH_pre / 42

tDQSL_pre / 43

tDQSL2PRE / 43

tDQSL3PRE / 44

tDQSL4PRE / 44

SRIdiffR_DQS / 45

SRIdiffF_DQS / 45

```

### 5 Continuous Data tests

Clock (Diff) tests / 48

VIHdiff.CK(AC) / 48

Test Availability Conditions / 48

```

VIHdiff.CK(DC) / 48

VILdiff.CK(AC) / 49

VILdiff.CK(DC) / 49

SRIdiffR.CK / 50

SRIdiffF.CK / 50

Clock Jitter tests / 51

Test Availability Conditions / 51

tCK / 51

tCK_Duty_UI_High / 51

tCK_Duty_UI_Low / 52

tCK_Duty_UI_Error / 52

(nUI) tCK_nUI_Ri_NoBUJ / 53

(nUI) tCK_nUI_Dj_NoBUJ / 54

(nUI) tCK_nUI_Tj_NoBUJ / 56

DQ Jitter tests / 58

Test Availability Conditions / 58

tTx_DQ_Duty_UI / 58

(nUI) tTX_DQ_nUI_Rj_NoBUJ / 59

(nUI) tTX_DQ_nUI_Dj_NoBUJ / 59

DQS Jitter tests / 61

Test Availability Conditions / 61

tTx_DQS_Duty_UI / 61

(nUI) tTX_DQS_nUI_Rj_NoBUJ / 62

(nUI) tTX_DQS_nUI_Dj_NoBUJ / 62

6 Clock (Single Ended) tests

Test Availability Conditions / 66

Overshoot/Undershoot (CK t) / 67

Overshoot amplitude (CK_t) / 67

Overshoot area above VDD Abs Max(CK_t) / 68

Overshoot area between VDD and VDD Abs Max(CK_t) / 69

```

Undershoot amplitude (CK\_t) / 70 Undershoot area below VSS(CK\_t) / 71

```

Overshoot/Undershoot (CK_c) / 73

Overshoot amplitude (CK_c) / 73

Overshoot area above VDD Abs Max(CK_c) / 74

Overshoot area between VDD and VDD Abs Max(CK_c) / 75

Undershoot amplitude (CK_c) / 76

Undershoot area below VSS(CK_c) / 77

Clock Cross Point Voltage Test / 79

Vix_CK_ratio / 79

```

### 7 CA (Command Address) tests

```

Test Availability Conditions / 82

tCIVW Margin / 82

vCIVW Margin / 83

CA VIHL(ac) / 84

SRIN_cIVW / 84

tCIPW / 85

Eye Diagram for Command Address / 85

```

### 8 Stressed Eye tests

```

Test Availability Conditions / 88

TxEH_DQ_SES_1UI / 88

TxEW_DQ_SES_1UI / 88

TxEH_DQ_SES_2UI / 89

TxEW_DQ_SES_2UI / 90

TxEH_DQ_SES_3UI / 90

TxEW_DQ_SES_3UI / 91

TxEH_DQ_SES_4UI / 91

TxEW_DQ_SES_4UI / 92

TxEH_DQ_SES_5UI / 92

TxEW_DQ_SES_5UI / 93

```

### 9 DQS (Single Ended) tests

```

Test Availability Conditions / 96

DQS Cross Point Voltage Test / 97

Vix_DQS_ratio / 97

```

### Keysight D9050DDRC DDR5 Test Application Methods of Implementation

## 1 Overview

DDR5 Automated Testing—At a Glance 8

Required Equipment and Software 9

In This Book 11

### DDR5 Automated Testing-At a Glance

The Keysight D9050DDRC DDR5 Test Application helps you verify that the transmitter device under test (DUT) conforms to the pre-defined limits using the supported Keysight Infiniium Oscilloscopes. The Keysight D9050DDRC DDR5 Test Application:

- · Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- · Automatically checks for proper oscilloscope configuration.

- · Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run and lets you specify the thresholds at which marginal or critical warnings appear.

- · Creates a printable HTML report of the tests that have been run.

NOTE

The tests performed by the Keysight D9050DDRC DDR5 Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

### Required Equipment and Software

In order to run the DDR5 automated tests, you need the following equipment and software:

### Hardware

- Use one of the following Oscilloscope models. Refer to www.keysight.com for the respective bandwidth ranges.

- · Keysight DSO9000A-Series, DSO90000A-Series and DSOX90000A/Q/Z/V-Series

- Oscilloscopes with a minimum bandwidth of 8GHz (recommended) for accurate measurements. For faster speed grade devices, a minimum bandwidth of 13GHz bandwidth is recommended.

- · Keysight UXR Oscilloscopes

- · Any PC motherboard system that supports DDR5 memory DIMM(s)

- · DUT: Saved waveform and PulseGen generated signal

- · InfiniiMax probe amplifiers:

- N1169A 12GHz InfiniiMax II probe amplifier

- MX0020A 10GHz InfiniiMax Ultra Probe Amplifier

- MX0021A 13GHz InfiniiMax Ultra Probe Amplifier

- · MX0022A 16GHz InfiniiMax Ultra Probe Amplifier

- MX0023A 25GHz InfiniiMax RC Probe Amp

- MX0024A 20GHz InfiniiMax Ultra Probe Amplifier

- · MX0025A 25GHz InfiniiMax Ultra Probe Amplifier

- InfiniiMax probe heads InfiniiMax II probe heads and accessories (compatible with 9000 Series and 90000 Series, use N5442A precision BNC adapter with 90000X/Q Series):

- · N5381A InfiniiMax II 12GHz differential solder-in probe head and accessories

- N5382A InfiniiMax II 12GHz differential browser

- E2677A InfiniiMax II 12GHz differential solder-in probe head and accessories

- N5425A InfiniiMax II 12GHz ZIF probe head

- N5426A InfiniiMax II ZIF tips (×10)

- InfiniiMax Ultra/RC Probe Amplifiers probe heads and accessories:

- · MX0100A InfiniiMax Micro Probe Head

- · MX0103A Bullet Adapter

- Precision 3.5 mm BNC to SMA male adapter, Keysight p/n 54855-67604, qty = 2 (provided with the Keysight 54855A and 80000B series oscilloscopes)

- 50-ohm Coax Cable with SMA Male Connectors 24-inch or less RG-316/U or similar, qty = 2, matched length

- Keyboard, qty = 1, (provided with the Keysight Infiniium Oscilloscope)

- Mouse, gty = 1, (provided with the Keysight Infiniium Oscilloscope)

- Keysight also recommends using a second monitor to view the test application.

### Software

- The minimum version of Infiniium Oscilloscope Software (see the Keysight D9050DDRC DDR5 Test Application Release Notes)

- Keysight D9050DDRC DDR5 Test Application software

- Keysight E2688A Serial Data Analysis and Clock Recovery software (for clock recovery)

### Licensing information

Refer to the *Data Sheet* for the DDR5 Test Application to know about the licenses you must install along with other optional licenses. Visit "http://www.keysight.com/find/D9050DDRC" and in the web page's **Document Library** tab, you may view the associated Data Sheet.

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

The licensing format for Keysight License Manager 6 differs from its predecessors. See "Installing the License Key" on page 15 to see the difference in installing a license key using either of the applications on your machine.

To launch the DDR5 Validation Test Application, you must have the SDA and DDR5 licenses installed.

#### Additional Licenses

- 1 InfiniiSim feature requires the following licenses:

- · InfiniiSim Basic or InfiniiSim Advanced

- 2 Precision Probe/Cable feature requires the following licenses:

- · Precision Probe or Precision Probe Advanced

### In This Book

This manual describes the tests that are performed by the Keysight D9050DDRC DDR5 Test Application in more detail.

- Chapter 2, "Installing the Test Application and Licenses" shows how to install the automated test application software and licenses (if it was purchased separately).

- Chapter 3, "Preparing to Take Measurements" shows how to start the Keysight D9050DDRC DDR5 Test Application and gives a brief overview of the required preparation and how the application is used.

- Chapter 4, "Burst Data tests" describes the methods of implementation for electrical and timing tests performed on READ and WRITE bursts of the DDR5 differential signals.

- Chapter 5, "Continuous Data tests" describes the methods of implementation for electrical and jitter tests performed on continuous DDR5 differential and single-ended Data Strobe signals.

- Chapter 6, "Clock (Single Ended) tests" describes the methods of implementation for tests performed on continuous DDR5 single-ended Clock signals.

- Chapter 7, "CA (Command Address) tests" describes the methods of implementation for tests performed on DDR5 Command & Address signals.

- Chapter 8, "Stressed Eye tests" describes the methods of implementation for DDR5 stressed eye

tests.

### See Also

The Keysight D9050DDRC DDR5 Test Application's Online Help, which describes:

- · Starting the DDR5 Test Application

- Creating or Opening a Test Project

- · Setting Up the Test Environment

- Selecting Tests

- Configuring Tests

- · Verifying Physical Connections

- Running Tests

- Configuring Automation in the Test Application

- · Viewing Results

- · Viewing HTML Test Report

- · Exiting the Test Application

- · Additional Settings in the Test App

1 Overview

# Keysight D9050DDRC DDR5 Test Application Methods of Implementation

# 2 Installing the Test Application and Licenses

Installing the Test Application 14

Installing the License Key 15

If you purchased the D9050DDRC DDR5 Test Application separate from your Infiniium oscilloscope, you must install the software and license key.

#### 2

### Installing the Test Application

- 1 Make sure you have the minimum version of Infiniium Oscilloscope software (see the D9050DDRC release notes). To ensure that you have the minimum version, select **Help > About Infiniium...** from the main menu.

- 2 To obtain the DDR5 Test Application, go to Keysight website: "http://www.keysight.com/find/D9050DDRC".

- 3 In the web page's **Free Trials** tab, click the **Details and Download** button to view instructions for downloading and installing the application software.

### Installing the License Key

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

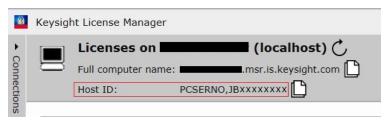

Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

Figure 1 Viewing the Host ID information in Keysight License Manager 5

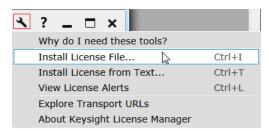

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

- 3 From the **Configuration** menu, use one of the options to install each license file.

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to Keysight License Manager 5 Supporting Documentation.

#### 2

### Using Keysight License Manager 6

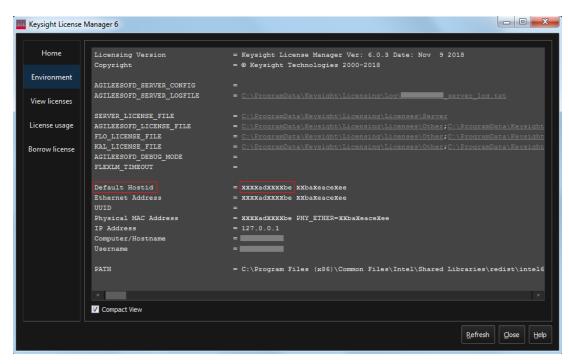

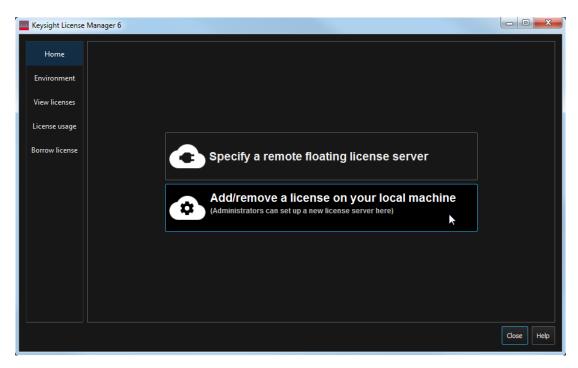

To view and copy the Host ID from Keysight License Manager 6:

- 1 Launch **Keysight License Manager 6** on your machine, where you wish to run the Test Application and its features.

- 2 Copy the **Host ID**, which is the first set of alphanumeric value (as highlighted in Figure 3) that appears in the **Environment** tab of the application. Note that x indicates numeric values.

Figure 3 Viewing the Host ID information in Keysight License Manager 6

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager 6.

- 3 From the **Home** tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to Keysight License Manager 6 Supporting Documentation.

2 Installing the Test Application and Licenses

# Keysight D9050DDRC DDR5 Test Application Methods of Implementation

# 3 Preparing to Take Measurements

Calibrating the Oscilloscope 20

Starting the DDR5 Test Application 21

Filtering tests in the DDR5 Test Application 23

Before running the automated tests, you must calibrate the oscilloscope and probe. No test fixture is required for this application. After the oscilloscope and probe have been calibrated, you are ready to start the DDR5 Test Application and perform the measurements.

### Calibrating the Oscilloscope

If you have not already calibrated the oscilloscope, refer to the *User Guide* for the respective Oscilloscope you are using.

NOTE

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the **Utilities > Calibration** menu.

NOTE

If you switch cables between channels or other Oscilloscopes, it is necessary to perform cable and probe calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.

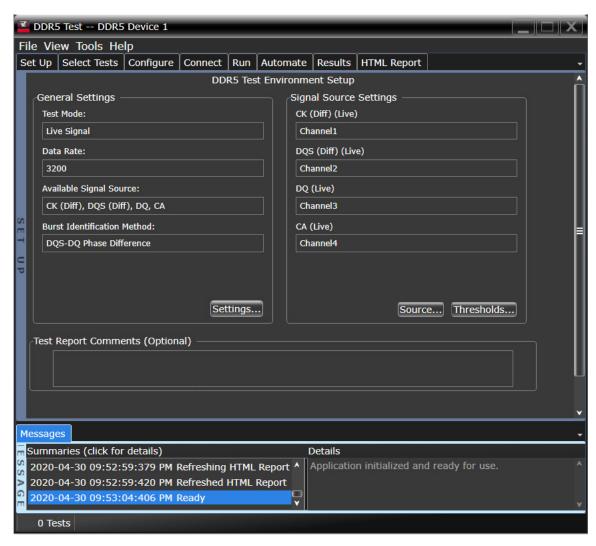

### Starting the DDR5 Test Application

1 Ensure that the DDR5 Device Under Test (DUT) is operating and set to desired test modes. To start the DDR5 Test Application: From the Infiniium Oscilloscope's main menu, select Analyze > Automated Test Apps > D9050DDRC DDR5 Test App.

Figure 5 DDR5 Test Application Main Window

To understand the functionality of the various features in the user interface of the Test Application, refer to the *Keysight D9050DDRC DDR5 Test Application Online Help* available in the **Help** menu.

The task flow pane and the tabs in the main pane show the steps you take in running the automated tests:

| Tab          | Description                                                                                                                                                                                                                                                                |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Set Up       | Lets you identify and set up the test environment, including information about the device under test. The Test App includes relevant information in the final HTML report.                                                                                                 |

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |

| Configure    | Lets you configure test parameters (for example, channels used in test, voltage levels, etc.).                                                                                                                                                                             |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests that are to be run.                                                                                                                                                                       |

| Run          | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Automate     | Lets you construct scripts of commands that drive execution of the application.                                                                                                                                                                                            |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

### NOTE

In the **Configure** tab, the values for all such Configuration parameters that are Oscilloscope-dependent, will correspond to the Oscilloscope Model (DSOs or UXRs), where you are running the Test Application.

### Filtering tests in the DDR5 Test Application

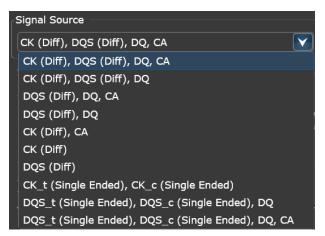

The DDR5 Test Application filters the list of tests based on the options you select in the **Signal Source** and **Signal Operation Mode** features.

- 1 In the **Set Up** tab, click **Settings...**.

- 2 In the **DDR5 General Setup** window that appears,

Figure 6 DDR5 General Setup window

a Select a set of signal combinations from the options that appear in the **Signal Source** drop-down field.

Figure 7 Set of signal combinations in Signal Source drop-down

### b In the Signal Operation Mode area,

- For the differential Clock and Data Strobe signals, set the mode either as **Burst** or as **Continuous**.

- By default, **DQS (Diff)** is set to **Burst**, so that you may configure DQS Burst data mode options by clicking the **Burst DQS Options...** button. For more information regarding setting Burst DQS Options, refer to the *Keysight D9050DDRC DDR5 Test Application Online Help*.

- For single ended Clock and Data Strobe signal source options, only **Continuous** mode can be applied.

- If **DQS** (**Diff**) is set to **Continuous**, the **DQ** mode options become available. By default, the DDR5 Test Application sets the DQ signal operation mode to **DataPattern**. All Jitter and Stressed Eye tests appear for this mode. For the DQ Jitter tests (that require Continuous DQ signal for processing) to appear, select **Continuous1010**.

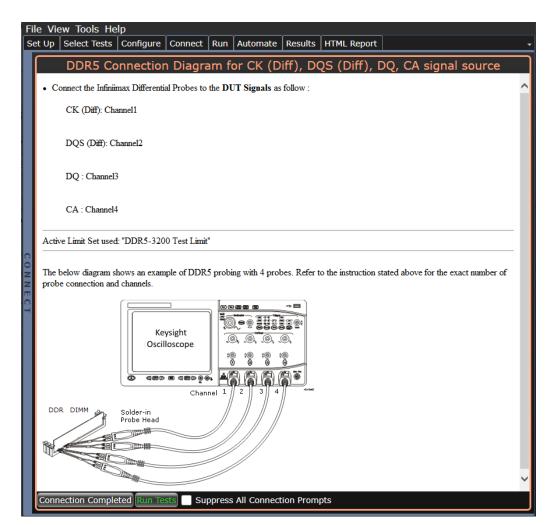

### Connections for Compliance Tests

To run tests using the DDR5 Test Application, you must make proper connections between the Oscilloscope and the DUT. Once you select the tests that you want to run, refer to the **Connect** tab in the DDR5 Test Application for connection instructions and the connection diagram, similar to the one shown in Figure 8.

Figure 8 Physical connection diagram and instructions for compliance tests

3 Preparing to Take Measurements

### Keysight D9050DDRC DDR5 Test Application Methods of Implementation

## 4 Burst Data tests

READ Burst 28 WRITE Burst 35

### **READ Burst**

### Test Availability Conditions

All tests in this test group appear for the following configuration in DDR5 General Setup window: Signal Source:

· Any signal set including CK (Diff), DQS (Diff), DQ

NOTE

Some tests appear only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

### Signal Operation Mode:

- · CK (Diff) Burst

- · DQS (Diff) Burst

- DQ Not applicable

### Burst DQS options:

- · Read Preamble Mode

- DDR5\_1tCK

- · DDR5\_2tCK\_0010

- · DDR5\_2tCK\_1110

- DDR5\_3tCK

- · DDR5\_4tCK

- · Read Postamble Mode

- DDR5\_0.5tCK

- DDR5\_1.5tCK

- Read Vsw1 (V)

- Read Vsw2 (V)

**tDQSCK**

NOTE

This test appears only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

Test ID: 14500

**Test Overview:** The purpose of this test is to verify the time interval from the data strobe output (DQS rising edge) access time to the nearest rising edge of the clock.

**Test Procedure:**

- 1 Acquire and split read and write burst of the acquired signal.

- 2 Take the first valid READ burst found.

- 3 Find all valid rising DQS crossings at 0V in the specified burst.

- 4 For all DQS crossings found, locate the nearest crossing at the rising edge of the Clock at OV.

- 5 Measure as tDQSCK the time difference from the DQS crossing to the corresponding Clock crossing (found in the previous step).

6 Report the measured tDQSCK.

### Expected/ Observable Results:

The measured value of tDQSCK shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

**tRPRE**

**Test ID:** 14530

**Test Overview:** The purpose of this test is to verify the Read preamble region of the DQS signal.

Test Procedure:

- 1 Acquire and split read and write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Disregard the invalid bursts.

- 3 Take the first valid READ burst found.

- 4 Find tLZBeginPoint on the DQS signal of the specified burst.

- 5 Find the first rising edge (excluding preamble pattern) on DQS of the found burst. tRPRE is the time interval between the rising DQS edge and tLZBeginPoint.

- 6 Report tRPRE.

### Expected/ Observable Results:

The measured value of tRPRE shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

**tRPST**

**Test ID:** 14540

**Test Overview:** The purpose of this test is to verify the Read postamble region of the DQS signal.

**Test Procedure:**

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Disregard the invalid bursts.

- 3 Take the first valid READ burst found.

- 4 Find tHZEndPoint on the DQS signal of the specified burst.

- 5 Find the last falling edge on DQS prior to tHZEndPoint found. tRPST is the time interval between the falling DQS edge's crossing and tHZEndPoint.

- 6 Report tRPST.

### Expected/ Observable Results:

The measured value of tRPST shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tLZDQS

NOTE

This test appears only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

**Test ID:** 14510

**Test Overview:** The purpose of this test is to verify the time when DQS starts driving (\*from High-impedance state to

High/Low state) to the nearest rising clock signal crossing.

#### 4 Burst Data tests

#### **Test Procedure:**

- 1 Acquire and split Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Disregard the invalid bursts.

- 3 Take the first valid READ burst found.

- 4 Find tLZBeginPoint on the DQS signal of the said burst.

- 5 Find the nearest Clock rising edge. tLZ(DQS) is the time interval between the Clock rising edge's crossing point and tLZBeginPoint.

- 6 Report tLZ(DQS).

### Expected/ Observable Results:

The value of measured tLZ(DQS) shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

**tHZDQS**

### NOTE

This test appears only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

**Test ID:** 14520

**Test Overview:**

The purpose of this test is to verify the time when DQS is no longer driving (from High state OR Low state to the High-impedance state) to the reference clock signal crossing.

#### **Test Procedure:**

- 1 Acquire and split read and write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Disregard the invalid bursts.

- 3 Take the first valid READ burst found.

- 4 Find tHZEndPoint on the DQS signal of the said burst.

- 5 Find the nearest Clock rising edge. tHZ(DQS) is the time interval between Clock rising edge's crossing point and tHZEndPoint.

- 6 Report tHZ(DQS).

### Expected/ Observable Results:

The value of measured tHZ(DQS) shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

#### VOHdiff(AC)

**Test ID:** 13510

**Test Overview:**

The purpose of this test is to verify the high level differential output voltage value of the test signal within the read burst.

### **Test Procedure:**

- 1 Acquire and split read and write burst of the acquired signal.

- 2 Take the first valid READ burst found.

- 3 Find all valid Strobe positive pulses in the said burst.

A valid Strobe positive pulse starts at the 0V crossing at the valid Strobe rising edge and ends at the 0V crossing at the following valid Strobe falling edge.

- 4 Zoom into the first pulse and perform  $V_{TOP}$ . Take the  $V_{TOP}$  measurement as  $V_{OHdiff\ (AC)}$  value.

- 5 Repeat step 4 with the rest of the positive pulses in the specified burst.

- 6 Determine the worst result from the set of V<sub>OHdiff (AC)</sub> measured.

### Expected/ Observable Results:

The worst measured  $V_{OHdiff\,(AC)}$  shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### VOLdiff(AC)

**Test ID:** 13515

**Test Overview:** The purpose of this test is to verify the low level differential output voltage value of the test signal

within the read burst.

**Test Procedure:** 1 Acquire and split read and write burst of the acquired signal.

2 Take the first valid READ burst found.

3 Find all valid Strobe negative pulses in the specified burst. A valid Strobe negative pulse starts at the 0V crossing at the valid Strobe falling edge and ends at the 0V crossing at the following valid Strobe rising edge.

4 Zoom into the first pulse and perform  $V_{BASE}$ . Take the  $V_{BASE}$  measurement as  $V_{OI\ diff\ (AC)}$  value.

- 5 Repeat step 4 with the rest of the negative pulses in the specified burst.

- 6 Determine the worst result from the set of V<sub>OI diff (AC)</sub> measured.

### Expected/ Observable Results:

The worst measured  $V_{OLdiff\,(AC)}$  shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### SRQdiffR

**Test ID:** 13500

**Test Overview:** The purpose of this test is to verify the differential output slew rate for rising edge of the test signal within the read burst.

**Test Procedure:**

- 1 Acquire and split the read and write burst of the acquired signal.

- 2 Take the first valid READ burst found.

- 3 Calculate V<sub>OLdiff(AC)</sub> and V<sub>OHdiff(AC)</sub> using the equation:

$V_{OHdiff(AC)} = 0.75 * Vdiffpk-pk$  $V_{OLdiff(AC)} = 0.25 * Vdiffpk-pk$

Then use calculated  $V_{OHdiff(AC)}$  and  $V_{OLdiff(AC)}$  to defined strobe edge level requirement.

- 4 Find all the valid Strobe rising edges in the specified burst. A valid Strobe rising edge starts at  $V_{OLdiff(AC)}$  crossing and ends at the following  $V_{OHdiff(AC)}$  crossing.

- 5 Calculate SRQdiffR using the equation:

$$SRQdiffR = [V_{OHdiff(AC)} - V_{OLdiff(AC)}] / DeltaTRdiff$$

6 Determine the worst result from the set of SRQdiffR measured.

### Expected/ Observable Results:

The measured value of SRQdiffR for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

**SRQdiffF**

13505 Test ID:

Test Overview: The purpose of this test is to verify the differential output slew rate for falling edge of the test signal

within the read burst.

1 Acquire and split the read and write burst of the acquired signal. **Test Procedure:**

2 Take the first valid READ burst found.

3 Calculate V<sub>OLdiff(AC)</sub> and V<sub>OHdiff(AC)</sub> using the equation:

$V_{OHdiff(AC)} = 0.75 * Vdiffpk-pk$  $V_{Oldiff(AC)} = 0.25 * Vdiffpk-pk$

Then use calculated V<sub>OHdiff(AC)</sub> and V<sub>OLdiff(AC)</sub> to defined strobe edge level requirement.

- 4 Find all the valid Strobe falling edges in the specified burst. A valid Strobe falling edge starts at  $V_{OHdiff(AC)}$  crossing and ends at the following  $V_{OLdiff(AC)}$ crossing.

- 5 Calculate SRQdiffF using the equation:

$SRQdiffF = [V_{OHdiff(AC)} - V_{OLdiff(AC)}] / DeltaTFdiff$

6 Determine the worst result from the set of SRQdiffF measured.

### Expected/ Observable Results:

The measured value of SRQdiffF for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

VOH(AC)

Test ID: 13520

Test Overview: The purpose of this test is to verify the high level DQ output voltage value of the test signal within a

valid read burst.

**Test Procedure:** 1 Acquire and split the read and write burst of the acquired signal.

2 Take the first valid READ burst found.

3 Find all valid positive pulses in the specified burst. A valid positive pulse starts at the VREFDQ configured in the app and ends at middle crossing at the following valid falling edge.

4 Zoom in on the first valid positive pulse and perform V<sub>TOP</sub> measurement.

Take the  $V_{T\Omega P}$  measurement results as  $V_{OH(AC)}$  value.

- 5 Continue the previous step with the rest of the valid positive pulses that were found in the burst.

- 6 Determine the worst result from the set of  $V_{OH(AC)}$  measured.

Expected/ Observable Results: The measured value of  $V_{OH(AC)}$  for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

VOH(DC)

13525 Test ID:

The purpose of this test is to verify the high level DQ output voltage value of the test signal within a Test Overview:

valid read burst.

**Test Procedure:** 1 Acquire and split the read and write burst of the acquired signal.

2 Take the first valid READ burst found.

- 3 Find all valid positive pulses in the specified burst. A valid positive pulse starts at the middle crossing at valid rising edge and ends at middle crossing at the following valid falling edge.

- 4 Zoom in on the first valid positive pulse and perform  $V_{TOP}$  measurement. Take the  $V_{TOP}$  measurement results as  $V_{OH(DC)}$  value.

- 5 Continue the previous step with the rest of the valid positive pulses that were found in the burst.

- 6 Determine the worst result from the set of  $V_{OH(DC)}$  measured.

### Expected/ Observable Results:

The measured value of  $V_{OH(DC)}$  for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### VOL(AC)

**Test ID:** 13530

**Test Overview:**

The purpose of this test is to verify the low level DQ output voltage value of the test signal within a valid read burst.

**Test Procedure:**

- 1 Acquire and split the read and write burst of the acquired signal.

- 2 Take the first valid READ burst found.

- 3 Find all valid negative pulses in the specified burst.

A valid negative pulse starts at the middle crossing at valid falling edge and ends at middle crossing at the following valid rising edge.

- 4 Zoom in on the first valid negative pulse and perform  $V_{BASE}$  measurement. Take the  $V_{BASE}$  measurement results as  $V_{OL(AC)}$  value.

- 5 Continue the previous step with the rest of the valid negative pulses that were found in the burst.

- 6 Determine the worst result from the set of V<sub>OL(AC)</sub> measured.

### Expected/ Observable Results:

The measured value of  $V_{OL(AC)}$  for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### VOL(DC)

**Test ID:** 13535

**Test Overview:**

The purpose of this test is to verify the DQ output low level voltage value of the test signal within a valid read burst.

### Test Procedure:

- 1 Acquire and split the read and write burst of the acquired signal.

- 2 Take the first valid READ burst found.

- 3 Find all valid negative pulses in the specified burst.

A valid negative pulse starts at the middle crossing at valid falling edge and ends at middle crossing at the following valid rising edge.

- 4 Zoom in on the first valid negative pulse and perform  $V_{BASE}$  measurement. Take the  $V_{BASE}$  measurement results as  $V_{OL(DC)}$  value.

- 5 Continue the previous step with the rest of the valid negative pulses that were found in the burst.

- 6 Determine the worst result from the set of V<sub>OI (DC)</sub> measured.

### Expected/ Observable Results:

The measured value of  $V_{OL(DC)}$  for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

SRQseR

13540 Test ID:

Test Overview: The purpose of this test is to verify the single-ended output slew rate for rising edge of the test signal

within the read burst.

1 Acquire and split the read and write burst of the acquired signal. **Test Procedure:**

2 Take the first valid READ burst found.

Find all the valid rising edges in the specified burst. A valid rising edge starts at  $V_{OL(AC)}$  crossing and ends at the following  $V_{OH(AC)}$  crossing.

4 For all the valid rising edges, find the transition time, DeltaTRdiff. DeltaTRdiff is the time starting at  $V_{OL(AC)}$  crossing and ending at the following  $V_{OH(AC)}$  crossing.

5 Calculate SRQseR using the equation:

$$SRQseR = [V_{OH(AC)} - V_{OL(AC)}] / DeltaTRdiff$$

6 Determine the worst result from the set of SRQseR measured.

### Expected/ Observable Results:

The calculated Rising Slew (SRQseR) value for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

SRQseF

13545 Test ID:

**Test Overview:** The purpose of this test is to verify that the single-ended output slew rate for falling edge of the test

signal within the read burst.

**Test Procedure:** 1 Acquire and split the read and write burst of the acquired signal.

2 Take the first valid READ burst found.

3 Find all the valid falling edges in the specified burst. A valid falling edge starts at  $V_{OH(AC)}$  crossing and ends at the following  $V_{OL(AC)}$  crossing.

4 For all the valid falling edges, find the transition time, DeltaTFdiff. DeltaTFdiff is the time starting at  $V_{OH(AC)}$  crossing and ending at the following  $V_{OL(AC)}$  crossing.

Calculate SRQseF using the equation:

$$SRQseF = [V_{OL(AC)} - V_{OH(AC)}] / DeltaTFdiff$$

Determine the worst result from the set of SRQseF measured.

### Expected/ **Observable Results:**

The calculated Falling Slew (SRQseF) value for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### WRITE Burst

### Test Availability Conditions

All tests in this test group appear for the following configuration in DDR5 General Setup window: Signal Source:

· Any signal set including CK (Diff), DQS (Diff), DQ

NOTE

Some tests appear only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

### Signal Operation Mode:

- · CK (Diff) Burst

- · DQS (Diff) Burst

- DQ Not applicable

### Burst DQS options:

- · Write Preamble Mode

- · DDR5\_2tCK

- · DDR5\_3tCK

- DDR5\_4tCK

- · Write Postamble Mode

- · DDR5\_0.5tCK

- · DDR5\_1.5tCK

- Write Vsw1 (V)

- · Write Vsw2 (V)

### tDQS2DQ

**Test ID:** 14050

**Test Overview:** The purpose of this test is to verify the tDQS2DQ parameter.

NOTE

To obtain a valid measurement result, this test requires a transitioning bit at the first valid bit in the DQ bus. Otherwise, this test uses the first opening in the eye diagram as the first transition bit, which may yield undesirable results.

#### Test Procedure:

- 1 Set up the oscilloscope:

- a Using UDF methodology, separate Write burst and return the filtered DQS signals as recovered clock for eye folding later.

- b Set up measurement threshold values for the DQ channel and the DQS channel input.

- c Set up vertical scale values for DQ channel and DQS channel input.

- d Turn ON Color Grade Display option.

- e Set up Mask Test settings.

- f Set up Clock Recovery on SDA. Explicit clock, Source = filtered DQS, Rise Edge

- g Turn ON Real Time Eye on SDA.

- 2 Realign the eye opening of the first transition DQ bit to the center of the screen:

- a Increase the search range on the screen to the range specified in the 'First DQ Transition Search Range (ps)', so that the crossing point of the eye is visible on the screen.

- b Use the Histogram feature to find the first crossing point at 'VRefDQ' level horizontally across the screen.

- c Skip/pad the number of bit/bits by the value specified in the configuration option Padding for First DQ Bit.

- d Realign the center of the eye to the middle time position.

- 3 Perform Mask Testing:

- a Set the Mask Test Run setting to 'Forever'.

- b Load the mask file and start the Mask Test.

- c Stop the Mask Test when the counter for 'Total Waveforms' exceeds the number of required waveforms specified in the configuration option 'Total Waveform'.

- 4 Determine and store the Vcent value.

There is an option to derive Vcent, which depends on the "Vcent Evaluation Mode" configuration option.

- If the "Vcent Evaluation Mode" option is set to "User defined Vcent", the value of Vcent follows the value of the "User Defined Vcent" configuration option.

- If the "Vcent Evaluation Mode" option is set to "Widest eye opening level", the application evaluates Vcent value from the level of widest eye opening on the generated eye diagram.

The detailed procedure for "Widest eye opening level" is:

- a The Vcent level search ranges from 40% to 60% of the eye amplitude (eye height measured at the center of the eye diagram).

- b Scan for the widest eye opening at the mentioned search range with a scan resolution of 5mV. The voltage level at the widest eye opening is used as Vcent.

- 5 Use Histogram measurements to determine the center location of the eye diagram at Vcent level and denote it as EyeCenterLoc.

- 6 Determine the location of the filtered DQS rising edges used in the recovered clock and denote it as FilteredDQSLoc.

- 7 Compute the final test result using the equation: tDQS2DQ = EyeCenterLoc - FilteredDQSLoc

### Expected/ Observable Results:

The measured value of tDQS2DQ for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### Write Eye Diagram

**Test ID:** 14090

#### Test Overview:

The purpose of this test is to automate all the required setup procedures required in order to generate an eye diagram for the DDR5 data WRITE cycle.

The additional feature of having a mask test is that it allows users to perform evaluations and debugging on the eye diagram created.

# NOTE

To obtain a valid measurement result, this test requires a transitioning bit at the first valid bit in the DQ bus. Otherwise, this test uses the first opening in the eye diagram as the first transition bit, which may yield undesirable results.

#### Test Procedure:

- 1 Acquire and split read and write burst of the acquired signal.

- 2 Gather the list of start time of each Write Burst.

- 3 Gather the list of end time of each Write Burst.

- 4 Save acquired DQS into new waveform file in BIN format. Name it "DQS.bin".

- 5 Measure VMinDQS which is the minimum voltage of DQS for the whole acquisition.

- 6 Modify "DQS.bin" waveform file to ignore unwanted region. It is done where within each of the region below, set the sampling voltage at VMinDQS.

- Region #1: from start of acquisition to start time of Write burst #1.

- Region #2: from end time of Write burst #1 to start time of Write burst #2. Continue this until

from end time of Write burst #n-1 to start time of Write burst #n. note n=number of Write

burst

- Region #3: from end time of the last Write burst to the end of acquisition.

- 7 Rename modified "DQS.bin" into "DQSEyeFilt.bin".

- 8 If DFE mode is Auto/Manual

- · Load acquired DQ signal into WMemory3.

- · Perform DFE setting where source is WMemory3. Set Display as function.

- · Save equalization output as BIN file.

- 9 If DFE mode is Auto/Manual

- · Load BIN file(post DFE DQ) into WMemory2.

If DFE is OFF

- · Load acquired DQ signal into WMemory2.

- 10 Load "DQSEyeFilt.bin" into WMemory4. Then use Function2 as "Magnify/Duplicate" of Loaded Waveform Memory.

- 11 Setup Clock Recovery settings on SDA.

- Explicit clock, Source = Function2(DQSEyeFilt), Rise/Fall Edge

- 12 Setup measurement threshold values for the Function3(Data) and the Function2(DQSEyeFilt).

- 13 Setup fix time scale and time position values for Function3(Data) and Function2(DQSEyeFilt).

- 14 Turn ON Color Grade Display option.

- 15 Identify the X1 value for re-adjustment of selected test mask.

- 16 Setup Mask Test settings.

- 17 Turn ON Real Time Eye on SDA.

- 18 Start mask test until eye diagram folded.

- 19 Perform Eye Width Measurement:

- a Set Histogram orientation into Horizontal

- b Set:

- X1= left boundary of screen

- X2= Center of "widest opening voltage"

- Y1= widest opening voltage

- Y2= widest opening voltage

- c EyeWidthT1= Histogram Max

- d Set:

- X1= Center of "widest opening voltage"

- X2= right boundary of screen

- Y1= widest opening voltage

- Y2= widest opening voltage

- e EyeWidthT2= Histogram Min

- f Calculate EyeWidth = EyeWidthT2 EyeWidthT1

- 20 Perform Eye Height Measurement:

- a Set Histogram orientation into Vertical

- b Set:

- X1= Center of "widest opening voltage"

- X2= Center of "widest opening voltage"

- Y1= widest opening voltage

- Y2= Bottom Level of display

- c EyeHeightV1= Histogram Max

- d Set:

- X1= Center of "widest opening voltage"

- X2= Center of "widest opening voltage"

- Y1= Top Level of display

- Y2= widest opening voltage

- e EyeHeightV2= Histogram Min

- f Calculate EyeHeight = EyeHeightV2 EyeHeightV1

- 21 Return total failed UnitInterval as a test result.

# Expected/ Observable Results:

The measured value of Write Eye Diagram for the test signal is considered for 'Information-Only' purpose.

**tDSS**

NOTE

This test appears only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

Test ID: 14000

**Test Overview:** The purpose of this test is to verify the time interval from the falling edge of the data strobe (DQS

falling edge) output access time to the clock (CLK rising edge) setup time.

**Test Procedure:** Acquire and split read and write burst of the acquired signal.

- 2 Take the first valid WRITE burst found.

- 3 Find all valid crossings on the falling edges of DQS in the specified burst.

- 4 For all crossings found on the falling edges of DQS, locate all the next nearest rising edges of the

- 5 Measure tDSS as the time between crossings on the falling edges of DQS and the rising edges of the Clock found in the previous step.

- 6 Collect all values of tDSS.

- 7 Report all values of tDSS measured.

# Expected/ Observable Results:

The measured value of tDSS shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tDSH

NOTE

This test appears only when CK (Diff) is included in the Signal Source along with DQS (Diff) and DQ.

14010 Test ID:

**Test Overview:** The purpose of this test is to verify the time interval from the falling edge of the data strobe (DQS falling edge) to clock (CLK rising edge) hold time.

Test Procedure:

2 Take the first valid WRITE burst found.

- 1 Acquire and split read and write burst of the acquired signal.

- 3 Find all valid falling DQS crossings in the specified burst.

- 4 For all the falling DQS crossings found, locate all nearest preceding rising Clock edges.

- 5 Measure tDSH as the time between falling DQS crossings and the crossing point of the Clock rising edges found.

- 6 Collect all tDSH.

- 7 Determine the worst result from the set of tDSH measured.

# Expected/ Observable Results:

The measured value of tDSH shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tWPRE\_2

NOTE

This test appears only when the DDR5\_2tCK is selected as the Write Preamble mode in the DQS Burst Options Setup window.

Test ID:

14031

Test Overview:

The purpose of this test is to verify the Write preamble region of the DQS signal (for 2tCK Preamble mode).

**Test Procedure:**

- Acquire and split the Read and Write bursts of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint on DQS signal of the said burst.

- 5 Find the first rising edge (excluding preamble pattern) on DQS of the found burst.

- 6 tWPRE\_2 is the time interval between the rising DQS edge and tLZBeginPoint.

- 7 Report tWPRE 2.

### Expected/ Observable Results:

The measured value of tWPRE 2 for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tWPRE\_3

NOTE

This test appears only when the DDR5 3tCK is selected as the Write Preamble mode in the DQS Burst Options Setup window.

Test ID:

14032

**Test Overview:**

The purpose of this test is to verify the Write preamble region of the DQS signal (for 3tCK Preamble

Test Procedure:

- 1 Acquire and split the Read and Write bursts of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint on DQS signal of the said burst.

- 5 Find the first rising edge (excluding preamble pattern) on DQS of the found burst.

- 6 tWPRE\_3 is the time interval between the rising DQS edge and tLZBeginPoint.

- 7 Report tWPRE\_3.

# Expected/ Observable Results:

The measured value of tWPRE 3 for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tWPRE\_4

NOTE

This test appears only when the DDR5\_4tCK is selected as the Write Preamble mode in the DQS Burst Options Setup window.

Test ID:

14033

Test Overview:

The purpose of this test is to verify the Write preamble region of the DQS signal (for 4tCK Preamble mode).

**Test Procedure:**

- 1 Acquire and split the Read and Write bursts of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint on DQS signal of the said burst.

- 5 Find the first rising edge (excluding preamble pattern) on DQS of the found burst.

- 6 tWPRE\_4 is the time interval between the rising DQS edge and tLZBeginPoint.

- 7 Report tWPRE\_4.

# Expected/ Observable Results:

The measured value of tWPRE\_4 for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tWPST\_0\_5

NOTE

This test appears only when the DDR5\_0.5tCK is selected as the Write Postamble Mode in the DQS Burst Options Setup window.

Test ID:

14041

**Test Overview:**

The purpose of this test is to verify the Write postamble region of the DQS signal (for 0.5tCK Postamble mode).

**Test Procedure:**

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tHZEndPoint of the said burst.

- 5 Find the last falling edge on DQS prior to the tHZEndPoint that was found in the previous step.

- 6 tWPST\_0\_5 is the time interval between the falling DQS edge's crossing and tHZEndPoint.

- 7 Report tWPST\_0\_5.

# Expected/ Observable Results:

The measured value of tWPST\_0\_5 for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

NOTE

This test appears only when the DDR5\_1.5tCK is selected as the Write Postamble Mode in the DQS Burst Options Setup window.

**Test ID:** 14042

**Test Overview:**

The purpose of this test is to verify the Write postamble region of the DQS signal (for 1.5tCK Postamble mode).

**Test Procedure:**

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tHZEndPoint of the said burst.

- 5 Find the last falling edge on DQS prior to the tHZEndPoint that was found in the previous step.

- 6 tWPST\_1\_5 is the time interval between the falling DQS edge's crossing and tHZEndPoint.

- 7 Report tWPST\_1\_5.

# Expected/ Observable Results:

The measured value of tWPST\_1\_5 for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tDQSH\_pre

**Test ID:** 14060

**Test Overview:**

The purpose of this test is to verify the positive pulse width of DQS within preamble region.

**Test Procedure:**

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint on DQS signal of the said burst.

- 5 Find tLZEndPoint. It is defined as first rising edge (excluding preamble pattern) on DQS of the found burst where first data bit is latching.

- 6 Find all valid rising and falling DQS crossings within "tLZBeginPoint + 0.5UI" and "tLZEndPoint + 0.5UI".

- 7 Measure tDQSH\_pre as the time starting from the rising edge of DQS and ending at the following falling edge.

- 8 Collect all tDQSH\_pre values.

- 9 Determine the worst result from the set of tDQSH\_pre measured.

# Expected/ Observable Results:

The measured value of tDQSH\_pre for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tDQSL\_pre

**Test ID:** 14070

**Test Overview:** The purpose of this test is to verify the negative pulse width of DQS within preamble region.

Test Procedure:

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint on DQS signal of the said burst.

- 5 Find tLZEndPoint. It is defined as first rising edge (excluding preamble pattern) on DQS of the found burst where first data bit is latching.

- 6 Find all valid rising and falling DQS crossings within "tLZBeginPoint + 0.5UI" and "tLZEndPoint + 0.5UI".

- 7 Measure tDQSL\_pre as the time starting from the falling edge of DQS and ending at the following rising edge.

- 8 Collect all tDQSL\_pre values.

- 9 Determine the worst result from the set of tDQSL\_pre measured.

# Expected/ Observable Results:

The measured value of tDQSL\_pre for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

#### tDQSL2PRE

**Test ID:** 14081

**Test Overview:** The purpose of this test is to verify the initial low pulse width during Write Preamble region of the DQS signal (for 2tCK Preamble mode).

DQS signal (for 2tCK Preamble mode).

**Test Procedure:** 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint on DQS signal of the said burst.

- 5 Find the first rising edge on DQS after the tLZEndPoint.

- 6 tDQSL2PRE is the time interval between the tLZBeginPoint and rising edge found in step 5.

- 7 Report tDQSL2PRE values.

# Expected/ Observable Results:

The measured value of tDQSL2PRE for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tDQSL3PRE

NOTE

This test appears only when the DDR5\_3tCK is selected as the Write Preamble Mode in the DQS Burst Options Setup window.

**Test ID:** 14082

**Test Overview:**

The purpose of this test is to verify the initial low pulse width during Write Preamble region of the DQS signal (for 3tCK Preamble mode).

**Test Procedure:**

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint of the said burst.

- 5 Find the first rising edge on DQS after the tLZEndPoint.

- 6 tDQSL3PRE is the time interval between the tLZBeginPoint and rising edge found in step 5.

- 7 Report tDQSL3PRE values.

# Expected/ Observable Results:

The measured value of tDQSL3PRE for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tDQSL4PRE

NOTE

This test appears only when the DDR5\_4tCK is selected as the Write Preamble Mode in the DQS Burst Options Setup window.

**Test ID:** 14083

**Test Overview:**

The purpose of this test is to verify the initial low pulse width during Write Preamble region of the DQS signal (for 4tCK Preamble mode).

**Test Procedure:**

- 1 Acquire and split the Read and Write burst of the acquired signal.

- 2 Validate the Read and Write bursts obtained in the previous step. Invalid bursts are disregarded.

- 3 Take the first valid WRITE burst found.

- 4 Find tLZBeginPoint of the said burst.

- 5 Find the first rising edge on DQS after the tLZEndPoint.

- 6 tDQSL4PRE is the time interval between the tLZBeginPoint and rising edge found in step 5.

- 7 Report tDQSL4PRE values.

# Expected/ Observable Results:

The measured value of tDQSL4PRE for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### SRIdiffR\_DQS

**Test ID:** 13000

**Test Overview:** The purpose of this test is to verify the differential input slew rate for rising edge of the test signal.

**Test Procedure:**

- 1 Acquire and split the read and write burst of the acquired signal.

- 2 Take the first valid WRITE burst found.

- 3 Calculate V<sub>ILdiff(AC)</sub> and V<sub>IHdiff(AC)</sub> using the equation:

$V_{IHdiff(AC)} = 0.75 * Vdiffpk-pk$  $V_{ILdiff(AC)} = 0.25 * Vdiffpk-pk$

Then use calculated  $V_{IHdiff(AC)}$  and  $V_{ILdiff(AC)}$  to defined strobe edge level requirement.

- 4 Find all the valid Strobe rising edges in the specified burst.

A valid Strobe rising edge starts at V<sub>ILdiff.DQS(AC)</sub> crossing and ends at the following V<sub>IHdiff.DQS(AC)</sub> crossing.

- For all the valid Strobe rising edges, find the transition time,  $T_R$ .  $T_R$  is the time starting at  $V_{ILdiff.DQS(AC)}$  crossing and ending at the following  $V_{IHdiff.DQS(AC)}$  crossing.

- 6 Calculate SRIdiffR\_DQS using the equation:

$SRIdiffR_DQS = [V_{IHdiff_DQS(AC)} - V_{ILdiff_DQS(AC)}] / T_R$

7 Determine the worst result from the set of SRIdiffR\_DQS measured.

# Expected/ Observable Results:

The measured value of SRIdiffR\_DQS for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

# SRIdiffF\_DQS

**Test ID:** 13005

**Test Overview:** The purpose of this test is to verify the differential input slew rate for falling edge of the test signal.

Test Procedure:

- 1 Acquire and split the read and write burst of the acquired signal.

- 2 Take the first valid WRITE burst found.

- 3 Calculate V<sub>ILdiff(AC)</sub> and V<sub>IHdiff(AC)</sub> using the equation:

$V_{IHdiff(AC)} = 0.75 * Vdiffpk-pk$  $V_{IIdiff(AC)} = 0.25 * Vdiffpk-pk$

Then use calculated  $V_{IHdiff(AC)}$  and  $V_{ILdiff(AC)}$  to defined strobe edge level requirement.

- 4 For all the valid Strobe falling edges, find the transition time,  $T_R$ .  $T_R$  is the time starting at  $V_{IHdiff,DQS(AC)}$  crossing and ending at the following  $V_{ILdiff,DQS(AC)}$  crossing.

- 5 Calculate SRIdiffF\_DQS using the equation:

$$SRIdiffF_DQS = [V_{IHdiff,DQS(AC)} - V_{ILdiff,DQS(AC)}] / T_R$$

6 Determine the worst result from the set of SRIdiffF\_DQS measured.

# Expected/ Observable Results:

The measured value of SRIdiffF\_DQS for the test signal shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

4 Burst Data tests

# Keysight D9050DDRC DDR5 Test Application Methods of Implementation

# 5 Continuous Data tests

Clock (Diff) tests 48

Clock Jitter tests 51

DQ Jitter tests 58

DQS Jitter tests 61

# Clock (Diff) tests

#### Test Availability Conditions

All tests in this test group appear for the following configuration in DDR5 General Setup window:

# Signal Source:

- · CK (Diff)

- Any set including CK (Diff)

# Signal Operation Mode:

- · CK (Diff) Continuous

- DQS (Diff) − Any

- DQ Any

#### VIHdiff.CK(AC)

Test ID: 10000

**Test Overview:** The purpose of this test is to verify the high level differential input voltage value of the test signal.

#### **Test Procedure:**

- 1 Pre-condition the oscilloscope.

- 2 Trigger on the rising edge of the clock signal under test.

- 3 Find all valid Clock positive pulses in the triggered waveform. A valid Clock positive pulse starts at the OV crossing at valid Clock rising edge and ends at the OV crossing at the following valid Clock falling edge.

- 4 Zoom into the first pulse and measure the top voltage  $V_{TOP}$ . Here,  $V_{TOP}$  is the voltage value on the rising edge after which the signal loses the monotonicity of the slope. Take the  $V_{TOP}$  measurement as  $V_{IHdiff}$  (AC) value.

- 5 Continue the previous step for all positive pulses found in the specified waveform.

- 6 Determine the worst result from the set of  $V_{IHdiff\,(AC)}$  values measured.

### Expected/ Observable Results:

The worst measured  $V_{IHdiff,CK}$  (AC) shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### VIHdiff.CK(DC)

**Test ID:** 10005

**Test Overview:** The purpose of this test is to verify the high level differential input voltage value of the test signal.

### **Test Procedure:**

- 1 Pre-condition the oscilloscope.

- 2 Trigger on the rising edge of the clock signal under test.

- 3 Find all valid Clock positive pulses in the triggered waveform.

A valid Clock positive pulse starts at the 0V crossing at valid Clock rising edge and ends at the 0V crossing at the following valid Clock falling edge.

- Zoom into the first pulse and measure the top voltage  $V_{TOP}$ . Here,  $V_{TOP}$  is the voltage value on the rising edge after which the signal loses the monotonicity of the slope. Take the  $V_{TOP}$  measurement as  $V_{IHdiff}$  (DC) value.

- 5 Continue the previous step for all positive pulses found in the specified waveform.

- 6 Determine the worst result from the set of V<sub>IHdiff (DC)</sub> values measured.

# Expected/ Observable Results:

The worst measured  $V_{IHdiff,CK\ (DC)}$  shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

#### VILdiff.CK(AC)

**Test ID:** 10010

**Test Overview:** The purpose of this test is to verify the low level differential input voltage value of the test signal.

**Test Procedure:**

- 1 Pre-condition the oscilloscope.

- 2 Trigger on the rising edge of the clock signal under test.

- 3 Find all valid Clock negative pulses in the triggered waveform.

A valid Clock negative pulse starts at the 0V crossing at valid Clock falling edge and ends at the 0V crossing at the following valid Clock rising edge.

- 4 Zoom into the first pulse and measure the base voltage  $V_{BASE}$ . Here,  $V_{BASE}$  is the voltage value on the falling edge after which the signal loses the monotonicity of the slope. Take the  $V_{BASE}$  measurement as  $V_{II \ diff}$  (AC) value.

- 5 Continue the previous step for all the negative pulses found in the specified waveform.

- 6 Determine the worst result from the set of  $V_{II \text{ diff (AC)}}$  values measured.

# Expected/ Observable Results:

The worst measured  $V_{\rm ILdiff,CK}$  (AC) shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

# VILdiff.CK(DC)

**Test ID:** 10015

**Test Overview:** The purpose of this test is to verify the low level differential input voltage value of the test signal.

#### Test Procedure:

- 1 Pre-condition the oscilloscope.

- 2 Trigger on the rising edge of the clock signal under test.

- 3 Find all valid Clock negative pulses in the triggered waveform. A valid Clock negative pulse starts at the 0V crossing at valid Clock falling edge and ends at the 0V crossing at the following valid Clock rising edge.

- 4 Zoom into the first pulse and measure the base voltage  $V_{BASE}$ . Here,  $V_{BASE}$  is the voltage value on the falling edge after which the signal loses the monotonicity of the slope. Take the  $V_{BASE}$  measurement as  $V_{ILdiff (DC)}$  value.

- 5 Continue the previous step for all the negative pulses found in the specified waveform.

- 6 Determine the worst result from the set of  $V_{\text{ILdiff}(DC)}$  values measured.

# Expected/ Observable Results:

The worst measured  $V_{ILdiff,CK\ (DC)}$  shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

#### SRIdiffR.CK

10100 Test ID:

Test Overview: The purpose of this test is to verify that the differential input slew rate for rising edge of the test

signal.

**Test Procedure:** 1 Trigger on the rising edge of the clock signal under test.

- 2 Find all the valid Clock rising edges in the entire waveform.

- 3 A valid clock rising edge starts at VILdiff CK crossing and ends at the following VIHdiff CK

- 4 For all the valid Clock rising edges, measure the transition time, DeltaTRdiff. DeltaTRdiff is the time starting at VILdiff\_CK crossing and ending at the following VIHdiff\_CK

- 5 Calculate SRIdiffR\_CK using the equation:

- SRIdiffR\_CK = [VIHdiff\_CK VILdiff\_CK] / DeltaTRdiff.

6 Determine the worst result from the set of SRIdiffR\_CK measured.

# Expected/ Observable Results:

The worst measured SRIdiffR\_CK shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

### SRIdiffF.CK

Test ID: 10105

**Test Overview:** The purpose of this test is to verify that the differential input slew rate for falling edge of the test signal.

**Test Procedure:**

- 1 Trigger on the falling edge of the clock signal under test.

- 2 Find all the valid Clock falling edges in the entire waveform. A valid clock falling edge starts at VIHdiff\_CK crossing and ends at the following VILdiff\_CK

- 3 For all the valid Clock falling edges, measure the transition time, DeltaTFdiff. DeltaTFdiff is the time starting at VIHdiff\_CK crossing and ending at the following VILdiff\_CK

- 4 Calculate SRIdiffF\_CK using the equation:

- SRIdiffF\_CK = [VILdiff\_CK VIHdiff\_CK] / DeltaTFdiff.

- 5 Determine the worst result from the set of SRIdiffF\_CK measured.

# Expected/ Observable Results:

The worst measured SRIdiffF\_CK shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

# Clock Jitter tests

#### Test Availability Conditions

All tests in this test group appear for the following configuration in DDR5 General Setup window:

### Signal Source:

- CK\_t (Single Ended), CK\_c (Single Ended)

- · CK (Diff)

- · Any signal set including CK (Diff)

#### Signal Operation Mode:

- · CK (Diff) Continuous

- DQS (Diff) Not applicable

- DQ Not applicable

tCK

**Test ID:** 15000

**Test Overview:** The purpose of this test is to measure the DRAM Reference clock frequency.

**Test Procedure:**

- 1 Measure the average period cycle width for the entire test signal. A period cycle is the time difference from the rising edge of a cycle to the next rising edge.

- 2 Calculate the average frequency of the test signal value using the following equation. average freq = 1 / average period

- 3 Use the calculated average frequency value as the final measurement result.

# Expected/ Observable Results:

The calculated average frequency value shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

# tCK\_Duty\_UI\_High

**Test ID:** 15010

**Test Overview:** The purpose of this test is to measure the duty cycle of all high pulse widths.

# **Test Procedure:**

NOTE

This test is expected to use continuous 101010... pattern for the test signal.

- 1 Perform signal conditioning on the test signal.

- 2 Measure the width of all the high pulses of the test signal. A high pulse width is the time difference from the rising edge of a pulse to the next falling edge.

- 3 Find the average high pulse width value for all the pulses found.

- 4 Measure the width of all the low pulses of the test signal. A low pulse width is the time difference from the falling edge of a pulse to the next rising edge.

- 5 Find the average low pulse width value for all the pulses found.

- 6 The average UI is calculated as the average of all the high pulse widths and low pulse widths measured.

7 The average duty high pulse width is calculated as follows. average duty high pulse width = average high pulse width / average UI

# Expected/ Observable Results:

The calculated average duty high pulse width shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tCK\_Duty\_UI\_Low

**Test ID:** 15015

**Test Overview:** The purpose of this test is to measure the duty cycle of all low pulse widths.

**Test Procedure:**

NOTE

This test is expected to use continuous 101010... pattern for the test signal.

- 1 Perform signal conditioning on the test signal.

- 2 Measure the width of all the high pulses of the test signal. A high pulse width is the time difference from the rising edge of a pulse to the next falling edge.

- 3 Find the average high pulse width value for all the pulses found.

- 4 Measure the width of all the low pulses of the test signal. A low pulse width is the time difference from the falling edge of a pulse to the next rising edge.

- 5 Find the average low pulse width value for all the pulses found.

- 6 The average UI is calculated as the average of all the high pulse widths and low pulse widths measured.

- 7 The average duty low pulse width is calculated as follows. average duty low pulse width = average low pulse width / average UI

# Expected/ Observable Results:

The calculated average duty low pulse width value shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

tCK\_Duty\_UI\_Error

**Test ID:** 15020

**Test Overview:** The purpose of this test is to measure the duty cycle error.

**Test Procedure:**

NOTE

This test is expected to use continuous 101010... pattern for the test signal.

- 1 Perform signal conditioning on the test signal.

- 2 Measure the width of all the high pulses of the test signal. A high pulse width is the time difference from the rising edge of a pulse to the next falling edge.

- 3 Find the average high pulse width value for all the pulses found.

- 4 Measure the width of all the low pulses of the test signal. A low pulse width is the time difference from the falling edge of a pulse to the next rising edge.

- 5 Find the average low pulse width value for all the pulses found.

- 6 The average UI is calculated as the average of all the high pulse widths and low pulse widths measured.

- 7 The average duty high pulse width is calculated as follows. average duty high pulse width = average high pulse width / average UI

- 8 The average duty low pulse width is calculated as follows. average duty low pulse width = average low pulse width / average UI

- 9 The duty error for the average high pulse and average low pulse is calculated as follows. duty high error = abs(average UI - average duty high pulse width) duty low error = abs(average UI - average duty low pulse width)

- 10 The worst duty error is derived from the largest value between duty high error and duty low error. worst duty error = max(duty high error, duty low error)

- 11 Report the worst duty error as the final measurement result.

# Expected/ Observable Results:

The calculated worst duty error value shall be within the conformance limits as defined in the Keysight D9050DDRC DDR5 Test Application.

# (nUI) tCK\_nUI\_Rj\_NoBUJ

```

Test ID:

(1UI) tCK_1UI_Rj_NoBUJ (Test ID: 15301)

(2UI) tCK_2UI_Ri_NoBUJ (Test ID: 15302)

(3UI) tCK_3UI_Rj_NoBUJ (Test ID: 15303)

(4UI) tCK_4UI_Rj_NoBUJ (Test ID: 15304)

(5UI) tCK_5UI_Rj_NoBUJ (Test ID: 15305)

(6UI) tCK_6UI_Rj_NoBUJ (Test ID: 15306)

(7UI) tCK_7UI_Rj_NoBUJ (Test ID: 15307)

(8UI) tCK_8UI_Rj_NoBUJ (Test ID: 15308)

(9UI) tCK_9UI_Rj_NoBUJ (Test ID: 15309)

(10UI) tCK_10UI_Rj_NoBUJ (Test ID: 15310)

(11UI) tCK_11UI_Ri_NoBUJ (Test ID: 15311)

(12UI) tCK_12UI_Rj_NoBUJ (Test ID: 15312)

(13UI) tCK_13UI_Rj_NoBUJ (Test ID: 15313)

(14UI) tCK_14UI_Ri_NoBUJ (Test ID: 15314)

(15UI) tCK_15UI_Rj_NoBUJ (Test ID: 15315)

(16UI) tCK_16UI_Rj_NoBUJ (Test ID: 15316)

(17UI) tCK_17UI_Rj_NoBUJ (Test ID: 15317)

(18UI) tCK_18UI_Rj_NoBUJ (Test ID: 15318)

(19UI) tCK_19UI_Rj_NoBUJ (Test ID: 15319)

(20UI) tCK_20UI_Rj_NoBUJ (Test ID: 15320)

(21UI) tCK_21UI_Rj_NoBUJ (Test ID: 15321)

(22UI) tCK_22UI_Rj_NoBUJ (Test ID: 15322)

(23UI) tCK_23UI_Ri_NoBUJ (Test ID: 15323)