# Keysight D9020DPHC MIPI® D-PHY<sup>SM</sup> Compliance Test Application

## **Notices**

© Keysight Technologies 2014-2023

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### **Trademarks**

MIPI<sup>®</sup> service marks and logo marks are owned by MIPI Alliance, Inc. and any use of such marks by Keysight Technologies is under license. Other service marks and trade names are those of their respective owners.

#### Version

Version 4.10.0.0

#### Edition

December 2023

Available in electronic format only.

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

#### Safety Notices

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## Contents

#### 1 Overview

```

MIPI® D-PHY<sup>SM</sup> Automated Testing—At a Glance 36

Required Equipment and Software 37

Hardware 37

Software 37

Licensing information 37

In This Book 38

See Also 38

2 Installing the Test Application and Licenses

Installing the Test Application 40

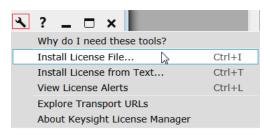

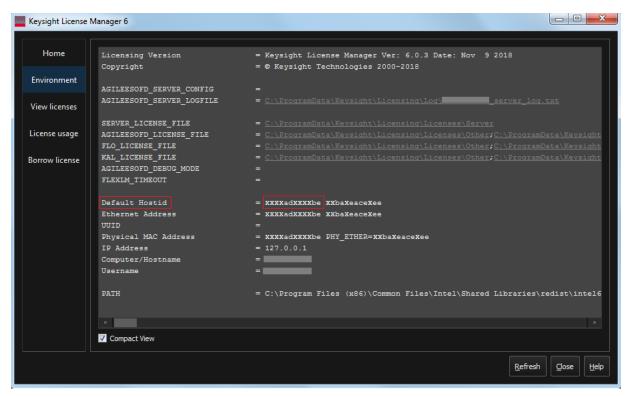

Installing the License Key 41

```

42

# 3 Preparing to Take Measurements

Calibrating the Oscilloscope 46

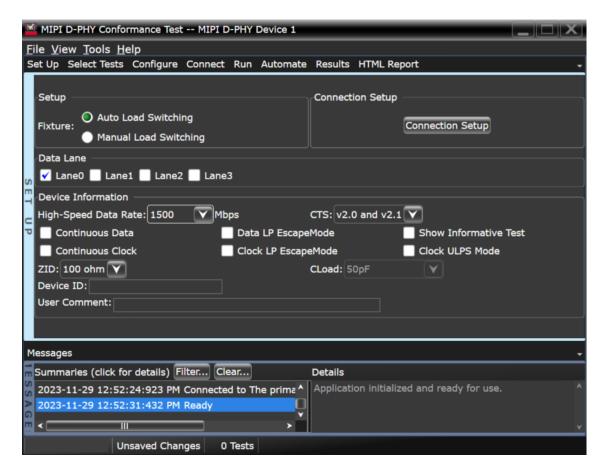

Starting the MIPI D-PHY Test Application 47

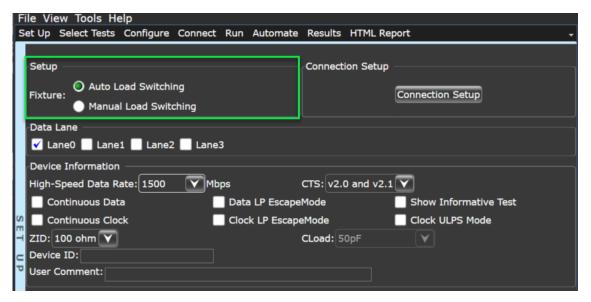

Fixture Options 49

Manual Load Switching 49

Auto Load Switching 50

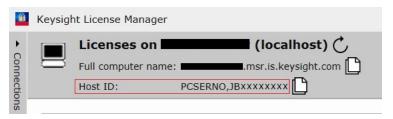

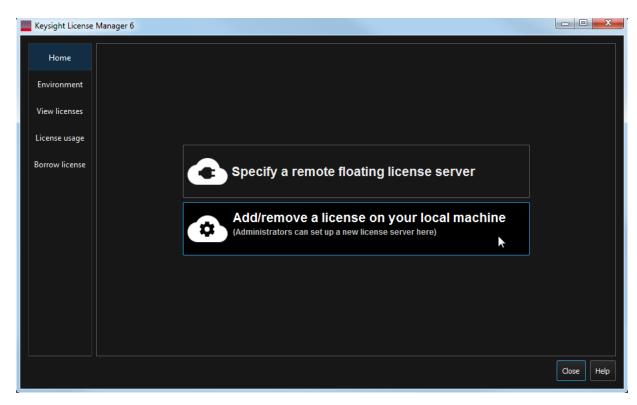

Using Keysight License Manager 5 Using Keysight License Manager 6

Part A MIPI D-PHY 1.0

Part I Electrical Characteristics

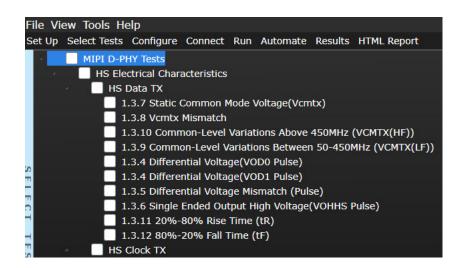

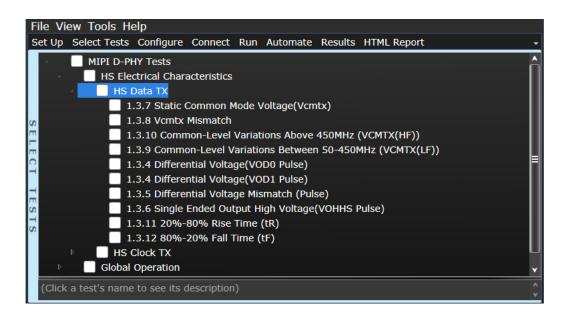

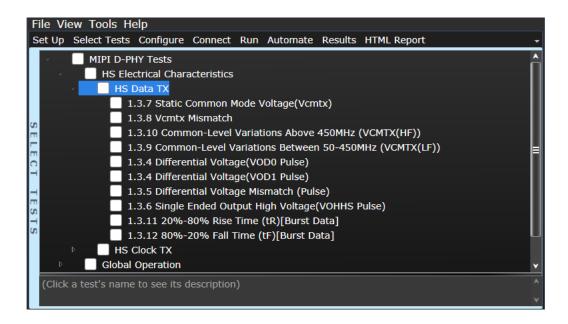

4 MIPI D-PHY 1.0 High Speed Data Transmitter (HS Data TX) Electrical Tests

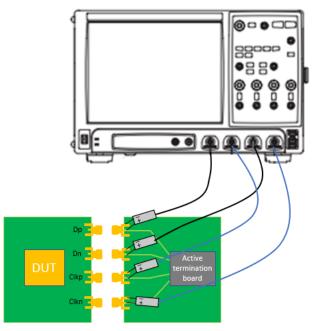

Probing for High Speed Data Transmitter Electrical Tests 56

Test Procedure 56

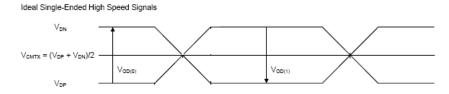

| Test 1.3.7 HS Data TX Static Common Mode Voltage (V <sub>CMTX</sub> ) Method of Implementation 58                         |

|---------------------------------------------------------------------------------------------------------------------------|

| PASS Condition 58 Test Availability Condition 58 Measurement Algorithm using Test ID 811 59 Test References 59            |

| Test 1.3.8 HS Data TX V <sub>CMTX</sub> Mismatch (ΔV <sub>CMTX</sub> ( <sub>1,0)</sub> ) Method of Implementation 60      |

| PASS Condition 60 Test Availability Condition 60 Measurement Algorithm using Test ID 812 61 Test References 61            |

| Test 1.3.10 HS Data TX Common Level Variations Above 450 MHz (ΔV <sub>CMTX</sub> (HF)) Method of                          |

| Implementation 62                                                                                                         |

| PASS Condition 62 Test Availability Condition 63 Measurement Algorithm using Test ID 818 63 Test References 63            |

| Test 1.3.9 HS Data TX Common Level Variations Between 50-450 MHz ( $\Delta V_{CMTX}(LF)$ ) Method of Implementation $64$  |

| PASS Condition 64 Test Availability Condition 65 Measurement Algorithm using Test ID 819 65 Test References 65            |

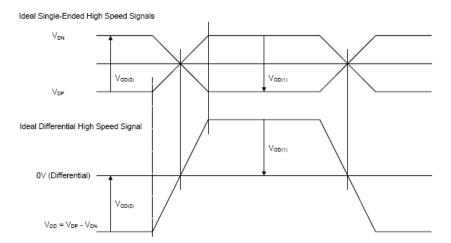

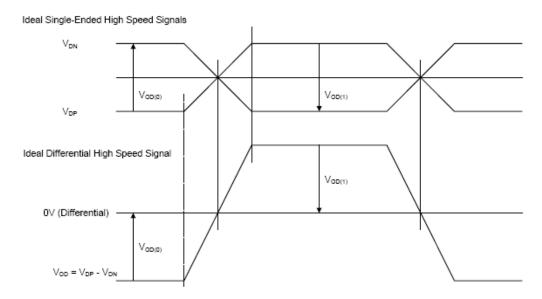

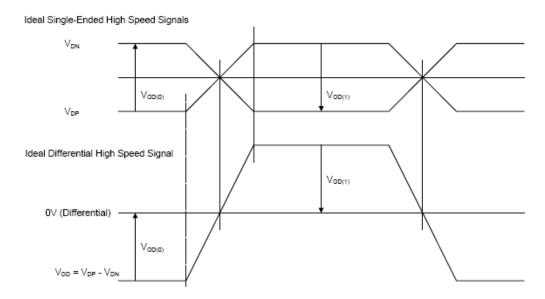

| Test 1.3.4 HS Data TX Differential Voltage (V <sub>OD</sub> ) Method of Implementation 66                                 |

| PASS Condition 66 Test Availability Condition 67 Measurement Algorithm using Test IDs 8131 and 8132 67 Test References 68 |

| Test 1.3.5 HS Data TX Differential Voltage Mismatch (ΔV <sub>OD</sub> ) Method of                                         |

| Implementation 69                                                                                                         |

| PASS Condition 69 Test Availability Condition 70 Measurement Algorithm using Test ID 8141 70 Test References 70           |

|                                                                                                                           |

|            | Took 1.2 C US Date TV Single Ended Outro                                                                                                                                                                                                                         | t High Voltage (V \ Nathod of                               |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|            | Test 1.3.6 HS Data TX Single-Ended Output Implementation 71  PASS Condition 71  Test Availability Condition 71  Measurement Algorithm using Test ID 8151  Measurement Algorithm using Test ID 8152  Measurement Algorithm using Test ID 8153  Test References 73 | 72<br>72                                                    |

|            | Test 1.3.11 Data Lane HS-TX 20%-80% Ri                                                                                                                                                                                                                           | se Time (t <sub>R</sub> ) Method of Implementation 74       |

|            | PASS Condition 74 Test Availability Condition 74 Measurement Algorithm using Test ID 8110 Test References 74                                                                                                                                                     | 74                                                          |

|            | Test 1.3.12 Data Lane HS-TX 80%-20% Fa                                                                                                                                                                                                                           | ll Time (t <sub>F</sub> ) Method of Implementation 75       |

|            | PASS Condition 75 Test Availability Condition 75 Measurement Algorithm using Test ID 8111 Test References 75                                                                                                                                                     | 75                                                          |

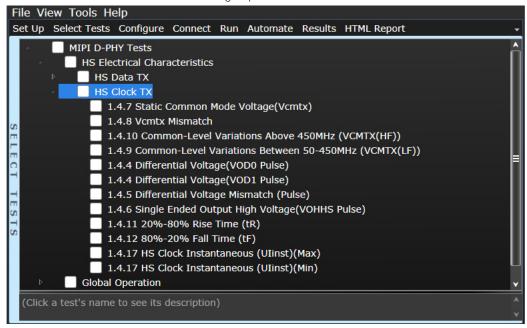

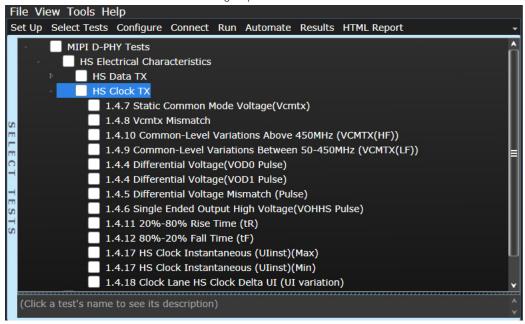

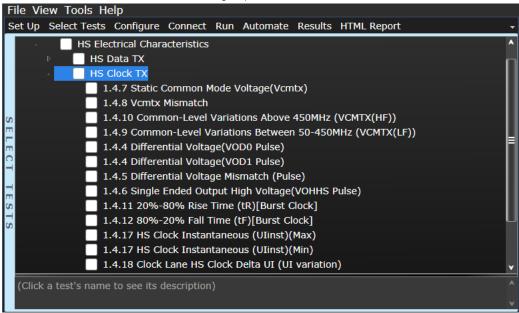

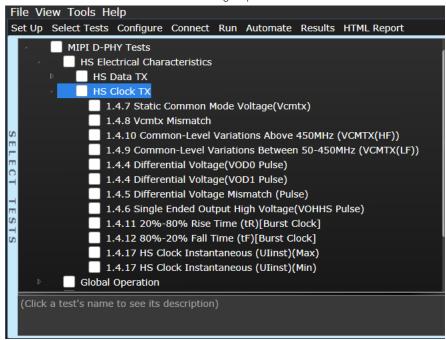

| 5 MIPI D-F | PHY 1.0 High Speed Clock Transmitter (HS                                                                                                                                                                                                                         | Clock TX) Electrical Tests                                  |

|            | Probing for High Speed Clock Transmitter                                                                                                                                                                                                                         | Electrical Tests 78                                         |

|            | Test Procedure 78                                                                                                                                                                                                                                                |                                                             |

|            | Test 1.4.7 HS Clock TX Static Common Molecular Memory 80  PASS Condition 80  Test Availability Condition 80  Measurement Algorithm using Test ID 1811 Test References 81                                                                                         | ode Voltage (V <sub>CMTX</sub> ) Method of                  |

|            | Test 1.4.8 HS Clock TX VCMTX Mismatch                                                                                                                                                                                                                            | $(\Delta V_{CMTX}(1,0))$ Method of Implementation 82        |

|            | PASS Condition 82 Test Availability Condition 83 Measurement Algorithm for Test ID 1812 Test References 83                                                                                                                                                       | 83                                                          |

|            | Test 1.4.10 HS Clock TX Common-Level V                                                                                                                                                                                                                           | ariations Above 450 MHz (ΔV <sub>CMTX</sub> (HF)) Method of |

|            | Implementation 84  PASS Condition 84  Test Availability Condition 85  Measurement Algorithm using Test ID 1818                                                                                                                                                   | <b></b>                                                     |

| Test 1.4.9 HS Clock TX Common-Level Variat                                                                                                   | tions Between 50-450 MHz (ΔV <sub>CMTX</sub> (LF))   |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Method of Implementation 86  PASS Condition 86  Test Availability Condition 87  Measurement Algorithm using Test ID 1819  Test References 87 | 87                                                   |

| Measurement Algorithm using Test ID 1820 Test References 88                                                                                  | 88                                                   |

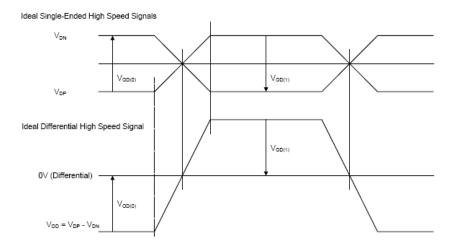

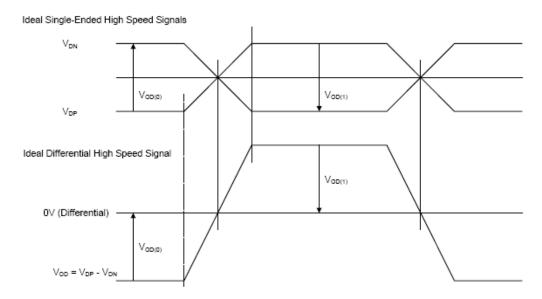

| Test 1.4.4 HS Clock TX Differential Voltage (                                                                                                | V <sub>OD</sub> ) Method of Implementation 89        |

| PASS Condition 89 Test Availability Condition 90 Measurement Algorithm using Test IDs 18131 at Test References 91                            | and 18132 <b>90</b>                                  |

| Test 1.4.5 HS Clock TX Differential Voltage N                                                                                                | Nismatch ( $\Delta V_{OD}$ ) Method of               |

| Implementation 92  PASS Condition 92  Test Availability Condition 93  Measurement Algorithm using Test ID 18141                              | 93                                                   |

| Test References 93  Test 1.4.6 HS Clock TX Single-Ended Output                                                                               | High Voltage (V) Method of                           |

| Implementation 94                                                                                                                            | Trigit voltage (v <sub>OHHS</sub> ) Method of        |

| PASS Condition 94 Test Availability Condition 94                                                                                             |                                                      |

| Measurement Algorithm using Test ID 18151 Test References 95                                                                                 | 95                                                   |

| Test 1.4.11 Clock Lane HS-TX 20%-80% Rise                                                                                                    | e Time (t <sub>R</sub> ) Method of Implementation 96 |

| PASS Condition 96 Test Availability Condition 96 Massyroment Algorithm using Test ID 19110                                                   | O.C.                                                 |

| Measurement Algorithm using Test ID 18110 Test References 96                                                                                 | 96                                                   |

| Test 1.4.12 Clock Lane HS-TX 80%-20% Fall                                                                                                    | Time (t <sub>F</sub> ) Method of Implementation 97   |

| PASS Condition 97                                                                                                                            |                                                      |

| Test Availability Condition 97  Measurement Algorithm using Test ID 18111  Test References 97                                                | 97                                                   |

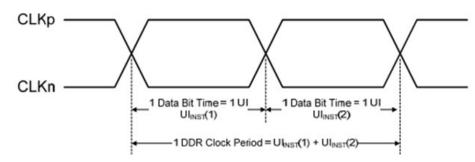

| Test 1.4.17 HS Clock Instantaneous Methor PASS Condition 98 Test Availability Condition 98                                                                                                                                | od of Implementation 98                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Measurement Algorithm using Test ID 911 Measurement Algorithm using Test ID 914 Test References 99                                                                                                                        | 99<br>99                                                   |

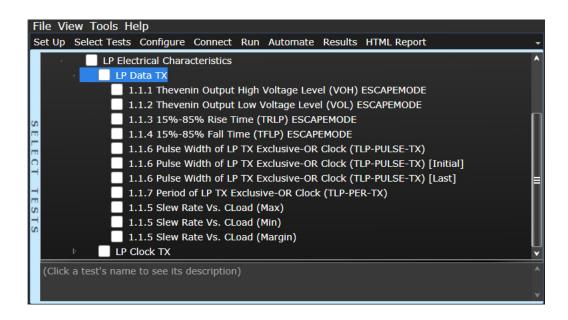

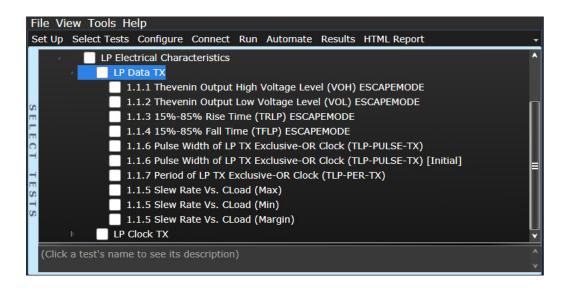

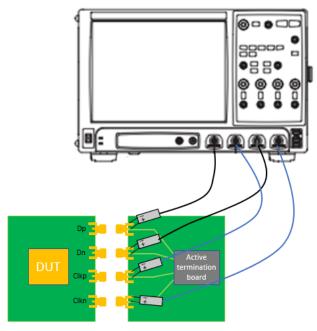

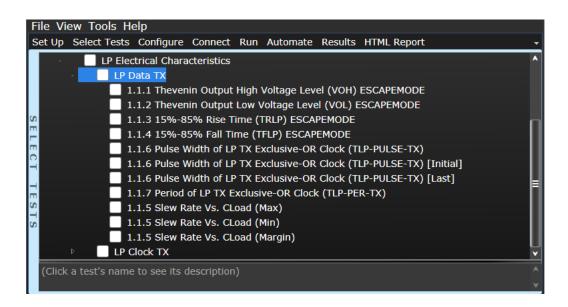

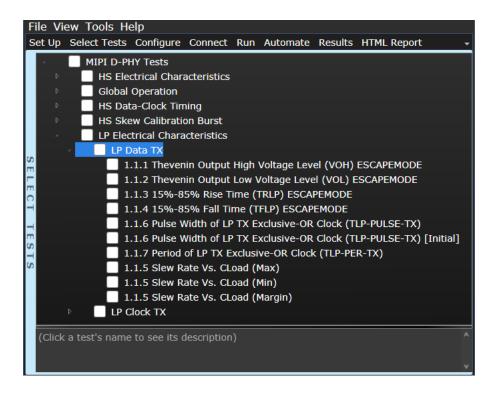

| 6 MIPI D-PHY 1.0 Low Power Data Transmitter (LP Da                                                                                                                                                                        | ata TX) Electrical Tests                                   |

| Probing for Low Power Transmitter Electric Test Procedure 102                                                                                                                                                             | cal Tests 102                                              |

| Test 1.1.1 LP TX Thevenin Output High Vol Implementation 104  PASS Condition 104  Test Availability Condition 104  Measurement Algorithm using Test ID 821  Measurement Algorithm using Test ID 8211  Test References 105 | tage Level (V <sub>OH</sub> ) Method of  104 105           |

| Test 1.1.2 LP TX Thevenin Output Low Volt                                                                                                                                                                                 | tage Level (V <sub>OL</sub> ) Method of Implementation 106 |

| PASS Condition 106 Test Availability Condition 106 Measurement Algorithm using Test ID 822 Measurement Algorithm using Test ID 8221 Test References 107                                                                   | 106<br>107                                                 |

| Test 1.1.3 LP TX 15%-85% Rise Time Leve                                                                                                                                                                                   | l (T <sub>RLP</sub> ) EscapeMode Method of                 |

| Implementation 108  PASS Condition 108  Test Availability Condition 108  Measurement Algorithm using Test ID 8241  Test References 108                                                                                    | 108                                                        |

| Test 1.1.4 LP TX 15%-85% Fall Time Level                                                                                                                                                                                  | (T <sub>FLP</sub> ) Method of Implementation 109           |

| PASS Condition 109 Test Availability Condition 109 Measurement Algorithm using Test ID 825 Measurement Algorithm using Test ID 8251 Test References 110                                                                   | 109<br>110                                                 |

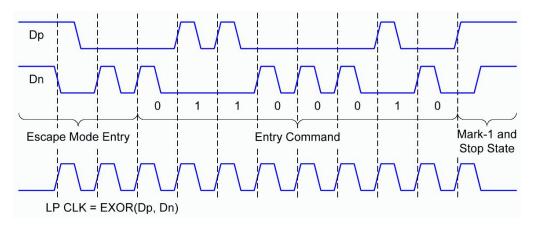

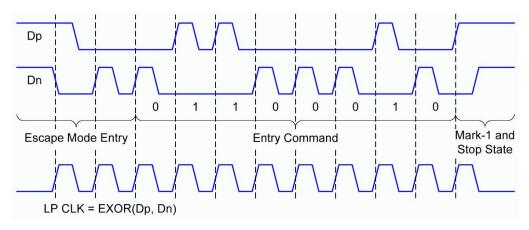

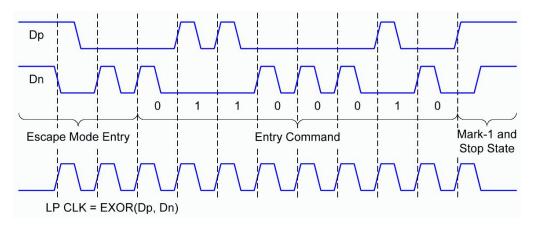

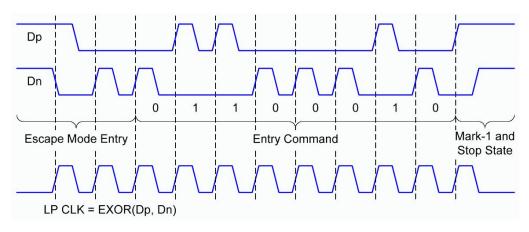

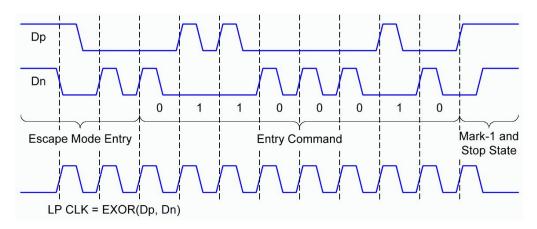

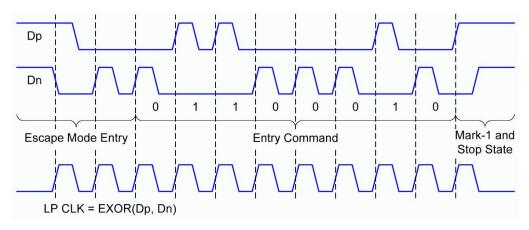

| Test 1.1.6 LP TX Pulse Width of LP TX Exclusive-Or Clock (T <sub>LP-PULSE-TX</sub> ) Method of Implementation 111  PASS Condition 111  Test Availability Condition 111  Measurement Algorithm using Test IDs 827, 8271 and 8272 112  Measurement Algorithm using Test IDs 1827, 18271 and 18272 113  Test References 113 |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Test 1.1.7 LP TX Period of LP TX Exclusive-OR Clock (T <sub>LP-PER-TX</sub> ) Method of Implementation 114  PASS Condition 114  Test Availability Condition 114  Measurement Algorithm using Test ID 828 115  Measurement Algorithm using Test ID 1828 115  Test References 115                                          |     |

| Test 1.1.5 LP TX Slew Rate vs. C <sub>LOAD</sub> Method of Implementation  PASS Condition 116  Test Availability Condition 116  Measurement Algorithm using Test IDs 829, 8291 and 8292 116  Test References 117                                                                                                         |     |

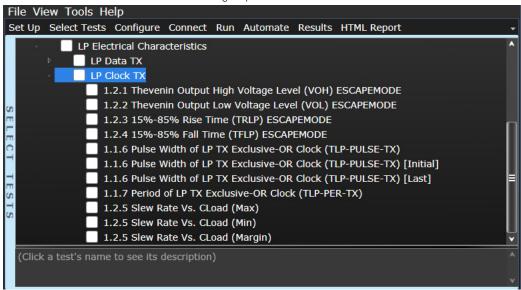

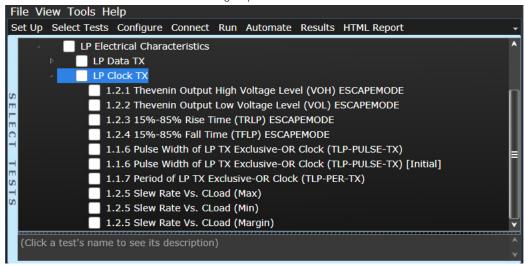

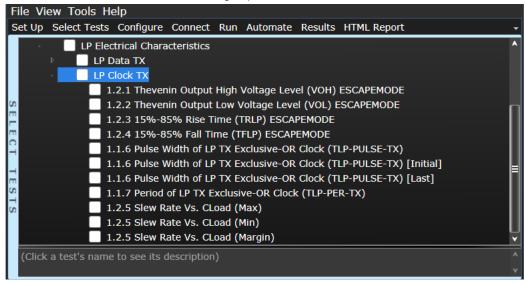

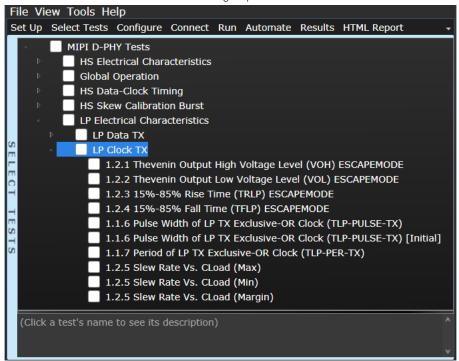

| 7 MIPI D-PHY 1.0 Low Power Clock Transmitter (LP Clock TX) Electrical Tests  Probing for Low Power Transmitter Electrical Tests 120  Test Procedure 120  Test 1.2.1 LP TX Thevenin Output High Voltage Level (V <sub>OH</sub> ) Method of                                                                                |     |

| Implementation 122 PASS Condition 122 Test Availability Condition 122 Measurement Algorithm using Test ID 1821 and 28211 122 Measurement Algorithm using Test ID 18211 123 Test References 123                                                                                                                           |     |

| Test 1.2.2 LP TX Thevenin Output Low Voltage Level ( $V_{OL}$ ) Method of Implementation                                                                                                                                                                                                                                 | 124 |

| PASS Condition 124 Test Availability Condition 124 Measurement Algorithm using Test ID 1822 124 Measurement Algorithm using Test ID 18221 125 Measurement Algorithm using Test ID 28221 125 Test References 125                                                                                                          |     |

| Test                 | 1.2.3 LP TX 15%-85% Rise Time Level (T <sub>RLP</sub> ) Method of Implementation                                                                                                                                | 126 |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| T<br>N               | PASS Condition 126 Fest Availability Condition 126 Measurement Algorithm using Test ID 18241 126 Measurement Algorithm using Test ID 28241 127 Fest References 127                                              |     |

| Test                 | 1.2.4 LP TX 15%-85% Fall Time Level (T <sub>FLP</sub> ) Method of Implementation                                                                                                                                | 28  |

| T<br>N<br>N          | PASS Condition 128 Fest Availability Condition 128 Measurement Algorithm using Test ID 1825 128 Measurement Algorithm using Test ID 18251 129 Measurement Algorithm using Test ID 28251 129 Fest References 129 |     |

| Test                 | <b>1.2.5 LP TX Slew Rate vs. C<sub>LOAD</sub> Method of Implementation</b> 131                                                                                                                                  |     |

| T<br>N               | PASS Condition 131 Fest Availability Condition 131 Measurement Algorithm using Test ID 1829, 18291 and 18292 131 Measurement Algorithm using Test ID 2829, 28291 and 28292 133 Fest References 133              |     |

| Part II<br>Operation |                                                                                                                                                                                                                 |     |

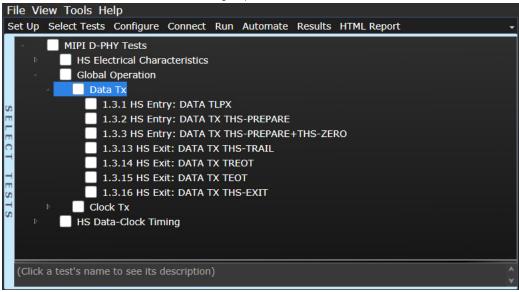

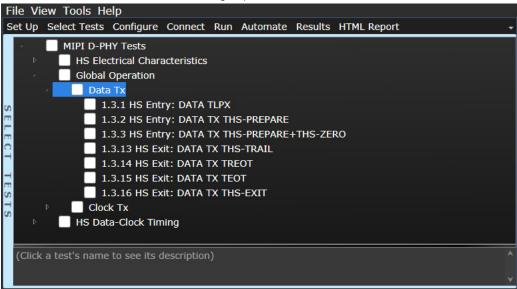

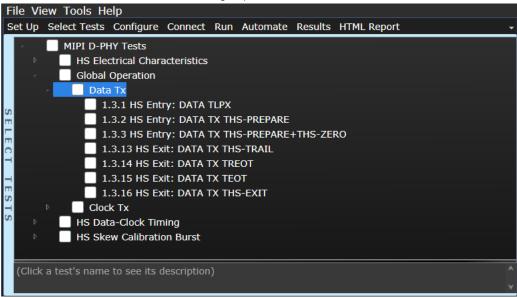

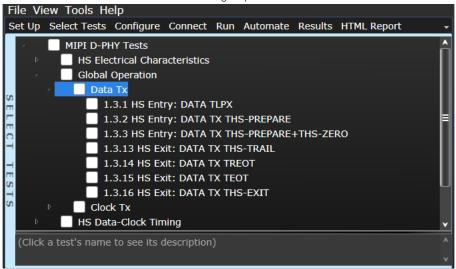

| 8 MIPI D-PHY 1.0     | Data Transmitter (Data TX) Global Operation Tests                                                                                                                                                               |     |

|                      | oing for Data TX Global Operation Tests 138  Test Procedure 138                                                                                                                                                 |     |

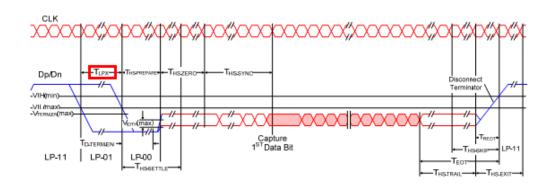

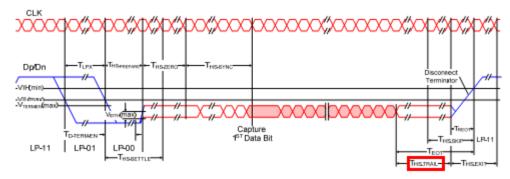

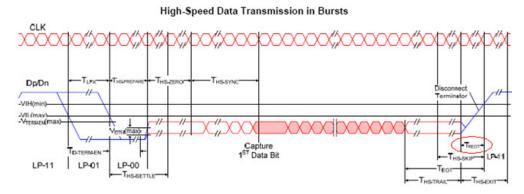

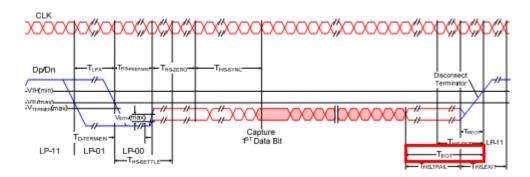

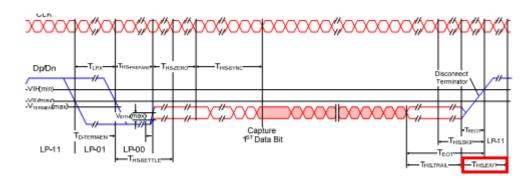

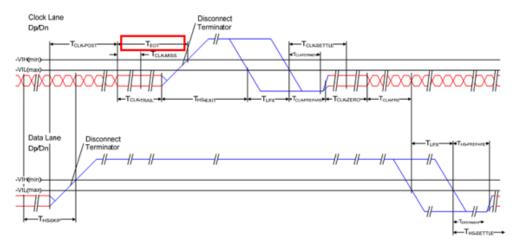

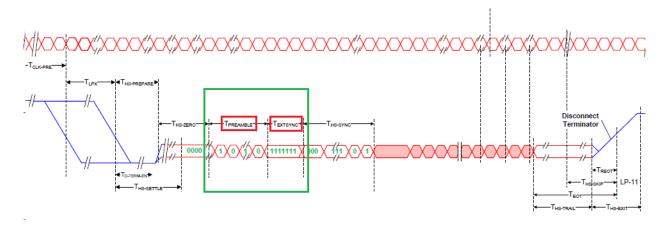

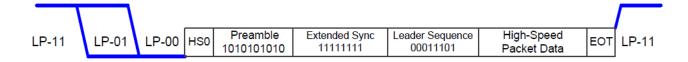

| Test                 | 1.3.1 HS Entry: Data T <sub>LPX</sub> Method of Implementation 140                                                                                                                                              |     |

| T<br>N               | PASS Condition 140 Fest Availability Condition 140 Measurement Algorithm using Test ID 511 140 Fest References 141                                                                                              |     |

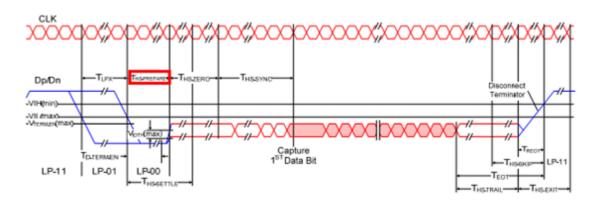

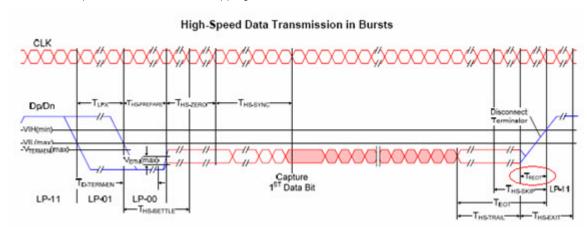

| Test                 | 1.3.2 HS Entry: Data TX T <sub>HS-PREPARE</sub> Method of Implementation 142                                                                                                                                    |     |

| T<br>N               | PASS Condition 142 Fest Availability Condition 142 Measurement Algorithm using Test ID 557 142 Fest References 143                                                                                              |     |

Global Operation

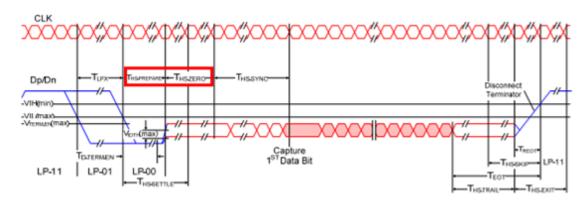

| Test 1.3.3 HS Entry: Data TX T <sub>HS-PREPARE</sub> +                                                          | - T <sub>HS-ZERO</sub> Method of Implementation 144      |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| PASS Condition 144 Test Availability Condition 144 Measurement Algorithm using Test ID 558 Test References 145  | 144                                                      |

| Test 1.3.13 HS Exit: Data TX T <sub>HS-TRAIL</sub> Met                                                          | hod of Implementation 146                                |

| PASS Condition 146 Test Availability Condition 146 Measurement Algorithm using Test ID 546 Test References 147  | 146                                                      |

| Test 1.3.14 LP TX 30%-85% Post -EoT Rise                                                                        | e Time (T <sub>REOT</sub> ) Method of Implementation 148 |

| PASS Condition 148 Test Availability Condition 148 Measurement Algorithm using Test ID 549 Test References 149  | 148                                                      |

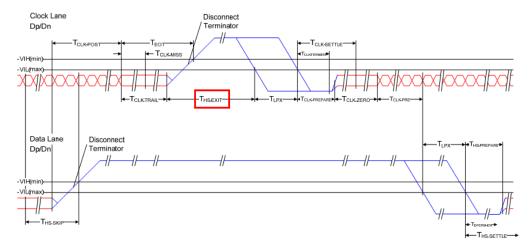

| Test 1.3.15 HS Exit: Data TX T <sub>EOT</sub> Method o                                                          | of Implementation 150                                    |

| PASS Condition 150 Test Availability Condition 150 Measurement Algorithm using Test ID 547 Test References 151  | 150                                                      |

| Test 1.3.16 HS Exit: Data TX T <sub>HS-EXIT</sub> Meth                                                          | od of Implementation 152                                 |

| PASS Condition 152 Test Availability Condition 152 Measurement Algorithm using Test ID 548 Test References 153  | 152                                                      |

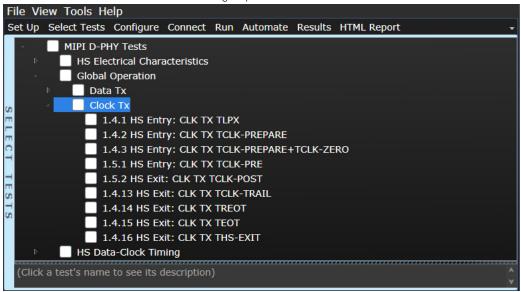

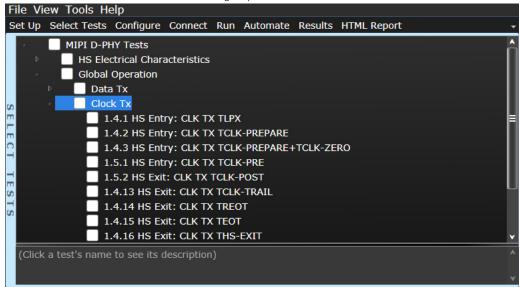

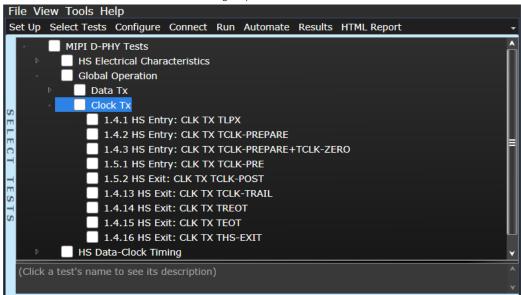

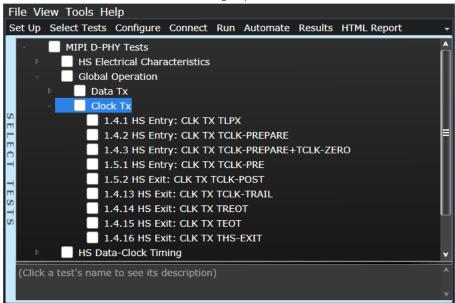

| 9 MIPI D-PHY 1.0 Clock Transmitter (Clock TX) Globa                                                             | l Operation Tests                                        |

| Probing for Clock TX Global Operation Test Test Procedure 157                                                   | ts 156                                                   |

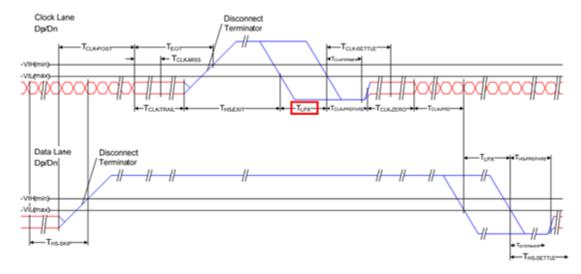

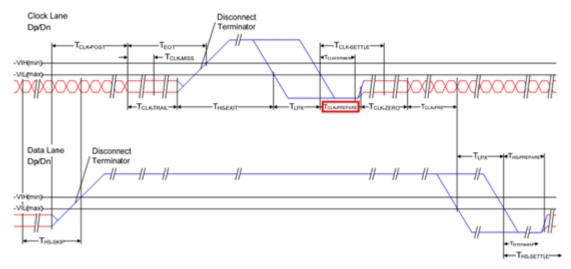

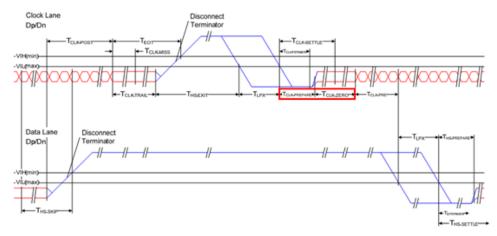

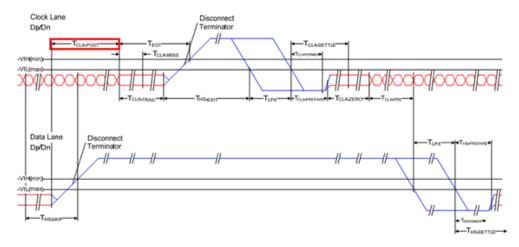

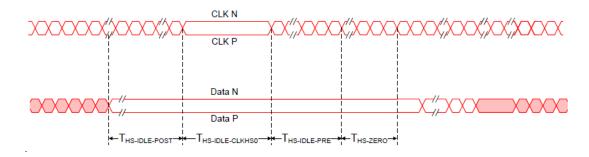

| Test 1.4.1 HS Entry: CLK TX T <sub>LPX</sub> Method o                                                           | f Implementation 158                                     |

| PASS Condition 158 Test Availability Condition 158 Measurement Algorithm using Test ID 5510 Test References 159 | 158                                                      |

| Test 1.4.2 HS Entry: CLK TX T <sub>CLK-PREPARE</sub> N                                                          | Method of Implementation 160                             |

| PASS Condition 160 Test Availability Condition 160 Measurement Algorithm using Test ID 552 Test References 161  | 160                                                      |

| Test 1.4.3 HS Entry: CLK TX T <sub>CLK-PREPARE</sub> +T <sub>C</sub>                                           | LK-ZERO Method of Implementation 162                  |  |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| PASS Condition 162 Test Availability Condition 162 Measurement Algorithm using Test ID 554 Test References 163 | 162                                                   |  |

| Test 1.5.1 HS Entry: CLK TX T <sub>CLK-PRE</sub> Method                                                        | of Implementation 164                                 |  |

| PASS Condition 164 Test Availability Condition 164 Measurement Algorithm using Test ID 551 Test References 165 | 164                                                   |  |

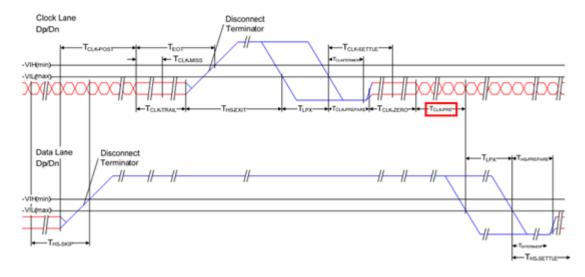

| Test 1.5.2 HS Exit: CLK TX T <sub>CLK-POST</sub> Method                                                        | of Implementation 166                                 |  |

| PASS Condition 166 Test Availability Condition 166 Measurement Algorithm using Test ID 555 Test References 167 | 166                                                   |  |

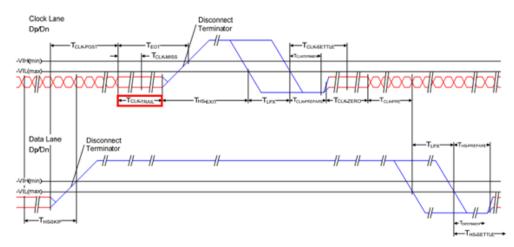

| Test 1.4.13 HS Exit: CLK TX T <sub>CLK-TRAIL</sub> Metho                                                       | od of Implementation 168                              |  |

| PASS Condition 168 Test Availability Condition 168 Measurement Algorithm using Test ID 543 Test References 169 | 168                                                   |  |

| Test 1.4.14 LP TX 30%-85% Post-EoT Rise T                                                                      | ime (T <sub>REOT</sub> ) Method of Implementation 170 |  |

| PASS Condition 170 Test Availability Condition 170 Measurement Algorithm using Test ID 559 Test References 171 | 170                                                   |  |

| Test 1.4.15 HS Exit: CLK TX T <sub>EOT</sub> Method of Implementation 172                                      |                                                       |  |

| PASS Condition 172 Test Availability Condition 172 Measurement Algorithm using Test ID 544 Test References 173 | 172                                                   |  |

| Test 1.4.16 HS Exit: CLK TX T <sub>HS-EXIT</sub> Method                                                        | of Implementation 174                                 |  |

| PASS Condition 174 Test Availability Condition 174 Measurement Algorithm using Test ID 556 Test References 175 | 174                                                   |  |

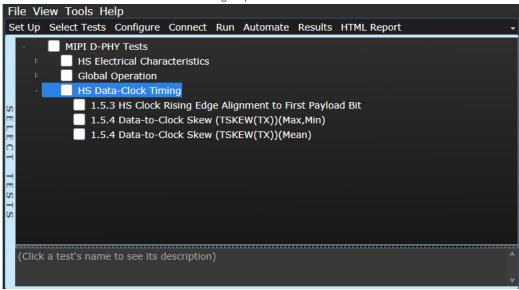

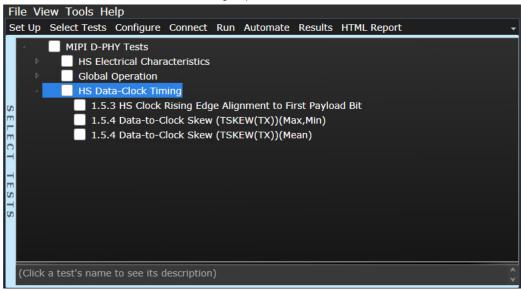

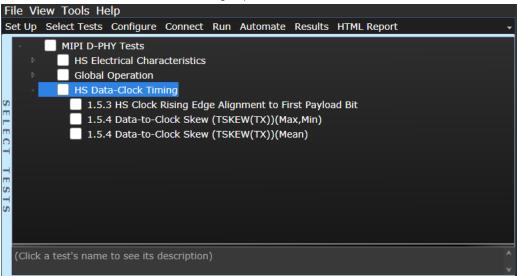

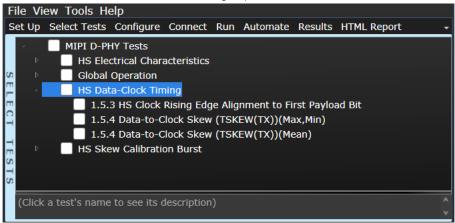

#### Part III HS Data-Clock Timing

#### 10 MIPI D-PHY 1.0 High Speed (HS) Data-Clock Timing Tests

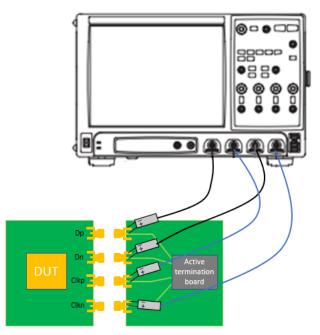

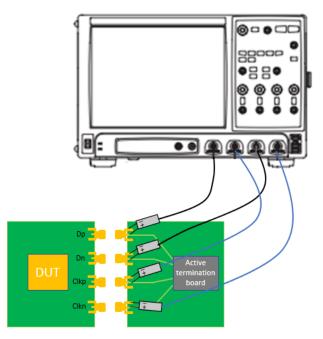

#### Probing for High Speed Data-Clock Timing Tests 180

Test Procedure 180

# Test 1.5.3 HS Clock Rising Edge Alignment to First Payload Bit Method of Implementation 182

PASS Condition 182

Test Availability Condition 182

Measurement Algorithm using Test ID 912 182

Test References 182

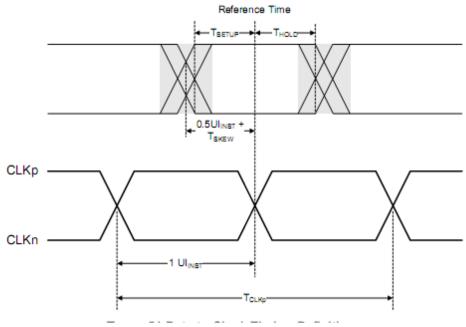

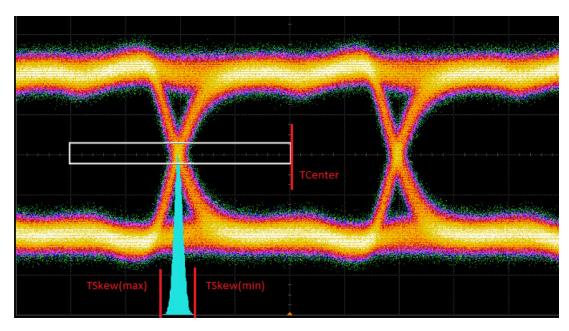

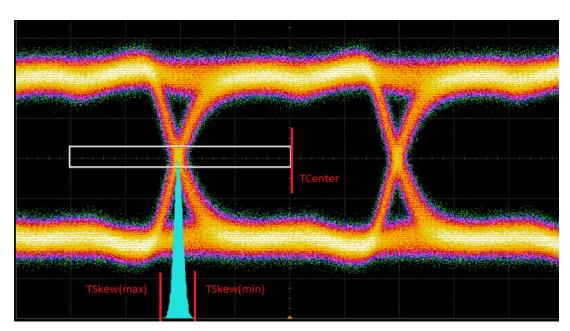

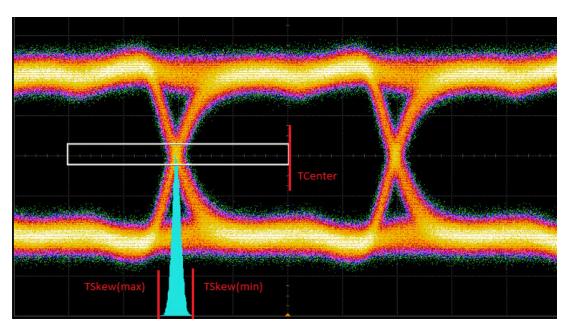

## Test 1.5.4 Data-to-Clock Skew (T<sub>SKEW(TX)</sub>) Method of Implementation 183

PASS Condition 183

Test Availability Condition 183

Measurement Algorithm using Test ID 913 184

Measurement Algorithm using Test ID 9131 185

Test References 185

# Part IV Informative Tests

#### 11 MIPI D-PHY 1.0 Informative Tests

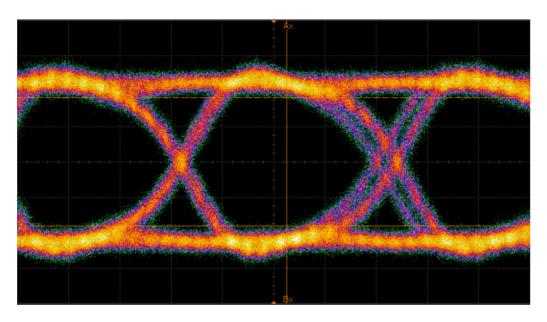

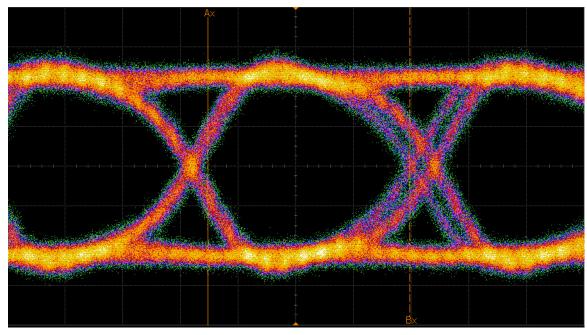

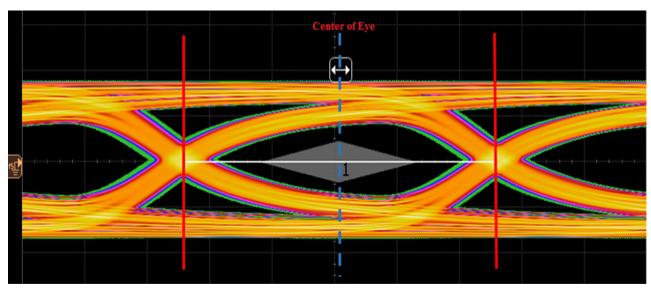

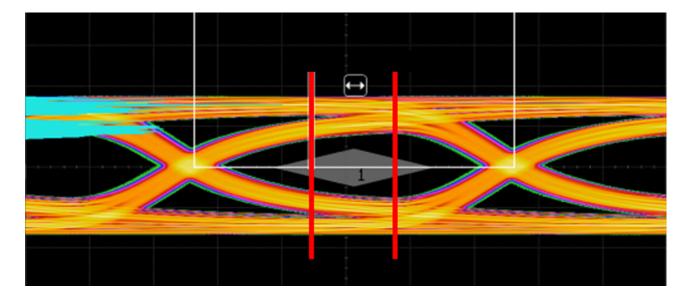

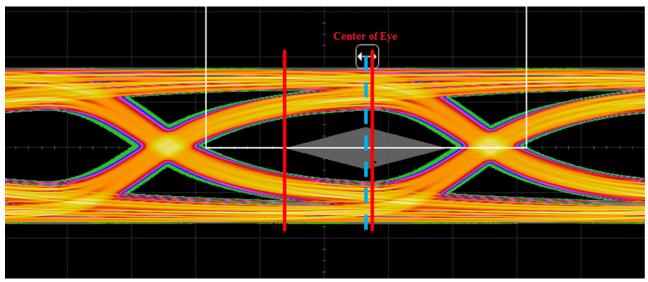

#### HS Data Eye Height (Informative) Method of Implementation 190

PASS Condition 190

Test Availability Condition 190

Measurement Algorithm using Test ID 915 190

Test References 191

#### HS Data Eye Width (Informative) Method of Implementation 192

PASS Condition 192

Test Availability Condition 192

Measurement Algorithm using Test ID 916 193

## Part B MIPI D-PHY 1.1

#### Part I **Electrical Characteristics**

#### 12 MIPI D-PHY 1.1 High Speed Data Transmitter (HS Data TX) Electrical Tests

202

**Probing for High Speed Data Transmitter Electrical Tests** 200

Test Procedure 200

Test 1.3.7 HS Data TX Static Common Mode Voltage (V<sub>CMTX</sub>) Method of

**Implementation** 202 Test References

Test 1.3.8 HS Data TX  $V_{CMTX}$  Mismatch ( $\Delta V_{CMTX}(1.0)$ ) Method of Implementation 202

202 Test References

Test 1.3.10 HS Data TX Common Level Variations Above 450 MHz (ΔV<sub>CMTX</sub>(HF)) Method of

**Implementation** 202

> 202 Test References

Test 1.3.9 HS Data TX Common Level Variations Between 50-450 MHz (ΔV<sub>CMTX</sub>(LF)) Method of Implementation 202

202 **Test References**

Test 1.3.4 HS Data TX Differential Voltage (V<sub>OD</sub>) Method of Implementation 202

Test References

Test 1.3.5 HS Data TX Differential Voltage Mismatch (? Von) Method of

**Implementation** 203

> 203 Test References

Test 1.3.6 HS Data TX Single-Ended Output High Voltage (V<sub>OHHS</sub>) Method of

**Implementation** 203

> 203 Test References

Test 1.3.11 Data Lane HS-TX 20%-80% Rise Time (t<sub>R</sub>) Method of Implementation 203

Test References 203

Test 1.3.12 Data Lane HS-TX 80%-20% Fall Time (t<sub>F</sub>) Method of Implementation 203

Test References 203

#### 13 MIPI D-PHY 1.1 High Speed Clock Transmitter (HS Clock TX) Electrical Tests

**Probing for High Speed Clock Transmitter Electrical Tests** 206

206 Test Procedure

| Test 1.4.7 HS Clock TX Static Common Mode Voltage (V <sub>CMTX</sub> ) Method of Implementation 208  Test References 208                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test 1.4.8 HS Clock TX VCMTX Mismatch (ΔV <sub>CMTX</sub> ( <sub>1,0)</sub> ) Method of Implementation 208                                                                                               |

| Test References 208                                                                                                                                                                                      |

| Test 1.4.10 HS Clock TX Common-Level Variations Above 450 MHz (ΔV <sub>CMTX</sub> (HF)) Method of Implementation 208  Test References 208                                                                |

| Test 1.4.9 HS Clock TX Common-Level Variations Between 50-450 MHz (ΔV <sub>CMTX</sub> (LF))  Method of Implementation 208  Test References 208                                                           |

| Test 1.4.4 HS Clock TX Differential Voltage (V <sub>OD</sub> ) Method of Implementation 208                                                                                                              |

| Test References 208                                                                                                                                                                                      |

| Test 1.4.5 HS Clock TX Differential Voltage Mismatch (ΔV <sub>OD</sub> ) Method of Implementation 209  Test References 209                                                                               |

| Test 1.4.6 HS Clock TX Single-Ended Output High Voltage (V <sub>OHHS</sub> ) Method of Implementation 209  Test References 209                                                                           |

| Test 1.4.11 Clock Lane HS-TX 20%-80% Rise Time (t <sub>R</sub> ) Method of Implementation 209                                                                                                            |

| Test References 209                                                                                                                                                                                      |

| Test 1.4.12 Clock Lane HS-TX 80%-20% Fall Time (t <sub>F</sub> ) Method of Implementation 209  Test References 209                                                                                       |

| Test 1.4.17 HS Clock Instantaneous Method of Implementation 209  Test References 209                                                                                                                     |

| Test 1.4.18 Clock Lane HS Clock Delta UI (UI variation) Method of Implementation  PASS Condition 210  Test Availability Condition 210  Measurement Algorithm using Test ID 1911 210  Test References 210 |

| 14 MIPI D-PHY 1.1 Low Power Data Transmitter (LP Data TX) Electrical Tests                                                                                                                               |

| Probing for Low Power Transmitter Electrical Tests 212  Test Procedure 212                                                                                                                               |

| Test 1.1.1 LP TX Thevenin Output High Voltage Level (V <sub>OH</sub> ) Method of                                                                                                                                          |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Implementation 214  PASS Condition 214  Test Availability Condition 214  Measurement Algorithm using Test ID 821 214  Measurement Algorithm using Test ID 8211 215  Test References 215                                   |     |

| Test 1.1.2 LP TX Thevenin Output Low Voltage Level (V <sub>OL</sub> ) Method of Implementation                                                                                                                            | 216 |

| PASS Condition 216 Test Availability Condition 216 Measurement Algorithm using Test ID 822 216 Measurement Algorithm using Test ID 8221 217 Test References 217                                                           |     |

| Test 1.1.3 LP TX 15%-85% Rise Time Level (T <sub>RLP</sub> ) EscapeMode Method of                                                                                                                                         |     |

| Implementation 218  PASS Condition 218  Test Availability Condition 218  Measurement Algorithm using Test ID 8241 218  Test References 218                                                                                |     |

| Test 1.1.4 LP TX 15%-85% Fall Time Level (T <sub>FLP</sub> ) Method of Implementation 219                                                                                                                                 |     |

| PASS Condition 219 Test Availability Condition 219 Measurement Algorithm using Test ID 825 219 Measurement Algorithm using Test ID 8251 220 Test References 220                                                           |     |

| Test 1.1.6 LP TX Pulse Width of LP TX Exclusive-Or Clock (T <sub>LP-PULSE-TX</sub> ) Method of                                                                                                                            |     |

| Implementation 221  PASS Condition 221  Test Availability Condition 221  Measurement Algorithm using Test IDs 827, 8271 and 8272 223  Measurement Algorithm using Test IDs 1827, 18271 and 18272 223  Test References 224 |     |

| Test 1.1.7 LP TX Period of LP TX Exclusive-OR Clock (T <sub>LP-PER-TX</sub> ) Method of                                                                                                                                   |     |

| Implementation 225                                                                                                                                                                                                        |     |

| PASS Condition 225 Test Availability Condition 225 Measurement Algorithm using Test ID 828 226 Measurement Algorithm using Test ID 1828 226 Test References 226                                                           |     |

| Test 1.1.5 LP TX Slew Rate vs. C <sub>LOAD</sub> Method of Implementation  PASS Condition 227  Test Availability Condition 227  Measurement Algorithm using Test IDs 829, 8291 and 8292 227  Test References 228                                                                                     | 227                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 15 MIPI D-PHY 1.1 Low Power Clock Transmitter (LP Clock TX) Electrical Tests                                                                                                                                                                                                                         |                      |

| Probing for Low Power Transmitter Electrical Tests 230  Test Procedure 230                                                                                                                                                                                                                           |                      |

| Test 1.2.1 LP TX Thevenin Output High Voltage Level (V <sub>OH</sub> ) Method of Implementation 232  PASS Condition 232  Test Availability Condition 232  Measurement Algorithm using Test ID 1821 and 28211 232  Measurement Algorithm using Test ID 18211 234  Test References 234                 | of                   |

| Test 1.2.2 LP TX Thevenin Output Low Voltage Level (V <sub>OL</sub> ) Method of PASS Condition 235  Test Availability Condition 235  Measurement Algorithm using Test ID 1822 235  Measurement Algorithm using Test ID 18221 236  Measurement Algorithm using Test ID 28221 236  Test References 237 | f Implementation 235 |

| Test 1.2.3 LP TX 15%-85% Rise Time Level (T <sub>RLP</sub> ) Method of Implemed PASS Condition 238  Test Availability Condition 238  Measurement Algorithm using Test ID 18241 238  Measurement Algorithm using Test ID 28241 239  Test References 239                                               | nentation 238        |

| Test 1.2.4 LP TX 15%-85% Fall Time Level (T <sub>FLP</sub> ) Method of Implementary PASS Condition 240  Test Availability Condition 240                                                                                                                                                              | entation 240         |

| Measurement Algorithm using Test ID 1825 240  Measurement Algorithm using Test ID 18251 241  Measurement Algorithm using Test ID 28251 241  Test References 242                                                                                                                                      |                      |

| Test 1.2.5 LP TX Slew Rate vs. C <sub>LOAD</sub> Meth                                                                                                    | hod of Implementation 243                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| PASS Condition 243 Test Availability Condition 243 Measurement Algorithm using Test ID 1829 Measurement Algorithm using Test ID 2829 Test References 246 |                                                          |

| Part II<br>Global Operation                                                                                                                              |                                                          |

| 16 MIPI D-PHY 1.1 Data Transmitter (Data TX) Global (                                                                                                    | Operation Tests                                          |

| Probing for Data TX Global Operation Test  Test Procedure 250                                                                                            | <b>es</b> 250                                            |

| Test 1.3.1 HS Entry: Data T <sub>LPX</sub> Method of I  Test References 252                                                                              | Implementation 252                                       |

| Test 1.3.2 HS Entry: Data TX T <sub>HS-PREPARE</sub> I  Test References 252                                                                              | Method of Implementation 252                             |

| Test 1.3.3 HS Entry: Data TX T <sub>HS-PREPARE</sub> - Test References 252                                                                               | + T <sub>HS-ZERO</sub> Method of Implementation 252      |

| Test 1.3.13 HS Exit: Data TX T <sub>HS-TRAIL</sub> Met  Test References 252                                                                              | thod of Implementation 252                               |

| Test 1.3.14 LP TX 30%-85% Post -EoT Ris  Test References 252                                                                                             | e Time (T <sub>REOT</sub> ) Method of Implementation 252 |

| Test 1.3.15 HS Exit: Data TX T <sub>EOT</sub> Method  Test References 252                                                                                | of Implementation 252                                    |

| Test 1.3.16 HS Exit: Data TX T <sub>HS-EXIT</sub> Meth<br>Test References 253                                                                            | nod of Implementation 253                                |

| 17 MIPI D-PHY 1.1 Clock Transmitter (Clock TX) Globa                                                                                                     | al Operation Tests                                       |

| Probing for Clock TX Global Operation Test Test Procedure 257                                                                                            | sts 256                                                  |

| Test 1.4.1 HS Entry: CLK TX T <sub>LPX</sub> Method of                                                                                                   | of Implementation 258                                    |

| Test References 258                                                                                                                                      | Mathadaflandanadatha 050                                 |

| Test 1.4.2 HS Entry: CLK TX T <sub>CLK-PREPARE</sub> Test References 258                                                                                 | Method of Implementation 258                             |

| Test 1.4.3 HS Entry:  | CLK TX T <sub>CLK-PREPARE</sub> +T <sub>CLK-ZERO</sub> Method of Imp | plementation               | 258          |

|-----------------------|----------------------------------------------------------------------|----------------------------|--------------|

| Test References       | 258                                                                  |                            |              |

| Test 1.5.1 HS Entry:  | CLK TX T <sub>CLK-PRE</sub> Method of Implementation                 | 258                        |              |

| Test References       | 258                                                                  |                            |              |

| Test 1.5.2 HS Exit: ( | CLK TX T <sub>CLK-POST</sub> Method of Implementation                | 258                        |              |

| Test References       | 258                                                                  |                            |              |

| Test 1.4.13 HS Exit:  | CLK TX $T_{CLK-TRAIL}$ Method of Implementation                      | 258                        |              |

| Test References       | 258                                                                  |                            |              |

| Test 1.4.14 LP TX 30  | $0\%$ -85% Post-EoT Rise Time (T $_{REOT}$ ) Method of               | <sup>†</sup> Implementatio | <b>n</b> 259 |

| Test References       | 259                                                                  |                            |              |

| Test 1.4.15 HS Exit:  | CLK TX T <sub>EOT</sub> Method of Implementation 259                 | 9                          |              |

| Test References       | 259                                                                  |                            |              |

| Test 1.4.16 HS Exit:  | CLK TX T <sub>HS-EXIT</sub> Method of Implementation                 | 259                        |              |

| Test References       | 259                                                                  |                            |              |

| Data_Clock Timing     |                                                                      |                            |              |

## Part III HS Data-Clock Timing

## 18 MIPI D-PHY 1.1 High Speed (HS) Data-Clock Timing Tests

**Probing for High Speed Data-Clock Timing Tests** 264

Test Procedure 264

Test 1.5.3 HS Clock Rising Edge Alignment to First Payload Bit Method of Implementation 266

Test References 266

Test 1.5.4 Data-to-Clock Skew (T<sub>SKEW(TX)</sub>) Method of Implementation 266

# Part IV Informative Tests

#### 19 MIPI D-PHY 1.1 Informative Tests

Part C MIPI D-PHY 1.2

Part I Electrical Characteristics

#### 20 MIPI D-PHY 1.2 High Speed Data Transmitter (HS Data TX) Electrical Tests

**Probing for High Speed Data Transmitter Electrical Tests** 276

Test Procedure 276

Test 1.3.7 HS Data TX Static Common Mode Voltage (V<sub>CMTX</sub>) Method of

**Implementation** 278

Test References 278

Test 1.3.8 HS Data TX  $V_{CMTX}$  Mismatch ( $\Delta V_{CMTX}(1.0)$ ) Method of Implementation 278

Test References 278

Test 1.3.10 HS Data TX Common Level Variations Above 450 MHz (ΔV<sub>CMTX</sub>(HF)) Method of

**Implementation** 278

Test References 278

Test 1.3.9 HS Data TX Common Level Variations Between 50-450 MHz ( $\Delta V_{CMTX}(LF)$ ) Method of Implementation 278

Test References 278

Test 1.3.4 HS Data TX Differential Voltage (V<sub>OD</sub>) Method of Implementation 278

Test References 278

Test 1.3.5 HS Data TX Differential Voltage Mismatch (ΔV<sub>OD</sub>) Method of

Implementation 279

Test References 279

Test 1.3.6 HS Data TX Single-Ended Output High Voltage (V<sub>OHHS</sub>) Method of

**Implementation** 279

|              | Test 1.3.11 Data Lane HS-TX 20%-80% Rise                                                                                                                                                                                                       | Time (t <sub>R</sub> ) Method of Implementation   | 280       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------|

|              | PASS Condition 280 Test Availability Condition 280 Measurement Algorithm using Test ID 81101 Measurement Algorithm using Test ID 81102 Measurement Algorithm using Test ID 81104 Measurement Algorithm using Test ID 81105 Test References 282 | 280<br>281<br>281<br>282                          |           |

|              | Test 1.3.12 Data Lane HS-TX 80%-20% Fall                                                                                                                                                                                                       | Time (t <sub>F</sub> ) Method of Implementation   | 283       |

|              | PASS Condition 283 Test Availability Condition 283 Measurement Algorithm using Test ID 81111 Measurement Algorithm using Test ID 81112 Measurement Algorithm using Test ID 81114 Measurement Algorithm using Test ID 81115 Test References 285 | 283<br>284<br>284<br>285                          |           |

|              | Test 1.4.9 HS Clock TX Common-Level Varia Method of Implementation 286  Test References 286                                                                                                                                                    | tions Between 50-450 MHz (ΔV <sub>CMTX</sub> (L   | .F))      |

| 21 MIPI D-PH | HY 1.2 High Speed Clock Transmitter (HS Cl                                                                                                                                                                                                     | ock TX) Electrical Tests                          |           |

|              | Probing for High Speed Clock Transmitter Electronic Test Procedure 288                                                                                                                                                                         | ectrical Tests 288                                |           |

|              | Test 1.4.7 HS Clock TX Static Common Mode Implementation 290  Test References 290                                                                                                                                                              | e Voltage (V <sub>CMTX</sub> ) Method of          |           |

|              | Test 1.4.8 HS Clock TX VCMTX Mismatch (Δ                                                                                                                                                                                                       | $V_{\mathrm{CMTX}}(1,0)$ Method of Implementation | 290       |

|              | Test References 290                                                                                                                                                                                                                            |                                                   |           |

|              | Test 1.4.10 HS Clock TX Common-Level Vari<br>Implementation 290<br>Test References 290                                                                                                                                                         | ations Above 450 MHz (ΔV <sub>CMTX</sub> (HF)) Ν  | lethod of |

|              | Test 1.4.4 HS Clock TX Differential Voltage (                                                                                                                                                                                                  | V <sub>OD</sub> ) Method of Implementation 29     | 0         |

|              | Test References 290                                                                                                                                                                                                                            |                                                   |           |

|              | Test 1.4.5 HS Clock TX Differential Voltage No. 1290 Test References 290                                                                                                                                                                       | /lismatch (ΔV <sub>OD</sub> ) Method of           |           |

| Test 1.4.6 HS Clock TX Single-Ended Output High Voltage (V <sub>OHHS</sub> ) Method of Implementation 291  Test References 291                                                                                                                                                                                                                                   |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Test 1.4.11 Clock Lane HS-TX 20%-80% Rise Time (t <sub>R</sub> ) Method of Implementation 29                                                                                                                                                                                                                                                                     | 2   |

| PASS Condition 292 Test Availability Condition 292 Measurement Algorithm using Test ID 181101 292 Measurement Algorithm using Test ID 181102 293 Measurement Algorithm using Test ID 181103 293 Measurement Algorithm using Test ID 181104 294 Measurement Algorithm using Test ID 181105 294 Measurement Algorithm using Test ID 181106 294 Test References 294 |     |

| Test 1.4.12 Clock Lane HS-TX 80%-20% Fall Time (t <sub>F</sub> ) Method of Implementation 295                                                                                                                                                                                                                                                                    |     |

| PASS Condition 295 Test Availability Condition 295 Measurement Algorithm using Test ID 181111 296 Measurement Algorithm using Test ID 181112 296 Measurement Algorithm using Test ID 181113 297 Measurement Algorithm using Test ID 181114 297 Measurement Algorithm using Test ID 181115 297 Measurement Algorithm using Test ID 181116 298 Test References 298 |     |

| Test 1.4.17 HS Clock Instantaneous Method of Implementation 299                                                                                                                                                                                                                                                                                                  |     |

| Test References 299  Test 1.4.18 Clock Lane HS Clock Delta UI (UI variation) Method of Implementation 300  PASS Condition 300  Test Availability Condition 300  Measurement Algorithm using Test ID 1911 300  Test References 300                                                                                                                                | 10  |

| MIPI D-PHY 1.2 Low Power Data Transmitter (LP Data TX) Electrical Tests                                                                                                                                                                                                                                                                                          |     |

| Probing for Low Power Transmitter Electrical Tests 302  Test Procedure 302                                                                                                                                                                                                                                                                                       |     |

| Test 1.1.1 LP TX Thevenin Output High Voltage Level (V <sub>OH</sub> ) Method of Implementation 304  Test References 304                                                                                                                                                                                                                                         |     |

| Test 1.1.2 LP TX Thevenin Output Low Voltage Level (V <sub>OL</sub> ) Method of Implementation  Test References 304                                                                                                                                                                                                                                              | 304 |

| Test 1.1.3 LP TX 15%-85% Rise T Implementation 304                                                                                                                                                | Fime Level (T <sub>RLP</sub> ) EscapeMode Method of             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|

| Test References 304                                                                                                                                                                               |                                                                 |     |

| Test 1.1.4 LP TX 15%-85% Fall Ti                                                                                                                                                                  | ime Level (T <sub>FLP</sub> ) Method of Implementation 304      |     |

| Test References 304                                                                                                                                                                               | · ·                                                             |     |

| Test 1.1.6 LP TX Pulse Width of L Implementation 305  PASS Condition 305  Test Availability Condition 305  Measurement Algorithm using Test Measurement Algorithm using Test Test References 307  | st IDs 827, 8271 and 8272 306                                   |     |

| Test 1.1.7 LP TX Period of LP TX E Implementation 308  PASS Condition 308  Test Availability Condition 308  Measurement Algorithm using Test Measurement Algorithm using Test Test References 309 | st ID 828 309                                                   |     |

| Test 1.1.5 LP TX Slew Rate vs. C <sub>L</sub> PASS Condition 310  Test Availability Condition 310  Measurement Algorithm using Test Test References 311                                           | )                                                               |     |

| 23 MIPI D-PHY 1.2 Low Power Clock Transmit                                                                                                                                                        | tter (LP Clock TX) Electrical Tests                             |     |

| Probing for Low Power Transmitted Test Procedure 314                                                                                                                                              | er Electrical Tests 314                                         |     |

| Test 1.2.1 LP TX Thevenin Output Implementation 316  Test References 316                                                                                                                          | t High Voltage Level (V <sub>OH</sub> ) Method of               |     |

| Test 1.2.2 LP TX Thevenin Output                                                                                                                                                                  | t Low Voltage Level (V <sub>OL</sub> ) Method of Implementation | 316 |

| Test References 316                                                                                                                                                                               |                                                                 |     |

|                                                                                                                                                                                                   | Fime Level (T <sub>RLP</sub> ) Method of Implementation 316     |     |

| Test References 316                                                                                                                                                                               |                                                                 |     |

|                                                                                                                                                                                                   | ime Level (T <sub>FLP</sub> ) Method of Implementation 316      |     |

| Test References 316                                                                                                                                                                               |                                                                 |     |

|              | Test 1.2.5 LP TX Slew Rate vs. C <sub>LOAD</sub> Method of Implementation 317                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------|

|              | PASS Condition 317                                                                                                           |

|              | Test Availability Condition 317                                                                                              |

|              | Measurement Algorithm using Test ID 1829, 18291 and 18292 318  Measurement Algorithm using Test ID 2829, 28291 and 28292 319 |

|              | 320                                                                                                                          |

|              | Test References 320                                                                                                          |

| Part II      |                                                                                                                              |

| al Operatior |                                                                                                                              |

| 24 MIPI D    | -PHY 1.2 Data Transmitter (Data TX) Global Operation Tests                                                                   |

|              | Probing for Data TX Global Operation Tests 324                                                                               |

|              | Test Procedure 324                                                                                                           |

|              | Test 1.3.1 HS Entry: Data T <sub>LPX</sub> Method of Implementation 326                                                      |

|              | Test References 326                                                                                                          |

|              | Test 1.3.2 HS Entry: Data TX T <sub>HS-PREPARE</sub> Method of Implementation 326                                            |

|              | Test References 326                                                                                                          |

|              | Test 1.3.3 HS Entry: Data TX T <sub>HS-PREPARE</sub> + T <sub>HS-ZERO</sub> Method of Implementation 326                     |

|              | Test References 326                                                                                                          |

|              | Test 1.3.13 HS Exit: Data TX T <sub>HS-TRAIL</sub> Method of Implementation 326                                              |

|              | Test References 326                                                                                                          |

|              | Test 1.3.14 LP TX 30%-85% Post -EoT Rise Time (T <sub>REOT</sub> ) Method of Implementation 326                              |

|              | Measurement Algorithm using Test ID 549 326                                                                                  |

|              | Test References 327                                                                                                          |

|              | Test 1.3.15 HS Exit: Data TX T <sub>EOT</sub> Method of Implementation 328                                                   |

|              | Measurement Algorithm using Test ID 547 328 Test References 328                                                              |

|              | Test 1.3.16 HS Exit: Data TX T <sub>HS-EXIT</sub> Method of Implementation 328                                               |

|              | Test References 328                                                                                                          |

| 25 MIPI D    | -PHY 1.2 Clock Transmitter (Clock TX) Global Operation Tests                                                                 |

|              | Probing for Clock TX Global Operation Tests 330                                                                              |

|              | Test Procedure 331                                                                                                           |

|              | Test 1.4.1 HS Entry: CLK TX T <sub>LPX</sub> Method of Implementation 332                                                    |

|              | Test References 332                                                                                                          |

Global Operation

|    | Test 1.4.2 HS Entry: CLK TX T <sub>CLK-PREPARE</sub> Method of Implementation 332  Test References 332           |

|----|------------------------------------------------------------------------------------------------------------------|

|    | Test 1.4.3 HS Entry: CLK TX T <sub>CLK-PREPARE</sub> +T <sub>CLK-ZERO</sub> Method of Implementation 332         |

|    | Test References 332                                                                                              |

|    | Test 1.5.1 HS Entry: CLK TX T <sub>CLK-PRE</sub> Method of Implementation 332                                    |

|    | Test References 332                                                                                              |

|    | Test 1.5.2 HS Exit: CLK TX T <sub>CLK-POST</sub> Method of Implementation 332                                    |

|    | Test References 332                                                                                              |

|    | Test 1.4.13 HS Exit: CLK TX T <sub>CLK-TRAIL</sub> Method of Implementation 332                                  |

|    | Test References 332                                                                                              |

|    | Test 1.4.14 LP TX 30%-85% Post-EoT Rise Time (T <sub>REOT</sub> ) Method of Implementation 333                   |

|    | Measurement Algorithm using Test ID 559 333 Test References 333                                                  |

|    | Test 1.4.15 HS Exit: CLK TX T <sub>EOT</sub> Method of Implementation 333                                        |

|    | Measurement Algorithm using Test ID 544 333 Test References 334                                                  |

|    | Test 1.4.16 HS Exit: CLK TX T <sub>HS-EXIT</sub> Method of Implementation 334                                    |

|    | Test References 334                                                                                              |

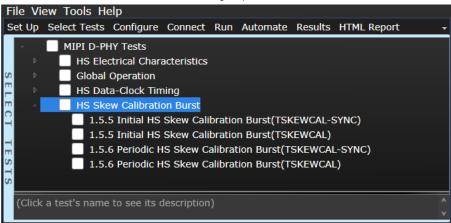

|    | Part III HS Data-Clock Timing & HS Skew Calibration Burst                                                        |

| 26 | MIPI D-PHY 1.2 High Speed (HS) Data-Clock Timing Tests                                                           |

|    | Probing for High Speed Data-Clock Timing Tests 338  Test Procedure 338                                           |

|    | Test 1.5.3 HS Clock Rising Edge Alignment to First Payload Bit Method of Implementation 340  Test References 340 |

|    | Test 1.5.4 Data-to-Clock Skew (T <sub>SKEW(TX)</sub> ) Method of Implementation 340                              |

|    | Measurement Algorithm using Test ID 913 340 Test References 341                                                  |

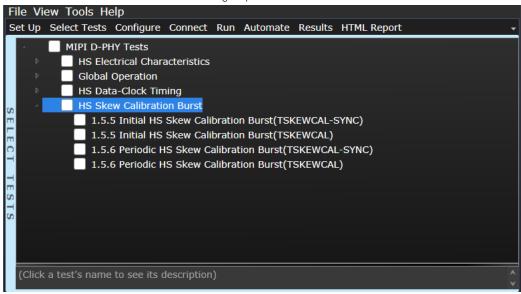

| 27 | MIPI D-PHY 1.2 High Speed (HS) Skew Calibration Burst Tests                                                      |

|    | Probing for High Speed Skew Calibration Burst Tests 344  Test Procedure 344                                      |

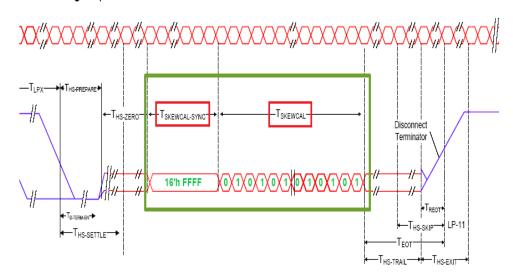

# Test 1.5.5 Initial HS Skew Calibration Burst (TSKEWCAL-SYNC, TSKEWCAL) Method of Implementation 346

PASS Condition 346

Test Availability Condition 346

Measurement Algorithm using Test ID 917 347

Measurement Algorithm using Test ID 918 347

Test References 347

# Test 1.5.6 Periodic HS Skew Calibration Burst (TSKEWCAL-SYNC, TSKEWCAL) Method of Implementation 348

PASS Condition 348

Test Availability Condition 348

Measurement Algorithm using Test ID 919 348

Measurement Algorithm using Test ID 920 349

Test References 349

Part IV Informative Tests

#### 28 MIPI D-PHY 1.2 Informative Tests

Part D MIPI D-PHY 2.0 & 2.1

Part I Electrical Characteristics

## 29 MIPI D-PHY 2.0 & 2.1 High Speed Data Transmitter (HS Data TX) Electrical Tests

Probing for High Speed Data Transmitter Electrical Tests 360

Test Procedure 360

Test 1.3.7 HS Data TX Static Common Mode Voltage (V<sub>CMTX</sub>) Method of

Implementation 362

Test References 362

Test 1.3.8 HS Data TX  $V_{CMTX}$  Mismatch ( $\Delta V_{CMTX}(1,0)$ ) Method of Implementation 362

Test References 362

Test 1.3.10 HS Data TX Common Level Variations Above 450 MHz (ΔV<sub>CMTX</sub>(HF)) Method of Implementation 362

Test References 362

# Test 1.3.9 HS Data TX Common Level Variations Between 50-450 MHz ( $\Delta V_{CMTX}(LF)$ ) Method of Implementation 362

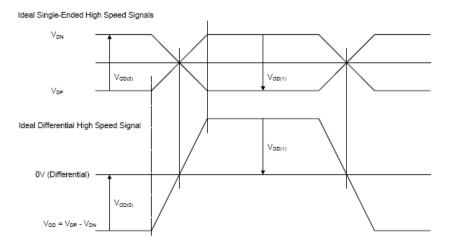

| Test 1.3.4 HS Data TX Differential Voltage (No PASS Condition 363 Test Availability Condition 364 Measurement Algorithm using Test IDs 8131, 17                                                                                                                                                |                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Test 1.3.5 HS Data TX Differential Voltage M Implementation 366  PASS Condition 366  Test Availability Condition 367  Measurement Algorithm using Test ID 8141 ar Test References 368                                                                                                          |                                                     |

| Test 1.3.6 HS Data TX Single-Ended Output Implementation 369  Test References 369                                                                                                                                                                                                              | High Voltage (V <sub>OHHS</sub> ) Method of         |

| PASS Condition 370 Test Availability Condition 370 Measurement Algorithm using Test ID 81101 Measurement Algorithm using Test ID 81102 Measurement Algorithm using Test ID 81104 Measurement Algorithm using Test ID 81105 Test References 372                                                 | 370 370 371 371 372                                 |

| Test 1.3.12 Data Lane HS-TX 80%-20% Fall  PASS Condition 373  Test Availability Condition 373  Measurement Algorithm using Test ID 81111  Measurement Algorithm using Test ID 81112  Measurement Algorithm using Test ID 81114  Measurement Algorithm using Test ID 81115  Test References 375 | 373<br>374<br>374                                   |

| Test 1.4.9 HS Clock TX Common-Level Varia<br>Method of Implementation 376<br>Test References 376                                                                                                                                                                                               | ations Between 50-450 MHz (ΔV <sub>CMTX</sub> (LF)) |

| 30 MIPI D-PHY 2.0 & 2.1 High Speed Clock Transmitter  Probing for High Speed Clock Transmitter El  Test Procedure 378  Test 1.4.7 HS Clock TX Static Common Mod                                                                                                                                | lectrical Tests 378                                 |

| Implementation 380 Test References 380                                                                                                                                                                                                                                                         |                                                     |

| Test 1.4.8 HS Clock TX VCMTX Mismatch (ΔV) Test References 380                                                       | <sub>CMTX</sub> ( <sub>1,0)</sub> ) Method of Implementation | 380      |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------|

|                                                                                                                      |                                                              |          |

| Test 1.4.10 HS Clock TX Common-Level Varia                                                                           | tions Above 450 MHz (ΔV <sub>CMTX</sub> (HF)) Me             | ethod of |