# Keysight D9030TBTC Thunderbolt 3 Test Application

#### **Notices**

© Keysight Technologies 2014-2020

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### Trademarks

UNIX is a registered trademark of UNIX System Laboratories in the U.S.A. and other countries. Target is copyrighted by Thru-Put Systems, Inc.

Version

Version 1.20.0.0

Edition

February 2020

Available in electronic format only

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS **COVERING THE MATERIAL IN THIS** DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

Safety Notices

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Contents

| 4 | $\sim$  |            |     |     |    |

|---|---------|------------|-----|-----|----|

| П | I۱      | νe         | n/  | ΙΔ۱ | ٨/ |

|   | <br>. , | $v \vdash$ | ΙVΙ | 117 | w  |

| Thunderbolt 3 Automated Testing-At a Glance 24                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Required Equipment and Software 25  Hardware 25  Software 25  Licensing information 25                                               |

| In This Book 27 See Also 27 References 27                                                                                            |

| 2 Installing the Test Application and Licenses                                                                                       |

| Installing the Test Application 30                                                                                                   |

| Using Keysight License Manager 5 31 Using Keysight License Manager 6 32                                                              |

| 3 Preparing to Take Measurements                                                                                                     |

| Calibrating the Oscilloscope 36                                                                                                      |

| Starting the Thunderbolt 3 Test Application 37                                                                                       |

| <b>Setting up the Thunderbolt 3 Test Application</b> 40                                                                              |

| Calibration Setup for Compliance Tests 47  Channel Skew Calibration 47  Preset Calibration 50  CTLE Calibration 52  Power Profile 54 |

| 4 Host / Device Thunderbolt 3 Transmitter Testing                                                                                    |

| System Components in Thunderbolt Technology 56                                                                                       |

Overview 56

| 3rd Generation Thunderbolt Compliance Methodology  System Compliance Test Point Definitions 59  AC Coupling Capacitors 59  Jitter and Eye Measurement Methodology 60  Reference Equalization Function 61                                                                                                    |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Requirements for Host / Device Transmitter Compliance 64  Host / Device Transmitter Specifications for both Gen2 and Gen3 devices (all bit-rates)  Host / Device Transmitter Compliance Specifications for Gen2 Connections 68  Host / Device Transmitter Compliance Specifications for Gen3 Connections 71 | 64 |

| <b>Transmitter Test Setup</b> 73 Connecting to the DUT 73                                                                                                                                                                                                                                                   |    |

| 5 Transmitter Tests for 10.3125 GB/s Systems                                                                                                                                                                                                                                                                |    |

| Tx Preset Calibration 76  Test Overview 76  Test Setup 76  Test Procedure 77  Expected / Observable Results 77  Test References 77                                                                                                                                                                          |    |

| Tx CTLE Calibration 78                                                                                                                                                                                                                                                                                      |    |

| Test Overview 78 Test Setup 78 Test Procedure 79 Expected / Observable Results 81 Test References 81                                                                                                                                                                                                        |    |

| Tx Rise/Fall Time 82                                                                                                                                                                                                                                                                                        |    |

| Test Overview 82 Test Pass Requirement 82 Test Setup 82 Test Procedure 83 Expected / Observable Results 83 Test References 83                                                                                                                                                                               |    |

| Tx Total Jitter 84                                                                                                                                                                                                                                                                                          |    |

| Test Overview 84  Test Pass Requirement 84  Test Setup 84  Test Procedure 85                                                                                                                                                                                                                                |    |

Expected / Observable Results 86

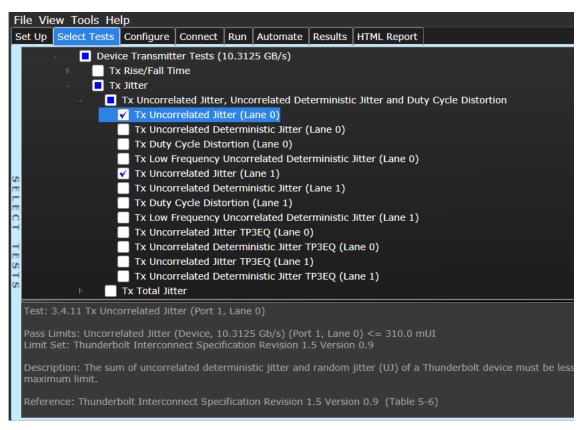

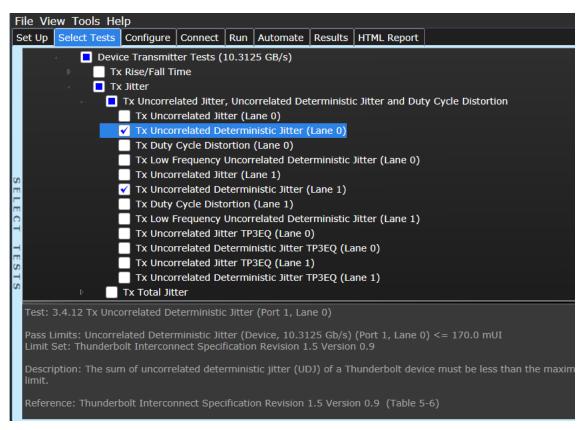

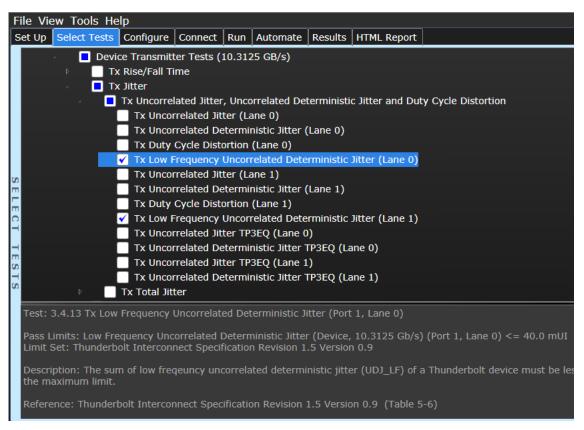

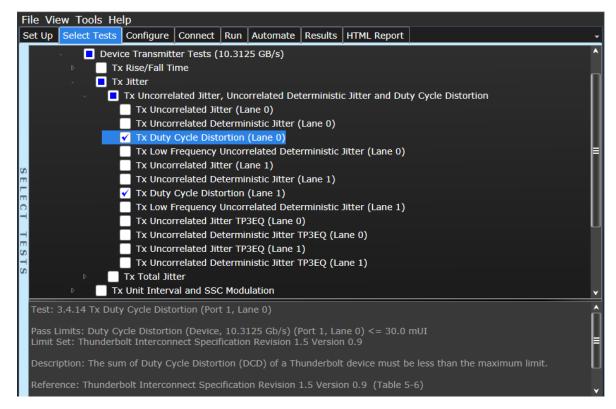

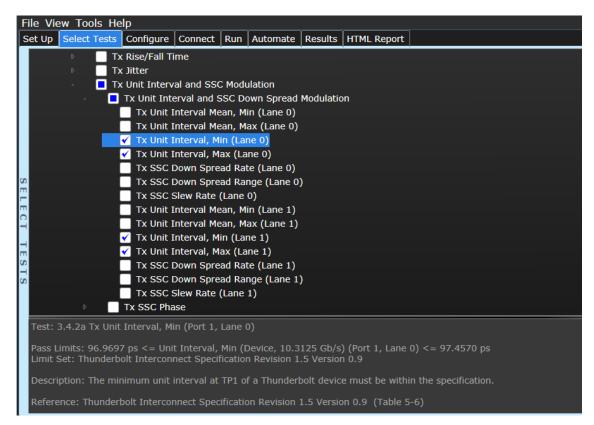

#### Tx Uncorrelated Jitter 87 Test Overview Test Pass Requirement 87 Test Setup 87 Test Procedure 88 Expected / Observable Results 89 Test References Tx Uncorrelated Deterministic Jitter 90 90 Test Overview Test Pass Requirement Test Setup 90 Test Procedure 91 Expected / Observable Results 91 Test References 92 Tx Low Frequency Uncorrelated Deterministic Jitter 93 Test Overview 93 Test Pass Requirement 93 Test Setup 93 Test Procedure 94 Expected / Observable Results 95 Test References 95 Tx Duty Cycle Distortion 96 Test Overview Test Pass Requirement 96 Test Setup 96 Test Procedure 97 Expected / Observable Results 97 Test References 97 Tx Unit Interval Test Overview 98 Test Pass Requirement 98 Test Setup 98 Test Procedure 99 Expected / Observable Results 99 99 Test References

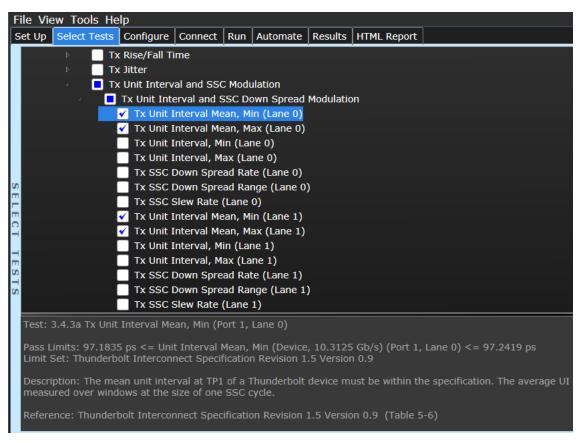

#### Tx Unit Interval Mean 100

Test Overview 100

Test Pass Requirement 100

Test Setup 100

Test Procedure 101

Expected / Observable Results 102

Test References 102

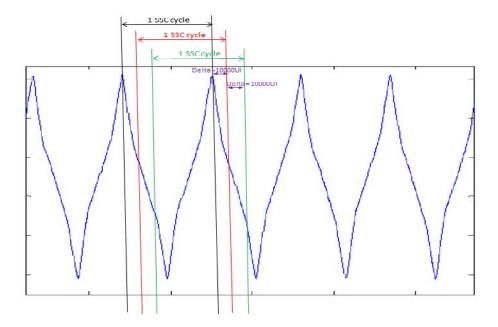

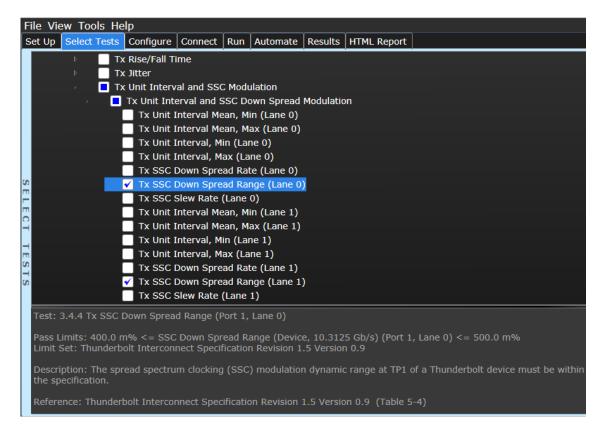

#### Tx SSC Down Spread Range 103

Test Overview 103

Test Pass Requirement 103

Test Setup 103

Test Procedure 104

Expected / Observable Results 104

Test References 104

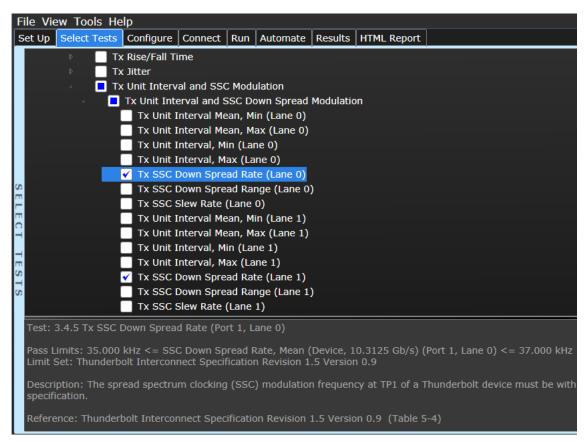

#### Tx SSC Down Spread Rate 105

Test Overview 105

Test Pass Requirement 105

Test Setup 105

Test Procedure 106

Expected / Observable Results 106

Test References 106

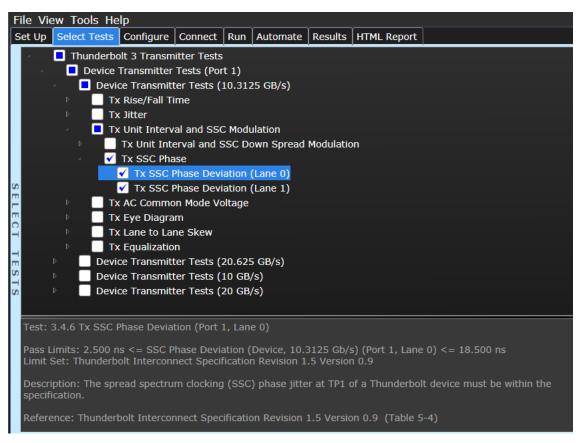

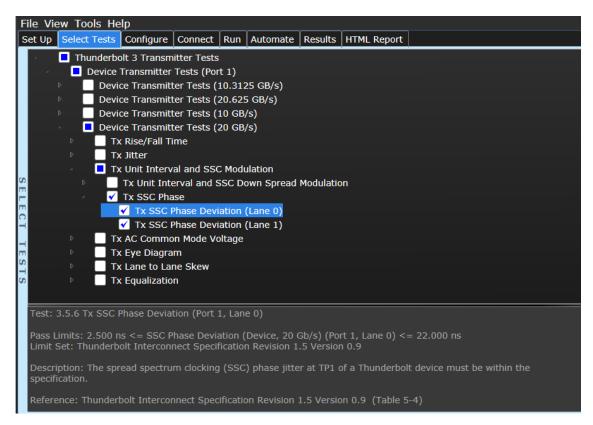

#### Tx SSC Phase Deviation 107

Test Overview 107

Test Pass Requirement 107

Test Setup 107

Test Procedure 108

Expected / Observable Results 108

Test References 109

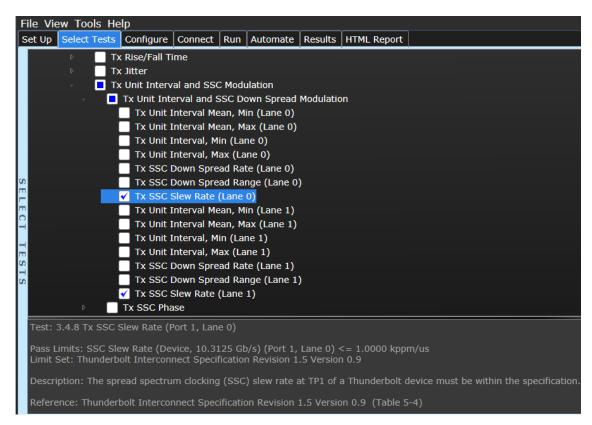

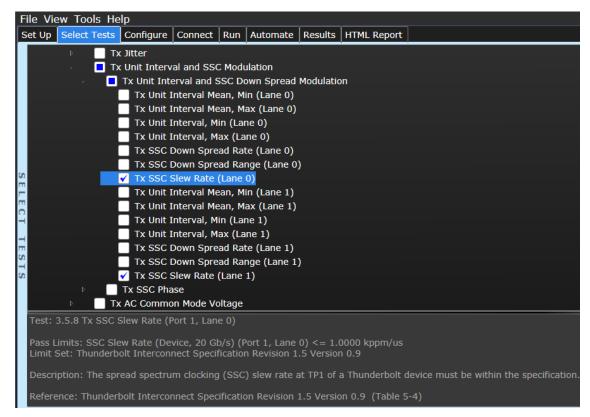

#### Tx SSC Slew Rate 110

Test Overview 110

Test Pass Requirement 110

Test Setup 110

Test Procedure 111

Expected / Observable Results 111

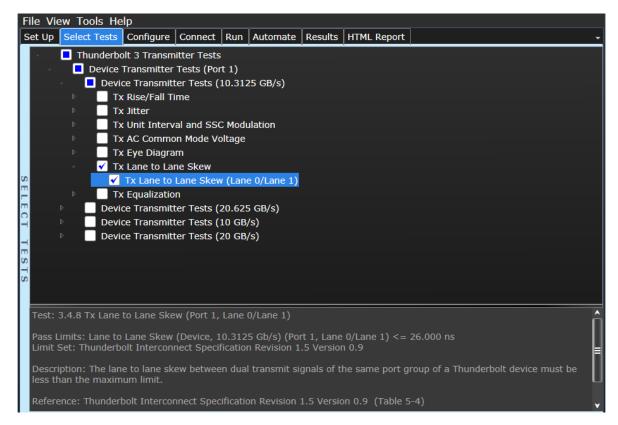

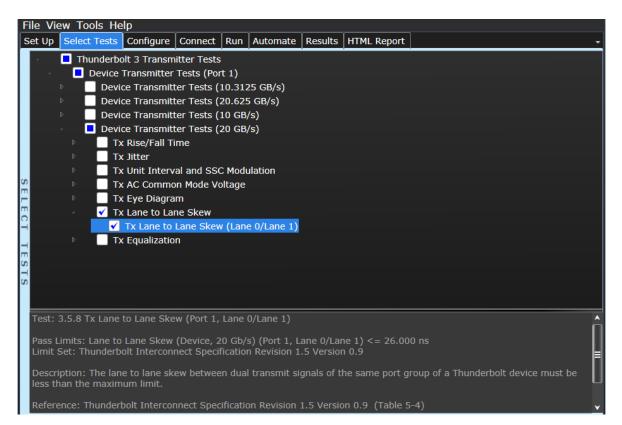

| Tx Lane to Lane Skew 112                                                                                                        |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Test Overview 112 Test Pass Requirement 112 Test Setup 112 Test Procedure 113 Expected / Observable Results Test References 113 | 113 |

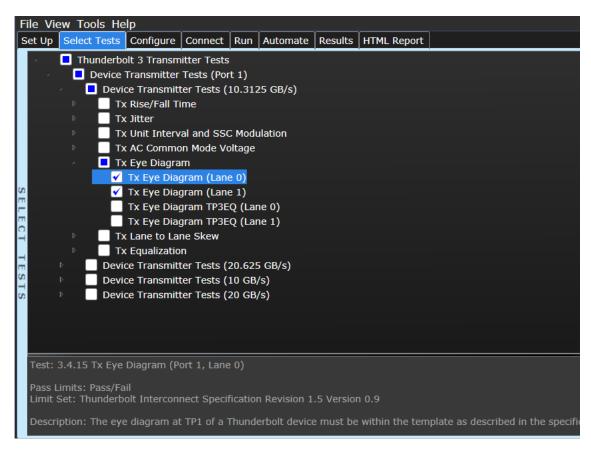

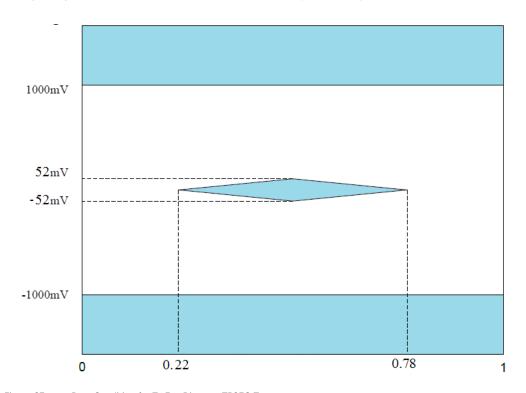

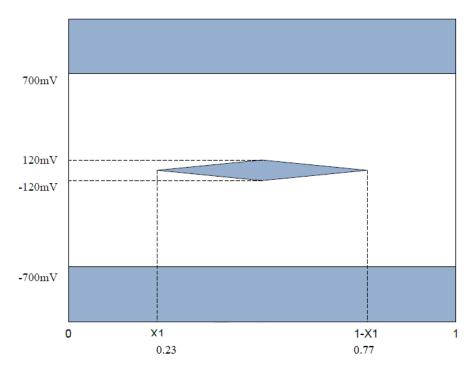

| Tx Eye Diagram 114                                                                                                              |     |

| Test Overview 114 Test Pass Requirement 114 Test Setup 114 Test Procedure 115                                                   | 115 |

| Expected / Observable Results Test References 116                                                                               | 115 |

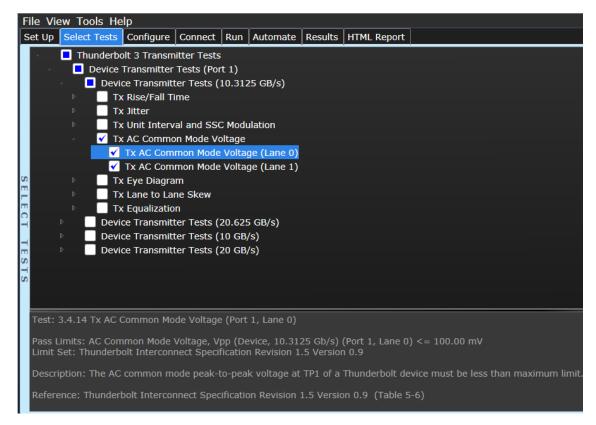

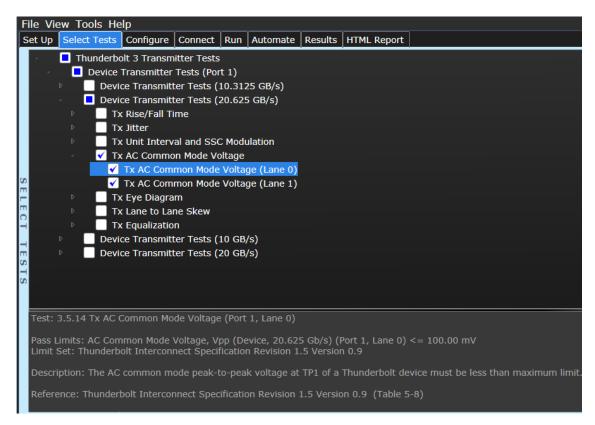

| Tx AC Common Mode Voltage                                                                                                       | 117 |

| Test Overview 117 Test Pass Requirement 117 Test Setup 117 Test Procedure 118 Expected / Observable Results Test References 118 | 118 |

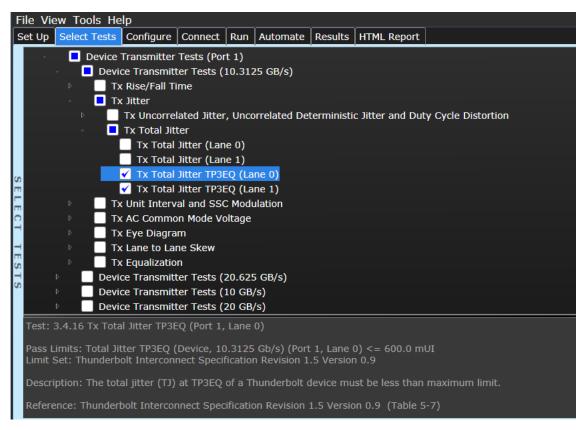

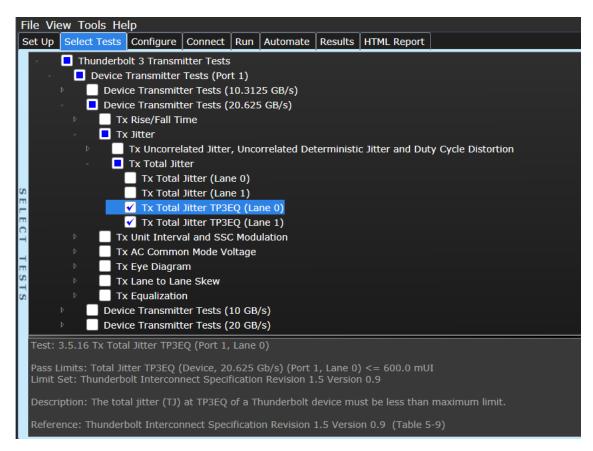

| Tx Total Jitter TP3EQ 119                                                                                                       |     |

| Test Overview 119 Test Pass Requirement 119 Test Setup 119 Test Procedure 120                                                   |     |

| Expected / Observable Results Test References 121                                                                               | 121 |

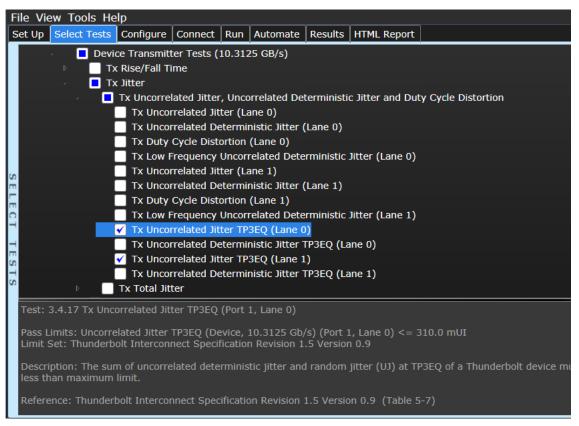

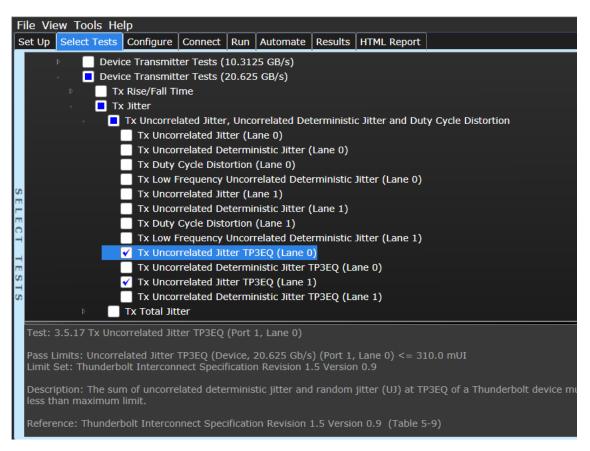

| Tx Uncorrelated Jitter TP3EQ                                                                                                    | 122 |

| Test Overview 122 Test Pass Requirement 122 Test Setup 122                                                                      |     |

| Test Procedure 123 Expected / Observable Results Test References 124                                                            | 124 |

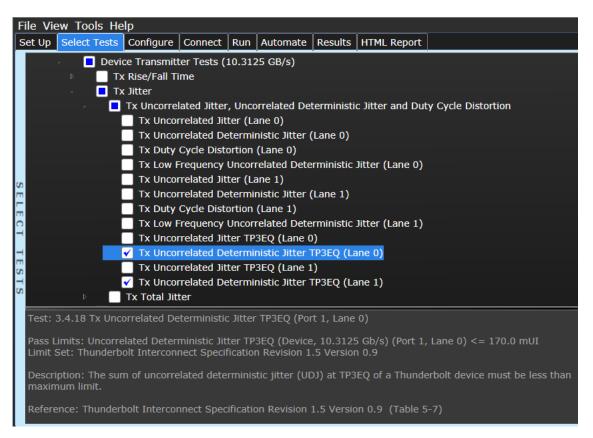

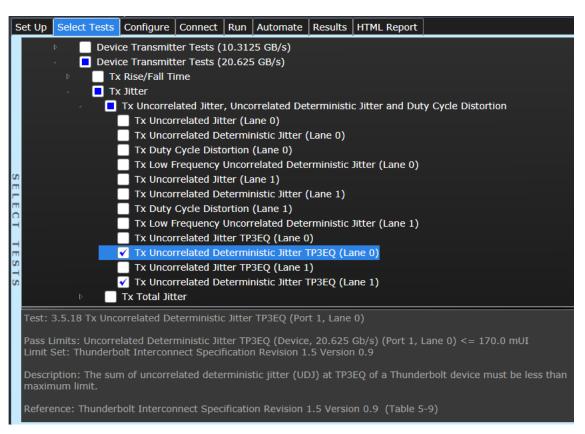

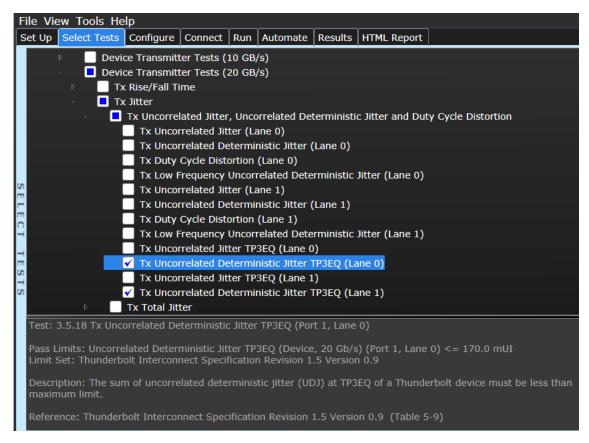

#### Tx Uncorrelated Deterministic Jitter TP3EQ 125

Test Overview 125

Test Pass Requirement 125

Test Setup 125

Test Procedure 126

Expected / Observable Results 127

Test References 127

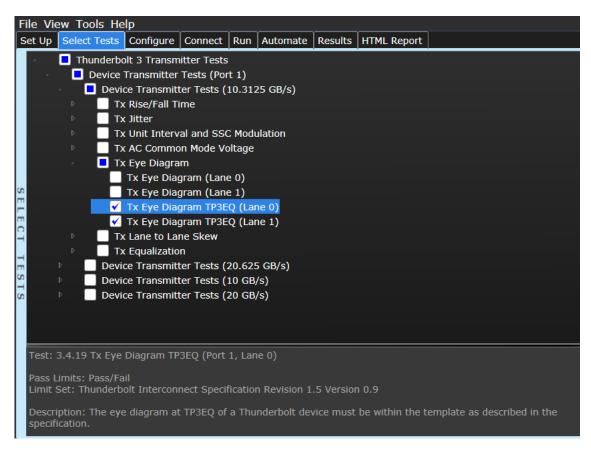

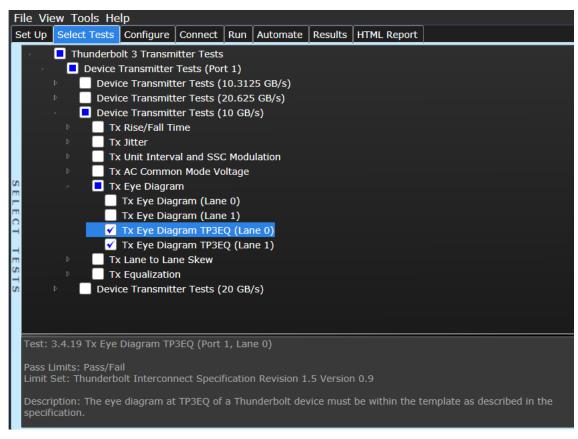

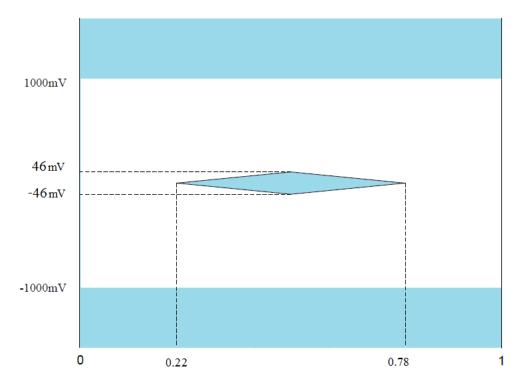

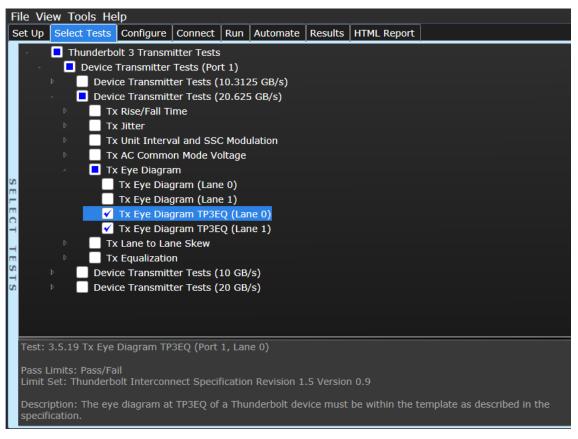

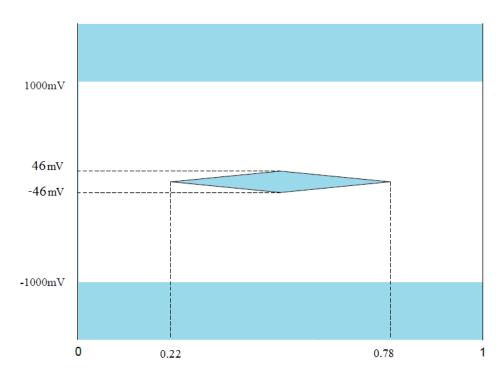

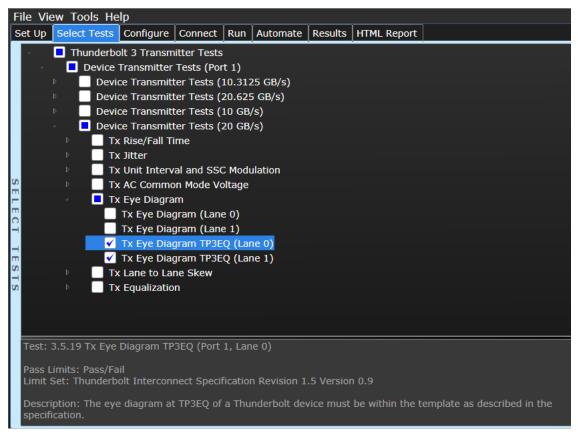

#### Tx Eye Diagram TP3EQ 128

Test Overview 128

Test Pass Requirement 128

Test Setup 128

Test Procedure 129

Expected / Observable Results 130

Test References 130

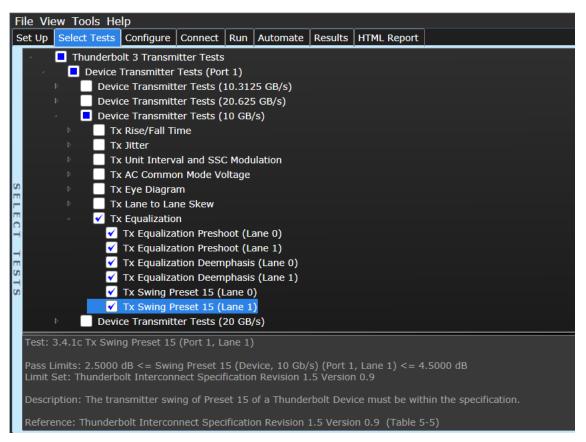

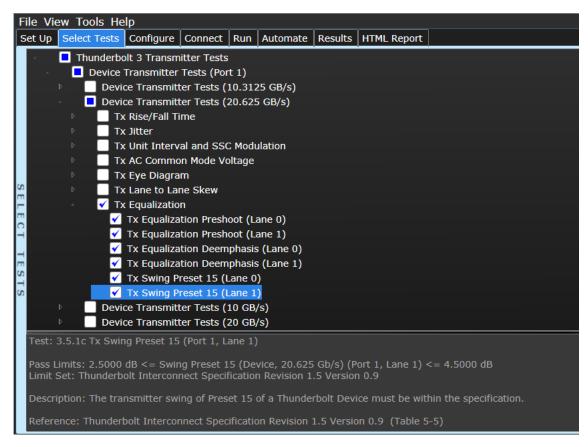

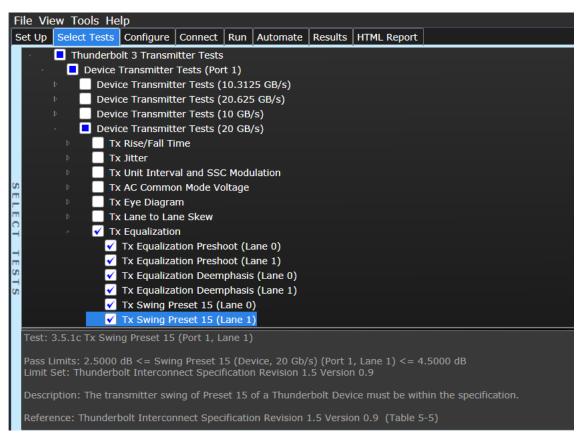

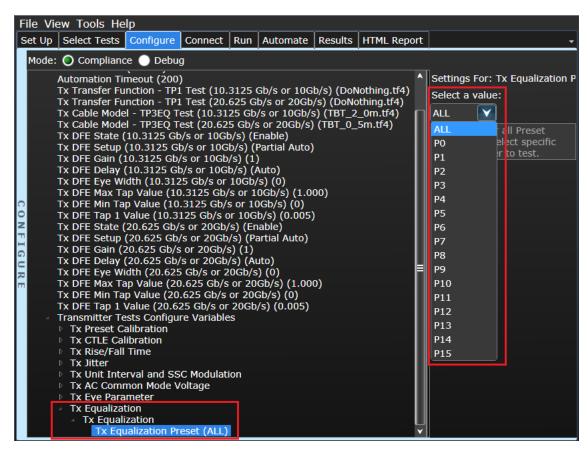

#### Tx Equalization Tests 131

Test Overview 131

Test Pass Requirement 131

Test Setup 132

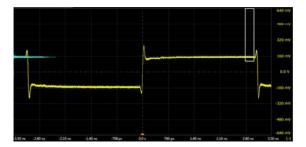

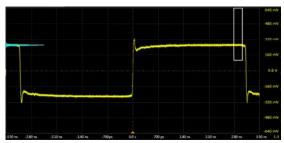

Test Procedure 133

Expected / Observable Results 135

Test References 135

#### 6 Transmitter Tests for 10 GB/s Systems

#### **Tx Preset Calibration** 138

Test Overview 138

Test Setup 138

Test Procedure 139

-----

Expected / Observable Results 139

Test References 139

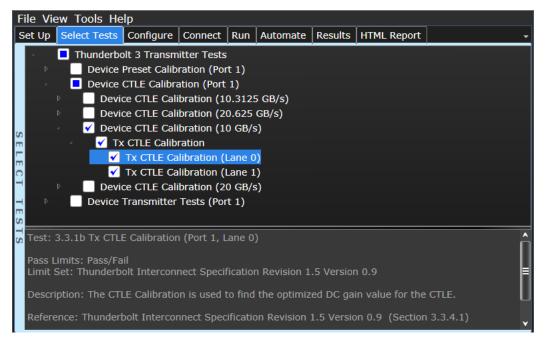

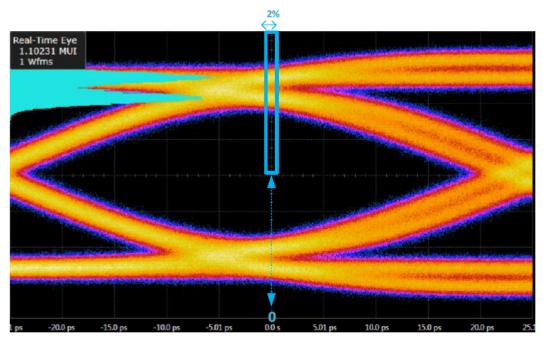

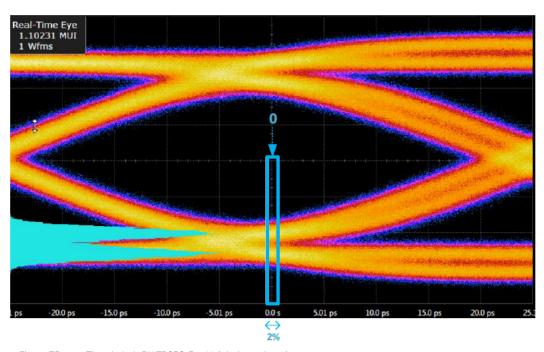

#### **Tx CTLE Calibration** 140

Test Overview 140

Test Setup 140

Test Procedure 141

Expected / Observable Results 143

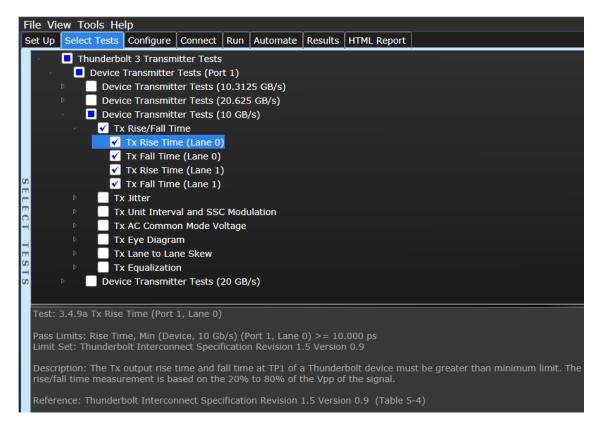

#### Test Overview 144 Test Pass Requirement 144 Test Setup 144 Test Procedure 145 Expected / Observable Results 145 Test References 145 Tx Total Jitter 146 Test Overview 146 Test Pass Requirement 146 Test Setup 146 Test Procedure 147 Expected / Observable Results 148 Test References 148 Tx Uncorrelated Jitter 149 Test Overview 149 Test Pass Requirement 149 Test Setup 149 Test Procedure 150 Expected / Observable Results 151 Test References 151 Tx Uncorrelated Deterministic Jitter 152 Test Overview 152 Test Pass Requirement 152 Test Setup 152 Test Procedure 153 Expected / Observable Results 154 Test References 154 Tx Low Frequency Uncorrelated Deterministic Jitter 155 Test Overview 155 Test Pass Requirement 155 Test Setup 155 Test Procedure 156 Expected / Observable Results 157 Test References 157

Tx Rise/Fall Time

144

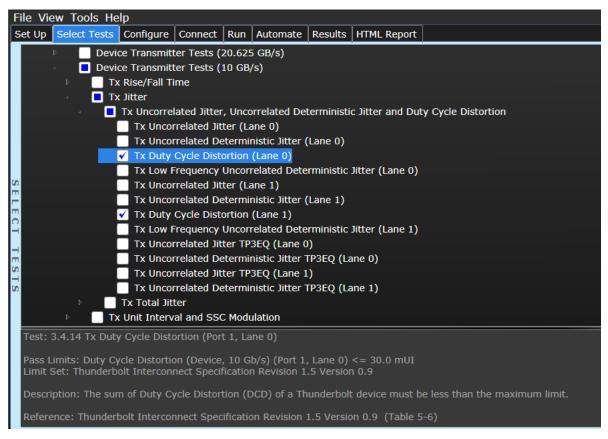

#### **Tx Duty Cycle Distortion** 158

Test Overview 158

Test Pass Requirement 158

Test Setup 158

Test Procedure 159

Expected / Observable Results 159

Test References 160

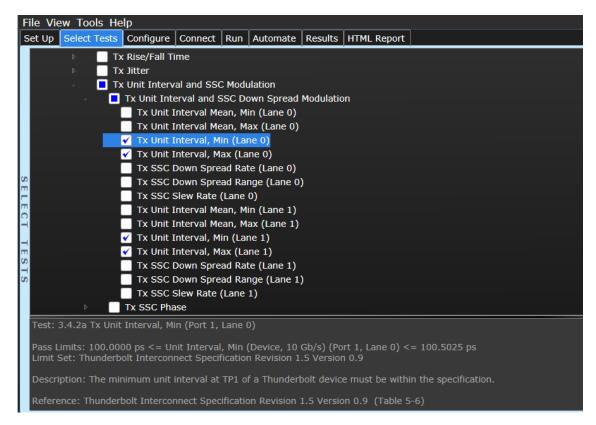

#### **Tx Unit Interval** 161

Test Overview 161

Test Pass Requirement 161

Test Setup 161

Test Procedure 162

Expected / Observable Results 162

Test References 162

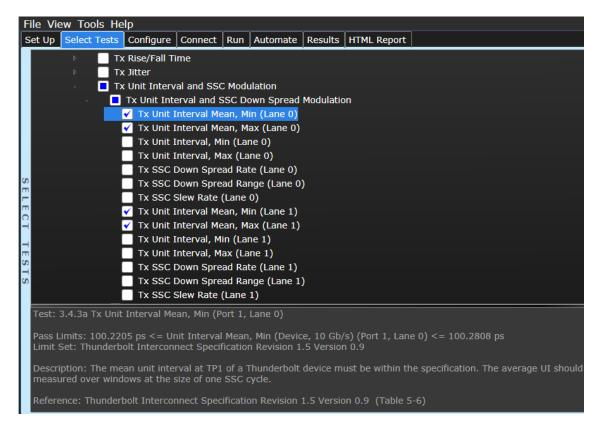

#### Tx Unit Interval Mean 163

Test Overview 163

Test Pass Requirement 163

Test Setup 163

Test Procedure 164

Expected / Observable Results 164

Test References 164

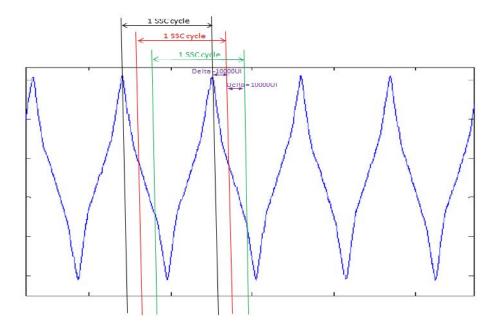

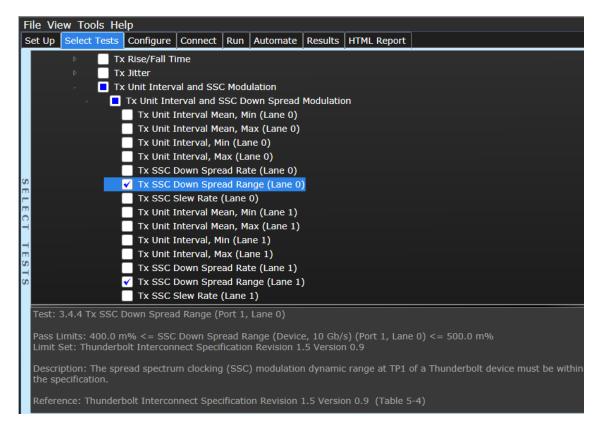

#### Tx SSC Down Spread Range 165

Test Overview 165

Test Pass Requirement 165

Test Setup 165

Test Procedure 166

Expected / Observable Results 166

Test References 166

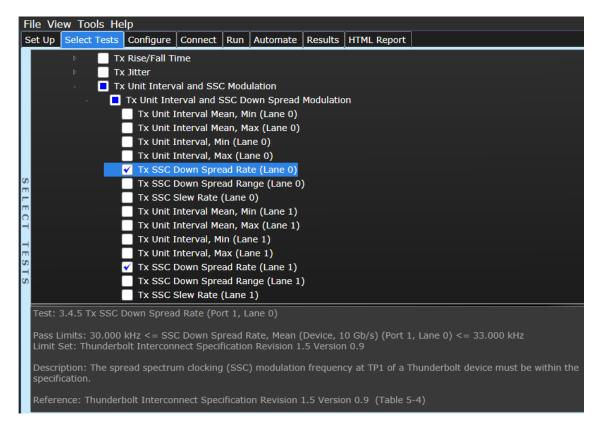

#### Tx SSC Down Spread Rate 167

Test Overview 167

Test Pass Requirement 167

Test Setup 167

Test Procedure 168

Expected / Observable Results 168

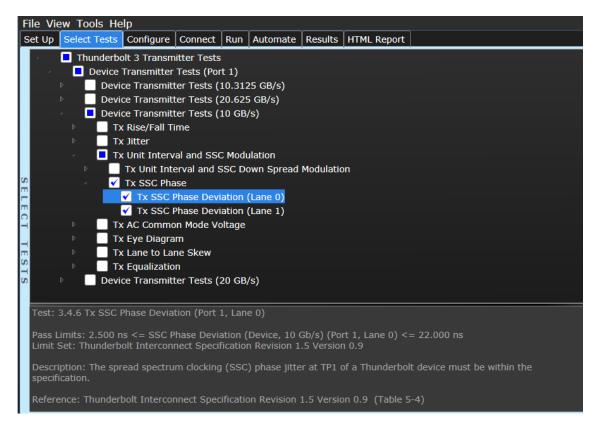

| <b>Tx SSC Phase Deviation</b> 169                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------|-----|

| Test Overview 169 Test Pass Requirement 169 Test Setup 169 Test Procedure 170 Expected / Observable Results Test References 170 | 170 |

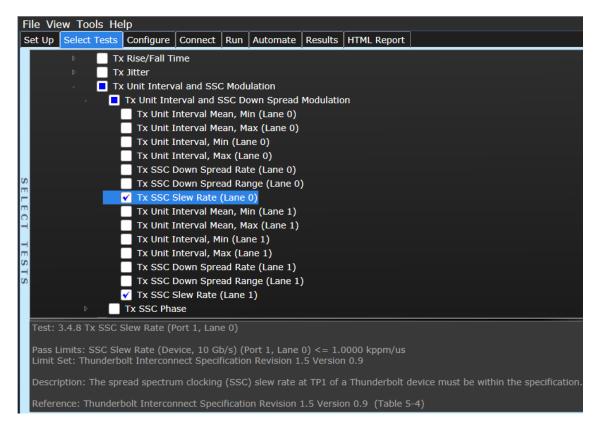

| Tx SSC Slew Rate 171                                                                                                            |     |

| Test Overview 171 Test Pass Requirement 171 Test Setup 171 Test Procedure 172 Expected / Observable Results Test References 172 | 172 |

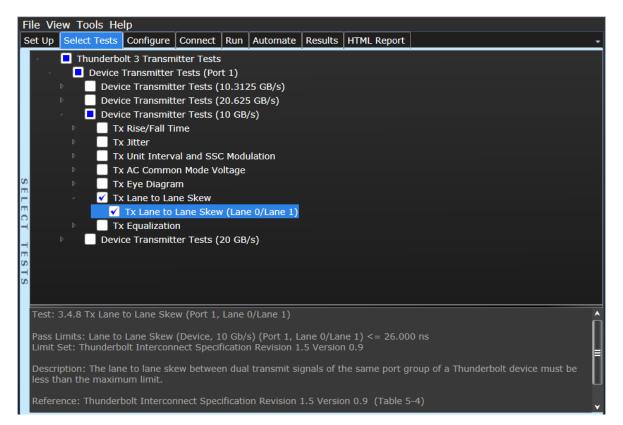

| Tx Lane to Lane Skew 173                                                                                                        |     |

| Test Overview 173 Test Pass Requirement 173 Test Setup 173 Test Procedure 174 Expected / Observable Results Test References 174 | 174 |

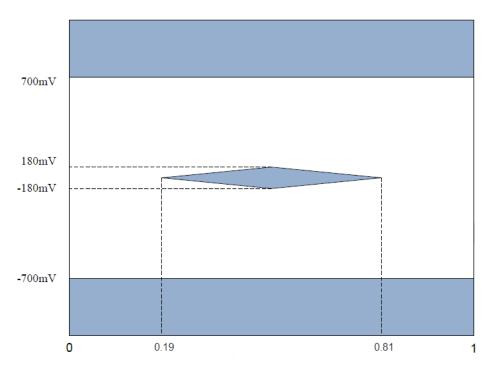

| Tx Eye Diagram 175                                                                                                              |     |

| Test Overview 175 Test Pass Requirement 175 Test Setup 175                                                                      |     |

| Test Procedure 176 Expected / Observable Results Test References 177                                                            | 176 |

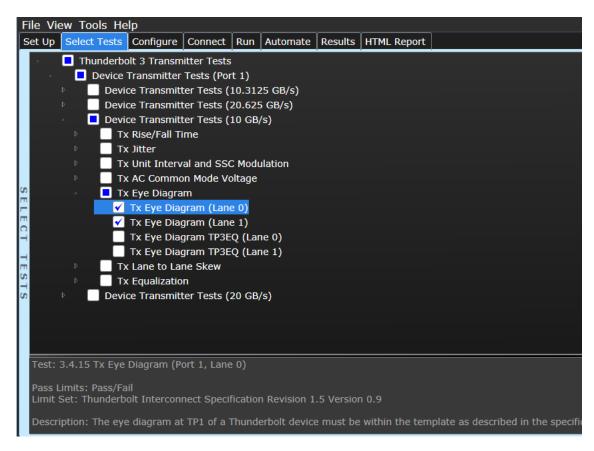

| Tx AC Common Mode Voltage                                                                                                       | 178 |

| Test Overview 178 Test Pass Requirement 178 Test Setup 178                                                                      |     |

| Test Procedure 179 Expected / Observable Results Test References 179                                                            | 179 |

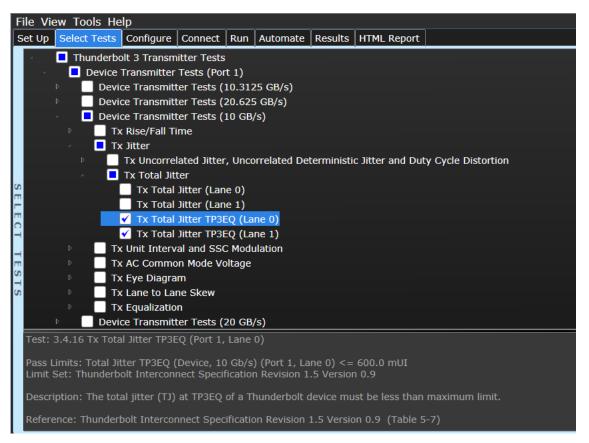

#### **Tx Total Jitter TP3EQ** 180

Test Overview 180

Test Pass Requirement 180

Test Setup 180

Test Procedure 181

Expected / Observable Results 182

Test References 182

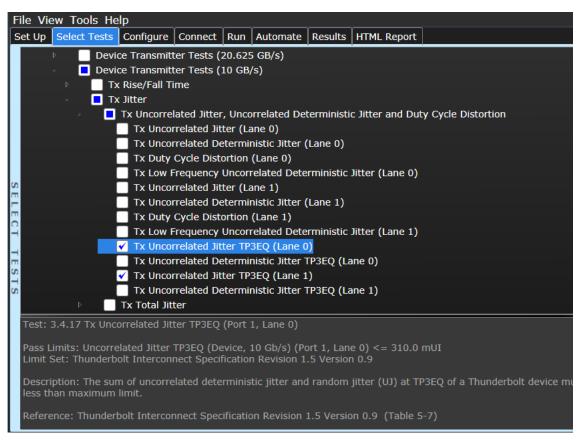

#### Tx Uncorrelated Jitter TP3EQ 183

Test Overview 183

Test Pass Requirement 183

Test Setup 183

Test Procedure 184

Expected / Observable Results 185

Test References 185

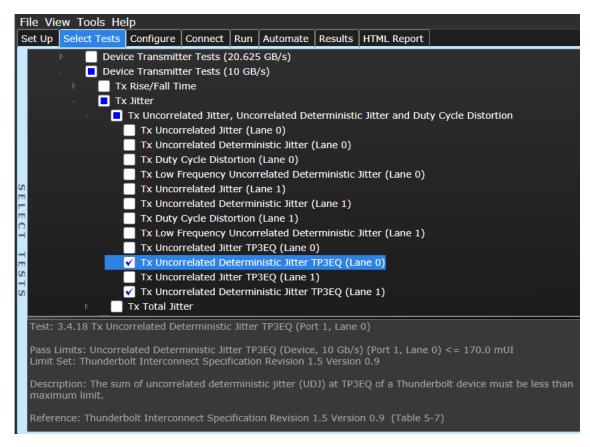

#### Tx Uncorrelated Deterministic Jitter TP3EQ 186

Test Overview 186

Test Pass Requirement 186

Test Setup 186

Test Procedure 187

Expected / Observable Results 188

Test References 188

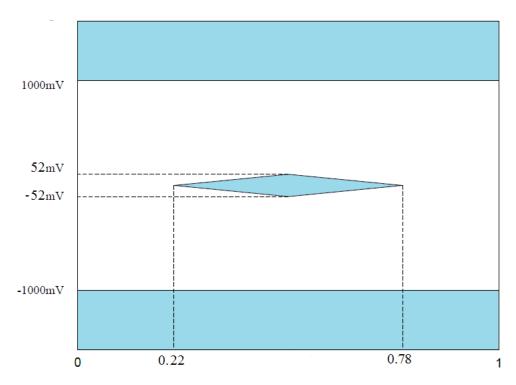

#### Tx Eye Diagram TP3EQ 189

Test Overview 189

Test Pass Requirement 189

Test Setup 189

Test Procedure 190

Expected / Observable Results 191

Test References 191

#### **Tx Equalization Tests** 192

Test Overview 192

Test Pass Requirement 192

Test Setup 193

Test Procedure 194

Expected / Observable Results 196

#### 7 Transmitter Tests for 20.625 GB/s Systems

#### **Tx Preset Calibration** 198

Test Overview 198

Test Setup 198

Test Procedure 199

Expected / Observable Results 199

Test References 199

#### Tx CTLE Calibration 200

Test Overview 200

Test Setup 200

Test Procedure 201

Expected / Observable Results 203

Test References 203

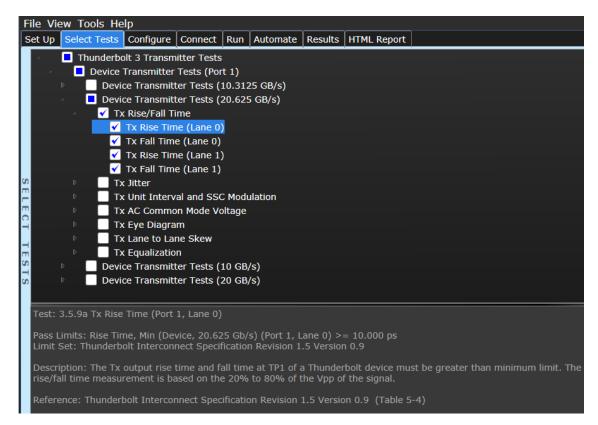

#### Tx Rise/Fall Time 204

Test Overview 204

Test Pass Requirement 204

Test Setup 204

Test Procedure 205

Expected / Observable Results 205

Test References 205

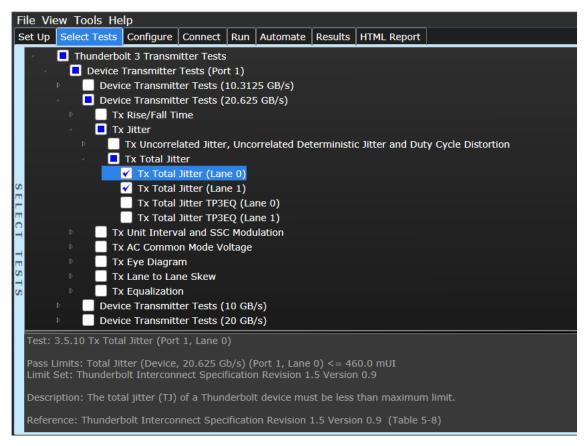

#### Tx Total Jitter 206

Test Overview 206

Test Pass Requirement 206

Test Setup 206

Test Procedure 207

Expected / Observable Results 208

Test References 208

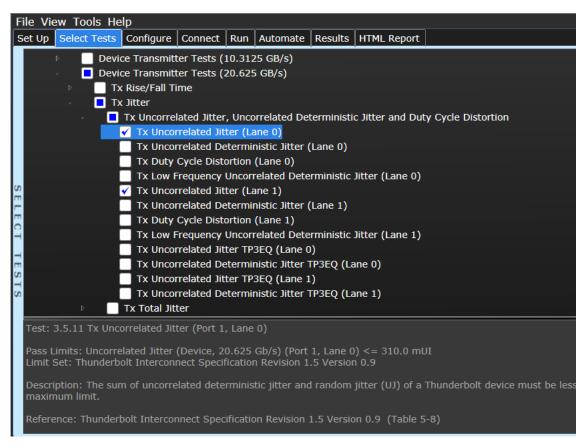

#### Tx Uncorrelated Jitter 209

Test Overview 209

Test Pass Requirement 209

Test Setup 209

Test Procedure 210

Expected / Observable Results 211

Test References 211

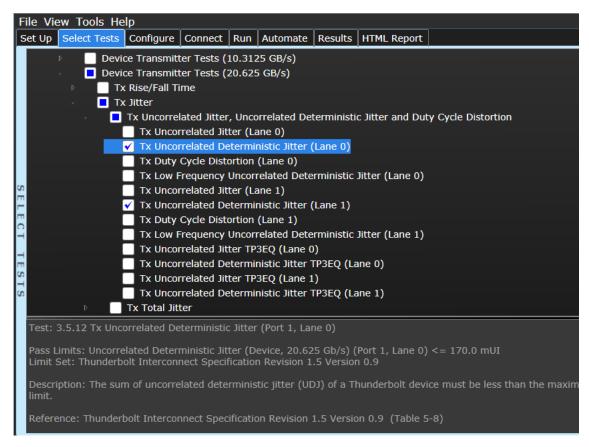

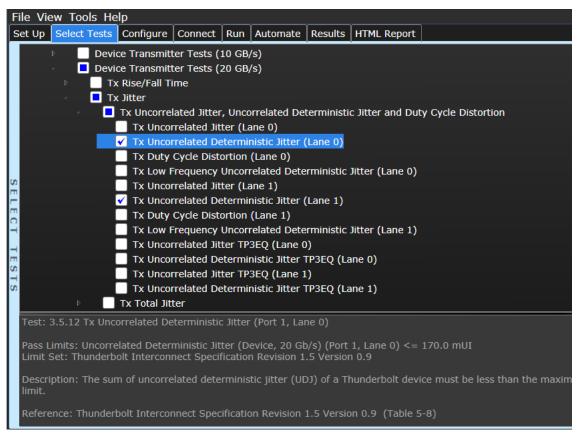

#### Tx Uncorrelated Deterministic Jitter 212

Test Overview 212

Test Pass Requirement 212

Test Setup 212

Test Procedure 213

Expected / Observable Results 214

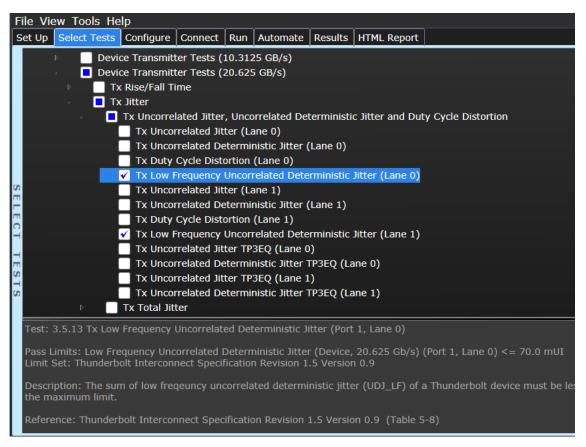

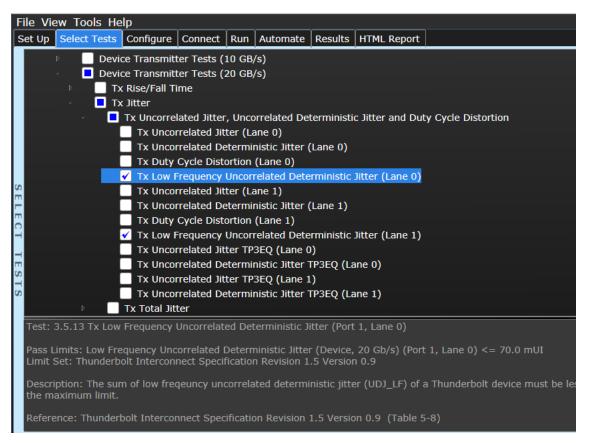

#### Tx Low Frequency Uncorrelated Deterministic Jitter 215

Test Overview 215

Test Pass Requirement 215

Test Setup 215

Test Procedure 216

Expected / Observable Results 217

Test References 217

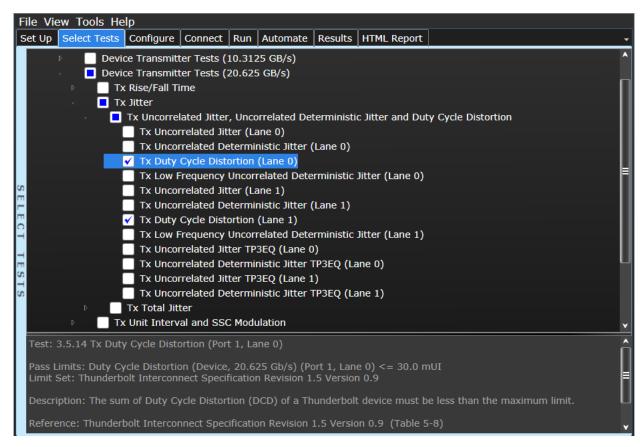

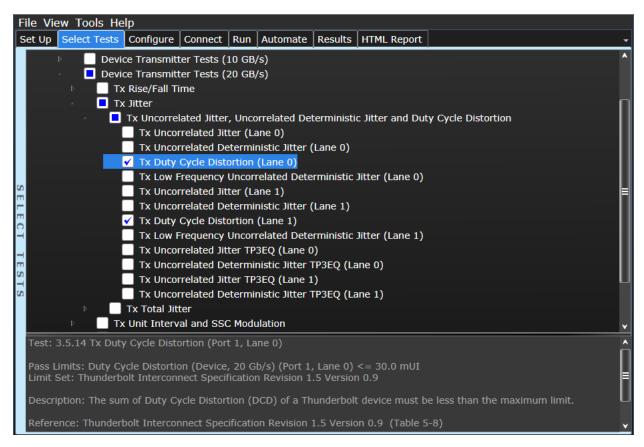

#### Tx Duty Cycle Distortion 218

Test Overview 218

Test Pass Requirement 218

Test Setup 218

Test Procedure 219

Expected / Observable Results 219

Test References 220

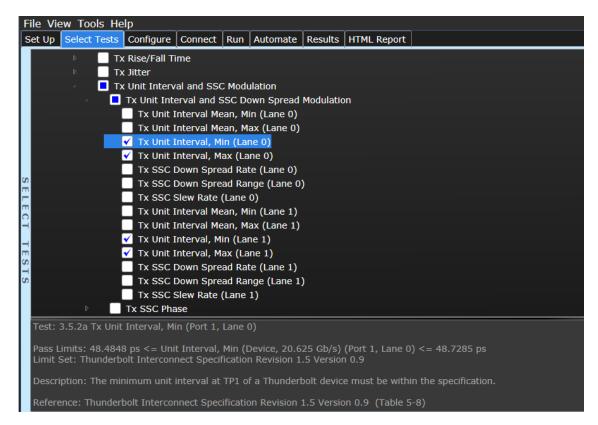

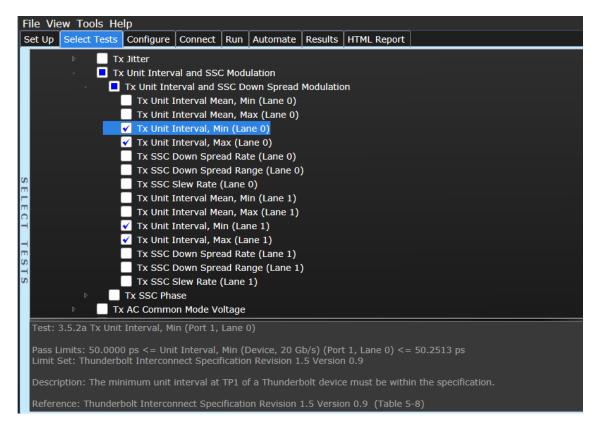

#### Tx Unit Interval 221

Test Overview 221

Test Pass Requirement 221

Test Setup 221

Test Procedure 222

Expected / Observable Results 222

Test References 222

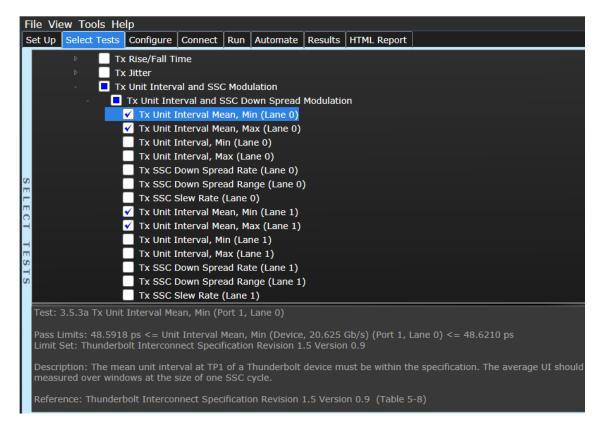

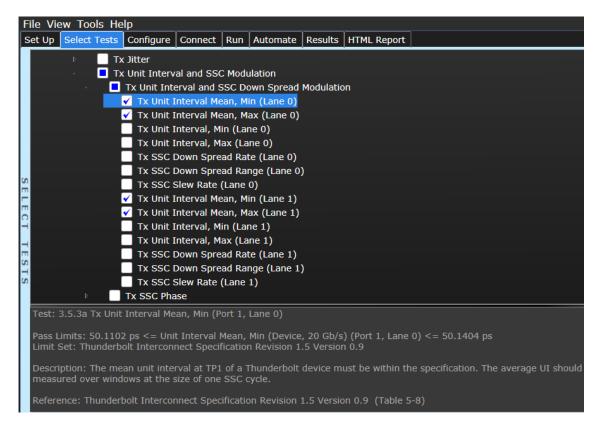

#### Tx Unit Interval Mean 223

Test Overview 223

Test Pass Requirement 223

Test Setup 223

Test Procedure 224

Expected / Observable Results 224

Test References 224

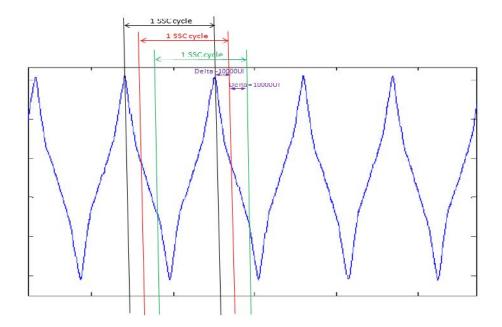

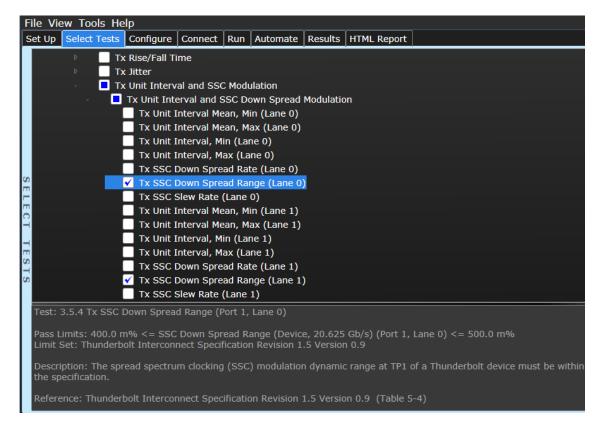

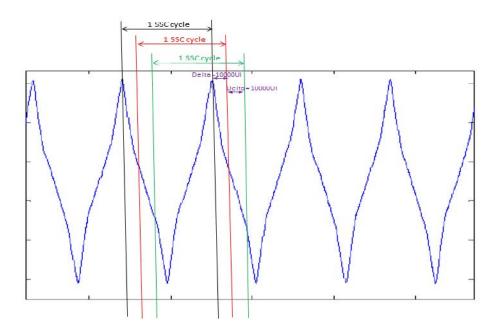

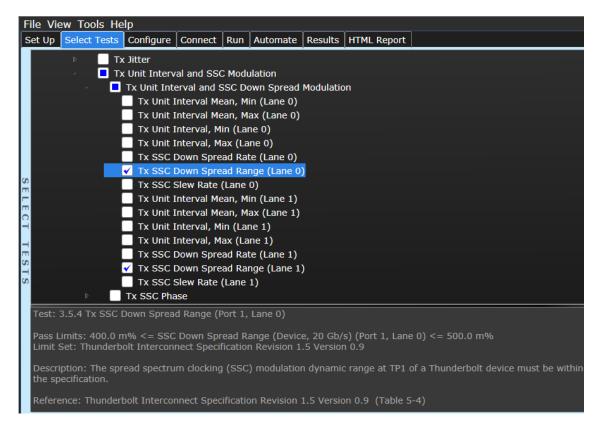

#### Tx SSC Down Spread Range 225

Test Overview 225

Test Pass Requirement 225

Test Setup 225

Test Procedure 226

Expected / Observable Results 226

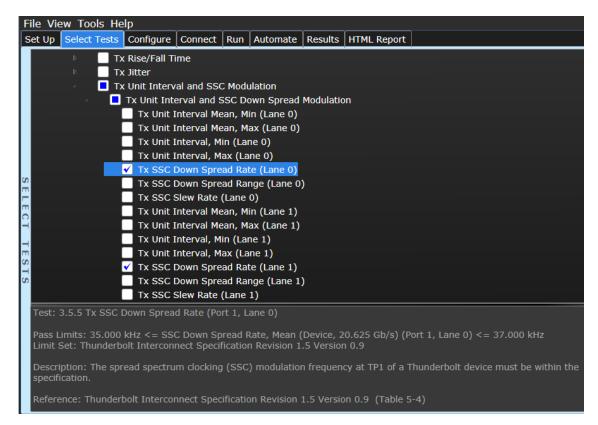

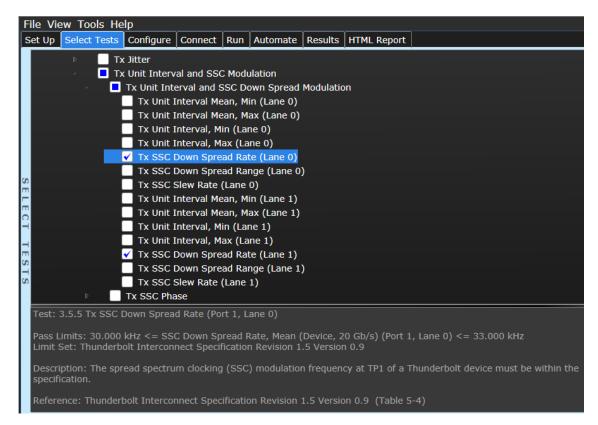

#### Tx SSC Down Spread Rate 227

Test Overview 227

Test Pass Requirement 227

Test Setup 227

Test Procedure 228

Expected / Observable Results 228

Test References 228

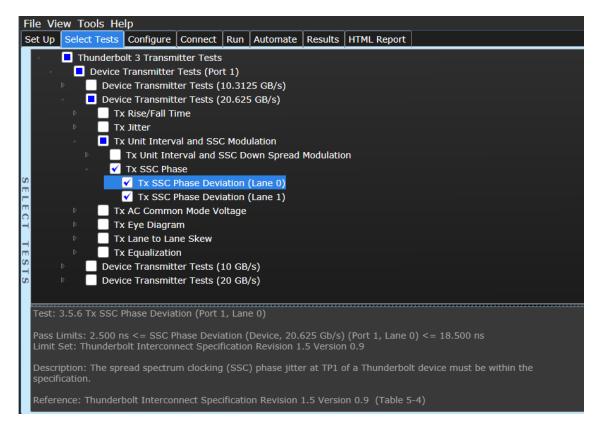

#### Tx SSC Phase Deviation 229

Test Overview 229

Test Pass Requirement 229

Test Setup 229

Test Procedure 230

Expected / Observable Results 230

Test References 230

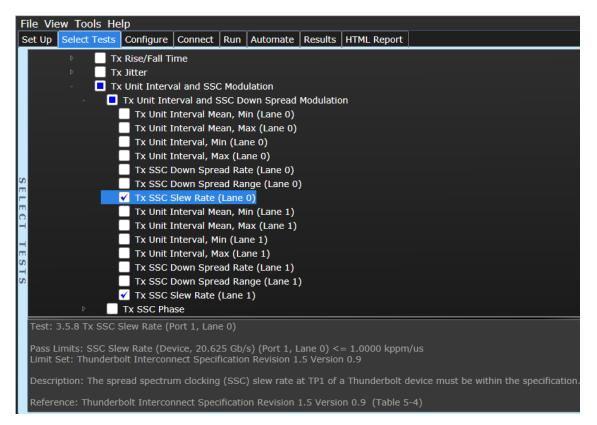

#### Tx SSC Slew Rate 231

Test Overview 231

Test Pass Requirement 231

Test Setup 231

Test Procedure 232

Expected / Observable Results 232

Test References 232

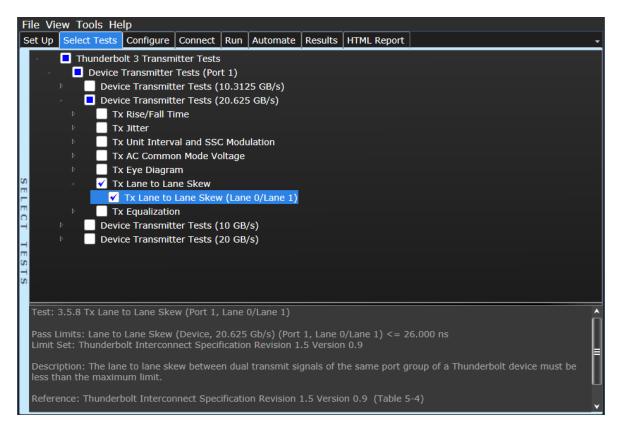

#### Tx Lane to Lane Skew 233

Test Overview 233

Test Pass Requirement 233

Test Setup 233

Test Procedure 234

Expected / Observable Results 234

Test References 234

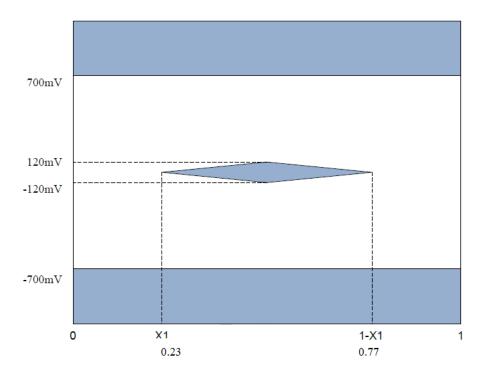

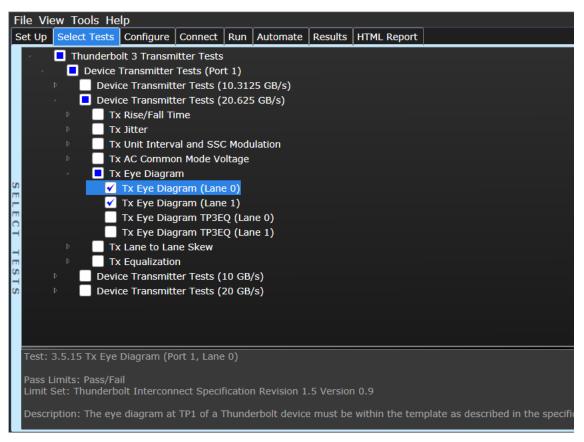

#### Tx Eye Diagram 235

Test Overview 235

Test Pass Requirement 235

Test Setup 235

Test Procedure 236

Expected / Observable Results 236

| Test Overview 238 Test Pass Requirement 238 Test Setup 238 Test Procedure 239 Expected / Observable Results Test References 239 |              |     |

|---------------------------------------------------------------------------------------------------------------------------------|--------------|-----|

| Tx Total Jitter TP3EQ 240                                                                                                       |              |     |

| Test Overview 240 Test Pass Requirement 240 Test Setup 240 Test Procedure 241 Expected / Observable Results Test References 242 | 242          |     |

| Tx Uncorrelated Jitter TP3EQ                                                                                                    | 243          |     |

| Test Overview 243 Test Pass Requirement 243 Test Setup 243 Test Procedure 244 Expected / Observable Results Test References 245 |              |     |

| Tx Uncorrelated Deterministic J                                                                                                 | litter TP3EQ | 246 |

| Test Overview 246 Test Pass Requirement 246 Test Setup 246 Test Procedure 247 Expected / Observable Results Test References 248 | ·            | . 9 |

| Tx Eye Diagram TP3EQ 249                                                                                                        |              |     |

| Test Overview 249 Test Pass Requirement 249 Test Setup 249 Test Procedure 250 Expected / Observable Results                     | 251          |     |

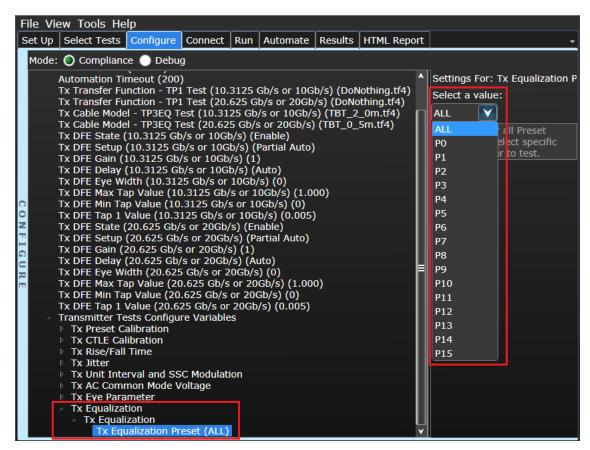

#### **Tx Equalization Tests** 252

Test Overview 252

Test Pass Requirement 252

Test Setup 253

Test Procedure 254

Expected / Observable Results 256

Test References 256

#### 8 Transmitter Tests for 20 GB/s Systems

#### **Tx Preset Calibration** 258

Test Overview 258

Test Setup 258

Test Procedure 259

Expected / Observable Results 259

Test References 259

#### **Tx CTLE Calibration** 260

Test Overview 260

Test Setup 260

Test Procedure 261

Expected / Observable Results 263

Test References 263

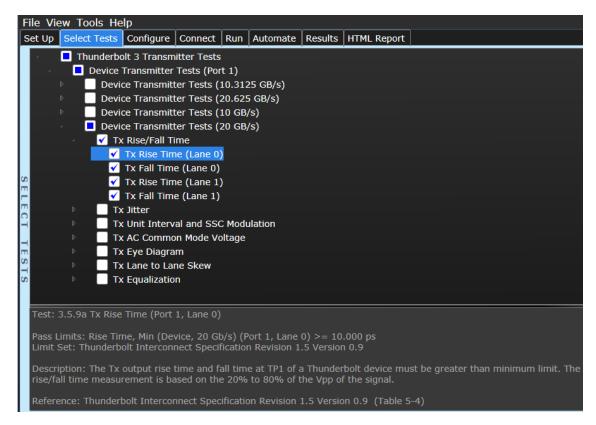

#### Tx Rise/Fall Time 264

Test Overview 264

Test Pass Requirement 264

Test Setup 264

Test Procedure 265

Expected / Observable Results 265

Test References 265

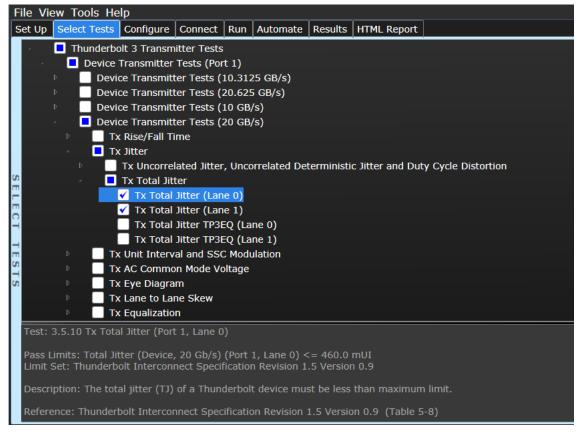

#### Tx Total Jitter 266

Test Overview 266

Test Pass Requirement 266

Test Setup 266

Test Procedure 267

Expected / Observable Results 268

Test References 268

Keysight D9030TBTC Thunderbolt 3 Test Application Methods of Implementation

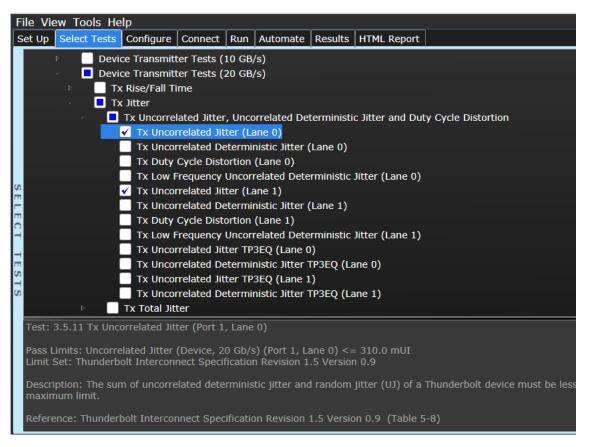

#### Tx Uncorrelated Jitter 269 Test Overview 269 269 Test Pass Requirement Test Setup 269 Test Procedure 270 Expected / Observable Results 271 271 Test References Tx Uncorrelated Deterministic Jitter 272 272 Test Overview Test Pass Requirement 272 Test Setup 272 273 Test Procedure Expected / Observable Results 274 Test References 274 275 Tx Low Frequency Uncorrelated Deterministic Jitter 275 Test Overview Test Pass Requirement 275 Test Setup 275 Test Procedure 276 Expected / Observable Results 277 277 Test References Tx Duty Cycle Distortion 278 Test Overview 278 Test Pass Requirement 278 Test Setup 278 Test Procedure 279 Expected / Observable Results 279 Test References 280 Tx Unit Interval 281 Test Overview 281 Test Pass Requirement 281 Test Setup 281 Test Procedure 282

Expected / Observable Results

Test References

282

282

#### Tx Unit Interval Mean 283

Test Overview 283

Test Pass Requirement 283

Test Setup 283

Test Procedure 284

Expected / Observable Results 284

Test References 284

#### Tx SSC Down Spread Range 285

Test Overview 285

Test Pass Requirement 285

Test Setup 285

Test Procedure 286

Expected / Observable Results 286

Test References 286

#### Tx SSC Down Spread Rate 287

Test Overview 287

Test Pass Requirement 287

Test Setup 287

Test Procedure 288

Expected / Observable Results 288

Test References 288

#### Tx SSC Phase Deviation 289

Test Overview 289

Test Pass Requirement 289

Test Setup 289

Test Procedure 290

Expected / Observable Results 290

Test References 290

#### Tx SSC Slew Rate 291

Test Overview 291

Test Pass Requirement 291

Test Setup 291

Test Procedure 292

Expected / Observable Results 292

#### Tx Lane to Lane Skew 293 Test Overview 293 293 Test Pass Requirement Test Setup 293 Test Procedure 294 294 Expected / Observable Results 294 Test References Tx Eye Diagram 295 295 Test Overview 295 Test Pass Requirement Test Setup 295 Test Procedure 296 Expected / Observable Results 296 Test References 297 Tx AC Common Mode Voltage 298 298 Test Overview Test Pass Requirement 298 Test Setup 298 Test Procedure 299 Expected / Observable Results 299 299 Test References Tx Total Jitter TP3EQ Test Overview Test Pass Requirement 300 Test Setup 300 Test Procedure 301 Expected / Observable Results 302 Test References 302 Tx Uncorrelated Jitter TP3EQ 303 Test Overview 303 Test Pass Requirement 303 Test Setup 303 Test Procedure 304 Expected / Observable Results 305

Test References

305

#### Tx Uncorrelated Deterministic Jitter TP3EQ 306

Test Overview 306

Test Pass Requirement 306

Test Setup 306

Test Procedure 307

Expected / Observable Results 308

Test References 308

#### Tx Eye Diagram TP3EQ 309

Test Overview 309

Test Pass Requirement 309

Test Setup 309

Test Procedure 310

Expected / Observable Results 311

Test References 311

#### **Tx Equalization Tests** 312

Test Overview 312

Test Pass Requirement 312

Test Setup 313

Test Procedure 314

Expected / Observable Results 316

Test References 316

Index

Contents

# Keysight D9030TBTC Thunderbolt 3 Test Application Methods of Implementation

## 1 Overview

Thunderbolt 3 Automated Testing—At a Glance 24

Required Equipment and Software 25

In This Book 27

#### Thunderbolt 3 Automated Testing-At a Glance

The Keysight D9030TBTC Thunderbolt 3 Test Application allows the testing of all 3rd Generation Thunderbolt devices with the Keysight Infiniium Oscilloscope. These tests are based on the *USB Type-C Thunderbolt Alternate Mode Electrical Host \ Device Compliance Test Specification Revision 1.5, Version 0.9.*

The USB Type-C connector in conjunction with a Thunderbolt Controller is capable of providing two dual-simplex lanes (or channels). Each lane provides bi-directional 10.3125, 20.625 GB/s, 10 GB/s or 20 GB/s of bandwidth. The USB Type-C connector is capable of connecting Thunderbolt products when using either a USB Type-C Full Featured cable, a Thunderbolt Passive cable, a Thunderbolt Active Electrical or Optical Cable, or Thunderbolt legacy Cable or Dongle.

The current version of the Thunderbolt 3 Test Application also extends support for bit rates of 10 Gb/s and 20Gb/s based on the *Thunderbolt Interconnect Specification Revision 1.5 Version 0.9* specification document.

The Thunderbolt 3 Test Application:

- · Lets you select individual or multiple tests to run.

- · Lets you identify the device being tested and its configuration.

- Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run, and lets you specify the thresholds at which marginal or critical warnings appear.

- · Creates a printable HTML report of the tests that have been run.

The tests performed by the Thunderbolt 3 Test Application are intended to provide a quick check of the electrical health of the DUT. This testing is not a replacement for an exhaustive test validation plan.

#### Required Equipment and Software

In order to run the Thunderbolt 3 automated tests, you need the following equipment and software:

#### Hardware

- Use one of the Oscilloscope models given in Table 1.

- Keyboard, qty = 1, (provided with the Keysight Infiniium oscilloscope)

- Mouse, qty = 1, (provided with the Keysight Infiniium oscilloscope)

- · Keysight also recommends using a second monitor to view the test application.

Table 1 lists the recommended test equipments for running the Thunderbolt 3 tests. Note that all test equipments require calibration to ensure accurate and repeatable results. The test equipments must be calibrated prior to, and if necessary, during the test procedure.

Table 1 Test Equipments and Accessories for Thunderbolt 3 Tests

| Required Equipment                      | Test Equipment Capabilities/Description                                                                                                                                                                                                                                                                                        | Recommended Test Equipment                                                                                                                                                     |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test Point Access Boards                | TPA Boards provide test point for the pins on the<br>Thunderbolt connector and an easy way to control the<br>DUT                                                                                                                                                                                                               | <ul> <li>Thunderbolt Plug Test Fixture or<br/>equivalent</li> <li>Wilder TBT-TPA-UHG2 Thunderbolt<br/>Micro-Controller Test Module with USB<br/>Cable or equivalent</li> </ul> |

| Real Time Scopes (choose                | <ul> <li>DC to 21±1GHz -3dB bandwidth or greater</li> <li>80G sample/sec Sampling rate or greater,<br/>sampling 2 channels simultaneously</li> <li>Sample memory: 2 channels at 50M samples per<br/>channel or greater</li> <li>1st and 2nd order CDR capability</li> <li>Equalization for USB 3.1 model capability</li> </ul> | Keysight Z-Series Oscilloscope (25GHz and above)                                                                                                                               |

| from one of the available options)      | <ul> <li>DC to 21±1GHz -3dB bandwidth or greater</li> <li>128G sample/sec Sampling rate or greater, sampling 2 channels simultaneously</li> <li>Sample memory: 2 channels at 50M samples per channel or greater</li> <li>1st and 2nd order CDR capability</li> <li>Equalization for USB 3.1 model capability</li> </ul>        | Keysight UXR Series Oscilloscope<br>(25GHz and above)                                                                                                                          |

| Accessories                             |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                |

| Low insertion loss phase matched cables | <ul> <li>Phase matched ±2° @ 40GHz</li> <li>Max IL in 10GHz &lt; 1.2dB</li> </ul>                                                                                                                                                                                                                                              | <ul> <li>Rosenberger UK Micro Coax<br/>FC142A0-014-MTIE 2.92m (x2) L-1m<br/>(40GHz)</li> <li>Rosenberger Adaptor: RPC-2.92 female<br/>– SMP female - 02K119-K00E3</li> </ul>   |

#### Software

- The minimum version of Infiniium Oscilloscope Software (see the Keysight D9030TBTC Thunderbolt 3 Test Application Release Notes)

- Keysight D9030TBTC Thunderbolt 3 Test Application software

#### Licensing information

Refer to the *Data Sheet* pertaining to Thunderbolt 3 Test Application to know about the licenses you must install along with other optional licenses. Visit "http://www.keysight.com/find/D9030TBTC" and in the web page's **Document Library** tab, you may view the associated Data Sheet.

#### Overview

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

The licensing format for Keysight License Manager 6 differs from its predecessors. See "Installing the License Key" on page 31 to see the difference in installing a license key using either of the applications on your machine.

#### In This Book

This manual describes the tests that are performed by the Thunderbolt 3 Test Application in more detail.

- Chapter 2, "Installing the Test Application and Licenses" describes how to install the software and licenses for the Thunderbolt 3 Test Application software (if it was purchased separately).

- Chapter 3, "Preparing to Take Measurements" describes how to start the Thunderbolt 3 Test Application and gives a brief overview of its features.

- Chapter 4, "Host / Device Thunderbolt 3 Transmitter Testing" contains an overview on the Thunderbolt system components and requirements for Transmitter testing.

- Chapter 5, "Transmitter Tests for 10.3125 GB/s Systems" describes procedures to run electrical tests on a Thunderbolt DUT operating at a bit rate of 10.3125 GB/s.

- Chapter 6, "Transmitter Tests for 10 GB/s Systems" describes procedures to run electrical tests on a Thunderbolt DUT operating at a rounded-off bit rate of 10 GB/s.

- Chapter 7, "Transmitter Tests for 20.625 GB/s Systems" describes procedures to run electrical tests on a Thunderbolt DUT operating at a bit rate of 20.625 GB/s.

- Chapter 8, "Transmitter Tests for 20 GB/s Systems" describes procedures to run electrical tests on a Thunderbolt DUT operating at a rounded-off bit rate of 20 GB/s.

#### See Also

The Keysight D9030TBTC Thunderbolt 3 Test Application Methods of Implementation's Online Help, which describes:

- · Starting the Thunderbolt 3 Test Application

- Creating or Opening a Test Project

- · Setting Up the Test Environment

- Selecting Tests

- Configuring Tests

- Verifying Physical Connections

- · Running Tests

- Configuring Automation in the Test Application

- Viewing Results

- Viewing HTML Test Report

- · Exiting the Test Application

- · Additional Settings in the Test App

#### References

• The Thunderbolt standard specifications are available in USB Type-C Thunderbolt Alternate Mode Electrical Host \ Device Compliance Test Specification Revision 1.5, Version 0.9 and Thunderbolt Interconnect Specification Revision 1.5 Version 0.9.

1 Overview

Keysight D9030TBTC Thunderbolt 3 Test Application Methods of Implementation

# 2 Installing the Test Application and Licenses

Installing the Test Application 30

Installing the License Key 31

If you purchased the Keysight D9030TBTC Thunderbolt 3 Test Application separate from your Infiniium oscilloscope, you must install the software and license key.

#### 2

#### Installing the Test Application

- 1 Make sure you have the minimum version of Infiniium Oscilloscope software (see the D9030TBTC Thunderbolt 3 Test Application release notes). To ensure that you have the minimum version, select **Help > About Infiniium...** from the main menu.

- 2 To obtain the Thunderbolt 3 Test Application, go to Keysight website: "http://www.keysight.com/find/D9030TBTC".

- 3 In the web page's **Trials & Licenses** tab, click the **Details and Download** button to view instructions for downloading and installing the application software.

#### Installing the License Key

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

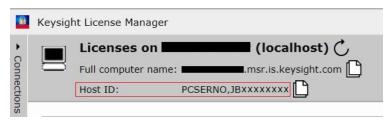

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

Figure 1 Viewing the Host ID information in Keysight License Manager 5

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

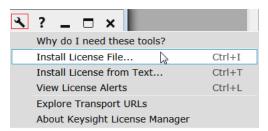

- 3 From the configuration menu, use one of the options to install each license file.

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to Keysight License Manager 5 Supporting Documentation.

#### Using Keysight License Manager 6

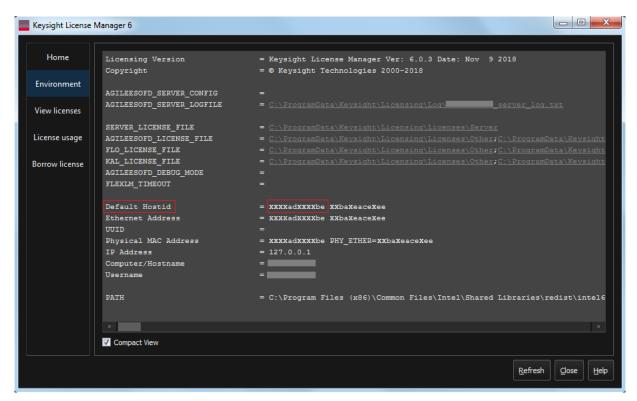

To view and copy the Host ID from Keysight License Manager 6:

- Launch Keysight License Manager 6 on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID, which is the first set of alphanumeric value (as highlighted in Figure 3) that appears in the Environment tab of the application. Note that x indicates numeric values.

Figure 3 Viewing the Host ID information in Keysight License Manager 6

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

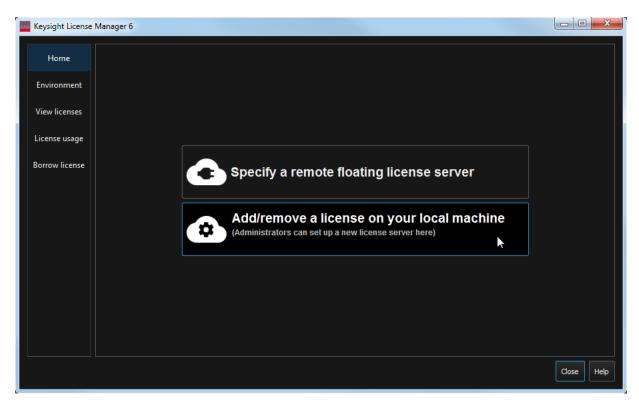

- 2 Launch Keysight License Manager 6.

- 3 From the Home tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to Keysight License Manager 6 Supporting Documentation.

2 Installing the Test Application and Licenses

Keysight D9030TBTC Thunderbolt 3 Test Application Methods of Implementation

# 3 Preparing to Take Measurements

Calibrating the Oscilloscope 36

Starting the Thunderbolt 3 Test Application 37

Before running the automated tests, you should calibrate the oscilloscope and probe. No test fixture is required for this application. After the oscilloscope and probe have been calibrated, you are ready to start the Thunderbolt 3 Test Application and perform the measurements.

#### Calibrating the Oscilloscope

If you have not already calibrated the oscilloscope, refer to the *User Guide* for the respective Oscilloscope you are using.

NOTE

If the ambient temperature changes more than 5 degrees Celsius from the calibration temperature, internal calibration should be performed again. The delta between the calibration temperature and the present operating temperature is shown in the **Utilities > Calibration** menu.

NOTE

If you switch cables between channels or other Oscilloscopes, it is necessary to perform cable and probe calibration again. Keysight recommends that, once calibration is performed, you label the cables with the channel on which they were calibrated.

## Starting the Thunderbolt 3 Test Application

1 Ensure that the Thunderbolt 3 Device Under Test (DUT) is operating and set to desired test modes. To start the Thunderbolt 3 Test Application: From the Infiniium Oscilloscope's main menu, select **Analyze > Automated Test Apps > D9030TBTC Thunderbolt 3 Test App**.

NOTE

The **Test Lane** drop-down options in the **Set Up** tab, when the Test App is launched on a 4-Channel Oscilloscope, are different from that on a 2-Channel Oscilloscope.

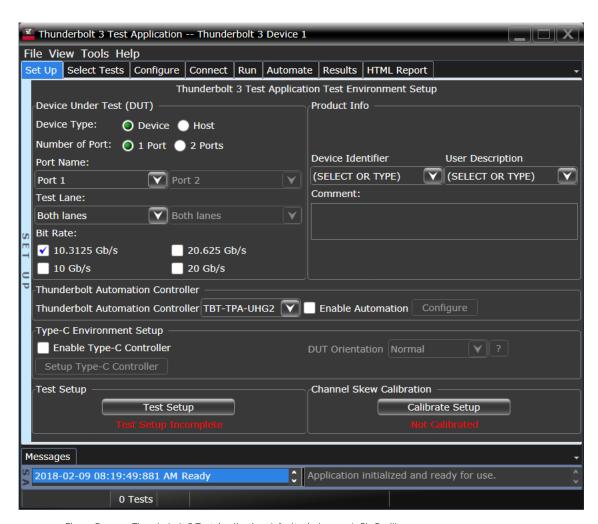

Figure 5 Thunderbolt 3 Test Application default window on 4-Ch Oscilloscope

Figure 6 Thunderbolt 3 Test Application default window on 2-Ch Oscilloscope

To understand the functionality of the various features in the user interface of the Test Application, refer to the *Keysight D9030TBTC Thunderbolt 3 Test Application Online Help* available in the Help menu.

The task flow pane and the tabs in the main pane show the steps you take in running the automated tests:

| Set Up       | Lets you identify and set up the test environment, including information about the device under test. The Test App includes relevant information in the final HTML report.                                                                                                 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

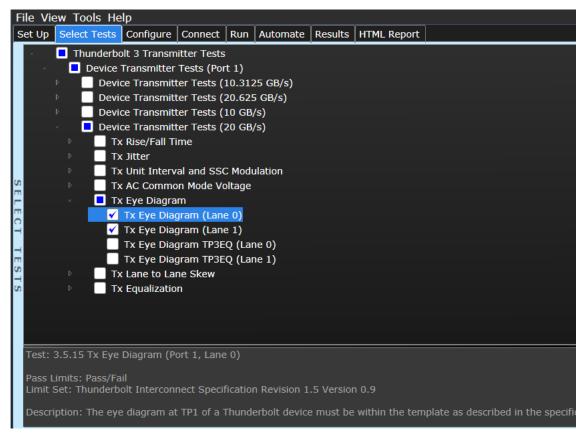

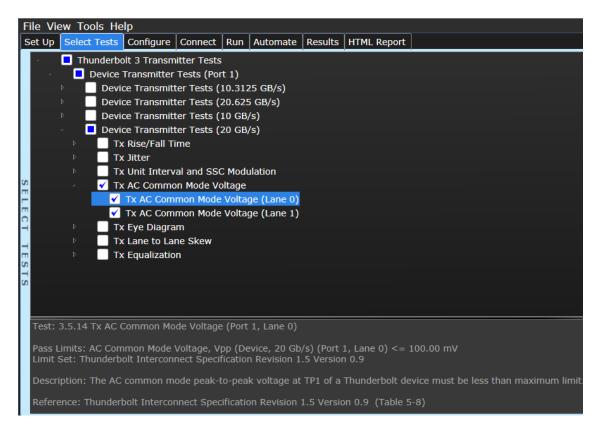

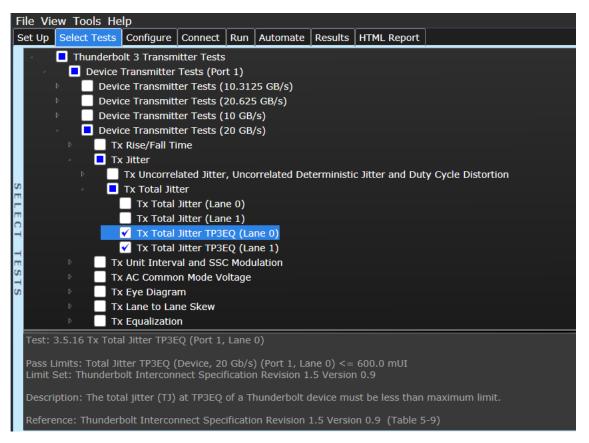

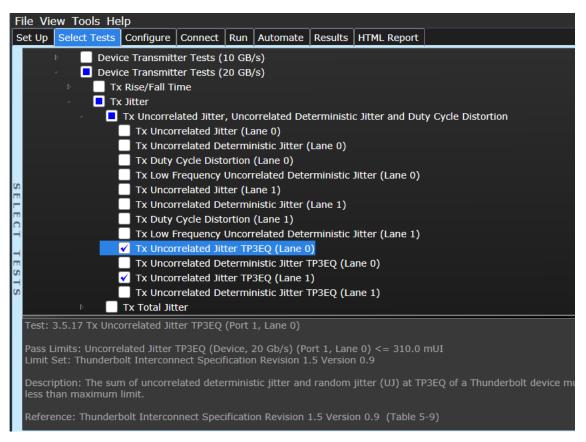

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select all tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.      |

| Configure    | Lets you configure test parameters (for example, channels used in test, voltage levels, etc.).                                                                                                                                                                             |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests that are to be run.                                                                                                                                                                       |

| Run          | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Automate     | Lets you construct scripts of commands that drive execution of the application.                                                                                                                                                                                            |

| Results      | Contains more detailed information about the tests that have been run. You can change the thresholds at which marginal or critical warnings appear.                                                                                                                        |

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

# NOTE

In the **Configure** tab, the values for all such Configuration parameters that are Oscilloscope-dependent, will correspond to the Oscilloscope Model (DSOs or UXRs), where you are running the Test Application.

## Setting up the Thunderbolt 3 Test Application

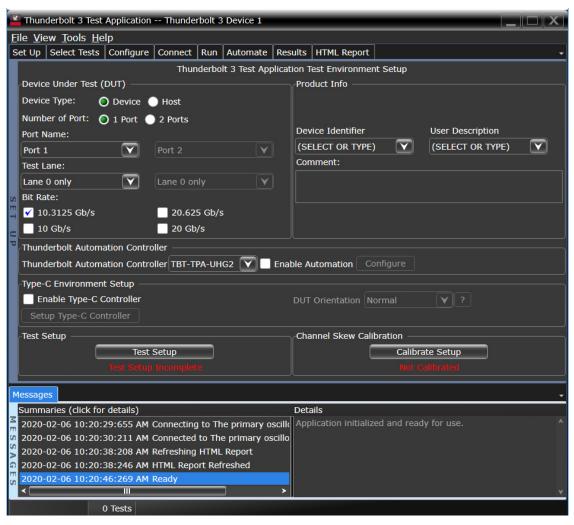

In order to run the electrical compliance tests on a Thunderbolt DUT operating at a bit rate of either 10.3125 GB/s, 20.625 GB/s, 10 GB/s. 20 GB/s or all, you must set up the Thunderbolt 3 Test Application to be able to view and select the required tests.

- 1 Start the Thunderbolt 3 Test Application. See "Starting the Thunderbolt 3 Test Application" on page 37.

- 2 Under the **Set Up** tab, select the following options, as shown in Figure 7.

- a **Device Type:** Select DUT Type as either **Device** (default) or **Host**.

- b Number of Port: Select 1 Port (default) or 2 Ports.

- c Port Name: —This drop-down field allows you to select a port name or even type a custom name for the ports being used for testing. Default values are Port 1 and Port 2.

- d Test Lane: The drop-down options, when the Test App is launched on a 4-Channel Oscilloscope, are different from that on a 2-Channel Oscilloscope.

- On a 4-Channel Oscilloscope—From the drop-down options, select either Both Lanes (default),

Lane 0 only or Lane 1 only; depending on the number of lanes being used for testing.

- On a 2-Channel Oscilloscope—From the drop-down options, select either Lane 0 only or Lane 1 only; depending on the number of lanes being used for testing.

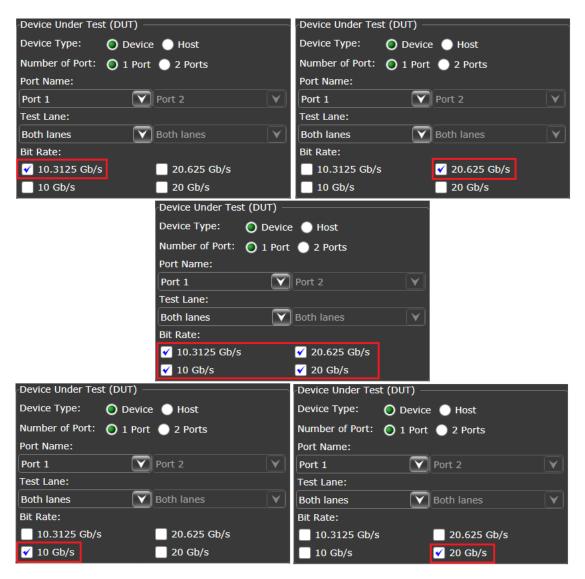

- e Bit Rate Select either one or more bit-rates to indicate the signal speed on the DUT.

- *f* **Product Info** Helps you in proper identification of the DUT on HTML reports. This option is particularly useful when running compliance tests on multiple DUTs.

- **Device Identifier:** Type an appropriate name/identifier for the DUT, which is being tested. The entries are saved such that you may select the values again later, if required.

- User Description: Type an appropriate description for the DUT, which is being tested. The

entries are saved such that you may select the values again later, if required.

- Comment: Type appropriate comments, if required.

- Thunderbolt Automation Controller Select Enable Automation to enable the automation controller. Use this feature for remote configuration and controlling of a Thunderbolt Host or Device, which is a usually a remote PC or a Thunderbolt Micro-Controller.

- h USB Type-C Test Controller Select Enable Type-C Controller to set up the Type-C controller. Use this feature to connect to the Type-C controller device along with defining the Type-C capability of the Thunderbolt DUT with Type-C implementation.

For more information about using the **Thunderbolt Automation Controller** and **USB Type-C Test Controller** features, refer to the *Keysight D9030TBTC Thunderbolt 3 Test Application Online Help*.

- Test Setup— Click the Test Setup button to set up the following calibration prerequisites:

- Preset Calibration Required to run the Transmitter Preset Calibration tests.

- CTLE Calibration Required to run the Transmitter CTLE Calibration tests.

- Power Profile Appears only when the Enable Type-C Controller is selected. Defines the power supply and demand requirements of a Thunderbolt DUT with Type-C implementation, which may be connected either as a provider or a consumer.

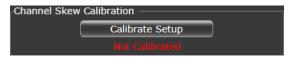

- j Channel Skew Calibration Click the Calibrate Setup button to perform Channel Skew Calibration before running the tests. Required to calibrate Channel Skew on the Oscilloscope Channels where the DUT is connected.

See "Calibration Setup for Compliance Tests" on page 47 for more information on these calibration options.

Figure 7 Set Up options for DUT Type "Device" on a 4-Channel Oscilloscope

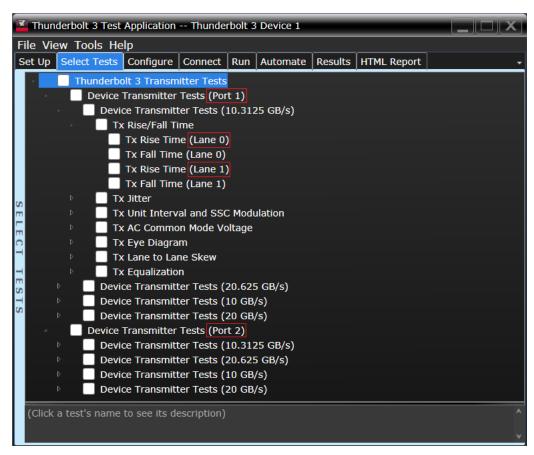

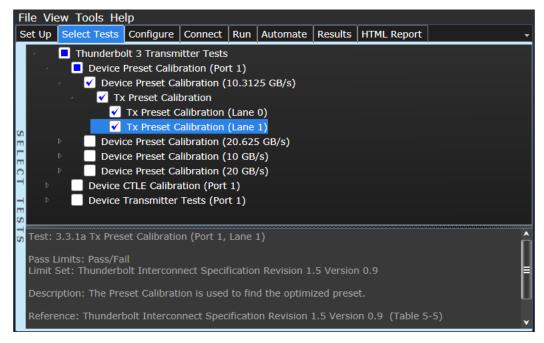

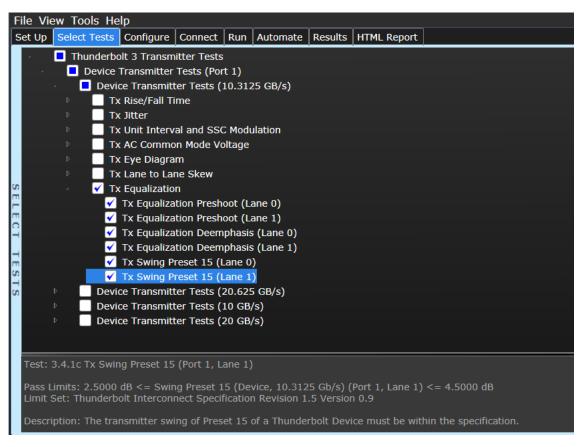

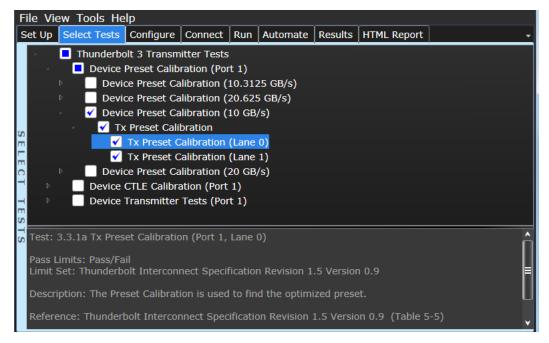

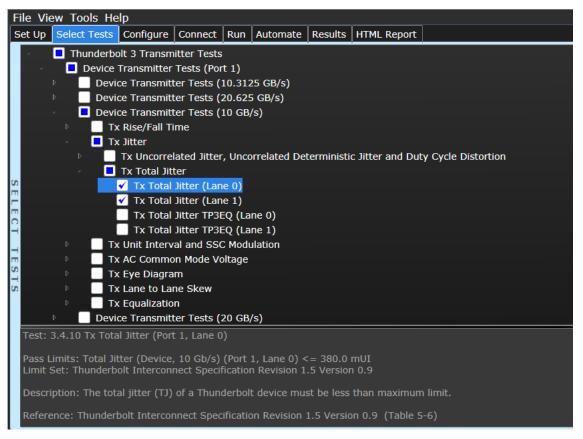

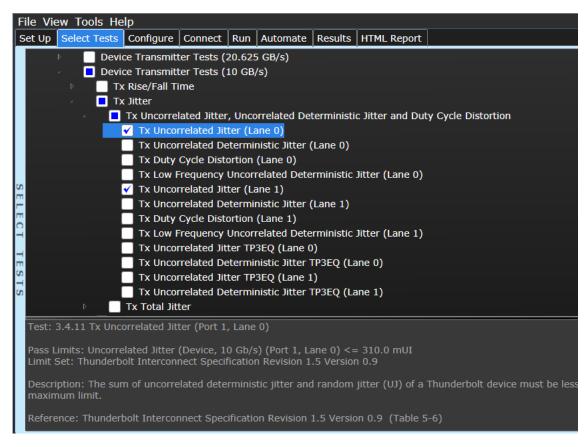

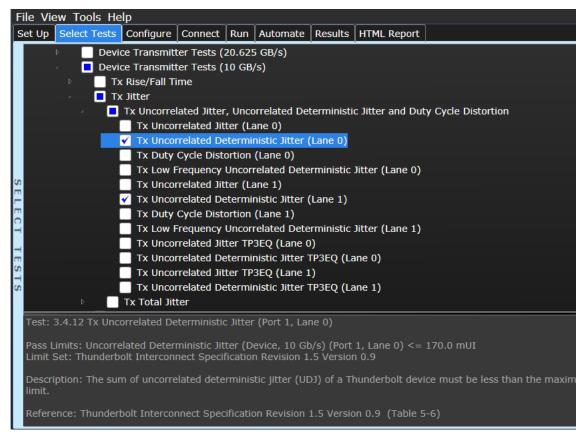

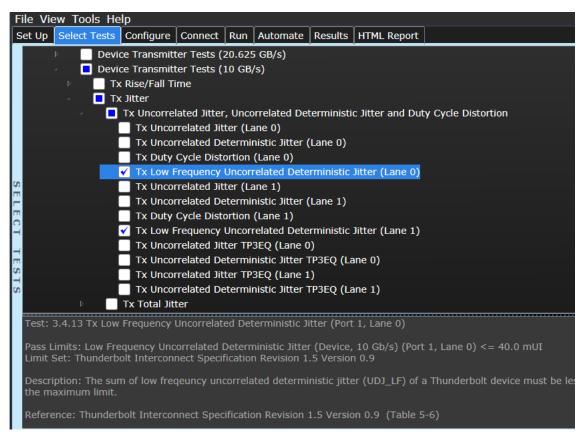

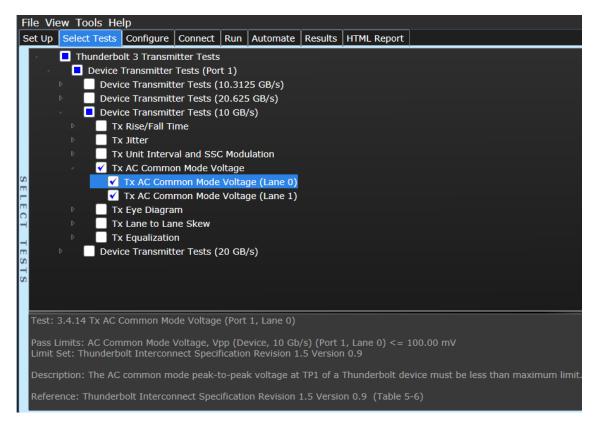

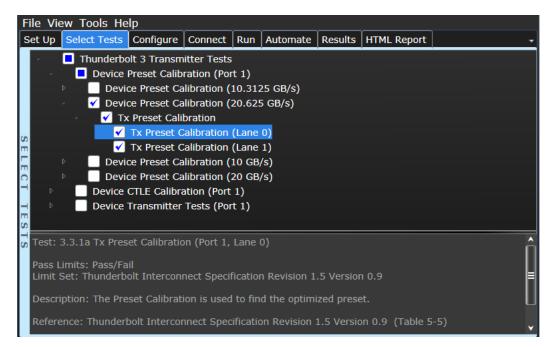

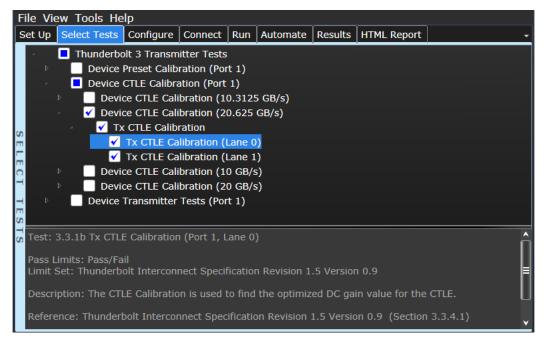

3 Based on your choices under the **Set Up** tab, the **Select Tests** tab filters tests into test groups corresponding to one or more selected bit-rates and the selected option for device type, port and lane.

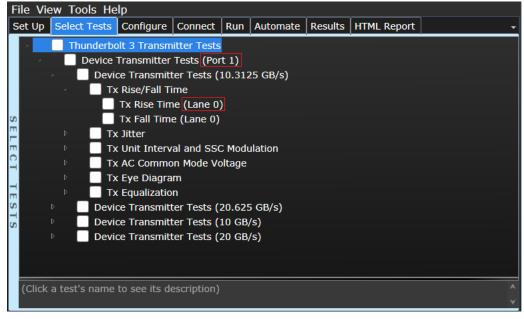

For example, Figure 8 shows how test groups are filtered when you select **Device Type:** as **Device**, **Number of Port** as **2 Ports** and **Test Lane:** as **Both lanes** along with selecting all bit rates. Similarly, Figure 9 shows how test groups are filtered when only one bit-rate is selected along with setting **Device Type:** as **Host**, **Number of Port** as **1 Port** and **Test Lane:** as **Lane 0 only.** Select the tests that you want to run using the Thunderbolt 3 Test Application. Refer to the *Keysight D9030TBTC Thunderbolt 3 Test Application Online Help* to know more about how to select tests.

NOTE

The **Test Lane** drop-down options in the **Set Up** tab, when the Test App is launched on a 4-Channel Oscilloscope, are different from that on a 2-Channel Oscilloscope. Therefore, on the latter instrument, only **Lane 0 only** or **Lane 1 only** options appear, as otherwise shown in Figure 8.

Figure 8 Selecting Transmitter Tests for all bit rates

Figure 9 Select Transmitter Tests for a single bit rate

NOTE

When running the Test App on a 2-Channel Oscilloscope, the **Select Tests** tab shall display tests pertaining to either **Lane 0 only** or to **Lane 1 only**.

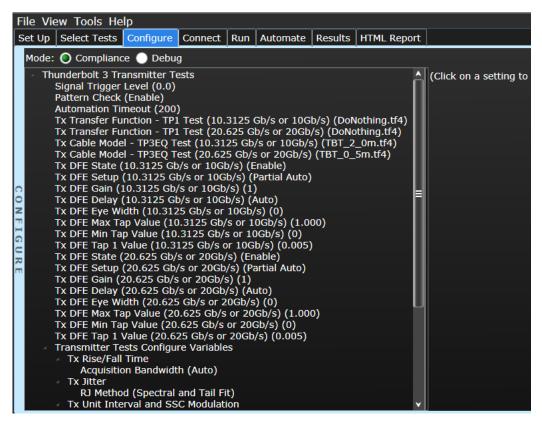

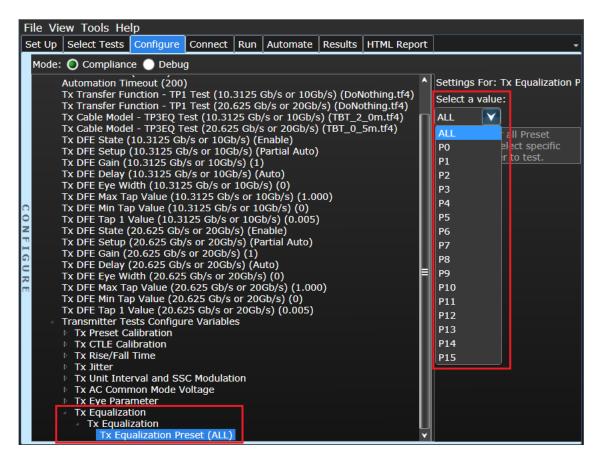

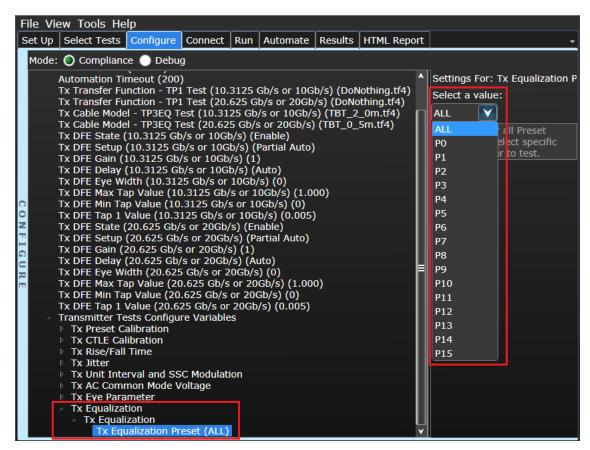

4 Under the **Configure** tab, you may modify the values for various configurable options associated with the compliance tests. By default, the Thunderbolt 3 Test Application sets the values of these options to the optimum value according to the standard specifications.

Figure 10 Configure options for Thunderbolt 3 Tests

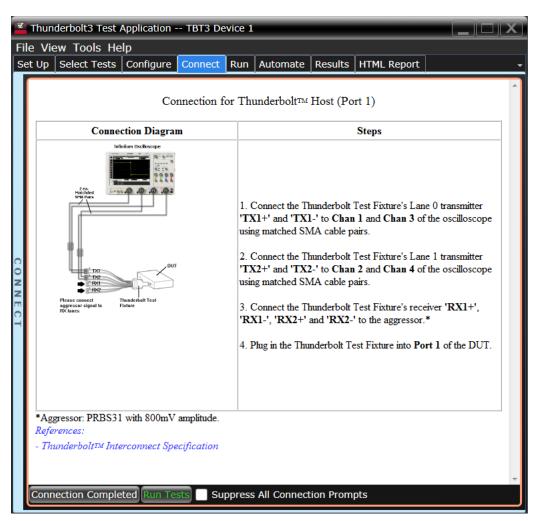

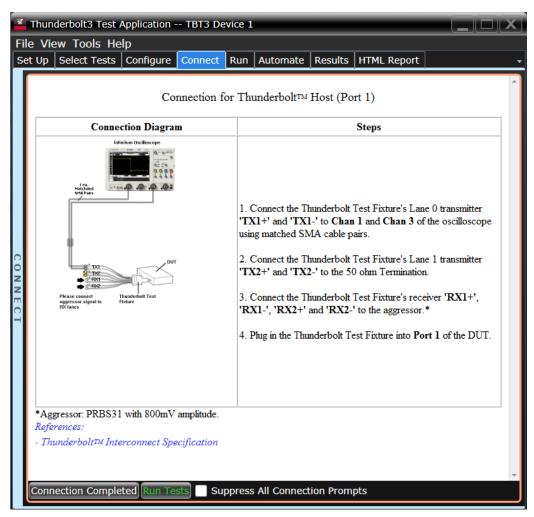

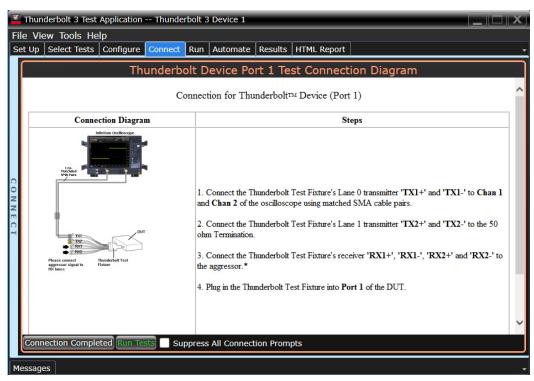

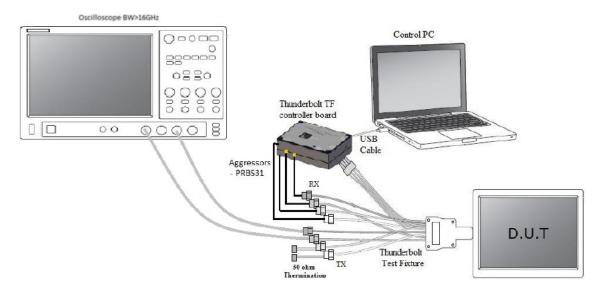

Under the **Connect** tab, the TThunderbolt 3 Test Application displays a Connection Diagram along with a list of instructions. Figure 11 and Figure 12 show the connection diagrams for a 2-Lane set up and for a 1-Lane set up, respectively, on a 4-Channel Oscilloscope, whereas Figure 13 shows the connection diagram for the "Lane 0 Only" set up on a 2-Channel Oscilloscope. If you have already set up a physical connection, you may verify else connect the DUT with the Oscilloscope as shown under this tab. Note that during some test runs, the application may prompt you for a change in physical connection/setup.

Figure 11 Connection Diagram and Instructions for a 2-Lane test set up on a 4-Ch Oscilloscope

Figure 12 Connection Diagram and Instructions for a 1-Lane test set up on a 4-Ch Oscilloscope

Figure 13 Connection Diagram and Instructions for "Lane 0 Only" on 2-Channel Oscilloscope

Once you have performed steps 1 to 5, you are ready to run compliance tests on the Thunderbolt DUT. Additionally, you may configure/modify the run settings, automate options in the Test Application, view, export and print the test results and the HTML reports generated by the Test Application. Refer to the Keysight D9030TBTC Thunderbolt 3 Test Application Online Help to know more about how to use the Test Application.

## Calibration Setup for Compliance Tests

Before running compliance tests on a Thunderbolt DUT, it is imperative that the testing equipment and its accessories be calibrated. The Thunderbolt 3 Test Application provides the options to run Channel Skew Calibration and configure settings for Preset Calibration and CTLE Calibration.

## Channel Skew Calibration

In order to achieve accurate test results and to verify that the Device under test is compliant to the standards, it is necessary to calibrate the Oscilloscope channels that are connected via cables to the Thunderbolt DUT.

## Perform the following:

1 In the **Channel Skew Calibration** area of the **Set Up** tab of the Thunderbolt 3 Test Application, click the **Calibrate Setup** button.

Figure 14 Channel Skew Calibration area under the **Set Up** tab

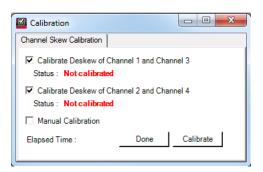

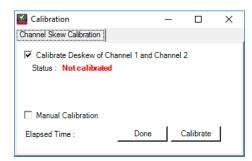

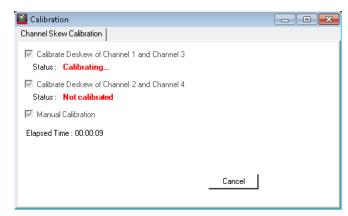

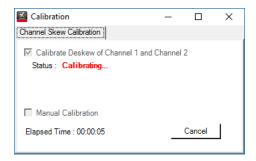

2 The **Calibration** window appears, where the **Channel Skew Calibration** tab is displayed by default, as shown in Figure 15 for a 4-Channel Oscilloscope and in Figure 16 for a 2-Channel Oscilloscope.

Figure 15 Options for Channel Skew Calibration on a 4-Channel Oscilloscope

Figure 16 Options for Channel Skew Calibration on a 2-Channel Oscilloscope

Under the **Channel Skew Calibration** tab, the Thunderbolt 3 Test Application displays the status of the Oscilloscope Channels that have been calibrated for de-skew. As shown in the images above, the options are checked by default and the status of each of these options is **Not Calibrated**. You may also select the **Manual Calibration** check box to perform Channel Skew Calibration later.

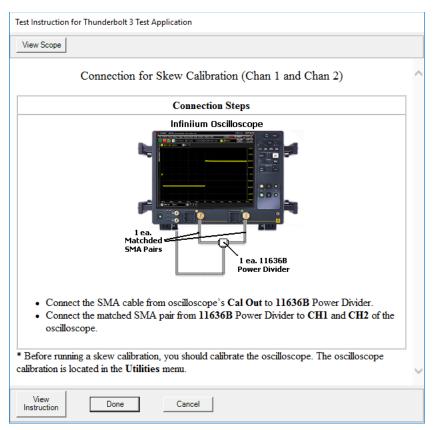

To start calibration of the selected Oscilloscope channel pairs, click the **Calibrate** button. The **Test Instruction for Thunderbolt 3 Compliance** window appears.

Figure 17 Instructions for Channel Skew Calibration for the selected Channels on a 4-Ch Oscilloscope

Figure 18 Instructions for Channel Skew Calibration for the selected Channels on a 2-Ch Oscilloscope

The **Test Instruction for Thunderbolt 3 Compliance** window provides instructions and connection diagram required to be set up to perform Channel Skew Calibration. Note that before you start performing Channel Skew Calibration, the Oscilloscope must have been calibrated.

On the Test Instruction for Thunderbolt 3 Compliance window,

- 1 Click the View Scope button to minimize this window and to see the Oscilloscope screen for the waveform and to use the Infiniium controls to perform Oscilloscope Calibration (if it has not been done yet).

- 2 Click the **View Instruction** button to maximize the window to view the instructions and the connection diagram again.

- 3 Once you have set up the physical connection for Channel Skew Calibration for the respective channels, click **Done** to begin Calibration. You may click **Cancel** at any point to simply return to the **Calibration** window.

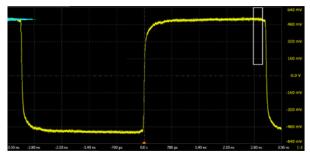

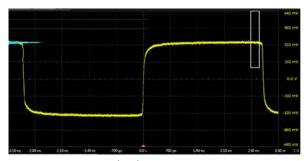

When you click **Done**, the **Calibration** window displays again with the updated Status along with the time elapsed during this process, as shown in Figure 19 and :

Figure 19 Changes in Calibration status on a 4-Channel Oscilloscope

Figure 20 Changes in Calibration status on a 2-Channel Oscilloscope

Once the Calibration process is successfully done, the status changes to **Calibrated**. You may click **Cancel** to stop the process of Channel Skew Calibration at any time.

4 After the Channel Skew Calibration is complete, click the **Done** button to return to the Thunderbolt 3 Test Application Test Environment Setup.

## Preset Calibration

The **Preset Calibration** tab allows you to select the preset number, which has been set on the Thunderbolt DUT, to be used in the Thunderbolt 3 Test Application. You may also perform the preset sweep to find the optimum preset.

Perform the following:

1 In the **Test Setup** area of the **Set Up** tab of the Thunderbolt 3 Test Application, click the **Test Setup** button.

Figure 21 Test Setup area under the **Set Up** tab

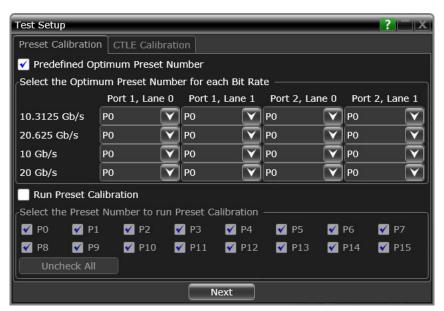

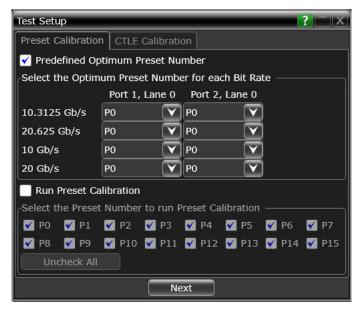

2 The **Test Setup** window appears, where the **Preset Calibration** tab is displayed by default, as shown in Figure 22 for a 4-Channel Oscilloscope and Figure 23 for a 2-Channel Oscilloscope.

Figure 22 Default view of the Preset Calibration tab on a 4-Channel Oscilloscope

Figure 23 Default view of the Preset Calibration tab on a 2-Channel Oscilloscope

Under the **Preset Calibration** tab,

- 1 By default, the **Predefined Optimum Preset Number** check-box is selected and the default Preset Number for the selected bit rates is set to **P0**.

- 2 From the **Select the Optimum Preset Number for each Bit Rate** area, select a preset number from the drop-down options corresponding to each bit-rate and port-lane combination.

- 3 Select the **Run Preset Calibration** check-box only if you wish to run Preset Calibration to find the optimum preset value for the DUT. By default, all preset values are selected.

- 4 In the **Run Preset Calibration**, you may de-select any of the preset numbers to exclude them from preset calibration. You may use the **Uncheck All** or **Check All** radio buttons to perform this action as well.

NOTE

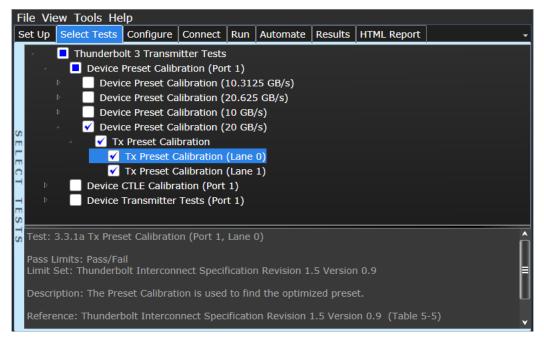

By default, the test group for **Preset Calibration** for each selected bit-rate is hidden in the **Select Tests** tab when **Predefined Optimum Preset Number** is selected for the respective bit-rates. To view and select the **Preset Calibration** tests in the **Select Tests** tab, select the **Run Preset Calibration** option in the **Test Setup** window of the **Set Up** tab.

5 Click **Next** to move to the next tab.

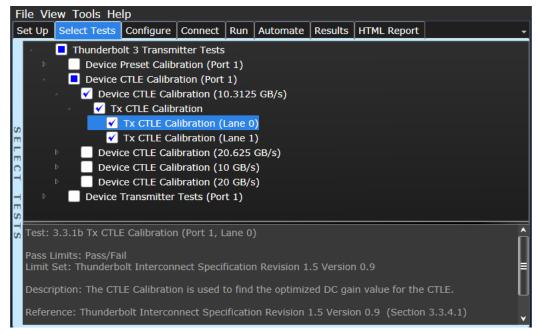

### **CTLE Calibration**

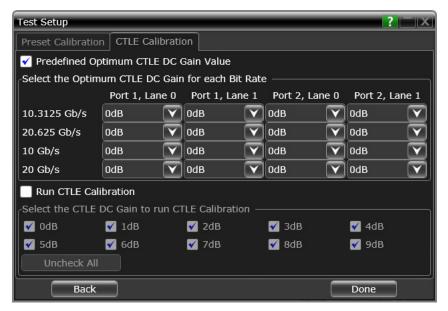

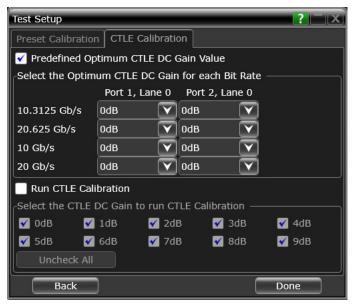

The **CTLE Calibration** tab allows you to select the Continues-Time Linear Equalizer (CTLE) used for the TP3EQ tests in the Thunderbolt 3 Test Application. You may also perform the CTLE DC gain sweep to find the optimum CTLE DC gain.

Figure 24 Default view of the CTLE Calibration tab on a 4-Channel Oscilloscope

Figure 25 Default view of the CTLE Calibration tab on a 2-Channel Oscilloscope

Under the CTLE Calibration tab.

- 1 By default, the **Predefined Optimum CTLE DC Gain Value** check-box is selected and the default DC Gain value for the selected bit rates is set to **0dB**.

- 2 From the **Select the Optimum CTLE DC Gain for each Bit Rate** area, select a DC Gain value from the drop-down options corresponding to each bit-rate and port-lane combination.

- 3 Select the **Run CTLE Calibration** check-box only if you wish to run CTLE Calibration to find the optimum DC Gain value for the DUT. By default, all DC Gain values are selected.

- 4 In the **Run CTLE Calibration** area, you may de-select any of the DC Gain values to exclude them from CTLE calibration. You may use the **Uncheck All** or **Check All** radio buttons to perform this action as well.

NOTE

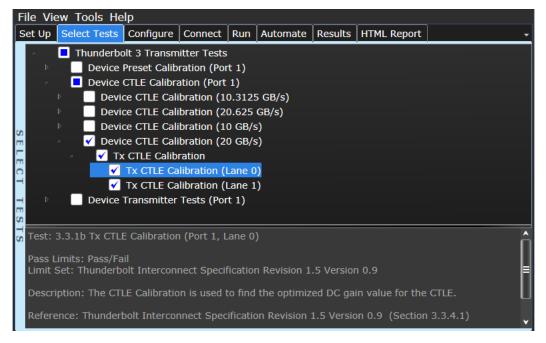

By default, the test group for CTLE Calibration for each selected bit-rate is hidden in the Select Tests tab when Predefined Optimum CTLE DC Gain Value is selected for the respective bit-rates. To view and select the CTLE Calibration tests in the Select Tests tab, select the Run CTLE Calibration option in the Test Setup window of the Set Up tab.

- 5 Click **Done** to save any modifications done to the **Test Setup** window and to return to the Thunderbolt Test Environment Setup.

- 6 If you have enabled Type-C Controller in the **Set Up** tab, the **Power Profile** tab is also displayed in the **Test Setup** window. Click the **Next** button, which appears instead of **Done**.

### Power Profile

The **Power Profile** tab allows you to select the voltage and current requirements when the Thunderbolt DUT with the Type-C implementation is connected for testing.

Figure 26 Default view of the Power Profile tab

## Under the Power Profile tab,

- 1 Use the check-box to select or de-select one of listed Provider Power Profile or Consumer Power Profile options.

- If the connected Thunderbolt3 DUT with Type-C behaves as the source of power supply, it is identified and denoted as Provider Power Profile. If the DUT consumes power, it is identified and denoted as Consumer Power Profile.

- 2 The number of power profiles displayed varies based on the power profile supported by the DUT, which in turn, is obtained during the DUT Capability Query.

- 3 Click **Done** to save any modifications done to the **Power Profile** tab and to return to the Thunderbolt 3 Test Application Test Environment Setup.

Keysight D9030TBTC Thunderbolt 3 Test Application Methods of Implementation

# 4 Host / Device Thunderbolt 3 Transmitter Testing

System Components in Thunderbolt Technology / 56

3rd Generation Thunderbolt Compliance Methodology / 59

Requirements for Host / Device Transmitter Compliance / 64

Transmitter Test Setup / 73

The Keysight D9030TBTC Thunderbolt 3 Test Application enables compliance testing of the Host and Device Transmitter systems operating at bit rates of either 10.3125 GB/s, 20.625 GB/s, 10 GB/s or 20 GB/s; based on *USB Type-C Thunderbolt Alternate Mode Electrical Host \ Device Compliance Test Specification Revision 1.5, Version 0.9.*

## System Components in Thunderbolt Technology

The following section help you understand an overview of the system components associated with Transmitter testing in the Thunderbolt Technology.

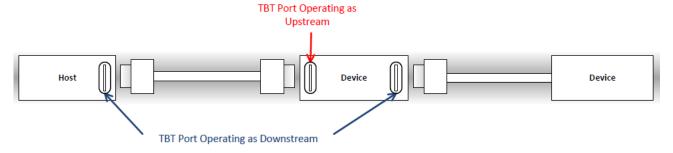

## Overview

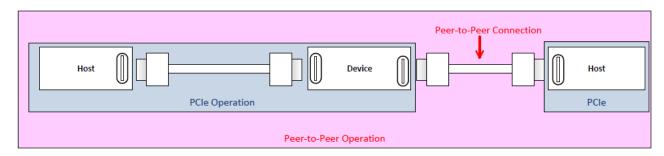

You may construct a range of system Devices using the networking architecture of the Thunderbolt Technology. The Thunderbolt Technology connector ports, which function either as "Upstream" (pointing towards a Host) or "Downstream" (pointing towards an Endpoint), characterize the Thunderbolt Technology link. A network of Thunderbolt Technology links, after they are connected and configured, form a tree topology, such that the upstream ports lead to a Thunderbolt Host at the root of the tree. For example, a Thunderbolt Device may exchange information with the Thunderbolt Host on its upstream Thunderbolt Technology connector, thereby behaving as an information channel between the Host and Devices to its downstream port(s), which may be connected directly or indirectly. See Figure 27.

Figure 27 Thunderbolt Technology Link Connection Block Diagram

An inter-domain connection is established when two Thunderbolt Host systems are connected directly. An inter-domain connection is also referred to as a peer-to-peer connection and is also formed when two downstream ports, originating from two different Host trees, are connected.

You shall find that in the inter-domain connections, memory to memory transactions occur for communication between the Host systems and the system software configures the connections for the Thunderbolt network in their respective tree, such as DisplayPort connections and PCIe transactions to Devices are carried out with the Host in their respective tree. See Figure 28.

Figure 28 Thunderbolt Technology Peer-to-Peer Connection Block Diagram

The Thunderbolt Technology link consists of a Thunderbolt Host, a Thunderbolt Display, a Thunderbolt Adapter and a Thunderbolt Application Device. A Thunderbolt Display, a Thunderbolt Adapter or a Thunderbolt Application Device are generically referred to as Thunderbolt Devices.

#### Thunderbolt Host

This component is a usually a computer. A Thunderbolt Host has one or more "Downstream" Thunderbolt Technology connector ports, but no "Upstream" Thunderbolt Technology connector ports. However, Thunderbolt Hosts can be connected peer-to-peer. A Thunderbolt Host provides the role of Thunderbolt network discovery and configuration. There shall be at least one Thunderbolt Host in a Thunderbolt network. A Thunderbolt network with more than one Thunderbolt Host can provide peer-to-peer communications between the Thunderbolt Hosts present on the network. A Thunderbolt Host Type-C includes the following:

- A Thunderbolt Controller, which contains one or more DisplayPort input interfaces, a PCI Express interface, and one or more Thunderbolt Technology interfaces.

- A multiplexer, which selects either Thunderbolt, DP v1.2, or USB r3.1 data. The multiplexer is integrated into the 3rd Generation Thunderbolt Controller.

- A Link Controller with a UART interface for managing operation and power states of the Thunderbolt link when in the Thunderbolt Alternate Mode. The Link Controller is integrated into the 3rd Generation Thunderbolt Controller.

- A USB PD Port Controller implemented as a DRP with the ability to support the Thunderbolt and DisplayPort Alternate Modes.

- · At least one USB Type-C connector.

Table 2 lists the Thunderbolt Host rules in conjunction with the USB Type-C connector.

Table 2 Thunderbolt Host Rules with USB Type-C connector

| Technology  | Thunderbolt Host Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB         | <ul> <li>Hosts shall support USB r3.1 gen1 and gen2. Hosts shall support USB r2.0.</li> <li>Hosts shall support USB PD and Biphase Mark Coding.</li> <li>Hosts shall provision power as defined in Section 7.3 of the USB Type-C Thunderbolt Alternate Mode Electrical Host \ Device Compliance Test Specification Revision 1.5, Version 0.9.</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |

| Thunderbolt | <ul> <li>Hosts shall support 3rd Generation Thunderbolt with the USB Type-C connector.</li> <li>Hosts shall support the pin mapping as defined in Section 7.5.1 of the USB Type-C Thunderbolt Alternate Mode Electrical Host \ Device Compliance Test Specification Revision 1.5, Version 0.9.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCle        | <ul> <li>Hosts shall connect PCIe to the Thunderbolt Controller.</li> <li>One port Hosts are recommended to connect 4-lanes of PCIe Gen3 to the Thunderbolt Controller.</li> <li>One port Hosts shall connect at least 2-lanes of PCIe Gen3 to the Thunderbolt Controller.</li> <li>Two port Hosts shall connect 4-lanes of PCIe Gen3 to the Thunderbolt Controller.</li> <li>Hosts shall support PCIe hot plug.</li> </ul>                                                                                                                                                                                                                                                                                   |

| DisplayPort | <ul> <li>Hosts shall redrive DisplayPort from the Thunderbolt Controller to the USB Type-C connector.</li> <li>One port Thunderbolt Hosts are recommended to connect two DP v1.2 streams (4-lanes each) to the Thunderbolt Controller.</li> <li>One port Thunderbolt Hosts shall connect at least one DP v1.2 stream (4-lanes) to the Thunderbolt Controller.</li> <li>Two port Thunderbolt Hosts shall connect at least two DP v1.2 streams (4-lanes each) to the Thunderbolt Controller.</li> <li>Hosts shall support the pin mapping as defined in Section 7.5.2 of the USB Type-C Thunderbolt Alternate Mode Electrical Host \ Device Compliance Test Specification Revision 1.5, Version 0.9.</li> </ul> |

#### Thunderbolt Device

A Thunderbolt Device has at least one port that is capable of operating as an "Upstream" port and contains a Thunderbolt Controller and optionally a PCIe to I/O Bridge to another interface such as FireWire, Ethernet, or eSATA. The Thunderbolt Device may present the other interface connector or may include internal functionality that is appropriate to a device. Thunderbolt Controllers contain some PCIe to I/O bridging capabilities and additional I/O Bridge chips may not be needed. You may refer to the appropriate Thunderbolt Controller datasheet for more information.

When the Thunderbolt Device is connected to the Thunderbolt Host, the bridge chip functions as if it were connected directly to the Host's PCIe bus. A Thunderbolt Device with a downstream port, shall provide DP v1.2 support or USB r3.1 support in the case where a USB Type-C cable and a USB or DP Device are connected. Examples of Thunderbolt Devices include a PCIe expansion chassis or a RAID array controller, a Thunderbolt to FireWire adapter, a Thunderbolt to Ethernet adapter, a Thunderbolt Display and so on.

A Thunderbolt Device may have one or more ports, which can operate as "Downstream" port(s). A Thunderbolt Device may or may not have a Thunderbolt cable permanently attached. A Thunderbolt Device with a Thunderbolt cable permanently attached is called a Tethered Device.

Thunderbolt Display—A Thunderbolt Display is a specific type of Thunderbolt Device. A Thunderbolt Display has at least one port, which is capable of operating as an Upstream Thunderbolt Technology connector port and an integrated display which shall display DisplayPort format information tunneled through the Thunderbolt Technology link. A Thunderbolt Display may also have a second port operating as a "Downstream" port. Downstream ports operate as the Thunderbolt Technology connector ports and optionally support USB r3.1 when a USB device is connected or DP on Type-C when a DisplayPort adapter is connected. A Thunderbolt Display may also contain PCIe subsystems connected to the Thunderbolt Controller's PCIe interface, for example a Gigabit Ethernet controller.

## Thunderbolt Links and Lanes

A link is defined as one or more dual-simplex communication paths between two Thunderbolt Controllers. A link may be composed of multiple lanes or channels. A link is symmetric in that each direction of the link shall support the same number of lanes and each lane shall operate at the same signaling rate.

A lane is composed of two differential signal pairs, one transmitting and one receiving. Each differential pair operates at a signaling rate which defines the speed of communication for that lane. Multiple lanes may be aggregated (bonded) to scale bandwidth. The Thunderbolt Technology connector can be connected to 1 or 2 Thunderbolt Lanes, depending on the implementation or Thunderbolt rules.

## 3rd Generation Thunderbolt Compliance Methodology

System Compliance Test Point Definitions

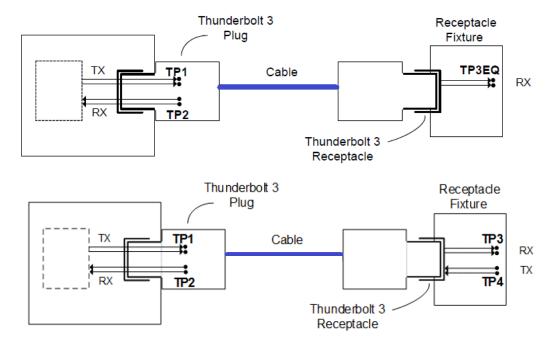

The 3rd Generation Thunderbolt defines the following reference points for compliance testing of Host/Device Thunderbolt Transmitter Systems:

- 1 TP1—Reference measurement point located at the plug side of the Host/Device Transmitter output. Used as a reference point for defining the Host/Device Transmitter and the Active Cable/Adapter Receiver specifications.

- 2 TP2—Reference measurement point located at the plug side of the Host/Device Receiver input. Used as a reference point for defining the Active Cable/Adapter Transmitter and the Host/Device Receiver specifications.

- 3 TP3EQ—Reference measurement point located at the far-end side of a passive cable or at the output of a tethered device. Used as a reference point for passive installations and tethered devices. All the measurements at this point are done after applying reference equalization.

For Host / Device Transmitter testing, all measurements shall be referenced to the TP1/TP3EQ compliance points defined above and as shown in Figure 29. Calibration shall be applied in cases where direct measurement at TP1 is not feasible.

Figure 29 Thunderbolt Compliance Points Definition

## AC Coupling Capacitors

The high speed electrical interfaces shall be AC-coupled. The Host/Device transmit paths shall include AC-coupling capacitance between 165nF and 265nF. In addition, the plugs of the Active Cable and the Tethered Device should include AC-coupling capacitance between 165nF and 265nF placed at their output transmit path. Capacitors shall not be placed on the high-speed receiver paths of the different 3rd Generation Thunderbolt components.

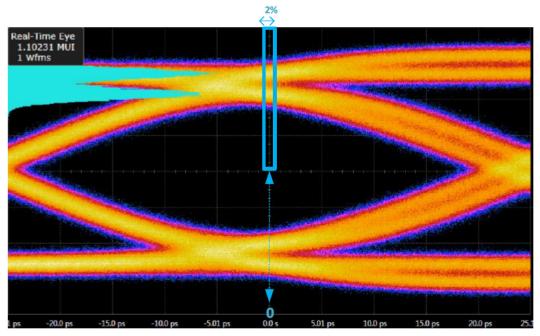

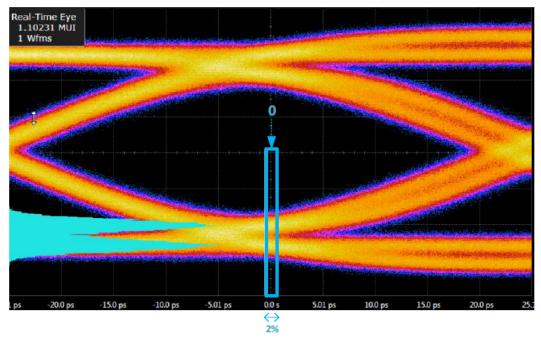

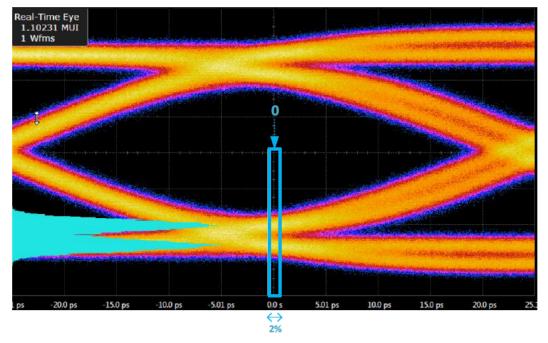

# Jitter and Eye Measurement Methodology

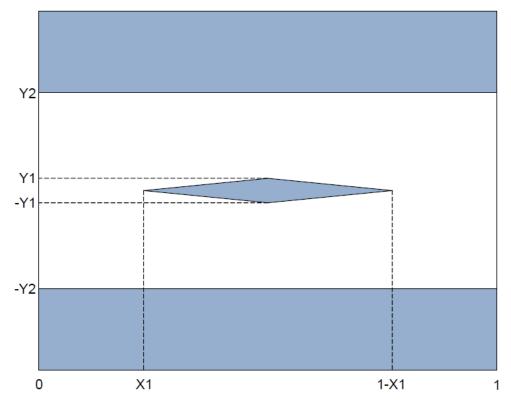

The Thunderbolt jitter and eye diagram specifications are all referenced to a golden clock-and-data recovery (CDR) function, meaning that all measurements shall be performed after applying appropriate tracking on the signal's phase. The reference CDR is modeled by a 2nd order PLL response (type II), which derives the following jitter rejection mask, described in Laplace domain, as described in Figure 30:

$$\begin{split} H_{jitter}(s) &= \frac{s^2}{s^2 + 2 \cdot \zeta \cdot \omega_n \cdot s + \omega_n^2} \\ \text{Where:} \\ s &= j \cdot 2 \cdot \pi \cdot f, \qquad \zeta \text{ is the damping factor,} \\ \omega_n \text{ is the natural frequency of the system} \end{split}$$

Figure 30 Jitter Rejection Mask described in Laplace domain

Table 3 defines the 3rd Generation Thunderbolt Reference CDR Parameters:

Table 3 3rd Generation Thunderbolt Reference CDR Parameters

| Speed                          | Damping Factor | Cutoff Frequency [Hz] |

|--------------------------------|----------------|-----------------------|

| Gen2 (10.3125 GB/s or 10 GB/s) | 0.94           | 5MHz                  |

| Gen3 (20.625 GB/s or 20 GB/s)  | 0.94           | 5MHz                  |

## Reference Equalization Function

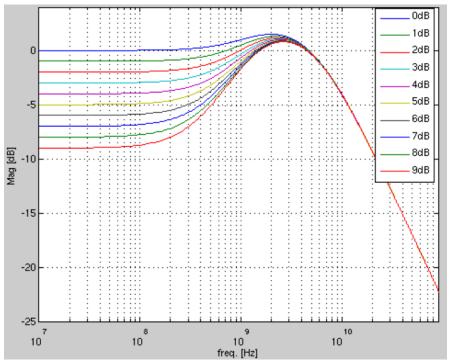

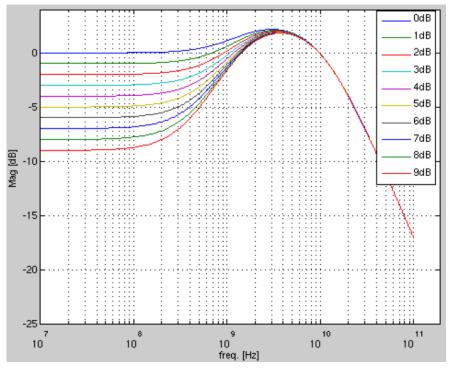

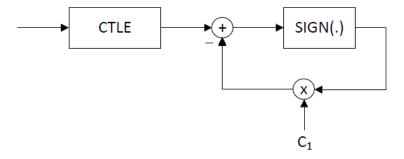

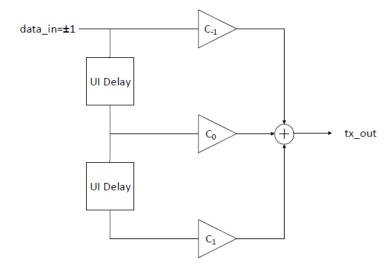

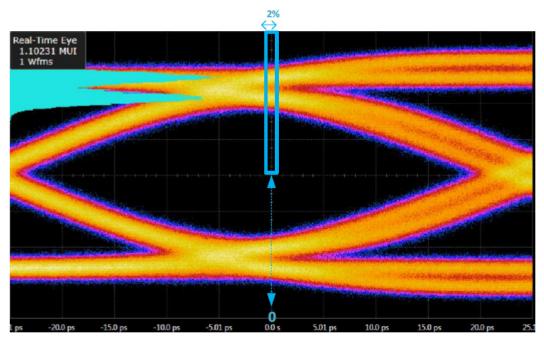

All the measurements done at the output of the cable assembly, denoted as TP3EQ, should be referenced to a golden receiver equalization function, that is, all measurements shall be performed after applying appropriate equalization on the measured signals. The reference receiver applied at TP3EQ comprises of parametric Continuous–Time–Linear–Equalizer (CTLE) and Decision–Feedback–Equalizer (DFE), as described in Figure 31. For each measurement referenced to TP3EQ, make sure to set the best equalization parameters such that the calculated eye–diagram is optimized.

## Reference CTLE

The equation, shown in Figure 31, describes the frequency response for the Converged IO reference continuous time linear equalizer (CTLE) that must be used for compliance testing:

$$H(s) = 1.41 \cdot w_{p2} \cdot \frac{s + \frac{A_{DC}}{1.41} \cdot w_{p1}}{(s + w_{p1}) \cdot (s + w_{p2})}$$

Where:

A<sub>DC</sub> is the DC gain

$$w_{p1} = \begin{cases} 2 \cdot \pi \cdot 1.5e9 \, \frac{rad}{Sec} & Speed = 10.3125 \, Gb \, / \, s \\ 2 \cdot \pi \cdot 5e9 \, \frac{rad}{Sec} & Speed = 20.625 \, Gb \, / \, s \end{cases}$$

$$w_{p2} = \begin{cases} 2 \cdot \pi \cdot 5e9 \frac{rad}{Sec} & Speed = 10.3125 Gb / s \\ 2 \cdot \pi \cdot 10e9 \frac{rad}{Sec} & Speed = 20.625 Gb / s \end{cases}$$

## $s = i \cdot 2 \cdot \pi \cdot f$ is the frequency in Laplace domain

Figure 31 Frequency Response Equation for 3rd Generation Thunderbolt CTLE

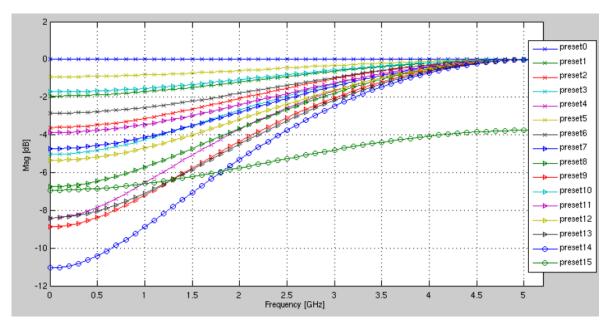

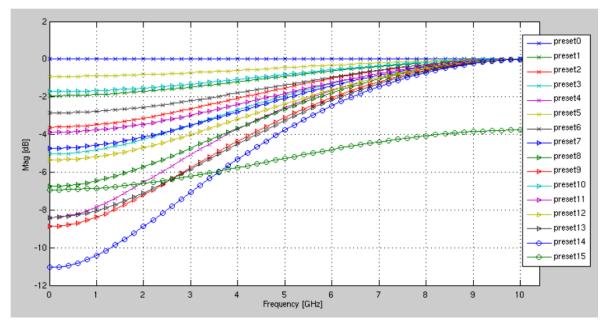

Apply ten different CTLE configurations such that the value of  $A_{DC}$  is one of  $\{10^{-x/20} : x = 0, 1, 2, ..., 9 [dB]\}$ .

Figure 32 and Figure 33 show the Frequency Response of the 3rd Generation Thunderbolt Reference CTLE for Gen2 devices and for Gen3 devices, respectively.

Figure 32 Thunderbolt 3 Reference CTLE for Gen2 devices

Thunderbolt 3 Reference CTLE for Gen3 devices Figure 33

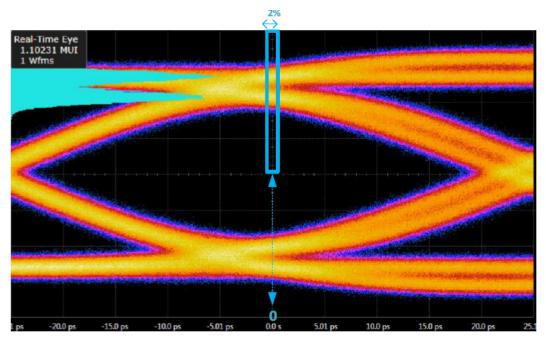

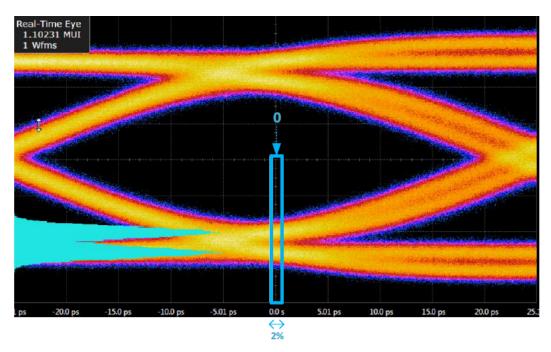

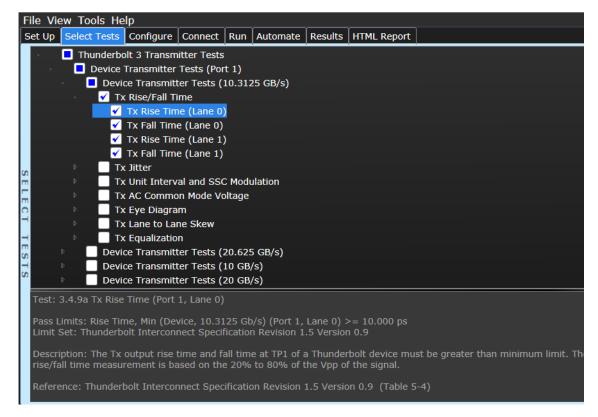

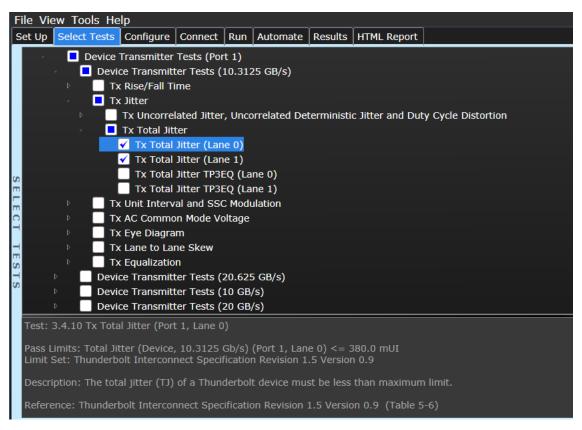

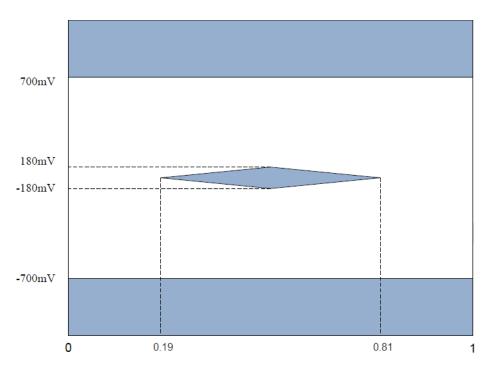

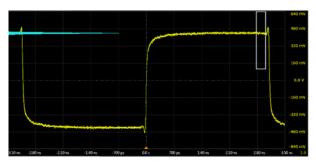

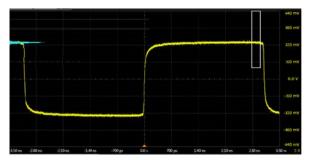

## Reference DFE