# DDR/LPDDR Post Process Compliance Tool

User Guide

### **Notices**

© Keysight Technologies 2008-2016, 2018, 2019, 2022

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

### **Trademarks**

UNIX is a registered trademark of UNIX System Laboratories in the U.S.A. and other countries. Target is copyrighted by Thru-Put Systems, Inc.

Software Release

07.00.0000

Edition

April 2022

Available in electronic format only

Keysight Technologies 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS." AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com /find/ sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater than Limited Rights as defined in

FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data. 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

Safety Notices

### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Safety Summary

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings or operating instructions in the product manuals violates safety standards of design, manufacture, and intended use of the instrument. Keysight Technologies assumes no liability for the customer's failure to comply with these requirements. Product manuals are provided with your instrument on CD-ROM and/or in printed form. Printed manuals are an option for many products. Manuals may also be available on the Web. Go to <a href="https://www.keysight.com">www.keysight.com</a> and type in your product number in the Search field at the top of the page.

General

Do not use this product in any manner not specified by the manufacturer. The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

Before Applying Power

Verify that all safety precautions are taken. Make all connections to the unit before applying power. Note the instrument's external markings described in "Safety Symbols".

Ground the Instrument

If your product is provided with a grounding type power plug, the instrument chassis and cover must be connected to an electrical ground to minimize shock hazard. The ground pin must be firmly connected to an electrical ground (safety ground) terminal at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

Fuses

See the user's guide or operator's manual for information about line-fuse replacement. Some instruments contain an internal fuse, which is not user accessible.

Do Not Operate in an Explosive Atmosphere Do not operate the instrument in the presence of flammable gases or fumes.

Do Not Remove the Instrument Cover

Only qualified, service-trained personnel who are aware of the hazards involved should remove instrument covers. Always disconnect the power cable and any external circuits before removing the instrument cover.

Cleaning

Clean the outside of the instrument with a soft, lint-free, slightly dampened cloth. Do not use detergent or chemical solvents.

Do Not Modify the Instrument

Do not install substitute parts or perform any unauthorized modification to the product. Return the product to an Keysight Sales and Service Office for service and repair to ensure that safety features are maintained.

In Case of Damage

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Safety Symbols

Table 1 Safety Symbol

| Symbol                             | Description                                                                                                                                  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| ===                                | Direct current                                                                                                                               |

| $\sim$                             | Alternating current                                                                                                                          |

| $\overline{\sim}$                  | Both direct and alternating current                                                                                                          |

| <sub>3</sub> ~                     | Three phase alternating current                                                                                                              |

| <sub>3</sub> ~                     | Three phase alternating current                                                                                                              |

| <b>=</b>                           | Earth ground terminal                                                                                                                        |

|                                    | Protective earth ground terminal                                                                                                             |

| /                                  | Frame or chassis ground terminal                                                                                                             |

|                                    | Terminal is at earth potential                                                                                                               |

| $\stackrel{\triangle}{\downarrow}$ | Equipotentiality                                                                                                                             |

| N                                  | Neutral conductor on permanently installed equipment                                                                                         |

| L                                  | Line conductor on permanently installed equipment                                                                                            |

|                                    | On (mains supply)                                                                                                                            |

| <u>Ф</u>                           | Off (mains supply)                                                                                                                           |

| <b>山</b>                           | Standby (mains supply). The instrument is not completely disconnected from the mains supply when the power switch is in the standby position |

|                                    | In position of a bi-stable push switch                                                                                                       |

| Symbol      | Description                                                                      |

|-------------|----------------------------------------------------------------------------------|

|             | Out position of a bi-stable push switch                                          |

|             | Equipment protected throughout by DOUBLE INSULATION or REINFORCED INSULATION     |

| $\triangle$ | Caution, refer to accompanying documentation                                     |

|             | Caution, risk of electric shock                                                  |

| 4           | Do not apply around or remove from<br>HAZARDOUS LIVE conductors                  |

| 4           | Application around and removal from<br>HAZARDOUS LIVE conductors is<br>permitted |

| <u></u>     | Caution, hot surface                                                             |

|             | lonizing radiation                                                               |

| CAT I       | IEC Measurement Category I                                                       |

| CAT II      | Measurement Category II                                                          |

| CAT III     | Measurement Category III                                                         |

| CAT IV      | Measurement Category IV                                                          |

## Compliance and Environmental Information

Table 2 Compliance and Environmental Information

| Safety Symbol | Description                                                                                                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>③</b> ∘    | $\ensuremath{CSA}$ is the Canadian certification mark to demonstrate compliance with the Safety requirements.                                                                                                            |

|               | The C-tick mark is a registered trademark of the Spectrum Management Agency of Australia. This signifies compliance with the Australia EMC Framework regulations under the terms of the Radio Communication Act of 1992. |

| CE            | CE compliance marking to the EU Safety and EMC Directives. ISM GRP-1A classification according to the international EMC standard. ICES/NMB-001 compliance marking to the Canadian EMC standard.                          |

### DDR/LPDDR Post Process Compliance-At a Glance

The DDR/LPDDR Post Process Compliance Tool evaluates the captured DDR/LPDDR data against a set of user-defined limits to help you validate that a memory system is operating properly. The bus types supported by this tool are:

- DDR1/2/3/4/5

- LPDDR1/2/3/4/4x/5

The automated test application guides you through the process of selecting and configuring tests, running tests, and evaluating the test results.

The application assumes that the Keysight logic analysis system has already been set up to properly capture DDR data.

To use the automated test application, see:

- · Chapter 2, "Starting the DDR/LPDDR Post Process Compliance Tool" on page 15

- · Chapter 4, "Setting Up the Test Environment" on page 19

- · Chapter 3, "Configuring Tests Limits" on page 27

- · Chapter 5, "Selecting Tests" on page 45

- · Chapter 6, "Running Tests" on page 55

- · Chapter 7, "Automating the Tests" on page 59

- · Chapter 8, "Viewing Results" on page 63

- Chapter 9"Viewing/Exporting/Printing the Report" on page 67

- Chapter 10 "Saving Test Projects" on page 73

- · Chapter 11, "Creating or Opening a Test Project" on page 75

## Contents

|   | Safety Summary 3  Compliance and Environmental Information 6  DDR/LPDDR Post Process Compliance—At a Glance 7                                                                                                                                    |  |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1 | About the Tool                                                                                                                                                                                                                                   |  |  |  |

| 2 | Starting the DDR/LPDDR Post Process Compliance Tool                                                                                                                                                                                              |  |  |  |

|   | To Toggle between the Toolbar 17                                                                                                                                                                                                                 |  |  |  |

| 3 | Setting Up the Test Environment                                                                                                                                                                                                                  |  |  |  |

|   | Configuring Trigger(s) to Acquire Data Relevant for Compliance Tests  How the Trigger Feature Works 22  Types of Available Triggers 22  To configure trigger(s) in the Post Process Compliance tool 22  To preview a trigger specification 24    |  |  |  |

| 4 | Configuring Tests Limits                                                                                                                                                                                                                         |  |  |  |

|   | Using the Default Limit Set and Manually Overriding the Default Value of a Test Limit 28                                                                                                                                                         |  |  |  |

|   | Using a Custom Limits File 30                                                                                                                                                                                                                    |  |  |  |

|   | Setting Tests Limits Automatically as per your System's Characteristics 31                                                                                                                                                                       |  |  |  |

|   | Customizing the Compliance Setup to Handle Multiple System Clock Speeds 36  Overview of Multiple Clock Speeds Support 36  To Customize the Setup for Multiple Clock Speeds 36  LPDDR5 Multiple Clock Speeds - XML File Structure and Elements 39 |  |  |  |

|   | To set the test limits (for information on how to calculate the limits) 42                                                                                                                                                                       |  |  |  |

| 5 | Selecting Tests                                                                                                                                                                                                                                  |  |  |  |

|   | Tests Available With B4661A License (based on Memory type) 46                                                                                                                                                                                    |  |  |  |

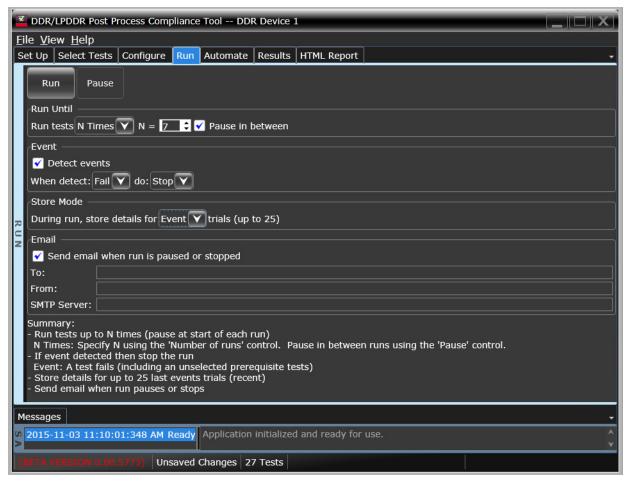

| 6 | Running Tests                                                                                                                                                                                                                                    |  |  |  |

|   | To set the display preferences 58                                                                                                                                                                                                                |  |  |  |

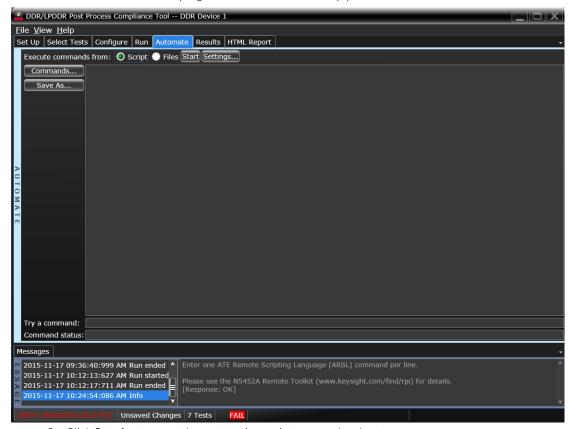

### 7 Automating the Tests

Prerequisites 59

Automation by Scripts 60

Automation by Files 61

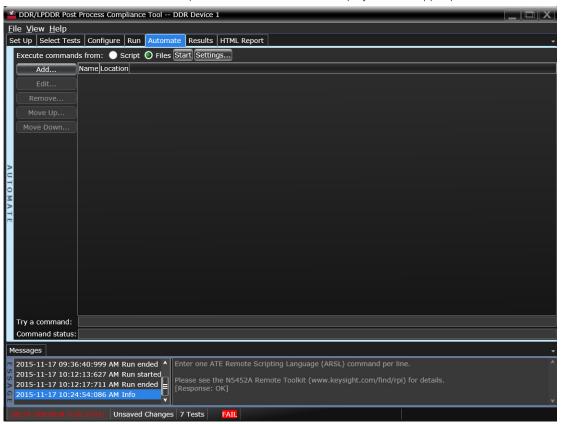

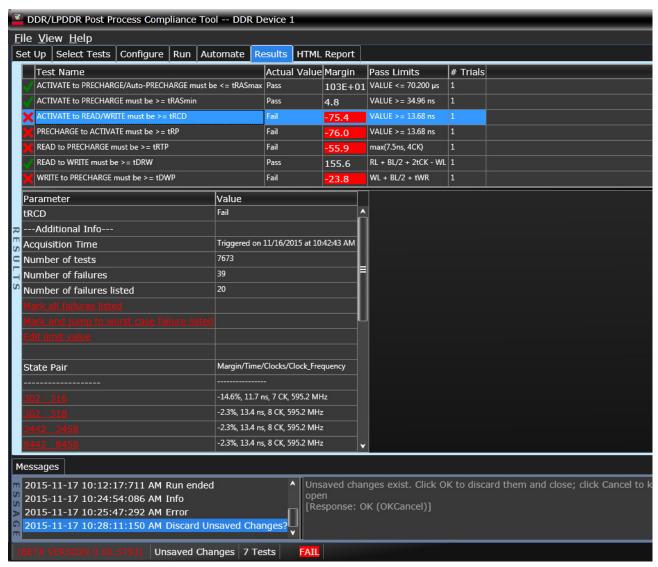

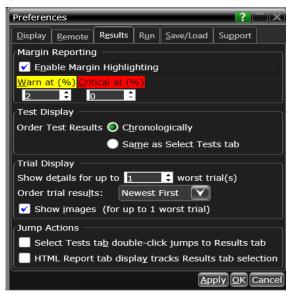

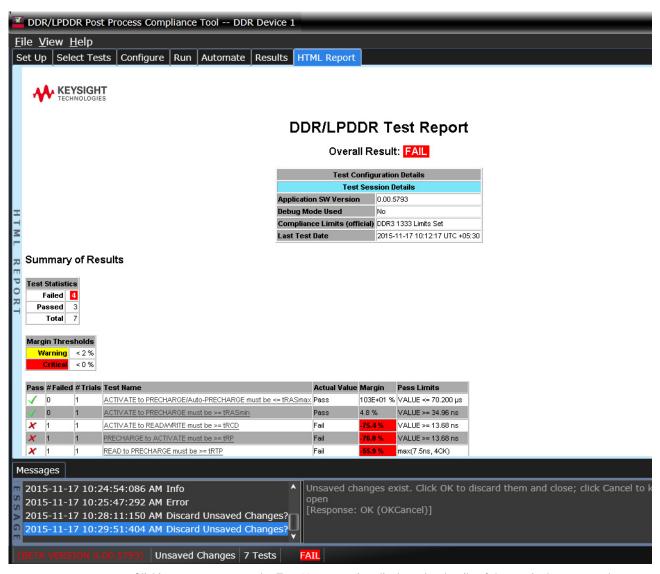

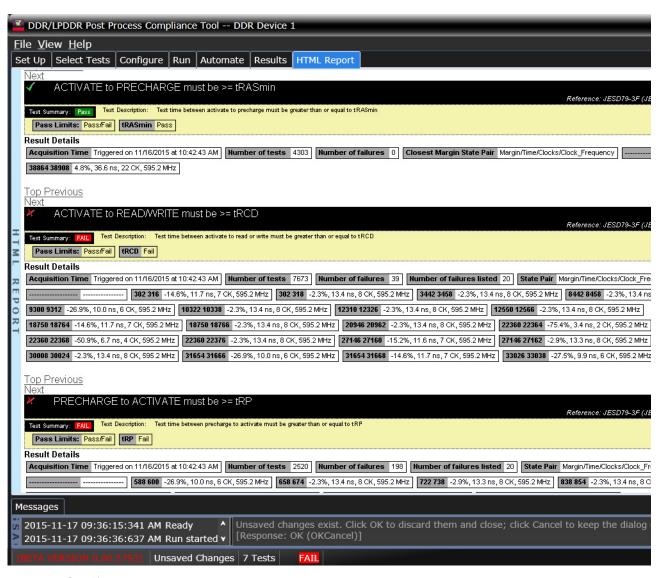

### 8 Viewing Results

To change margin thresholds 65

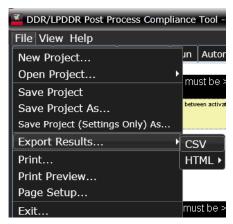

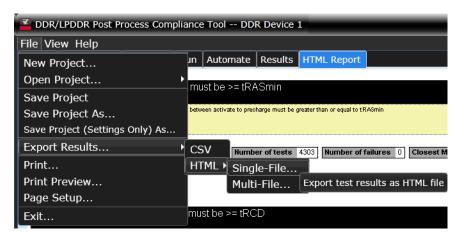

## 9 Viewing/Exporting/Printing the Report

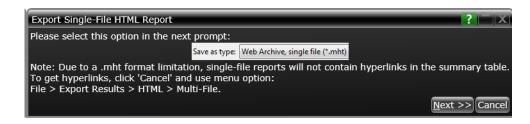

**To export the report** 69 **To print the report** 71

## 10 Saving Test Projects

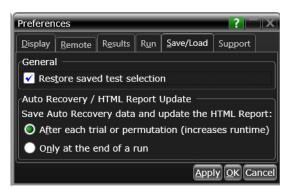

To set AutoRecovery preferences 74

## 11 Creating or Opening a Test Project

To set load preferences 76

Index

## 1 About the Tool

## Overview of the tests

There are two types of tests:

- Tests which check for timing violations

- · Tests which check for illegal DDR state transitions

The test limits can be (and must be) configured by the user.

The provided timing violation tests include:

| Parameter           | Description                                          | Test              |

|---------------------|------------------------------------------------------|-------------------|

| tRAS <sub>max</sub> | Row Active time ACTIVATE to PRECHARGE/Auto-PRECHARGE | must be < tRASmax |

| tRAS <sub>min</sub> | Row Active time ACTIVATE to PRECHARGE/Auto-PRECHARGE | must be > tRASmin |

| tRP                 | PRECHARGE to any other command (same bank)           | must be > tRP     |

| tCCD                | Time between any read or write command               | must be > tCCD    |

| tRRD                | ACTIVATE to ACTIVATE (any bank)                      | must be >= tRRD   |

| tFAW                | Time for four ACTIVATEs (any bank)                   | must be >= tFAW   |

| tRFC                | REFRESH to REFRESH or ACTIVATE                       | must be > tRFC    |

| tDARW               | ACTIVATE to external READ/WRITE                      | must be > tDARW   |

| tDRP                | Read to Precharge/AutoPrecharge                      | must be > tDRP    |

| tDRW                | Read to Write                                        | must be > tDRW    |

| tDWP                | Write to Precharge/AutoPrecharge                     | must be > tDWP    |

| tDWR                | Write to Read                                        | must be > tDWR    |

| Description                      |

|----------------------------------|

| READ or WRITE to an inactive row |

| REFRESH to an active bank        |

| ACTIVATE to an active bank       |

### Compatibility

The DDR/LPDDR Post Process Compliance Tool works for most DDR, DDR2, DDR3, DDR4, DDR5, LPDDR, LPDDR2, LPDDR3, LPDDR4, LPDDR4x, and LPDDR5 systems.

The tool is not able to fully model systems which use the following optional DDR features:

- · Partial Array Self-Refresh (PASR)

- · Auto Self-Refresh (ASR)

- · On-the-fly Burst Length switching

About the software

The Post Process Compliance Tool is part of the Keysight B4661A DDR/LPDDR Toolset package. This tool requires that you install the Logic and Protocol Analyzer software version 6.2 or higher. Versions prior to 6.2 do not support this tool.

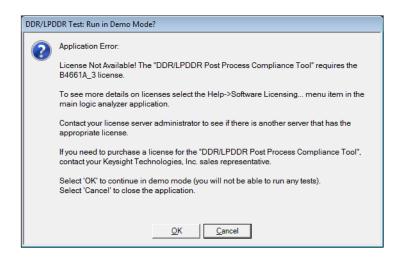

Software License

The DDR/LPDDR Post Process Compliance Tool requires B4661A\_3 license to operate. If this license is not installed in your system, the following license error dialog box is displayed while launching the DDR/LPDDR Post Process Compliance Tool application. Additionally, you need the B4661A\_5 license for DDR5 compliance validation and the B4661A\_6 license for LPDDR5 compliance validation.

When you are launching the DDR/LPDDR Post Process Compliance Tool for the first time, the Keysight Technologies Software End User License Agreement dialog box appears. You can read the agreement and choose to agree or disagree before proceeding further to use the DDR/LPDDR Post Process Compliance Tool.

1 About the Tool

# 2 Starting the DDR/LPDDR Post Process Compliance Tool

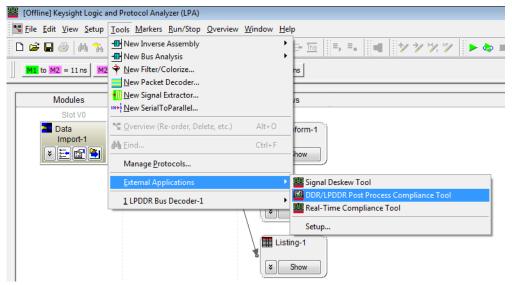

1 From the logic analysis system's main menu, choose **Tools > External Applications > DDR/LPDDR Post Process Compliance Tool**.

The DDR/LPDDR Post Process Compliance Tool window appears.

See Also · "To Toggle between the Toolbar" on page 17

Next · "Creating or Opening a Test Project" on page 75

### To Toggle between the Toolbar

To toggle between the toolbars, you can click and drag the toolbars accordingly. To keep the default display for the toolbars, select **View>Preferences>Tab Layout** from the menu.

2 Starting the DDR/LPDDR Post Process Compliance Tool

# 3 Setting Up the Test Environment

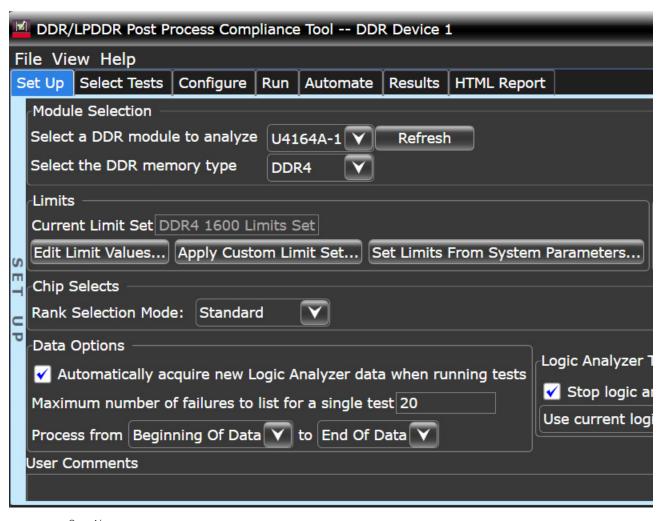

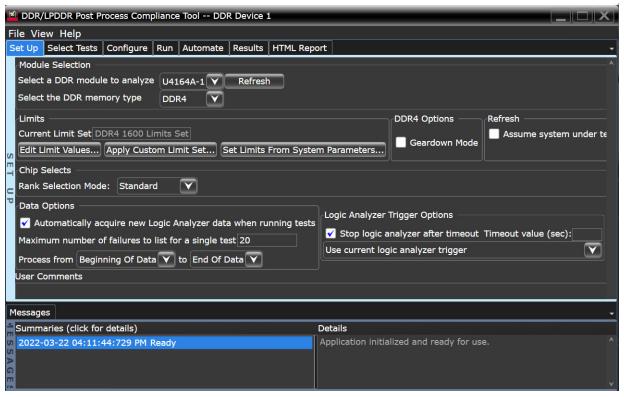

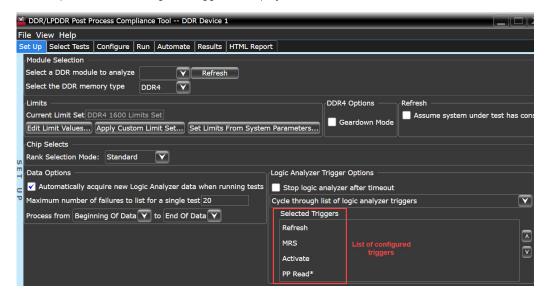

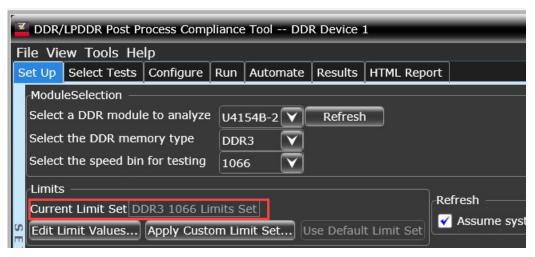

- 1 Click the **Set Up** tab.

- 2 If more than one DDR bus decoder exists in the logic analysis system setup, select which one to use for the compliance tests from the **Select a DDR module to analyze** listbox.

- If only one decoder exists, it will be selected automatically.

- If needed, click **Refresh** to update the list. You may need to refresh the list and select a new decoder if you load a new logic analyzer configuration file, or whenever you add or remove a decoder

- 3 Select the DDR memory type. The DDR/LPDDR Post Process Compliance Tool can work with any of the following memory bus standards.

- DDR1/2/3 /4/5

- LPDDR1/2/3/4/4x/5

- 4 Use the options available in the **Limits** section to edit or automatically set the values of the limits associated to the compliance tests. The Post Process Compliance tool will then use these new values to perform compliance testing and to arrive at pass/fail and/or margin information for each test. Refer to the chapter "Configuring Tests Limits" on page 27 to know about these options in detail.

5 From the Chip Selects section, select the checkboxes for the chip selects that are being used for the SDRAM. For the post process compliance testing to be correct, make sure that the chip selects that are being used in the system must be enabled and unused chip selects must not be enabled.

If you select **DDR4** or **DDR5** from the **Memory Type** listbox, the **DDR4 Rank Selection Mode** listbox is also displayed in the **Chip Selects** section. You use this listbox to select the appropriate rank addressing mode option based on the rank addressing being used for your DDR4/DDR5 RDIMM device.

In the Standard DDR4/DDR5 rank addressing, there is one CS# (chip select) line for each rank. In the 3DS rank addressing, there is only one CS# line for all the ranks. Therefore, the logical value of the C (Chip ID) bits is used to identify the rank being addressed in the decode. The number of Chip ID bits to be used for rank identification is as per the 3DS specifications.

From the available 3DS rank addressing options (2-high, 4-high, or 8-high), select the appropriate option based on whether your 3DS device has two, four, or eight logical ranks.

Based on the rank addressing mode that you select, the appropriate number of chip selects are displayed and enabled in the **Chip Selects** section. For instance, if you select the Quad CS rank addressing mode, four chip selects are displayed by default.

The tests displayed in the **Select Tests** tab vary based on the rank addressing mode that you select in this section. For instance, the tests for same or different logical ranks are displayed if you select one of the 3DS rank addressing mode.

- From the **Data Options** section, select whether or not you want the tool to automatically acquire new data when compliance tests are run. Whether you plan to run tests once or multiple times, the selection of this checkbox instructs the tool to first run the logic analyzer for data acquisition. When the data acquisition run is complete, the tool starts post processing the newly acquired data by running the selected tests. If you plan to run the tests multiple times or forever, then you must select this checkbox to ensure that the tool runs the logic analyzer repetitively for data acquisition and then acquires the new data automatically for post processing.

- Deselecting this checkbox instructs the tool to use the already acquired data for post processing. The tool does not run the logic analyzer for data acquisition in this case. Therefore, when you deselect this checkbox, you can run the tests only once on existing data.

- 7 From the Logic Analyzer Trigger Options section, configure one or more triggers so that Logic Analyzer can acquire relevant traces with event(s) of interest for running compliance tests. See "Configuring Trigger(s) to Acquire Data Relevant for Compliance Tests to know more. This section is displayed only when you select the Automatically acquire new logic analyzer data when running tests checkbox and set the memory type to DDR4, DDR5, or LPDDR5.

- 8 (optional) Describe the test for future reference. The specified **User Comments** will appear on the HTML report which is generated for the test.

Next · "Selecting Tests" on page 45

#### Configuring Trigger(s) to Acquire Data Relevant for Compliance Tests

By default, the Post Process Compliance tool processes the already acquired data in the current logic analyzer trace and runs compliance tests on this data. However, to improve the effectiveness and coverage of your compliance testing, you may want the logic analyzer to capture the event(s) of interest for your specific compliance testing scenario and the tests to be run on multiple relevant traces offering a wider coverage. The Post Process Compliance tool allows you to configure trigger(s) for data acquisition so that the logic analyzer captures the event(s) that are required for the intended compliance tests coverage and then run tests on this relevant data.

The triggers configured in the Post Process Compliance tool provides an additional benefit of acquiring multiple relevant traces for running compliance tests. Instead of running compliance tests on the data acquired using a single logic analyzer trigger definition, you can set a sequence of triggers and acquire a different trace using each of these triggers.

The trigger feature also removes complexity from the task of setting triggers by providing a set of predefined triggers that you would find useful specifically for compliance testing scenarios.

NOTE

The tool's trigger feature is available only for DDR4, DDR5, and LPDDR5 memory types. Therefore, if you select a memory type other than these in the Set Up tab, then the trigger options are not displayed.

As the trigger feature is only applicable for data acquisition when running compliance tests, therefore the trigger options are available only when you select the **Automatically acquire new logic analyzer data when running tests** checkbox.

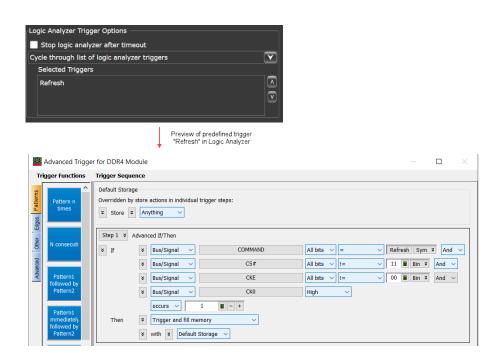

An example of a list of configured triggers is displayed in the screen below.

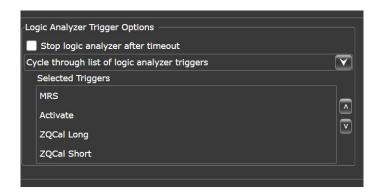

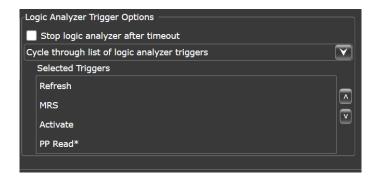

### How the Trigger Feature Works

- 1 The tool runs the logic analyzer to capture data using the first trigger configured in the triggers list. When the trigger event occurs, the data acquisition starts. The tool then runs the selected compliance tests on the captured trace.

- 2 The tool runs the logic analyzer to capture data using the next trigger configured in the list. When the trigger event occurs, the data acquisition starts. The tool then runs the selected compliance tests on the newly captured trace.

- 3 This cycle continues until all triggers configured in the list are sequentially used to capture traces and run tests.

The following screen displays a trigger sequence with four predefined triggers configured to acquire traces for running post process compliance tests.

NOTE

To avoid the situation where the logic analyzer keeps running while waiting for the configured trigger event to occur, select the Stop logic analyzer after timeout checkbox and specify the timeout. After the timeout, the logic analyzer stops and the tool runs the logic analyzer with the next trigger in the sequence.

### Types of Available Triggers

The following three options are available when configuring triggers in the Post Process Compliance tool.

- Use the trigger definition currently set in the Logic Analyzer's Trigger Setup dialog.

- · Use the predefined triggers available in the tool.

- · Create custom trigger(s) using the tool.

These are described in the steps below.

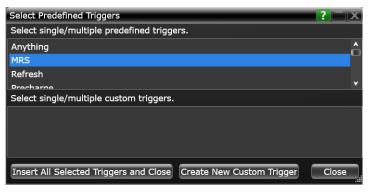

To configure trigger(s) in the Post Process Compliance tool

- 1 Click the **Set Up** tab in the Post Process Compliance tool.

- 2 Select the DDR memory type (DDR4, DDR5, or LPDDR5).

- 3 From the Data Options section, select the Automatically acquire new logic analyzer data when running tests checkbox.

- 4 The **Logic Analyzer Trigger Options** section is displayed. Click the drop-down listbox arrow available in this section.

- 5 If you want to use the currently set logic analyzer trigger for data acquisition, then select the **Use** current logic analyzer trigger option.

- 6 If you want to define one or more triggers specifically for data acquisition relevant for compliance testing, select the Cycle through list of logic analyzer triggers option and perform the following steps.

- a Click the icon to add one or more triggers to the list.

The **Select Predefined Triggers** dialog box is displayed. In this dialog box, you can choose one or more predefined triggers, create your own custom triggers, or choose a combination of predefined as well as custom triggers for your list. Predefined triggers may vary based on the selected memory type.

- b To add predefined trigger(s), select one or more triggers from the Select single/multiple predefined triggers list.

- To add a custom trigger, click the **Create New Custom Trigger** button and specify trigger details in the **Enter Custom Trigger Detail** dialog.

- d Specify a name in the **Name of new trigger** field. The custom trigger appears with this name in the Triggers list.

- e In this custom trigger, you can either store the currently set logic analyzer trigger specifications or load the trigger specifications from an XML format trigger specifications file.

- f Click OK

- g Once you have added the required predefined/custom triggers, click the Insert All Selected Triggers and Close button.

All selected triggers are then displayed in the **Selected triggers** listbox in the same sequence in which you added these.

NOTE

The tool appends an \* with a trigger name to indicate that it is a custom trigger.

### To preview a trigger specification

For any predefined or custom trigger added to the list, you can preview how the trigger would translate to the trigger definition to be used in logic analyzer.

As the tool needs to communicate with the Logic Analyzer software, ensure that the Logic Analyzer software GUI is currently open.

- 1 Select the trigger from the **Selected Triggers** list.

- 2 Click the icon displayed with the trigger.

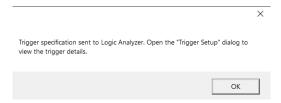

The tool sends the trigger's specification to the Logic Analyzer and notifies on the status. An error message is displayed if the tool is not able to communicate with the Logic Analyzer software or the logic analyzer measurement setup is not appropriate for the trigger. For instance, the required bus/signals are not set in the Bus/Signals Setup.

The following is an example of a predefined trigger uploaded to Logic Analyzer for preview.

3 Setting Up the Test Environment

# 4 Configuring Tests Limits

Using the Default Limit Set and Manually Overriding the Default Value of a Test Limit  $\,/\,\,28\,$  Using a Custom Limits File  $\,/\,\,30\,$

Setting Tests Limits Automatically as per your System's Characteristics / 31 Customizing the Compliance Setup to Handle Multiple System Clock Speeds / 36 To set the test limits (for information on how to calculate the limits) / 42

While setting up the test environment, you must ensure that the tests limits are as per your specific requirements such as bus speed and bus type. You can do this using various options available in the **Limits** section in the **Set Up** tab.

Each compliance test has a specification parameter (limit) associated with it. The default value of each specification parameter is already set in the Post Process Compliance tool. If required, you can override this default value and set a new value suitable to your specific requirements such as the memory part you are using and certain characteristics of the memory bus. The Post Process Compliance tool will then use these new values to perform compliance testing and to arrive at pass/fail and/or margin information for each test.

You can set the tests limits in the following ways:

| Method                                                                                                                                                                                                                                                                                                                                                                                                                           | Available for                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Use the default limit set and then manually override the default value of individual test limit(s).                                                                                                                                                                                                                                                                                                                              | All test groups                    |

| See "Using the Default Limit Set and Manually Overriding the Default Value of a Test Limit" on page 28.                                                                                                                                                                                                                                                                                                                          |                                    |

| Use a custom limit set (.lim) file to change the value of test limits in a test group to the values appropriate for a particular bus speed. A number of predefined limit files are installed with the Post Process Compliance tool for the most common bus speeds for all DDR bus types. These files are installed at:  C:\Program Files\Keysight Technologies\Logic Analyzer\ExternalApps\DDRApps\ DDRComplianceTool\app\limits | All test groups                    |

| Applying a custom limit file quickly changes all limit values to match the values applicable for a particular bus speed.  See "Using a Custom Limits File" on page 30.                                                                                                                                                                                                                                                           |                                    |

| Set tests limits automatically based on the specific characteristics that you specified for your system.                                                                                                                                                                                                                                                                                                                         | DDR4, DDR5, and LPDDR5 test groups |

| See "Setting Tests Limits Automatically as per your System's Characteristics" on page 31.                                                                                                                                                                                                                                                                                                                                        |                                    |

| Customize tests limits automatically as per the set of bus settings that you specified for each clock speed.                                                                                                                                                                                                                                                                                                                     | LPDDR5 test group                  |

| See "Customizing the Compliance Setup to Handle Multiple System Clock Speeds" on page 36.                                                                                                                                                                                                                                                                                                                                        |                                    |

These methods are described in this chapter.

### Using the Default Limit Set and Manually Overriding the Default Value of a Test Limit

When you select the logic analyzer module and DDR memory type in the Set Up tab, the default limit set applicable to these selections is automatically loaded and displayed as the **Current Limit Set** in the **Limits** section.

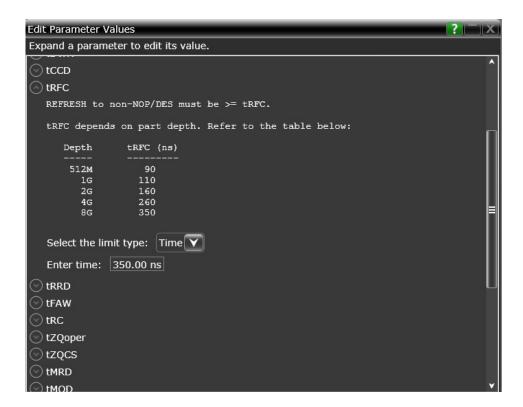

If you want to change the value of a test limit from this default limit set, perform the following steps:

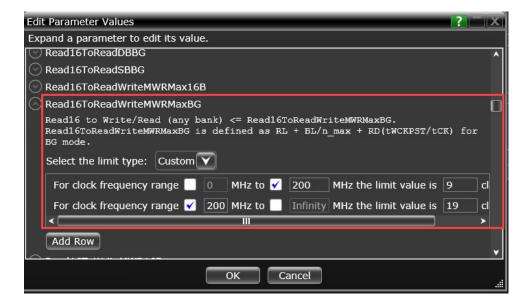

- 1 In the **Set Up** tab, click **Edit Limit Values....**.

- 2 The **Edit Parameter Values** dialog box is displayed with the list of all test limits applicable for the test group. Click the down-arrow button displayed with a test limit to view its current value, get more information about it, and view options to modify its value.

- 3 Click **OK** when you have completed making changes to test limits.

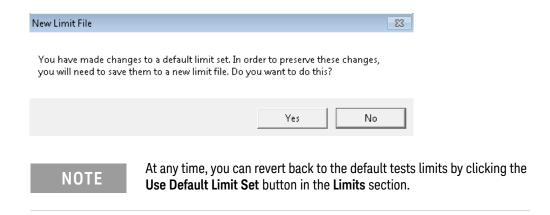

- 4 To preserve and use these changed tests limits, you need to save these values in a new limit set. This also ensures that the default limit set remains intact with the default values. To save, click **Yes** in the displayed message box and then specify the path and name for a new limits file.

See Also "To set the test limits (for information on how to calculate the limits)" on page 42 (for information on how to calculate the limits)

### Using a Custom Limits File

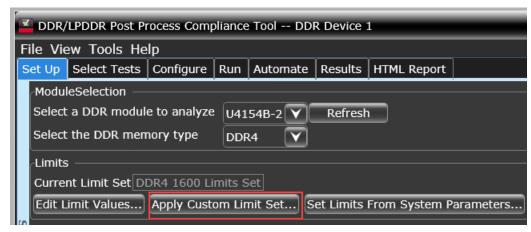

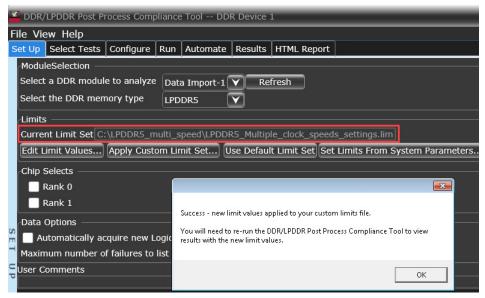

1 Click the **Apply Custom Limit Set...** button displayed in the **Limits** section of the **Set Up** tab.

The **Open** dialog box is displayed.

- 2 Select the customized limits (.lim) file that you want to use and click **Open**.

- 3 Click **OK** to acknowledge the success message.

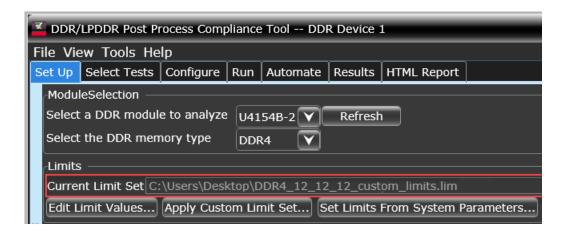

The custom limits file is then displayed as the Current Limit Set. All the tests limits are automatically changed to match the values in the custom limits file.

### Setting Tests Limits Automatically as per your System's Characteristics

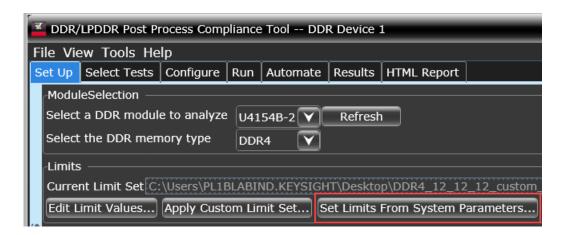

1 Click the **Set Limits From System Parameters...** button displayed in the **Limits** section of the **Set Up** tab.

NOTE

The **Set Limits From System Parameters...** button is displayed only for a DDR4, DDR5, or LPDDR5 memory type.

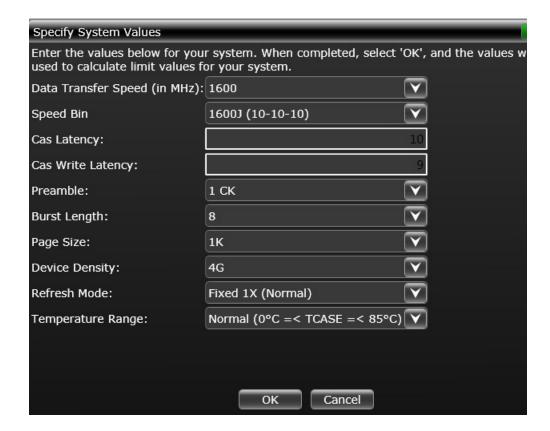

The **Specify System Values** dialog box is displayed.

2 Specify the values matching your system's characteristics and then click **OK**. All the tests limits are then automatically modified as per the system values that you specified in the Specify System Values dialog box.

NOTE

For an LPDDR5 bus, you can select whether the bus runs on a single clock speed or at multiple clock speeds in the Specify System Values dialog box.

For the multiple clock speeds scenario, you need to specify the relevant bus settings at each possible clock speed for your DUT. This allows the Post Process Compliance tool to automatically calculate correct test limits from the changing bus settings when the system clock speed changes. As a result, the tool can generate the compliance results accurately for systems running at multiple clock speeds.

Refer to the topic "Customizing the Compliance Setup to Handle Multiple System Clock Speeds" on page 36 to know more.

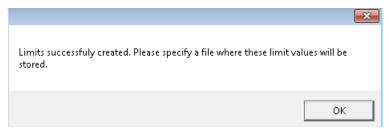

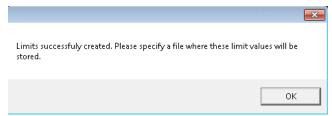

3 To allow the tool to use these changed limits, save these changed limits in a limits (.lim) file by clicking **OK** on the displayed message box and proceeding with saving the limits file.

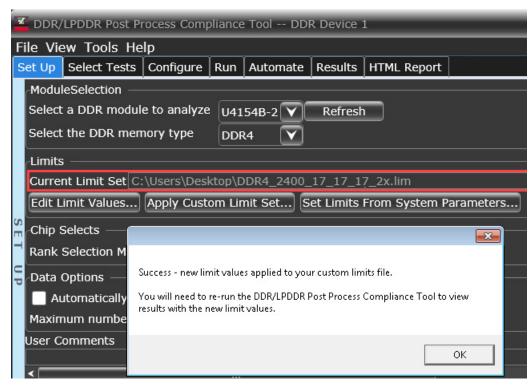

4 The saved limits file is then displayed as the Current Limit Set. Click OK to acknowledge the success message.

You can view the changed tests limits in the Edit Parameters Values dialog which can be accessed by clicking the Edit Limit Values button.

NOTE

A test limit value may at times differ slightly from the specifications. This is because the limit value is truncated to a number evenly divisible by 80ps to match the logic analyzer time tagger that works in 80ps ticks. In the example given below, the value of the tRCD limit is set to 12.48ns instead of the 12.5ns in the specifications, because 12.485ns is evenly divisible by 80ps.

### Example of setting tests limits automatically based on system characteristics

The following is an example of how the **tRCD** limit value is changed automatically based on the user-specified system characteristics.

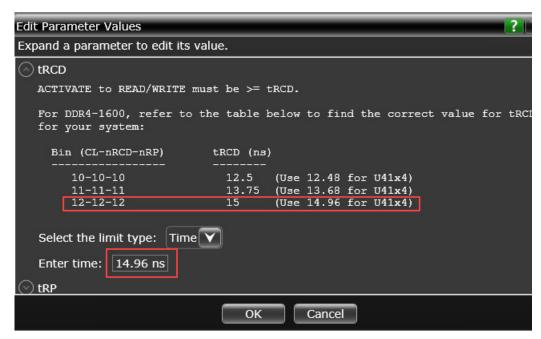

In screen 1, the default value of the tRCD parameter is set to 14.96 ns (1600L 12-12-12 speed bin).

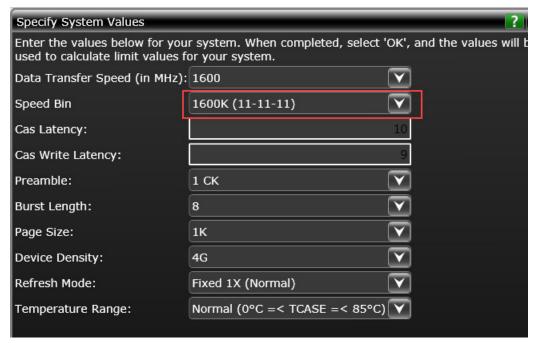

In screen 2, the Speed Bin system value is changed to **1600K 11-11-11** to match the system characteristics.

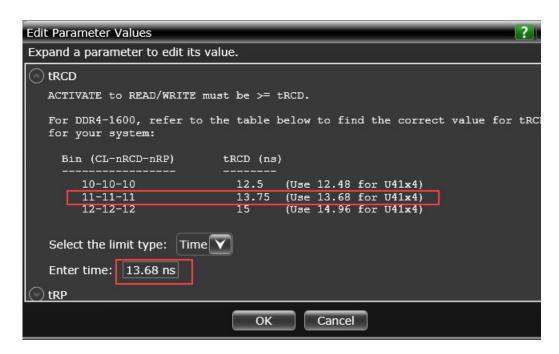

In screen 3, the value of the tRCD parameter is automatically changed to **13.68 ns** (1600K 11-11-11 speed bin) to match the changed Speed Bin system characteristic.

Screen 1 showing the default value of the tRCD parameter

Screen 2 showing the Speed Bin system value changed to 11-11-11

Screen 3 showing the changed tRCD limit value to match the changed speed bin system value

See Also

• "To set the test limits (for information on how to calculate the limits)" on page 42 (for information on how to calculate the limits)

### Customizing the Compliance Setup to Handle Multiple System Clock Speeds

The Post Process Compliance tool can perform compliance testing for systems running at:

- · a single (fixed) clock speed.

- · multiple clock speeds.

You can customize the compliance setup in the Post Process Compliance tool to indicate whether your LPPDDR5 bus is running at a single clock speed or at multiple clock speeds. This topic describes how to configure the setup to handle multiple clock speeds.

### Overview of Multiple Clock Speeds Support

For an LPDDR5 bus running at multiple clock speeds, the change in the system clock speed results in the change in the LPDDR5 bus setting(s). These bus settings usually impact the test limit(s) that the Post Process Compliance tool uses to arrive at pass/fail/margin information for each test. To ensure that the tool calculates correct test limits and generates accurate compliance results for systems changing clock speeds, you need to provide a set of bus settings applicable for each possible clock speed for your DUT. You specify these multiple sets of bus settings in an XML input file described later in this chapter. The format for this file should be as per the format provided in the topic "LPDDR5 Multiple Clock Speeds - XML File Structure and Elements" on page 39. You may also refer to an example of this XML file included in this topic.

To Customize the Setup for Multiple Clock Speeds

- 1 Select LPDDR5 from the Select the DDR Memory Type listbox in the Set Up tab.

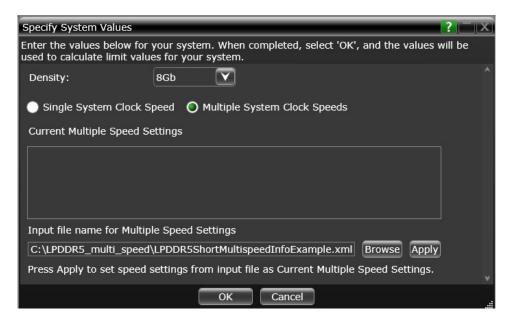

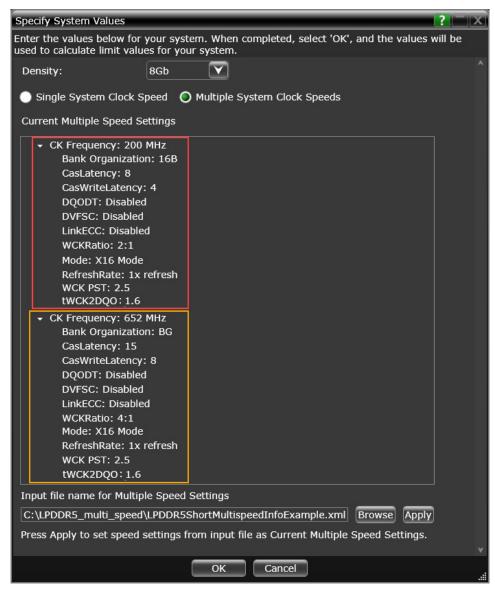

- 2 Click the **Set Limits From System Parameters...** button displayed in the **Limits** section of the **Set Up** tab. The **Specify System Values** dialog box is displayed.

- 3 Select the **Density** of your system.

- 4 Select the **Multiple System Clock Speeds** radio button.

- On selecting this radio button, the **Input file name for Multiple Speed Settings** field is displayed. Click the **Browse** button displayed with this field to browse and select the XML input file in which you have defined the bus settings for each possible clock speed of your DUT.

6 Click **Apply** to load the system values from the newly selected XML input file.

On clicking Apply, the bus settings for each possible clock speed of your DUT included in the XML input file are loaded from this file and displayed in the Current Multiple Speed Settings section. An example of these settings loaded from the XML input file is shown below.

- 7 Click **OK** to confirm the selections and close the **Specify System Values** dialog box.

- 8 The Post Process Compliance tool uses these bus settings to create test limits and displays the following message indicating the successful creation of test limits for different clock speeds. Click **OK** to proceed with saving these newly created test limits in a limits (.lim) file.

9 The saved limits file is then displayed as the **Current Limit Set**. Click **OK** to acknowledge the following success message.

10 If you want to view the new test limit values created for multiple clock speeds, click the Edit Limit Values... button.

11 Finally, re-run the tests with the new limit values so that test limits as per the changing system clock speeds are used to arrive at test results.

When the clock speed change is encountered, the Post Process Compliance tool automatically uses the test limits created for that clock speed in the limits file and computes compliance results using these settings.

LPDDR5 Multiple Clock Speeds - XML File Structure and Elements

You can create/edit this XML file using any text editor. This topic describes the format and hierarchy of the XML elements to be followed for this XML file.

#### XML Elements Hierarchy

The XML elements shown below are for a set of bus settings to be used for a particular clock speed. Depending on the clock speeds possible for your DUT, you can replicate this set with different settings in the XML file.

#### XML Elements Description

These XML elements are described in the table below.

| XML Element                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Attributes                                                                                                                                               |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| <systemclockspeeds></systemclockspeeds> | The multiple clock speeds settings XML file begins with the<br><systemclockspeeds> element.  This element allows you to define one or more sets of bus settings for system's clock speeds.</systemclockspeeds>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                        |

| <systemclockspeed></systemclockspeed>   | Contains the set of following bus settings to be applied for the clock speed that you specified in the <i>Value</i> attribute.  - <bankorganization> - Possible values are 8B, 16B, BG  - <caslatency> - <caswritelatency> - <dqodt> - Possible values are Disabled or Enabled <dvfsc> - Possible values are Disabled or Enabled <linkecc> - Possible values are Disabled or Enabled <linkecc> - Possible values are Disabled or Enabled <wckratio> - Possible values are 2:1, 4:1 <density> - Possible values are 2Gb, 3Gb, 4Gb, 6Gb, 8Gb, 12Gb, 16Gb, 24Gb, 32Gb <mode> - Possible values are X8 Mode, X16 Mode <refreshrate> - Possible values are Ref8x, Ref6x, Ref4x, Ref3_3x, Ref2_5x, Ref2_0x, Ref1_7x, Ref1_3x, Ref1x, Ref0_75x, Ref0_25x, Ref0_25xD, Ref0_125xD, Ref0_125xD <wckpst> - Possible values are 2.5, 4.5, 6.5 <rdqspst> - Possible values are 0.5, 2.5, 4.5 <twck2dqo> - Maximum value of tWCK2DQO in ns <wckfreerunningmode> - Possible values are Disabled or Enabled.</wckfreerunningmode></twck2dqo></rdqspst></wckpst></refreshrate></mode></density></wckratio></linkecc></linkecc></dvfsc></dqodt></caswritelatency></caslatency></bankorganization> | Value - A String representing the clock speed for which the set of bus settings is applicable. Example <systemclockspeed value="200"></systemclockspeed> |

#### XML File Example

This topic includes an example of the XML input file created in the required format to decode as per the multiple clock speeds of the DUT.

```

<SystemClockSpeeds>

<SystemClockSpeed Value="200">

<!-- 8B, 16B, BG -->

<BankOrganization>16B</BankOrganization>

<CasLatency>8</CasLatency>

<CasWriteLatency>4</CasWriteLatency>

<!-- Disabled, Enabled -->

<DQODT>Disabled</DQODT>

<!-- Disabled, Enabled -->

<DVFSC>Disabled</DVFSC>

<!-- Disabled, Enabled -->

<LinkECC>Disabled</LinkECC>

<!-- 2:1, 4:1 -->

<WCKRatio>2:1</WCKRatio>

<!--X8 Mode, X16 Mode -->

<Mode>X16 Mode</Mode>

<!-- Ref8x, Ref6x, Ref4x, Ref3_3x, Ref2_5x, Ref2_0x,

Ref1_7x, Ref1_3x, Ref1x, Ref0_75x, Ref0_5x, Ref0_25x,

Ref0 25xD, Ref0 125x, Ref0 125xD -->

```

```

<RefreshRate>Ref1x</RefreshRate>

<!-- 2.5, 4.5, 6.5 -->

<WCKPST>2.5</WCKPST>

<!-- 0.5, 2.5, 4.5 -->

<RDQSPST>0.5</RDQSPST>

<!-- tWCK2DQO max value in ns -->

<tWCK2DQO>1.6 </tWCK2DQO>

<!-- Disabled, Enabled -->

<WCKFreeRunningMode>Disabled</WCKFreeRunningMode>

</SystemClockSpeed>

<SystemClockSpeed Value="652">

<BankOrganization>BG</BankOrganization>

<CasLatency>15</CasLatency>

<CasWriteLatency>8</CasWriteLatency>

<DQODT>Disabled</DQODT>

<DVFSC>Disabled</DVFSC>

<LinkECC>Disabled</LinkECC>

<WCKRatio>4:1</WCKRatio>

<Mode>X16 Mode</Mode>

<RefreshRate>Ref1x</RefreshRate>

<WCKPST>2.5</WCKPST>

<RDQSPST>0.5</RDQSPST>

<tWCK2DQO>1.6</tWCK2DQO>

<WCKFreeRunningMode>Disabled</WCKFreeRunningMode>

</SystemClockSpeed>

</SystemClockSpeeds>

```

#### To set the test limits (for information on how to calculate the limits)

All timing violation tests are based on compliance limits that are specified by the user. Specify these limits based on the specific DDR memory parts you are using. Limits will vary depending on:

- Memory technology (DDR2, DDR3)

- · Speed grade

- Clock speed

- · Part density

- User selected options such as Additive Latency and burst length

#### Units

Some times must be entered in seconds (s). If the data sheet expresses these limits in terms of clock cycles, you will need to convert those limits to seconds.

Each logic analyzer sample has a timestamp. Results will be calculated by subtracting the time stamp of the first event from the timestamp of the second event. Note that the time stamps are only as good as the time stamp resolution of the logic analyzer card being used (this resolution may be as coarse as 2ns; see the Specifications and Characteristics in the logic analyzer's Online help for details). The elapsed time includes time during which the DDR clock is inactive.

Other times must be entered as a number of clock cycles (CK). Results will be calculated by counting the number of logic analyzer samples between the two events.

Additive latency (AL) is normally expressed as a number of clocks (CK). For some calculations, you will need to convert AL to seconds (s) by dividing by the clock rate.

Burst length (BL) is simply an integer (4 or 8).

### Definitions of the limits

You will need to look up some of the limits from the part data sheet. You will then calculate values for the derived limits.

Keysight suggests using the formulas here to compute the derived limits. However, it is entirely the responsibility of the user to choose limits that are appropriate for the intended application.

Here are the limits you need to specify:

| Parameter           | Description                                                       | Unit | Suggested Definition                                                                   | Reference                                 |

|---------------------|-------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|-------------------------------------------|

| tRAS <sub>max</sub> | Row Active time ACTIVE to<br>PRECHARGE                            | S    | Part dependent (9 * tREFI)                                                             | Data Sheet (tREFI). See<br>DDR3 page 147. |

| tRAS <sub>min</sub> | Row Active time ACTIVE to<br>PRECHARGE                            | S    | Part dependent                                                                         | Data Sheet                                |

| tDARW               | Min ACT to external READ/WRITE                                    | S    | tRCD-AL                                                                                | DDR2)3.5 / DDR3 12.3                      |

| tRP                 | Row Precharge time min PRECHARGE to any other command (same bank) | S    | Part dependent                                                                         | Data Sheet                                |

| tDRP                | Min Read to Precharge                                             | СК   | DDR2: AL + BL/2 + max (tRTP, 2CK)<br>-2CK<br>DDR3: AL + tRTP                           | DDR2 3.7.1 / DDR3 4.13.3                  |

| tDRW                | Min Read to Write                                                 | CK   | DDR2: BL/2 + 2CK<br>DDR3: BL4: RL + CCD/2 + 2CK - WL<br>DDR3: BL8: RL + CCD + 2CK - WL | DDR2 figure 35 / DDR3<br>figure 35, 36    |

| tRFC                | REFRESH command time. min time<br>REFRESH to REFRESH or ACTIVATE  | S    | Part dependent                                                                         | Data Sheet                                |

| tDWP                | Min Write to Precharge                                            | СК   | WL + BL/2 + tWR                                                                        | DDR2 (3.7.2 / DDR3 Figure<br>49, 50       |

| Parameter | Description                                                 | Unit | Suggested Definition                                | Reference                              |

|-----------|-------------------------------------------------------------|------|-----------------------------------------------------|----------------------------------------|

| tDWR      | Min Write to Read                                           | CK   | DDR2: CL -1 + BL/2 + tWTR<br>DDR3: WL + BL/2 + tWTR | DDR2 Figure 41 / DDR3<br>Figure 53, 56 |

| tCCD      | CAS to CAS delay min time between any read or write command | CK   | Part dependent                                      | Data Sheet                             |

| tRRD      | Min time between two ACTIVATE commans (different banks)     | s    | Part dependent                                      | Data Sheet                             |

| tFAW      | Min time for four ACTIVATE commands (different banks)       | S    | Part dependent                                      | Data Sheet                             |

### Values used to calculate the limits

To calculate the limits, you will need to look up or calculate the following values:

| Parameter | Description                                             | Unit  | Suggested Definition              | Reference           |

|-----------|---------------------------------------------------------|-------|-----------------------------------|---------------------|

| AL        | Additive Latency                                        | CK, s | User selection                    | System Design       |

| BL        | Burst Length                                            |       | User selection                    | System Design       |

| CL        | CAS (Read) Latency                                      | CK    | Part dependent                    | Data Sheet          |

| CWL       | CAS Write Latency                                       | СК    | Part dependent                    | Data Sheet          |

| RL        | Read Latency                                            | CK    | AL + CL                           | DDR3 (see ) 3.4.3.4 |

| WL        | Write latency                                           | СК    | AL + CWL                          | DDR3 (see ) 3.4.3.4 |

| tRCD      | RAS to CAS Delay (ACT to internal R/W)                  | S     | Part dependent                    | Data Sheet          |

| tREFI     | Refresh Interval; average time between Refresh commands | S     | Part dependent                    | Data Sheet          |

| tRTP      | Internal Read to Precharge                              | S     | Part dependent (max 4CK or 7.5ns) | Data Sheet          |

| tWR       | Internal Write Recovery                                 | S     | Part dependent                    | Data Sheet          |

| tWTR      | Internal Write to internal Read                         | S     | Part dependent (max 4CK or 7.5ns) | Data Sheet          |

#### External Read/Write + AL = Internal Read/Write

### Naming conventions

Limits which are normally expressed as maximum or minimum times have names beginning with 't'.

The names of derived timing limits begin with 'tD'. Derived limits are not usually specified directly in the part data sheet. In general, you will compute these from the standard timing parameters.

Limits which are normally expressed as a number of clock cycles have no prefix. In some cases, you may need to convert these to seconds for use by the tool.

### Customizing the limits

The definitions are suggestions based on the DDR standards. There is no requirement that the user must set the limits to those specified in the data sheet or in the JEDEC standard. You can set the limits however you like, depending on the goals of your testing.

To load and view the limits, you can either use the default limit set or use customized limit sets. If you are using customized limit sets, you can select the customized compressed archived files (.lim) from your local system. See previous topics in this chapter to know more.

#### Example limits

Example limit sets is supplied with the Post Process Compliance tool.

#### 4 Configuring Tests Limits

The below example is based on a DDR800 part with 6-6-6 timing.

#### Example part:

- Data sheet: MICRON DDR3 MT41J256-32 Me x 4 x 8 Banks PDF: 09005aef82f1e6e2 Rev. M 9/08 EN

- Speed Grade 25 (6-6-6)

- · Clock 400 MHz (2.5ns)

- · Data Rate 800 MT/s

- · Temperature 0-85C

| Parameter           | Value             | Reference                                        |

|---------------------|-------------------|--------------------------------------------------|

| tREFI               | 7.8 us (low temp) | Data Sheet, page 71                              |

| tRAS <sub>max</sub> | 70.2us            | Data Sheet (tREFI), page 63                      |

| tRAS <sub>min</sub> | 37.5ns            | Data Sheet, page 30                              |

| tRP                 | 15ns              | Data Sheet, page 30                              |

| tCCD                | 4CK (10ns)        | Data Sheet, page 70                              |

| tRRD                | 10ns              | Data Sheet, page 30                              |

| tFAW                | 50ns              | Data Sheet, page 30                              |

| tRFC                | 110ns             | Data Sheet, page 30                              |

| tRCD                | 15ns              | Data Sheet, page 30                              |

| tRTP                | 10ns              | Data Sheet, page 70                              |

| tWR                 | 15ns              | Data Sheet, page 70                              |

| tWTR                | 10ns              | Data Sheet, page 70                              |

| AL                  | Ons (OCK)         | User selected (MR1, 0 means no additive latency) |

| BL                  | 10ns (8 bursts)   | User selected (MR0)                              |

| CL                  | 6CK (15ns)        | Data Sheet, page 30 (MR0)                        |

| CWL                 | 5CK (12.5ns)      | Data Sheet, page 116 (MR2)                       |

| Parameter | Value        |

|-----------|--------------|

| RL        | 6CK (15ns)   |

| WL        | 5CK (12.5ns) |

| tDARW     | 15ns         |

| tDRP      | 10ns         |

| tDRW      | 17.5ns       |

| tDWP      | 32.5ns       |

| tDWR      | 27.5ns       |

#### References

- DDR2 JEDEC Standard 79-2E, April 2008

- DDR3 JEDEC Standard 79-3C, November 2008

# 5 Selecting Tests

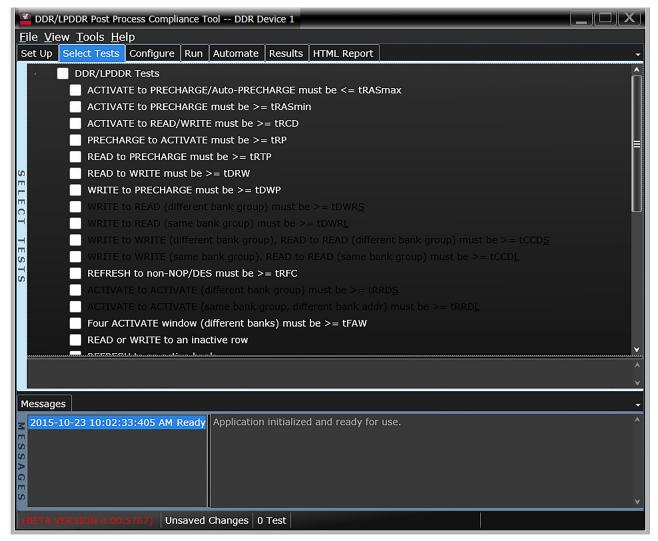

1 Click the **Select Tests** tab and then select the tests you want to run.

The tests displayed in this tab vary depending on the memory bus type and the rank addressing mode that you selected in the **Set Up** tab. For instance, the tests for same or different logical ranks are displayed if you select a 3DS rank addressing mode.

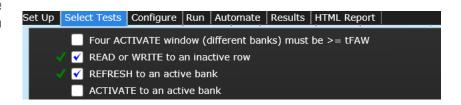

Some things to consider while selecting tests:

- · Some tests might not make sense for your system. Do not select those tests.

- · Checking a parent node/group will check all available sub-groups/tests.

- · Unchecking a parent node/group will uncheck all sub-groups/tests.

- · A parent node is checked if all subgroups are checked.

- · A parent node is unchecked if ANY subgroup is unchecked.

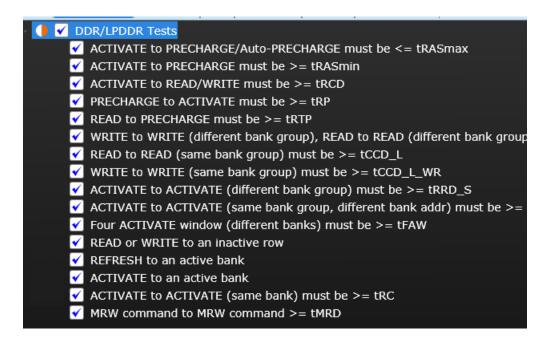

#### Tests Available With B4661A License (based on Memory type)

The following section lists the tests available for the memory bus types.

#### DDR1, 2 tests

#### DDR/LPDDR Tests ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax ACTIVATE to PRECHARGE must be >= tRASmin ACTIVATE to READ/WRITE must be >= tRCD PRECHARGE to ACTIVATE must be >= tRP READ to PRECHARGE must be >= tRTP READ to WRITE must be >= tDRW WRITE to PRECHARGE must be >= tDWP WRITE to READ must be >= tDWR WRITE to WRITE, READ to READ must be >= tCCD REFRESH to non-NOP/DES must be >= tRFC ACTIVATE to ACTIVATE (different banks) must be >= tRRD READ or WRITE to an inactive row REFRESH to an active bank ACTIVATE to an active bank ACTIVATE to ACTIVATE (same bank) must be >= tRC Mode Register Set command to Mode Register Set command >= tMRD Refresh tests REFRESH cmd to REFRESH cmd must be <= tREFI \* 9

#### **DDR3** tests

#### DDR/LPDDR Tests ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax ACTIVATE to PRECHARGE must be >= tRASmin ACTIVATE to READ/WRITE must be >= tRCD PRECHARGE to ACTIVATE must be >= tRP READ to PRECHARGE must be >= tRTP READ to WRITE must be >= tDRW WRITE to PRECHARGE must be >= tDWP WRITE to READ must be >= tDWR WRITE to WRITE, READ to READ must be >= tCCD REFRESH to non-NOP/DES must be >= tRFC ACTIVATE to ACTIVATE (different banks) must be >= tRRD Four ACTIVATE window (different banks) must be >= tFAW READ or WRITE to an inactive row REFRESH to an active bank ACTIVATE to an active bank ACTIVATE to ACTIVATE (same bank) must be >= tRC Mode Register Set command to Mode Register Set command >= tMRD Mode Register Set command to valid command >= tMOD Refresh tests REFRESH cmd to REFRESH cmd must be <= tREFI \* 9 Long cal (normal operation) to valid command must be >= tZQoper Powerdown and Self Refresh tests REF command to power down entry >= tREFPDEN Read command to power down entry >= tRDPDEN Write command to power down entry >= tWRPDEN Exit reset from CKE high to valid command >= tXPR SelfRefreshExit to Valid command with DLL <tXSDLL Exit Precharge Power Down with DLL to any valid command <tXPDLL

Short cal (normal operation) to valid command must be >= tZQCS

Calibration Tests

#### **DDR4 Tests**

DDR/LPDDR Tests ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax ACTIVATE to PRECHARGE must be >= tRASmin ACTIVATE to READ/WRITE must be >= tRCD PRECHARGE to ACTIVATE must be >= tRP READ to PRECHARGE must be >= tRTP READ to WRITE must be >= tDRW WRITE to PRECHARGE must be >= tDWP WRITE to READ (different bank group) must be >= tDWRS WRITE to READ (same bank group) must be >= tDWRL WRITE to WRITE (different bank group), READ to READ (different bank group) WRITE to WRITE (same bank group), READ to READ (same bank group) must REFRESH to non-NOP/DES must be >= tRFC Four ACTIVATE window (different banks) must be >= tFAW READ or WRITE to an inactive row REFRESH to an active bank ACTIVATE to an active bank ACTIVATE to ACTIVATE (same bank) must be >= tRC Mode Register Set command to Mode Register Set command >= tMRD Mode Register Set command to valid command >= tMOD Refresh tests REFRESH cmd to REFRESH cmd must be <= tREFI \* 9 Long cal (normal operation) to valid command must be >= tZQoper Powerdown and Self Refresh tests REF command to power down entry >= tREFPDEN Read command to power down entry >= tRDPDEN Write command to power down entry >= tWRPDEN Exit reset from CKE high to valid command >= tXPR SelfRefreshExit to Valid command with DLL <tXSDLL Exit Precharge Power Down with DLL to any valid command <tXPDLL Calibration Tests Short cal (normal operation) to valid command must be >= tZQCS

#### **DDR5 Tests**

#### LPDDR tests

DDR/LPDDR Tests ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax ACTIVATE to PRECHARGE must be >= tRASmin ACTIVATE to READ/WRITE must be >= tRCD PRECHARGE to ACTIVATE must be >= tRP READ to PRECHARGE must be >= tRTP READ to WRITE must be >= tDRW WRITE to PRECHARGE must be >= tDWP WRITE to READ must be >= tDWR WRITE to WRITE, READ to READ must be >= tCCD REFRESH to non-NOP/DES must be >= tRFC ACTIVATE to ACTIVATE (different banks) must be >= tRRD READ or WRITE to an inactive row REFRESH to an active bank ACTIVATE to an active bank ACTIVATE to ACTIVATE (same bank) must be >= tRC Mode Register Set command to Mode Register Set command >= tMRD Refresh tests REFRESH cmd to REFRESH cmd must be <= tREFI \* 9

#### LPDDR2 tests

- DDR/LPDDR Tests

- ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax

- ACTIVATE to PRECHARGE must be >= tRASmin

- ACTIVATE to READ/WRITE must be >= tRCD

- READ to PRECHARGE must be >= tRTP

- READ to WRITE must be >= tDRW

- WRITE to PRECHARGE must be >= tDWP

- WRITE to READ must be >= tDWR

- WRITE to WRITE, READ to READ must be >= tCCD

- ACTIVATE to ACTIVATE (different banks) must be >= tRRD

- Four ACTIVATE window (different banks) must be >= tFAW

- READ or WRITE to an inactive row

- REFRESH to an active bank

- ACTIVATE to an active bank

- MRW Long Calibration command to any valid command (or CKE low) must be >

- MRW Short Calibration command to any valid command (or CKE low) must be >

- MRW Init Calibration command to any valid command (or CKE low) must be > ta

- MRW Reset Calibration command to any valid command (or CKE low) must be >

- MRW command to any valid command (or CKE low) must be > tMRW

- MRR command to any valid command (or CKE low) must be > tMRR

- PRECHARGE (all banks) to ACTIVATE/REFRESH must be >= tRPab

- PRECHARGE (per bank) to ACTIVATE/REFRESH must be >= tRPpb

- Duration of CKE high/low >= tCKE.

- Duration of self-refresh >= tCKESR

- Duration of deep power down >= tDPD

- Refresh tests

- Greater than 8 REFRESH all bank commands in tREFBW

- Required number of refresh commands occur in time period <= tREFW

- Refresh (all banks) to Activate or Refresh must be > tRFCab

- Refresh (per bank) to Activate (same bank) or Refresh must be > tRFCpb

- Powerdown and Self Refresh tests

- Exit self-refresh to valid command >= tXSR

- Exit power down to valid command >= tXP

#### **LPDDR3 Tests**

DDR/LPDDR Tests ACTIVATE to PRECHARGE/Auto-PRECHARGE must be <= tRASmax ACTIVATE to PRECHARGE must be >= tRASmin ACTIVATE to READ/WRITE must be >= tRCD READ to PRECHARGE must be >= tRTP READ to WRITE must be >= tDRW WRITE to PRECHARGE must be >= tDWP WRITE to READ must be >= tDWR WRITE to WRITE, READ to READ must be >= tCCD ACTIVATE to ACTIVATE (different banks) must be >= tRRD Four ACTIVATE window (different banks) must be >= tFAW READ or WRITE to an inactive row REFRESH to an active bank ACTIVATE to an active bank MRW Long Calibration command to any valid command (or CKE low) must be > t MRW Short Calibration command to any valid command (or CKE low) must be > MRW Init Calibration command to any valid command (or CKE low) must be > tZ MRW Reset Calibration command to any valid command (or CKE low) must be > MRW command to MRW command (or CKE low) must be > tMRW MRW command to any valid command must be > tMRD MRR command to any valid command (or CKE low) must be > tMRR PRECHARGE (all banks) to ACTIVATE/REFRESH must be >= tRPab PRECHARGE (per bank) to ACTIVATE/REFRESH must be >= tRPpb Duration of CKE high/low >= tCKE. Duration of self-refresh >= tCKESR Duration of deep power down >= tDPD Refresh tests Greater than 8 REFRESH all bank commands in tREFBW Required number of refresh commands occur in time period <= tREFW

Refresh (all banks) to Activate or Refresh must be > tRFCab

Powerdown and Self Refresh tests

Exit self-refresh to valid command >= tXSR

Exit power down to valid command >= tXP

Refresh (per bank) to Activate (same bank) or Refresh must be > tRFCpb

DDR/LPDDR Post Process Compliance Tool User Guide

#### **LPDDR4 Tests**

|   | ■ DDR/LPDDR Tests                                                                                                                       |

|---|-----------------------------------------------------------------------------------------------------------------------------------------|

| • |                                                                                                                                         |

|   | <ul> <li>✓ ACTIVATE to PRECHARGE/Auto-PRECHARGE must be &lt;= tRASmax</li> <li>✓ ACTIVATE to PRECHARGE must be &gt;= tRASmin</li> </ul> |

|   | <u> </u>                                                                                                                                |

|   | ✓ ACTIVATE to READ/WRITE must be >= tRCD                                                                                                |

|   | ACTIVATE to ACTIVATE (different banks) must be >= tRRD                                                                                  |

|   | Four ACTIVATE window (different banks) must be >= tFAW                                                                                  |

|   | ▼ READ or WRITE to an inactive row                                                                                                      |

|   | ✓ REFRESH to an active bank                                                                                                             |

|   | ✓ ACTIVATE to an active bank                                                                                                            |

|   | MRW command to MRW command (or CKE low) must be > tMRW                                                                                  |

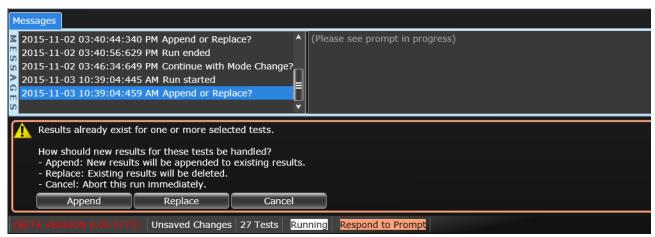

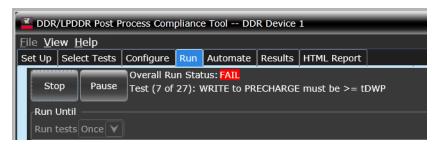

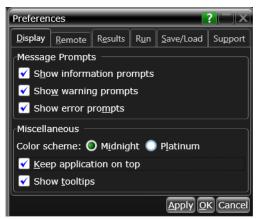

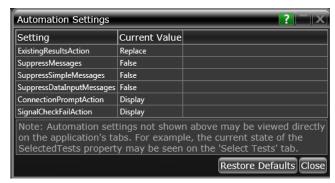

|   | MRW command to any valid command must be > tMRD                                                                                         |