トランジェント・コンボリューション・エレメントはトランジェントシミュレータだけではなく、シグナルインゲグリティーのための以下の多くの機能も備えています。

- Sパラメータからの因果およびパッシブ・タイムドメイン・モデルを作成するためのコンボリューションメソッド。 ADSコンボリューションは、他のツールとは異なり、長い伝送ラインや損失のある伝送ラインなどの難しい問題に対応できます。

- オンダイSパラメータ(BIRD 152)、高度なジッタ(BIRD 123)、ミッドチャネルリドライバーおよびリタイマー(BIRD 156)(下記に詳細を記載)などの仕様へのIBIS AMIおよび規格化前の拡張への対応を含む、ビット・バイ・ビットおよび統計モード付きのチャネルシミュレータ。

- BER等高線およびバスタブ曲線の表示などアイダイアグラム解析を提供するアイプローブコンポーネント。 自動マスク違反チェック機能付きのアイ・マスク・ユーティリティも含まれています。

- 自動タップ最適化を伴うイコライザーのサポート。

- それぞれ異なるデータレートの複数のアグレッサーのクロストークチェック機能。

- DDR2/DDR3/LPDDR2規格のコンプライアンス・デザイン・キット。

- IBIS I/O業界標準(ANSI/EIA-656)に準拠したトランシーバモデルの組み込み。

- タイムドメイン・リフレクトメトリー・ツール

- キーサイトの測定器で使用されている実証済みのEZJITアルゴリズムを用いたジッタ分離。

- 測定/シミュレーションSパラメータモデルを集中定数等価回路や極/零点表現に変換可能な広帯域SPICEモデルジェネレーター。

- 4ポートのVNA測定より、ビクティム/アグレッサー・チャネル・モデルを構築できるTouchstoneコンバイナー。

チップ間データリンクは、ラップトップコンピューターからデータセンターのサーバー、電気通信交換局、インターネットルーターまで、今日のほとんどすべての民生用/企業用デジタル製品に使用されています。

より低速の場合、デザイナーはSPICEで集中定数モデルを使用してシミュレーションを実行できます。 しかし、今日のマルチギガビット/sのチップ間データレートでは、インピーダンス不整合、反射、クロストーク、表皮効果、誘電損失などの高周波および分布定数の影響を考慮する必要があります。

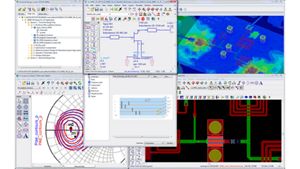

そのために、シグナル・インテグリティー・エンジニアにはSPICEを超えるものが必要です。 Advanced Design System(ADS)のトランジェント・コンボリューション・エレメントのSPICEライクのシミュレータ部分は、集中定数のモデルだけでなく、高速PCBトレースをモデル化するために必要な分散定数の伝送ライン、Sパラメータ、EMモデルも扱うことができます。 トランジェント・コンボリューション・エレメントは、高性能なポイントツールというだけでなく、ADSに一連の機能が完全に統合されています。 システムレベル、回路レベル、電磁界レベルのモデルを適切な抽象化レベルで1つのシミュレーションに組み合わせることができます。

また、マルチコアプロセッサのサポート、新しい高性能疎行列ソルバにより、従来のトランジェントシミュレーションよりも速度が3倍に向上し、業界最高速のシグナルインテグリティー回路シミュレータを実現しています。

シグナル・インテグリティー・エンジニアは、トランスミッター、チャネル、レシーバーに最適な特性を選択するために、超低ビット・エラー・レート(BER)の等高線をデザイン空間の数千ポイントで決定する必要があります。 マルチコアと最新の線形代数アルゴリズムを用いても、トランジェントシミュレーションにはかなり長い時間がかかります。 100万ビットの場合は1日以上です。

この問題に対応するために、キーサイトは時間のかかるトランジェントシミュレーションの必要性を排除する新しい2つのモードを追加しました。 チャネルのトレース、ビア、ボンドワイヤー、コネクタなどが線形時不変("LTI")という利点を活用して、 トランジェントソルバをタイムステップごとに実行する強引な手法を回避して、 超低BER等高線を数秒で求めることができます。 このため、非常に高速で完全な「カット&トライ」によるデザイン空間の探索を実現できます。

下の表は、従来のトランジェントシミュレータとビット・バイ・ビット・モードおよび統計モードのチャネルシミュレータを比較した場合の長所と短所を示しています。

| |

トランジェント(SPICEのような)シミュレータ |

チャネルシミュレータ、ビット・バイ・ビット・モード |

チャネルシミュレータ、統計モード |

|---|

| 手法 |

すべてのタイムステップでのキルヒホッフの電流則の修正節点解析 |

ビット・バイ・ビットでのステップ応答の重ね合わせ |

ステップ応答ベースの統計計算 |

| 適用範囲 |

線形/非線形チャネル

有限なユーザー指定のビットパターン

アダプティブ/固定のイコライザータップ |

LTIチャネル

有限なユーザー指定のビットパターン

アダプティブ/固定のイコライザータップ

IBIS AMI |

LTIチャネル

無限ビットパターンの確率論的性質 固定イコライザータップ IBIS AMI(モデルが提供する場合は、GetWave関数の線形近似を使用) |

| 1分間のシミュレーションでのBERフロア |

~10-3 |

~10-6 |

~10-16 |

| メガビットシミュレーション時間(代表値) |

25時間 |

12分 |

40秒 |

このエレメントに含まれる機能

- 高周波SPICEシミュレータ : 非常に大きいベースバンド回路、スタートアップトランジェント、発振器、高速デジタル/スイッチング回路の解析用非線形タイムドメインシミュレータ。

- コンボリューションシミュレータ : 周波数異存コンポーネント(分布定数エレメント、Sパラメータ・データ・ファイル、伝送ラインなど)を正確にシミュレートすることによって高周波SPICEモジュールの機能を拡張する高度なタイムドメインシミュレータ。

- IBIS I/Oモデル : ICのドライバー、出力、レシーバー、入力の非線形ビヘイビアのモデル化のためのI/Oバッファー情報仕様(IBIS)モデル。

- シグナルインテグリティー検証ツールキット : マルチギガビット通信リンクのデザインの性能劣化の原因となるジッタの解析機能。 このツールキットを使用すると、ハードウェアのプロトタイプの作成を開始する前に、ジッタの原因を特定して取り除くことができるので、開発サイクルの後半でのコストのかかる再設計がなくなります。

- 広帯域SPICEモデルジェネレーター : デザイナーは測定/シミュレーションSパラメータモデルを集中定数等価回路や極/零点表現に変換可能。

サポートされているIBISのキーワードの表 (ナレッジセンターへのログインが必要)