您希望搜索哪方面的内容?

PathWave 先进设计系统(ADS)2020 更新 2.0 产品发布

Highlights

PathWave 先进设计系统(ADS)2020 更新 2.0 为以下应用提供了丰富的解决方案和其他功能:

- 高速数字(HSD)设计

- 电磁(EM)仿真

- 电路仿真

- 电力电子设计

- 设计与技术管理

- 设计编辑

PathWave 先进设计系统(ADS)2020 更新 2.0 现已发布!

请点击上面的试用和许可证选项卡,然后点击详细信息和下载按钮下载这个最新软件。

Description

PathWave 先进设计系统(ADS)2020 更新 2.0 针对复杂的高速数字设计、射频和微波设计以及电力电子设计提供了多种解决方案和更多功能。这些设计包括:

PathWave 先进设计系统(ADS)2020 更新 2.0 针对复杂的高速数字设计、射频和微波设计以及电力电子设计提供了多种解决方案和更多功能。这些设计包括:

高速数字设计

SerDes

- 通过与 VPIphotonics 公司合作,针对数据通信和电信市场推出了 E-O-E(电-光-电)综合工作流程。这使用户在分析端到端链路设计时能够将光通道效应也考虑在内,例如:

- 电吸收调制器(EAM)的非线性波长相关传递函数

- 非线性

- 相对噪声强度(RIN)

- 光纤衰减

- 色散

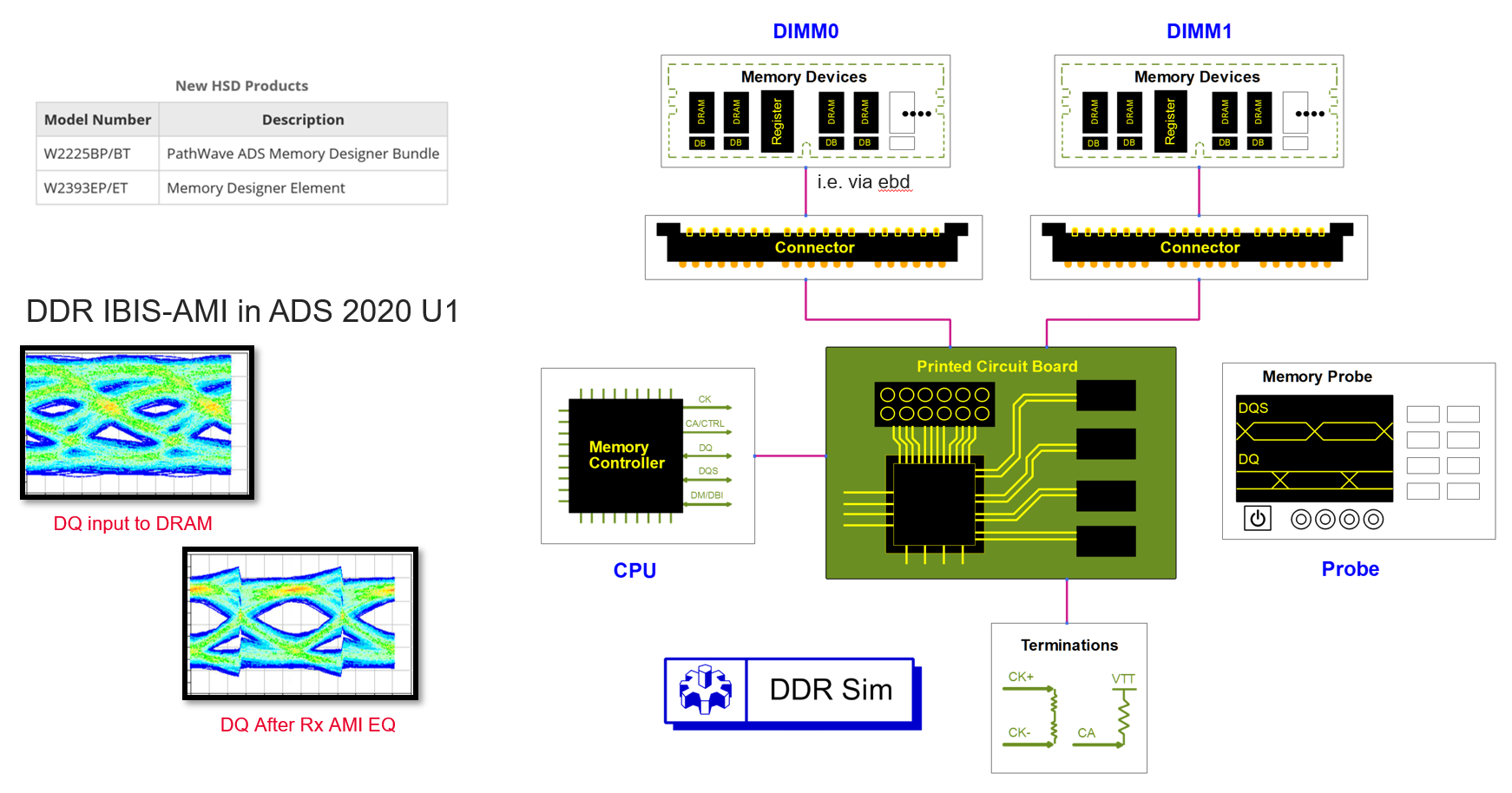

DDR/存储器

- 全新 DDR5 和 LPDDR5 解决方案采用 IBIS-AMI 建模确保均衡

- 通过内部相位内插器训练跟踪抖动,实现最佳的 DFE 时钟

- 对仿真波形进行自动 DDR5 一致性测试

- 简化存储器设计流程,例如在控制器和存储器中集成封装设置,大大减少接线操作

- 改进了控制器、存储器和端子 GUI,并提供对 DDR_端子器件的群编辑功能,使用起来更容易

SIPro/PIPro/过孔设计程序

- 在 SIPro 中提供了情境感知信号名称匹配算法

- 在结果窗口中添加了时延图。

- 在过孔设计程序中,使对数频率计划支持直流频率(0 Hz)。

- 添加了设置 siodump 样本数的选项。

电磁仿真

一般特性

- 在电磁仿真流程中添加了对 Teardrops(泪滴焊盘)的支持

RFPro

- 为自定义编译器启用了 RFPro 流程

- 提高了 RFPro 的打开速度,并改进了元器件角色更改功能

电路仿真

一般特性

- 修改了自定义规则常规表达式

- 将上升时间和下降时间更改为 0.2 dq UI

- 在指定规则时使用自定义规则,而不必将其添加到预设中

- 添加了 BER 列表和“计算多个 BER 下的轮廓”选项

- 修复了 DDR_PCB 表格调整大小的问题

- IBIS 模型选择设置现在会显示完整的模型名称

- 修复了两个 DCD 实施报告显示不同结果的问题

- 当进行 IBIS-AMI 通道仿真时 Density(密度)不在 2UI 中心,WidthAtBER 现在会给出正确的结果

电热

- ETH 目前可以支持使用原始的 TransientVars :: step_reduction_factor 数据,而不需要进行任何处理(数据截断)

- 修复了在使用加密热技术时复用模型提取的问题

电力电子

从技术资料获得模型

- 添加了一个模板,可以从功率 MOSFET 技术资料中提取模型

- 添加了一个示例工作区,用于演示如何从功率 MOSFET 技术资料中提取模型

在电力电子模型库中添加了一个通用的功率 MOSFET 元器件

修复了 IGBT 示例工作区的一个漏洞

电力电子专业(PEPro)软件

- 修复了 PEPro 版图显示设置面板中“显示/隐藏”按钮的一个漏洞

- 修复了电路激励设置中“选择数据集”对话框的一个信息图标漏洞

- 修复了闭环降压转换器示例工作区中的一个漏洞

- 修复了场比例属性中的一个漏洞

设计与技术管理

数据显示

公式管理器是一个在表格中显示所有公式和迹线公式的停靠窗口。您现在可以在一个公式管理器窗口中显示打开的多个数据显示窗口。以下是改进之处:

- 提供了参考更新,改进了选择(selection)设置,并且增加了新的右键单击选项

- 现在,选择相关选项,您将看到关于已停用相关公式的警告

- 现在,在默认情况下,选择相关公式将不会跳转到选择(selection)设置

设计编辑

添加了下列 AEL 功能:

- 泪滴焊盘 AEL 功能,用于向选择(selection)设置添加泪滴焊盘,修改选择(selection)设置中的泪滴焊盘,以及删除选择(selection)设置中的泪滴焊盘。如欲了解更多信息,请参见泪滴焊盘功能。

- db_find_inst_term_by_name()——在给定实例对象和实例终端名称的情况下,查找并返回实例终端

- db_set_edge_area_port_of_fig() ——将引脚图片的边缘/区域端口设置为传入项。如果传入的项编号为 0 或项名称为空,则图片的边缘/区域端口将被清空

设计导入/导出

- 添加了对导入网表的支持,网表中包含二极管模型温度系数参数

- 添加了对导入 LTspice 网表的支持,其中的元器件参数值用大括号括起来

设计规则检查(DRC)

Assura DRC

- 提供的配置能够设置默认元器件,从而生成相关元器件的原图(参数化单元)

Calibre DRC

- 添加了能够配置规则文件和规则文件夹的功能

验证测试台(VTB)

现在支持单端口 VTB(仅信号源)仿真。现在,您可以在 SystemVue 中创建复合调制源,并在 ADS 电路包络组件中使用。

注意:在 SystemVue VTB 的默认设置下,SystemVue 负责管理仿真的时标设置。通常,如果 VTB 配有接收机,接收机(在 SystemVue 工作区内)会设置为:自动设置仿真的停止时间,以便取回必要的数据量来计算所需的品质因数。如果 VTB 未配备接收机(纯输入 VTB),则在 SystemVue 工作区中可能无法设置准确的停止时间。在这种情况下,如果停止时间较长,则可能会导致仿真时间过长。

在默认情况下,这不会发出警告,因为仿真器在运行前并不知道 SV 工作区的停止时间。

如果用户设置的值不是 100n(不包括 0),则包络控制器将成为主机。在这种情况下,仿真将在到达第一个停止时间时停止(在包络控制器中设置的停止时间或在 SystemVue 工作区中设置的停止时间,取两者中的较小值)。在调试通用 VTB(无需运行整个时间表)时,最好设置一个自定义停止时间;而在调试纯输入 VTB 时,则必须这样做,以便使仿真到达一个实际时间时停止,避免过长时间运行

注意:当您设置 100ns 时,出于向后兼容的原因,仿真器将忽略它。当将其放在原理图上时,停止时间 = 100n 便是在控制器中设置的值。为了向后兼容,停止时间 = 100n 意味着我们让 SV 工作区来控制计时。

从 ADS 2017 起,要安装 VTB 功能所需的文件,您需要下载一个单独的 VTB 安装程序(仅适用于 Windows 操作系统)。如果是 Linux 操作系统,VTB 安装程序与 ADS 安装程序绑定在一起。

- 建议将兼容的 ADS 和 VTB 安装程序下载到同一目录中。下载完成后,运行 ADS 安装程序。此程序将自动安装 VTB 功能。

- 如果您已经安装了 ADS 并发现 VTB 功能丢失,那么您需要下载并安装 VTB。

- 升级了 ADS 中的 SystemVue 2018 更新 1 引擎。

- 更新了下列 VTB:

- 3GPP_NR_DL_Tx_Source

- 3GPP_NR_DL_Tx

- 3GPP_NR_UL_Tx_Source

- 3GPP_NR_UL_Tx

- 更新了下列 VTB:

- 进行了下列修改:

- 支持 3GPP TS 38.141 V1.2.0(2018-11)标准中针对新空口下行链路示例所定义的测试模型

- 支持 3GPP 38.521-1/38.521-2 标准中的表 6.1-1 针对新空口上行链路示例所定义的通用配置

- 通过将测量长度缩短到 1 子帧,加速 EVM 测量

- 添加 ACLR 测量

注意:ADS 2020 更新 1.0 中使用的 SystemVue 引擎是在 SystemVue 2018 更新 1.0 的基础上改进而来的,修复了一些关键问题。因此,尽管在 ADS 2020 更新 1.0 中运行上述 VTB 示例可以得出正确结果,但如果在 SystemVue 2018 更新 1.0 中运行,有可能出错或得到错误的结果。如果需要修改这些示例,建议使用 SystemVue 2018 更新 1.0 打开和进行修改,再将它们导入回 ADS,通过运行 ADS 2020 更新 1.0 观察结果。

ADS 2020 更新 1.0 仅支持导入由 SystemVue 2018 和 SystemVue 2018 更新 1.0 所创建的自定义 VTB(SystemVue 工作区)。

快速入门

准备好开始使用 PathWave ADS 了吗?索取免费试用版本。

查看其他 ADS 产品版本。

京公网安备 11010502040140 号

京公网安备 11010502040140 号