User Guide

Keysight N4962A Serial BERT 12.5 Gb/s

#### **Notices**

© Keysight Technologies, Inc. 2012-2014

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies, Inc. as governed by United States and international copyright laws.

#### Manual Part Number

N4962-91021

#### Edition

Edition 6.0, September 2014

Printed in Germany

Keysight Technologies, Inc. Agilent Technologies R&D and Marketing-GmbH & Co. KG Herrenberger Str. 130 71034 Böblingen, Germany

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

#### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

#### Restricted Rights Legend

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Keysight Technologies' standard commercial license terms, and non-DOD Departments and

Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

#### Safety Notices

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

#### Safety Summary

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings or operating instructions in the product manuals violates safety standards of design, manufacture, and intended use of the instrument. Keysight Technologies assumes no liability for the customer's failure to comply with these requirements. Product manuals are provided with your instrument on CD-ROM and/or in printed form. Printed manuals are an option for many products. Manuals may also be available on the Web. Go to www.keysight.com and type in your product number in the Search field at the top of the page.

#### General

This product is a Safety Class 1 instrument (provided with a protective earth terminal). The protective features of this product may be impaired if it is used in a manner not specified in the operation instructions.

All Light Emitting Diodes (LEDs) used in this product are Class 1 LEDs as per IEC 60825-1.

#### **Environment Conditions**

This instrument is intended for indoor use in an installation category II, pollution degree 2 environment. It is designed to operate at a maximum relative humidity of 95% and at altitudes of up to 2000 meters.

Refer to the specifications tables for the ac mains voltage requirements and ambient operating temperature range.

#### Before Applying Power

Verify that all safety precautions are taken. The power cable inlet of the instrument serves as a device to disconnect from the mains in case of hazard. The instrument must be positioned so that the operator can easily access the power cable inlet. When the instrument is rack mounted the rack must be provided with an easily accessible mains switch.

Ground the Instrument To minimize shock hazard, the instrument chassis and cover must be connected to an electrical protective earth ground. The instrument must be connected to the ac power mains through a grounded power cable, with the ground wire firmly connected to an electrical ground (safety ground) at the power outlet. Any interruption of the protective (grounding) conductor or disconnection of the protective earth terminal will cause a potential shock hazard that could result in personal injury.

#### Do Not Operate in an Explosive Atmoshpere

Do not operate the instrument in the presence of flammable gases or fumes.

#### Do Not Remove the Instrument Cover

Operating personnel must not remove instrument covers. Component replacement and internal adjustments must be made only by qualified personnel.

Instruments that appear damaged or defective should be made inoperative and secured against unintended operation until they can be repaired by qualified service personnel.

### Safety Symbols

Table 1. Safety Symbol

| Symbol                  | Description                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\triangle$             | Indicates warning or caution. If you see this symbol on a product, you must refer to the manuals for specific Warning or Caution information to avoid personal injury or damage to the product.                                                                                                                                                 |

| ילי                     | Frame or chassis ground terminal. Typically connects to the equipment's metal frame.                                                                                                                                                                                                                                                            |

| A                       | Indicates hazardous voltages and potential for electrical shock.                                                                                                                                                                                                                                                                                |

| $\stackrel{\bigstar}{}$ | Indicates that antistatic precautions should be taken.                                                                                                                                                                                                                                                                                          |

|                         | Indicates hot surface. Please do not touch.                                                                                                                                                                                                                                                                                                     |

| <b>③</b> ∘              | CSA is the Canadian certification mark to demonstrate compliance with the Safety requirements.                                                                                                                                                                                                                                                  |

| CICES/NMB-001           | CE compliance marking to the EU Safety and EMC Directives. ISM GRP-1A classification according to the international EMC standard. ICES/NMB-001 compliance marking to the Canadian EMC standard.                                                                                                                                                 |

|                         | The RCM mark indicates that this product meets EMS/Product Safety Requirements and may be imported to Australia and New Zealand.                                                                                                                                                                                                                |

| ICES/NMB-001            | This mark indicates compliance with the Canadian EMC regulations.                                                                                                                                                                                                                                                                               |

| ISM 1-A                 | This text denotes the instrument is an Industrial Scientific and Medical Group 1 Class A product.                                                                                                                                                                                                                                               |

|                         | China RoHS regulations include requirements related to packaging, and require compliance to China standard GB18455-2001. This symbol indicates compliance with the China RoHS regulations for paper/fiberboard packaging.                                                                                                                       |

| 40                      | Indicates the time period during which no hazardous or toxic substance elements are expected to leak or deteriorate during normal use. Forty years is the expected useful life of the product.                                                                                                                                                  |

|                         | The South Korean Class A EMC declaration (KC) mark indicates that this product is Class A suitable for professional use and is for use in electromagnetic environments outside of the home.  The KC mark includes the marking's identifier code that has up to 26 digits and follows this format: KCC-VWX-YYY-ZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZZ |

#### **Compliance and Environmental Information**

Table 2. Compliance and Environmental Information

# This product complies with WEEE Directive (2002/96/EC) marking requirements. The affixed label indicates that you must not discard this electrical/electronic product in domestic household waste. Product Category: With reference to the equipment types in WEEE Directive Annex I, this product is classed as a "Monitoring and Control instrumentation" product. Do not dispose in domestic household waste. To return unwanted products, contact your local Keysight office, or see www.keysight.com/environment/product/ for more information.

#### Contents

| 1 | Getti | ng Started                                            | 9  |

|---|-------|-------------------------------------------------------|----|

|   | 1.1   | General                                               | 9  |

|   |       | 1.1.1 Key Features                                    | 9  |

|   |       | 1.1.2 Internal clock system                           |    |

|   |       | 1.1.3 PRBS generator                                  |    |

|   |       | 1.1.4 Error detector                                  |    |

|   |       | 1.1.5 Operating modes                                 |    |

|   |       | 1.1.7 Data entry / interface                          |    |

|   | 1.2   | N4962A Operation Overview                             |    |

|   | 1.3   | Getting Started with the N4962A Serial BERT 12.5 Gb/s |    |

|   |       | 1.3.1 Unpacking and Installation                      |    |

|   |       | 1.3.2 Safety and Regulatory                           |    |

|   |       | 1.3.3 Declaration of Conformity                       |    |

|   |       | 1.3.4 Important Notes                                 |    |

|   |       | 1.3.5 Performance Recommendations                     |    |

|   | 1.4   | Connect the Hardware                                  | 14 |

|   | 1.5   | Turn It On                                            | 14 |

|   | 1.6   | Align Clock and Data                                  | 15 |

|   | 1.7   | Make the Measurement                                  | 15 |

| 2 | N496  | S2A System Overview                                   | 17 |

|   | 2.1   | Front Panel Quick Reference                           | 18 |

|   | 2.2   | Rear Panel Quick Reference                            | 21 |

|   | 2.3   | Connector Care                                        | 22 |

| 3 | Syste | em Details and Performance Specifications             | 23 |

|   | 3.1   | General                                               | 23 |

|   | 3.2   | Safety and Regulatory                                 | 24 |

|   | 3.3   | Internal Clock                                        | 24 |

|   | 3.4   | PRBS Generator                                        | 27 |

|   | 3.5   | Error Detector                                        | 29 |

|   | 3.6   | Data Path                                             | 32 |

| 4 | Opera | ation3                                                                                                       | 33             |

|---|-------|--------------------------------------------------------------------------------------------------------------|----------------|

|   | 4.1   | General Information                                                                                          | 34             |

|   | 4.2   | Front Panel Interface                                                                                        | 36<br>37<br>39 |

|   | 4.3   | Rear Panel Interface                                                                                         | 46             |

|   | 4.4   | Power-On State                                                                                               | <del>4</del> 8 |

|   | 4.5   | System Verification 4.5.1 Self Test Mode 4.5.2 Error Free Test 5.3 High BER Test 5.4.5.4 Low BER Test 5.5    | 49<br>50<br>50 |

|   | 4.6   | BER Detector Clock Phase Adjustment                                                                          | 51             |

|   | 4.7   | Basic BER Measurement 5                                                                                      | 53             |

| 5 | Remo  | ote GPIB Interface5                                                                                          | 55             |

|   | 5.1   | GPIB Capabilities 5                                                                                          | 56             |

|   | 5.2   | GPIB Command Syntax                                                                                          |                |

|   | 5.3   | IEEE Common Commands5                                                                                        | 59             |

|   | 5.4   | SCPI Mandated Commands6                                                                                      | 30             |

|   | 5.5   | N4962A Device Commands65.5.1 Internal Clock Commands65.5.2 PRBS Pattern Commands65.5.3 Measurement Commands7 | 31<br>35       |

|   | 5.6   | Examples                                                                                                     | 30             |

| 6 | Retur | rning the N4962A Serial BERT to Kevsight Technologies8                                                       | 35             |

# 1 Getting Started

#### 1.1 General

The N4962A serial BERT 12.5 Gb/s operates from 500 Mb/s – 12.5 Gb/s referencing an external clock, and from 9.90 – 11.35 Gb/s with the programmable internal clock.

#### The N4962A includes:

- Internal clock system

- PRBS generator

- Error detector

#### 1.1.1 Key Features

- Low cost, high performance

- Programmable output amplitude control

- Electronic receiver clock phase adjust

- Differential inputs and outputs

- Synchronous clock & pattern triggers

- Selectable pattern lengths, mark density

- Data Thru switch on Receiver for use with Oscilloscope on received data

- Controlled with GPIB control bus format

#### 1.1.2 Internal clock system

- Internal clock 9.90 to 11.35 GHz

- External clock input for 0.5 to 12.5 GHz operation

#### 1.1.3 PRBS generator

Selectable PRBS patterns:

o Lengths: 27-1, 210-1, 215-1, 223-1, 231-1

o Mark densities: 1/2, 1/4, 1/8

• Adjustable PRBS amplitude:

o Voltage: 0.3 - 1.8 V pp per output

o Step size: 10 mV

#### 1.1.4 Error detector

- Automatic sampling point adjustment

- Elapsed time BER measurements

- Manual threshold adjustment)

#### 1.1.5 Operating modes

- Disabled ('safe mode': no output)

- Enabled (PRBS output enabled)

- Thru (no detector; inputs connected to Data Thru connectors on back panel)

#### 1.1.6 Display

- LED indicators

- Multifunction alphanumeric display

#### 1.1.7 Data entry / interface

- Push-button control (local)

- Remote GPIB (IEEE 488.2-1992)

- Compatible with N4980A multi-instrument BERT software user interface

#### 1.2 N4962A Operation Overview

The Keysight Technologies N4962A is a cost-effective serial BERT 12.5 Gb/s, consisting of an internal clock system, PRBS generator, and error detector. It is designed for automated production-line testing, manufacturing, characterization, and R&D lab use. The N4962A features high-UI jitter injection and programmable output amplitude.

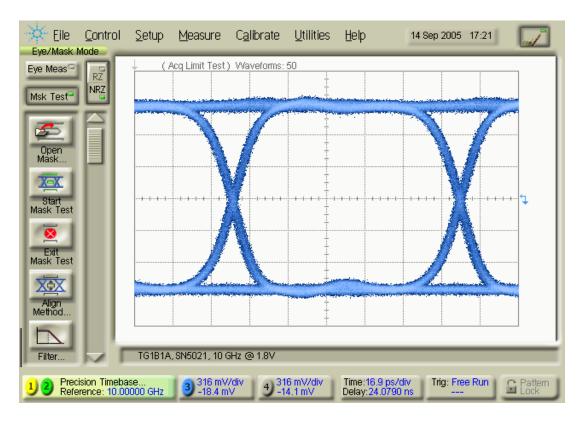

Figure 1. Eye waveform

The N4962A generates a continuous bit pattern that is applied to the DUT then fed back into the error detector. The input is automatically synchronized and compared with the original bit stream. The bit error rate is calculated by comparing the number of bit errors to the total number of bits transmitted. The BER can be shown on the display and can be captured through the remote GPIB interface.

#### 1.3 Getting Started with the N4962A Serial BERT 12.5 Gb/s

#### 1.3.1 Unpacking and Installation

The N4962A serial BERT 12.5 Gb/s is shipped with all the accessories required for the self-test mode and verification. The contents includes:

- N4962A serial BERT 12.5 Gb/s

- Two coax cables to connect rear-panel clocks (TX CKO, RX CKO to TX CKI, RX CKI)

- Two phase balanced 50  $\Omega$  coaxial cables for self-test mode (IN, /IN to OUT, /OUT)

- Four 2.92 mm male-female adapters

- AC power converter module

- AC power cord

- CD containing the N4962A User Guide and N4962A Data Sheet

Refer to the N4960-90030 N495xA through N498xA Connector Care Reference Guide at www.Keysight.com/find/N4962A.

WARNING

If this product is not used as specified, the protection provided by the equipment could be impaired. This product must be used in a normal condition (in which all means for protection are intact) only.

CAUTION

Before switching on this instrument, make sure the supply voltage is in the specified range.

CAUTION

This instrument has autoranging line voltage input. Be sure the supply voltage is within the specified range.

In an ESD-safe environment, carefully remove the N4962A. Install on a flat surface with unobstructed air flow to the back panel. Plug the AC power cord into the power converter module and a wall socket, then plug the converter module into the N4962A.

#### 1.3.2 Safety and Regulatory

This product has been designed and tested in accordance with accepted industry standards, and has been supplied in a safe condition. The documentation contains information and warnings that must be followed by the user to ensure safe operation and to maintain the product in a safe condition.

#### WARNING

Do not remove instrument covers. There are no user serviceable parts within. Operation of the instrument in a manner not specified by Keysight Technologies may result in personal injury or loss of life.

#### WARNING

For continued protection against fire hazard, replace fuses, and or circuit breakers only with same type and ratings. The use of other fuses, circuit breakers or materials is prohibited.

#### WARNING

To prevent electrical shock, disconnect instrument from mains before cleaning. Use a dry cloth or one slightly dampened with water to clean the external case parts. Do not attempt to clean internally.

#### CAUTION

The Mains wiring and connectors shall be compatible with the connector used in the premise electrical system. Failure, to ensure adequate earth grounding by not using the correct components may cause product damage, and serious injury.

#### 1.3.3 Declaration of Conformity

A EU declaration of conformity is available at <a href="http://regulations.about.Keysight.com/doc/search.htm">http://regulations.about.Keysight.com/doc/search.htm</a>

#### 1.3.4 Important Notes

- Use ESD protection at all times when using the instrument

- Review min/max specifications before applying input signals

- Use only K-connectors on the OUT and /OUT ports

- Handle the pair of self-test and clock loop coaxial cables with care

- Leave dust jackets on unused back panel connectors

- Situate the instrument away from heat sources, do not block the fan

#### 1.3.5 Performance Recommendations

- When using differential-mode connections, ensure the cables are phase balanced

- Differential connectors may be used single-ended if unused ports are terminated in 50  $\boldsymbol{\Omega}$

- Use high quality cables and connector savers (or adaptors)

- Keep cable lengths short and minimize number of cable bends

- Use a 7-10 in-lbs torque wrench when attaching connectors

- Terminate all unused RF connectors with 50  $\Omega$  terminations

#### 1.4 Connect the Hardware

- Connect power cord to adaptor to N4962A; plug in the power cord

- Connect TX CKO to TX CKI with included coaxial cable

- Connect RX CKO to RX CKI with included coaxial cable

- Connect the OUT (and optionally /OUT to your DUT input

- Connect your DUT output to IN (and optionally /IN)

#### 1.5 Turn It On

- Turn on the power switch from the back panel

- Press the Data Path > Select Path button and select Enabled

- o This will turn on the PRBS output; when Disabled is selected, the instrument is in a 'safe mode' and no output is generated

- Press the Display > Scroll ↓ button and select Ampl (V)

- Press the Adjust > Ampl +/- buttons to set the single-ended output voltage

#### 1.6 Align Clock and Data

- Press the Data Path > PRBS button only if the DUT is inverting

When on, the PRBS will generate an inverted output signal

- Press the Display > Scroll ↓ button and select Ø

- Press the Adjust > Config State + button to auto-set the detector phase

- Observe the Error **c** light

- The light indicates errors are being measured by the error detector, if the light is on, no error-free sampling point could be found

#### 1.7 Make the Measurement

- Press the Receiver > On button and ensure the light is on

- Press the Display > Scroll ↓ button and view Err (error counter)

- Press the Display > Scroll ↓ button and view BER

- Press the Display > Scroll ↓ button and view ε time (sec)

- Press the Receiver > On button to end the measurement

Getting Started

## 2 N4962A System Overview

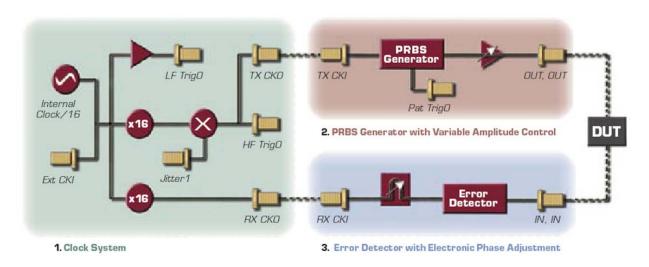

The N4962A consists of three functional blocks:

- Internal/external clock system with analog jitter injection

- PRBS generator (TX) with variable output amplitude control

- Error detector (RX) with electronic clock phase adjustment

The N4962A is controlled by front-panel buttons and remote GPIB (IEEE 488.2) commands; information is conveyed with LED indicators and a display on the front panel, along with GPIB data communication.

Figure 2. N4962A simplified block diagram; system overview

The clock system features an internal generator that creates a 9.90 to 11.35 GHz system clock from an internal 1/16th-rate clock generator. The internal clock/16 can also be phase locked to an external 1/16th clock if desired. The high-frequency TX clock and trigger output can be FM-modulated with an optional external jitter signal. Alternatively, external 500 Mb/s to 12.5 Gb/s clocks can be used in place of the internal high-frequency clocks for the PRBS generator and error detector.

The PRBS generator creates a continuous bit stream triggered by the input clock rate, configured by the selectable pattern length, mark space density, data inversion, and error injection settings. The output is amplified by a programmable gain stage.

The error detector compares the input to an automatically-synchronized bit stream generated with the same system settings. The clock input features an electronic phase adjuster to correctly align the clock and data sampling point.

The system settings can be set by the local push-button interface or remote GPIB (IEEE 488.2) interface. All settings can be accessed through the menu system or through GPIB commands. The N4962A is compatible with the N4980A multi-instrument BERT software which is available through Keysight Technologies to help speed up programming time.

#### 2.1 Front Panel Quick Reference

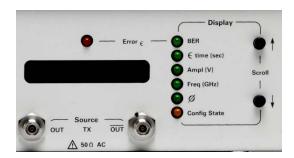

Figure 3. N4962A front panel

**Connectors** RECEIVER: IN, /IN (SMA) – input to error detector (differential or single-ended)

SOURCE: OUT, /OUT (2.92 mm K) - PRBS generator output (differential or single-

ended)

**Display** (display panel) – eight-character display to show display status and configure

system

Error  $\varepsilon$  (light) – indicates errors are being detected by the error detector

#### **Controls**

Local (button & light) – indicates local (vs. remote) control; button selects local control

#### Receiver >

On (button & light) - indicates detector state; button toggles & resets BER

#### Data Path >

PRBS (button & light) – indicates inversion of PRBS signal; button toggles Select Path (button & 3 lights) – data path (disabled, enabled, thru); button cycles

#### Adjust >

Freq (2 buttons) – adjust the internal clock frequency up or down (shown on display)

Ampl (2 buttons) – adjust the PRBS output amplitude up or down (shown on display)

ø (2 buttons) – adjust the detector clock phase up or down (shown on display) Config State (2 buttons) – change value of the currently-displayed configuration state.

#### Display >

Scroll (2 buttons & 6 lights) – select which feature is shown on the display panel:

- BER measured BER (# bit errors / total # bits)

- ε time (sec) elapsed time of BER measurement, in seconds

- Ampl (V) single-ended PRBS generator output amplitude, in volts per side

- Freq (GHz) internal clock frequency, in GHz (10 GHz corresponds to 10 Gb/s)

- Ø BER clock phase adjustment, in degrees (360-degrees = 1 UI)

- Config State- selects one of the configuration states shown in *Table 3*.

Table 3. Configuration state details (shown on display panel, default in BOLD)

| Config State    | Description                                                                                                         | Options                                                                                           |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|

| PAT 2E31        | PRBS generator pattern length                                                                                       | 2E31, 2E23, 2E15, 2E10, 2E7                                                                       |  |

| MS 0.500        | PRBS generator mark space density                                                                                   | <b>0.500</b> (1/2), 0.250 (1/4), 0.125 (1/8)                                                      |  |

| Jitter 0        | _                                                                                                                   | <i>0</i> (low-jitter mode), <i>1</i> (external jitter on)                                         |  |

| Synth 1         |                                                                                                                     | 0 (internal clock off), 1 (Internal clock on)                                                     |  |

| Err00000        | Lowest digits of error counter                                                                                      |                                                                                                   |  |

| ErAd <i>OFF</i> |                                                                                                                     | <b>OFF</b> , 1E0, 1E1,, 1E7 (errors per second)                                                   |  |

| NoData 0        | Error detector data sense                                                                                           | 0 (data sense off), 1 (data sense on)                                                             |  |

| TD= 0010        | Time delay for measurement start (for long length DUT)                                                              | 10-9999 (1/10 <sup>th</sup> of a microsecond)                                                     |  |

| APT=0010        |                                                                                                                     | 0-5000 (1/10 <sup>th</sup> of a millisecond per<br>phase step; default 10 (1ms time per<br>step)) |  |

| 1234R567        | Serial number and FW revision (only the last four digits of the serial number are shown on the front panel display) | none                                                                                              |  |

(Display > Scroll to select state; Adjust > Config State to change value)

#### 2.2 Rear Panel Quick Reference

Figure 4. N4962A rear panel

Connectors

DataThru, DataThru (SMA) - connected to IN, IN when 'thru' data path selected.

PatTrigO (SMA) - PRBS pattern trigger output

TX CKI (SMA) - PRBS generator clock input (default connected to TX CKO)

RX CKI (SMA) – error detector clock input (default connected to RX CKO)

RX CKO (SMA) - internal clock output for error detector

TX CKO (SMA) - internal clock output for PRBS generator

HF TrigO (SMA) - high-frequency (9.90 - 11.35 GHz) clock output

LF TrigO (SMA) - low-frequency (619 - 709 MHz) clock output

Ext CKI (SMA) – low-frequency (619 – 709 MHz) clock input; used to phase lock

with external clock source

JitterI (SMA) – jitter signal input (DC-100 MHz); turn jitter mode on before use

(GPIB) - GPIB connector, conforms to IEEE 488.1 mechanical specification

Label

SN (white area) – N4962A serial number

**Controls**

GPIB (switch panel) - N4962A GPIB address (down is '0', up is '1', LSB is on the

left)

(Default GPIB address as shipped from the factory is 25)

Power (switch) - N4962A is powered when switch is toggled up towards 'Power'

label

Power connector - connects with AC/DC adapter. Use only the supplied AC/DC

adapter.

#### 2.3 Connector Care

Refer to the N4960-90030 N495xA through N498xA Connector Care Reference Guide at www.Keysight.com/find/N4962A.

Inspect the connectors for the following:

- Worn or damaged threads

- Scratches to mating surface

- Burrs and loose metal particles

- Dust or foreign material in the space surrounding the center pin (type K only)

- Ensure that female contacts are straight and aligned

Clean the connectors as described in the following procedure. Cleaning connectors with alcohol shall only be done with the instruments power cord removed, and in a well-ventilated area. Allow all residual alcohol moisture to evaporate, and the fumes to dissipate prior to energizing the instrument.

- 1. Remove any dust or loose particles using a low-pressure air source.

- 2. Moisten a lint-free swab with isopropyl alcohol. Do not saturate the swab.

- 3. Minimize the wicking of the alcohol into the connector structure.

- 4. Clean the mating plane surfaces and threads.

- 5. Allow alcohol to evaporate, and then use a low-pressure air source to blow surfaces clean.

- 6. Make sure no particles or residue remains.

- 7. Inspect connector for damage.

# 3 System Details and Performance Specifications

Specifications describe the instrument's warranted performance. Nonwarranted values are stated as typical. All specifications are valid in a range from 10°C to 40°C ambient temperature after a 30 minute warmup phase. If not otherwise stated, all unused RF inputs and outputs must be terminated with the included 50  $\Omega$  –terminated connectors.

#### 3.1 General

Table 4. General and mechanical parameters of N4962A

| Operating Temperature | +10°C to +40°C                                                                                                                                                                                                                               |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Storage Temperature   | -40°C to +70°C                                                                                                                                                                                                                               |  |  |

| Power Requirements    | 42 W External AC Adaptor (included)  • 100 to 240 VAC, 47 to 63 Hz                                                                                                                                                                           |  |  |

| Physical Dimensions   | Width: 254 mm (10 in), Height: 63.5 mm (2.5 in), Depth: 254 mm (10 in)                                                                                                                                                                       |  |  |

| Weight                | 3.4 kg (7.5 lbs)                                                                                                                                                                                                                             |  |  |

| EMC                   | Complies with European EMC Directive 2004/108/EC  IEC/EN 61326-1  CISPR Pub 11 Group 1, class A  AS/NZS CISPR 11  ICES/NMB-001  This ISM device complies with Canadian ICES-001. Cet appareil ISM est conforme a la norme NMB-001 du Canada. |  |  |

#### 3.2 Safety and Regulatory

#### WARNING

Do not remove instrument covers. There are no user serviceable parts within. Operation of the instrument in a manner not specified by Keysight Technologies may result in personal injury or loss of life.

#### WARNING

To prevent electrical shock, disconnect instrument from mains before cleaning. Use a dry cloth or one slightly dampened with water to clean the external case parts. Do not attempt to clean internally.

#### WARNING

For continued protection against fire hazard, replace fuses, and or circuit breakers only with same type and ratings. The use of other fuses, circuit breakers or materials is prohibited.

#### CAUTION

The Mains wiring and connectors shall be compatible with the connector used in the premise electrical system. Failure, to ensure adequate earth grounding by not using the correct components may cause product damage, and serious injury.

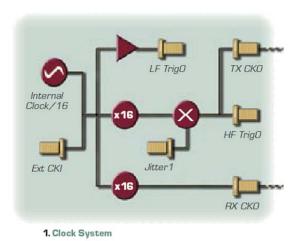

#### 3.3 Internal Clock

The internal clock is generated from a low-frequency (LF) 1/16th-rate clock signal that is multiplied up to the high-frequency (HF) clock rate, 9.90 to 11.35 GHz. The internal HF clock or an external 500 MHz to 12.5 GHz clock is required to trigger the PRBS generator and error detector. The generator and detector operate at 1 bit per clock cycle (10 Gb/s at a clock speed of 10 GHz).

Figure 5. N4962A block diagram - internal clock system

The internal LF 1/16th-rate clock can be phase locked to an external source in order to synchronize the N4962A with the external device. To synchronize the clocks, follow the procedure detailed below. The internal or external LF clock is available from the buffered LF TrigO connector.

To ensure phase lock of an external LF clock applied to the ExtCKI port, the following procedure must be used:

- 1. Turn off the external signal generator RF output

- 2. Set external signal generator to new 1/16th-rate RF frequency

- 3. Set N4962A to new HF frequency value (or nearest value)

- 4. Turn on the external signal generator RF output

- 5. Turn off the N4962A internal synthesizer (change "synth" to 0)

Users wanting to change frequency from this condition should:

- 1. Turn on the internal synthesizer (synth to 1)

- 2. Turn off the external signal generator RF output

- 3. Set the external signal generator to the new 1/16th-rate frequency

- 4. Set the N4962A to new HF frequency value (or nearest value)

- 5. Turn on the external signal generator RF output

- 6. Turn off the N4962A internal synthesizer (synth to 0)

The clocks should now be phase locked to the new frequency.

Table 5. Parameters for N4962A internal low-frequency clock (LF TrigO, Ext CKI)

| Frequency           | 618.75 to 709.375 MHz                                       |  |

|---------------------|-------------------------------------------------------------|--|

| Max input amplitude | Ext CKI: 2.0 Vpp (+10 dBm)                                  |  |

| Output power        | LF TrigO, 0.5 V pp typical                                  |  |

| Connector           | Female SMA, single-ended, AC coupled, $50~\Omega$ impedance |  |

NOTE

The LF 1/16th rate clock must phase lock to the data rate clock.

The LF clock is multiplied up to HF clock frequencies and is split into two output paths: a transmit clock for the PRBS generator, TX CKO, which can be modulated with an external jitter input signal, and a receive clock for the error detector, RX CKO. Both outputs are buffered. The clock outputs are connected by default to the input clock connectors for the PRBS generator and error detector, TX CKI and RX CKI, with a pair of coaxial cable loops.

To trigger the PRBS generator and error detector with an external 500 MHz to 12.5 GHz clock, remove the coax loops and apply the external source to TX CKI and RX CKI. The generator and detector must be triggered with the same phase-synchronous clock. Ensure that at least 0 dBm (630 mV pp) is applied to the TXCKI and the RXCKI input. Do not apply more than +5 dBm (1.1 V pp) to these inputs.

Table 6. Parameters for N4962A internal clock (TX CKO, RX CKO, HF TrigO)

| Frequency    | 9.90 to 11.35 GHz, over-programmable to 9.98 GHz <sup>1</sup>                              |  |

|--------------|--------------------------------------------------------------------------------------------|--|

| Resolution   | 10 MHz front-panel, 1 MHz GPIB                                                             |  |

| Output power | TX CKO, Typ: +4 dBm (1 V pp) RX CKO, Typ: +4 dBm (1 V pp) HF TrigO, Typ: +6 dBm (1.3 V pp) |  |

| Connector    | Female SMA, single-ended, AC coupled, 50 $\Omega$ impedance                                |  |

<sup>&</sup>lt;sup>1</sup> Internal clock is over-programmable down to 9.98 GHz, but performance below 9.90 GHz is not guaranteed.

The TX clock, available from the buffered HF TrigO and TX CKO connectors, features the optional addition of an external jitter signal.

To add jitter to the PRBS clock, and therefore to the PRBS output signal, switch into jitter-injection mode by changing the Config State "Jitter" setting to 1, and apply a DC to 100 MHz sinusoid to the Jitterl connector. The jitter input signal will be FM modulated onto the clock; the amount of added jitter corresponds to the amplitude of the input signal.

The Jitter setting of 0 will still FM modulate any signal under 100 kHz. To properly ensure no jitter is added, disconnect any source from the Jitterl connector.

Table 7. Parameters for N4962A internal clock jitter injection (Jitterl)

| Frequency     | Typ: DC to 100 MHz                                          |

|---------------|-------------------------------------------------------------|

| Input Voltage | 2 V pp max                                                  |

| Jitter Added  | Up to 5 UI ≤ 2 MHz, up to 0.15 UI ≥ 10 MHz                  |

| Connector     | Female SMA, single-ended, DC coupled, 50 $\Omega$ impedance |

NOTE

Switch to jitter-injection mode before applying a signal to Jitterl

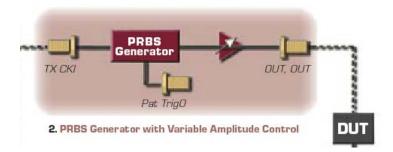

#### 3.4 PRBS Generator

The PRBS generator creates a continuous bit stream based on the configuration settings and the TX CKI input clock rate. The internal clock can be used for 9.90 to 11.35 Gb/s operation, or an external clock can be used for 500 Mb/s to 12.5 Gb/s operation. The PRBS generator and error detector must be clocked at the same rate.

The PRBS generator configuration includes selectable pattern length, mark space density ratio, and digital error injection settings. The PRBS also features polarity control to allow for both inverting and non-inverting DUTs. These configuration settings are detailed in Section 4.2.

Figure 6. N4962A block diagram - PRBS generator

The PRBS output bit stream is amplified by an adjustable gain stage. The output amplitude ranges from 300 mV pp to 1800 mV pp per output (0.6 V pp to 3.6 V pp differential) in 10 mV pp increments.

The amplified PRBS output signal is available from the single-ended or differential 2.92 mm K-connector OUT and /OUTconnectors on the front panel. The PRBS generator also generates a pattern trigger output, available from Pat TrigO on the back panel, which changes state after 32 complete PRBS bit streams have been generated. Pat TrigO has a frequency equal to (clock\_rate) / (32 \* bit\_pattern\_length). Users of Pat TrigO should verify that its output is a square wave in order to ensure proper pattern triggering.

Table 8. Parameters for N4962A PRBS generator (OUT, OUT)

| Data rate                                             | 0.5 to 12.5 Gb/s                                                                 |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------|--|

| PRBS patterns                                         | 2 <sup>n</sup> – 1, n=7, 10, 15, 23, 31                                          |  |

| Mark space density                                    | 1/2, 1/4, 1/8                                                                    |  |

| Pattern invert                                        | available for all patterns                                                       |  |

| Error injection                                       | selectable uniform rate                                                          |  |

| Error injection rates                                 | 1 x10 <sup>n</sup> errors per second, n = 1, 2, 3, 4, 5, 6, 7                    |  |

| Data output amplitude300 to 1800 mV pp (single-ended) |                                                                                  |  |

| Data output amplitude resolution                      | 10 mV                                                                            |  |

| Data output jitter                                    | 1.1 ps rms typical at 10 Gb/s                                                    |  |

| Data output rise/fall time (20% to 80%)               | 18 ps typical, 23 ps maximum                                                     |  |

| Data output external interface                        | (May be operated single end without unused output terminated into 50 $\Omega$ .) |  |

| TXCKI Clock input frequency range                     | 0.5 to 12.5 GHz                                                                  |  |

| TXCKI Clock input amplitude range                     | 0 to +5 dBm (630 mV pp to 1.1 V pp)                                              |  |

| TXCKI Clock input external interface                  | AC coupled, $50~\Omega$ nominal, female SMA                                      |  |

The PRBS bit stream consists of data generated by one of five patterns, listed in Table 9. The pattern length is a system configuration setting, selected by changing the Config State "PAT xxxx" setting, detailed in Section 4.2.3.

Pattern Config State Polynomial Tone Spacing (10Gb/s) ITU Standard  $2^{31} - 1$ 2E31  $X^{31} + X^{28} + 1 = 0$ ITU-T 0.150 4.67 Hz  $2^{23} - 1$ 2E23 1.19 kHz ITU-T 0.150  $X^{23} + X^{18} + 1 = 0$  $2^{15} - 1$ 2E15  $X^{15} + X^{14} + 1 = 0$ 305 kHz ITU-T 0.150 2E7 ITU-T V.29  $2^7 - 1$  $X^7 + X^6 + 1 = 0$ 78.7 MHz

Table 9. N4962A PRBS generator patterns

#### 3.5 Error Detector

The error detector counts errors in the input bit stream, based on the configuration settings and the RX CKI input clock rate. The internal clock can be used for 9.90 to 11.35 Gb/s operation, or an external clock can be used for 500 Mb/s to 12.5 Gb/s operation. The PRBS generator and error detector must be clocked at the same rate.

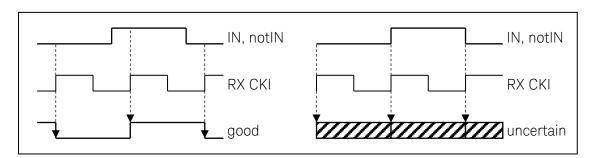

The error detector samples the input bit stream on the rising edge of the clock. If the clock transition occurs near the data transition – that is, if the clock and the data are changing at the same time – the sampled data value is uncertain, which may result in high BER. This is illustrated in Figure 13.

To ensure the clock and data transition points are correctly offset, the error detector features a user-adjustable 360-degree electronic phase shifter. The phase shifter delays the clock input to the detector, allowing the user to select the optimal sampling point. The N4962A can automatically adjust the receiver phase to the best sampling point, detailed in Section 4.6.

3. Error Detector with Electronic Phase Adjustment

Figure 7. N4962A block diagram – error detector

The error detector compares the sampled input bit stream to a separate internal PRBS signal generated with the same configuration settings as the PRBS generator. The error detector automatically synchronizes its internal PRBS with the incoming bit stream, in a process called 'training'. The error detector is in training mode when off, and switches to error-counting mode when the detector is turned on. Assuming the training was successful, and the error detector was able to synchronize with the input bit stream, the detector starts counting errors less than 1 us after turning on.

Training the error detector takes approximately 50 us, and requires a somewhat error-free input bit stream. If the detector is unable to synchronize with the incoming bit stream, the measured BER will be very high. This is only an issue for bit error rates higher than 5E-01 (50% of incoming bits are errors); for most applications with high BER, the detector will auto-synchronize very rapidly.

The phase adjustment offers 2 degree resolution capability from 5 Gb/s to 12.5 Gb/s. The linearity accuracy of phase is limited to 10 degree steps for operation from 5 Gb/s to 12.5 Gb/s. For external clock rates below 5 GHz the specific values of 0, 90, 180 or 270 degrees are required for the receiver clock phase alignment in order to obtain correct BER results. Employing the receiver's auto-phase feature or manual adjustment to the receiver phase resulting in any other phase values may lead to receive errors. Users requiring greater precision in receiver clock and data alignment below 5 GHz can achieve this result using external means such as a mechanical phase-shifter.

Table 10. Parameters for N4962A error detector (IN, /IN)

| Data rate                                                | 0.5 to 12.5 Gb/s                                                               |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------|--|

| PRBS patterns                                            | 2 <sup>n</sup> - 1, n=7, 10, 15, 23, 31                                        |  |

| Data input sensitivity (single ended)                    | 0.1 V pp typical                                                               |  |

| Data input voltage range                                 | 2 Vpp max (single-ended)                                                       |  |

|                                                          | ± 0.5 V DC common mode voltage max                                             |  |

| Data input phase adjust                                  | 0 to 360°                                                                      |  |

| Data input phase adjust resolution                       | 2° for data rates ≥ 5 Gb/s                                                     |  |

|                                                          | 90° for data rates < 5 Gb/s                                                    |  |

| Data input external interface                            | Differential. DC coupled, 50 $\Omega$ nominal, female SMA                      |  |

|                                                          | (May be operated single end without unused input terminated into 50 $\Omega$ ) |  |

| <b>RXCKI Clock input frequency range</b> 0.5 to 12.5 GHz |                                                                                |  |

| RXCKI Clock input amplitude range                        | 0 to +5 dBm (630 mV to 1.1 V pp)                                               |  |

| RXCKI Clock input external interface                     | AC coupled, 50 $\Omega$ nominal, female SMA                                    |  |

After the error detector synchronizes with the incoming bit stream, and is turned on, it compares the sampled input bit stream against the synchronized comparison signal. The detector counts the number of bit errors and the total number of bits, and generates the BER measurement (# bit errors / total # bits). The error detector counter sizes have been selected to enable long-term BER measurements without counter overflow, detailed in Table 11. The measurement will stop if one of these counters reaches the maximum value.

Table 11. N4962A error detector counter specifications

| Counter           | Counter Size | Overflow Time at 12.5 Gb/s                  |

|-------------------|--------------|---------------------------------------------|

| Bit errors        | 48 bits      | ~12.5 hours (0.5 BER), 2606 days (1E-4 BER) |

| Total bits        | 56 bits      | 1601 hours (67 days)                        |

| Elapsed time bits | 22 bits      | 4194304 seconds (48.5 days)                 |

#### 3.6 Data Path

The N4962A can operate in one of three data path configurations. The data path can be set from the front panel, detailed in Section 4.2.2, or through GPIB remote commands.

The current data path is indicated with the front panel lights. One of the three lights will be lit. The lights are labeled Disabled, Enabled, and Thru.

The Disabled data path is selected by default; this disables the PRBS output and can be considered a 'safe mode' to be used to avoid DUT damage. The Enabled data path turns on the PRBS output. The Thru data path connects the IN/IN signals directly to the DataThru and /DataThru output connectors on the back panel, with an associated switching loss in the data path. Errors are not counted. The data path configurations are summarized in Table 12.

The Thru feature allows users to ensure the quality and amplitude of the received signal is measured with a sampling scope without disconnecting the cables from the N4962A. Once the path loss is determined, an accurate estimate of the eye quality and amplitude can be determined for every test.

Table 12. N4962A data path configurations

| Data Path light | Configuration                              | PRBS generator | Additional path loss |

|-----------------|--------------------------------------------|----------------|----------------------|

| Disabled        | IN/IN connected to error detector, default | Disabled       |                      |

| Enabled         | IN/IN connected to error detector          | Enabled        |                      |

| Thru            | IN/IN connected to<br>DataThru/DataThru    | Enabled        | Typ. 4 dB            |

# 4 Operation

The following section provides detailed information regarding the use of the N4962A serial BERT 12.5 Gb/s. Please refer to the front and rear panel quick reference, in Section 2, for abbreviated information.

#### 4.1 General Information

The N4962A serial BERT 12.5 Gb/s should be used in accordance with the following:

- Read and follow operating instructions; do not exceed min/max specifications.

- Use ESD protection at all times, but especially when handling RF input/outputs; ground coaxial cable conductor pins before use to remove static buildup.

- Situate the instrument away from heat sources.

- Do not block airflow to the fan; do not allow foreign material into enclosure.

- Always use provided AC adaptor. Do not power the unit with a different adaptor. Do not modify the power plug or wall outlet to remove the third (ground) pin.

- Do not drop or shake the instrument; minimize vibration; handle with care.

- There are no user-serviceable parts within. Return damaged instruments for factory-authorized repair. Refer to instrument warranty for more information.

#### 4.1.1 Performance Recommendations

Follow the following recommendations for best performance:

- When using differential mode connection for IN and /IN, OUT and /OUT, or DataThru and /DataThru, ensure the cables are phase balanced. If the electrical length of one cable is a significant fraction of a unit interval longer than the other, the quality of the differential signal will be degraded and BER will increase.

- Keep cable lengths short and minimize number of cable bends.

- Terminate all unused RF connectors with 50  $\Omega$  terminations.

#### 4.1.2 Connector Care

The N4962A serial BERT 12.5 Gb/s features high-quality SMA connectors, and two 2.92 mm K-connectors for the front-panel OUT and /OUT interface. Keysight Technologies does not recommend using male SMA connectors with the female K-connectors; the male SMA pin has looser tolerances than the female K sleeve, and may damage the connector. Connector damage will degrade signal fidelity.

Refer to the N4960-90030 N495xA through N498xA Connector Care Reference Guide at <a href="https://www.Keysight.com/find/N4962A">www.Keysight.com/find/N4962A</a>.

Keysight Technologies also recommends the following:

- Use a 7-10 in-lbs torque wrench when attaching connectors.

- Consider using connector savers to prolong performance and minimize damage.

- Differential connectors may be used single-ended if second end terminated in 50  $\Omega$ .

- Terminate all unused RF connectors with 50  $\Omega$  terminations.

#### 4.2 Front Panel Interface

Figure 8. N4962A front panel

The N4962A front panel indicates system configuration, and can be used for local operation of the instrument. The front panel contains three groupings of buttons and lights (local, receiver, and data path controls; configuration adjustment controls; and display selection controls), a display panel and error light, and the PRBS generator (SOURCE) and error detector (RECEIVER) connectors.

The PRBS generator connectors, labeled SOURCE, are 2.92 mm K-connectors. The PRBS output is available in single-ended or differential form from these connectors. The output signal is specified in Section 3.3.

The error detector connectors, labeled RECEIVER, are SMA connectors. The input bit stream (from the output of the DUT) can be connected in single-ended or differential form to these connectors. The input signal requirements are specified in Section 3.4.

To use either the SOURCE or RECEIVER connector pairs in a single-ended configuration, terminate the unused RF connector in a 50  $\Omega$  termination. To use the connectors differentially, ensure the cables used are phase balanced – the same electrical length – to avoid errors caused by out-of-phase differential signals.

#### 4.2.1 Front Panel – Display Panel

Figure 9. N4962A front panel – display panel

Table 13. N4962A front panel – display panel

| Text    | Туре             | Description                                                                                                                                                                                                                                                                                       | Default    |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Error e | light            | The error light is lit for a short period of time when the error detector identifies a bit error. If the error light is solid red, many errors are being detected.                                                                                                                                | N/A        |

|         | display<br>panel | The eight-character display shows the current configuration option selected by using the <i>Display-&gt;</i> Scroll UP and DOWN buttons.  When one of the configuration <i>Adjust</i> buttons (Freq, Ampl, Ø) are pressed, the display will briefly show the corresponding configuration setting. | Freq (GHz) |

# 4.2.2 Front Panel - Local, Receiver, and Data Path Controls

Figure 10. N4962A front panel – local, receiver, and data path controls

Table 14. N4962A front panel – local, receiver, and data path controls

| Text                 | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      | Default |

|----------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Local                | button<br>& light | Light indicates local control:  ON when front-panel control is enabled;  OFF when remote GPIB interface is in use.  Button switches to local control.                                                                                                                                                                                                                                                                                            | ON      |

| Receiver<br>-><br>On | button<br>& light | Light indicates error detector is ON, and:  Elapsed time is accumulating; Total bits and errors are being counted; BER measurement is being calculated.  If detector is ON, pressing button: Saves state (# bits, errors, & seconds); Turns off detector; Puts detector into training mode (for auto-synchronization of incoming bit stream).  If detector is OFF, pressing button: Resets state (# bits, errors, & seconds); Turns on detector. | OFF     |

| Text                                      | Туре                    | Description                                                                                                                                                                                                                                                                                                                                                | Default  |

|-------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Data Path -> PRBS Invert                  | button<br>& light       | Light indicates inverted PRBS generator output:  OFF when PRBS bit stream is not inverted; ON when PRBS bit stream is inverted.  Button toggles the output inversion ON and OFF.  Inverting the bit stream after training and turning on the detector will result in a BER measurement approaching 1EO.                                                    | OFF      |

| Data Path -> Disabled Enabled Thru (none) | button<br>& 3<br>lights | Light indicates which data path is selected:  Disabled: IN and /IN connected to error detector, PRBS generator is disabled; Enabled: IN and /IN connected to error detector, PRBS generator is enabled; Thru: IN and /IN connected to DataThru and /DataThru with some path loss, PRBS generator is enabled;  Button cycles between the data path options. | Disabled |

# 4.2.3 Front Panel – Configuration Adjustment Controls

Figure 11. N4962A front panel – configuration adjustment controls

Table 15. N4962A front panel – configuration adjustment controls

| Text                 | Туре                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Default  |

|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Adjust<br>-><br>Freq | UP and DOWN<br>buttons | Buttons adjust internal clock frequency by 0.01 GHz:  • UP increases frequency (max 11.35 GHz); • DOWN decreases frequency (min 9.90 GHz)¹.  Display will briefly show new frequency setting after pressing either button, and then switches back to previously-displayed setting.  When using an external clock (Synth = 0), the Freq adjust range is increased to 500 MHz min, 12.5 GHz max. The N4962A frequency setting should be set to the frequency of the external clock so that the N4962A frequency dependent parameters are correctly set. | 10.0 GHz |

| Adjust<br>-><br>Ampl | UP and DOWN<br>buttons | Buttons adjust PRBS output amplitude by 10 mV:  • UP increases amplitude (max 1800 mV);  • DOWN decreases amplitude (min 300 mV).  Display will briefly show new amplitude setting after pressing either button, and then switches back to previously-displayed setting.                                                                                                                                                                                                                                                                              | 500 mV   |

| Text                   | Туре                      | Description                                                                                                                                                                                                                                                                                                                    | Default                                                                                     |

|------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Adjust<br>-><br>Ø      | UP and DOWN<br>buttons    | Buttons adjust BER clock phase by 2 degrees from 5 to 12.5 GHz, and in 90-degree increments below 5 GHz:  • UP increases phase offset (max 358, min 0)  • DOWN decreases phase offset  Display will briefly show new clock phase setting after pressing either button, and then switches back to previously-displayed setting. | 0 degrees                                                                                   |

| Adjust -> Config State | PLUS and MINUS<br>buttons | MS 0.500     options: 0.500, 0.250, 0.125  PRBS output mark space density setting, which is the ratio of logic 1's to the total of logic 1's and logic 0's. A mark space density of 0.5 (1/2)                                                                                                                                  | PAT 2E31<br>MS 0.500<br>Jitter 0<br>Synth 1<br>Err00000<br>ErAd OFF<br>NoData 0<br>1234R567 |

| Text | Туре | Description                                                                                             | Default |

|------|------|---------------------------------------------------------------------------------------------------------|---------|

| TOAL | Турс | ·                                                                                                       | Deladit |

|      |      | <ul><li>Synth 1</li><li>o options: 0, 1</li></ul>                                                       |         |

|      |      | options. 6, 1                                                                                           |         |

|      |      | Internal clock setting: 0 = use external clock                                                          |         |

|      |      | (internal clock turned off); 1 = use internal clock.                                                    |         |

|      |      | - F**00000                                                                                              |         |

|      |      | • Err00000                                                                                              |         |

|      |      | Five-digit error detector error counter, included for                                                   |         |

|      |      | low BER applications, or for testing external error                                                     |         |

|      |      | injection. The counter accumulates errors since the                                                     |         |

|      |      | detector was reset, and wraps around 99999. This counter should not be used as the authoritative        |         |

|      |      | number of errors counted.                                                                               |         |

|      |      |                                                                                                         |         |

|      |      | <ul> <li>ErAd OFF</li> <li>o options: OFF, 1E0, 1E1, 1E2,, 1E7</li> </ul>                               |         |

|      |      | ο ομιοίις. στι, τεο, τει, τε2,, τε                                                                      |         |

|      |      | Digital error injection setting, which indicates how                                                    |         |

|      |      | many bit inversions occur per second. OFF                                                               |         |

|      |      | indicates no bit errors are injected, 1E0 indicates 1 error per second, 1E7 indicates 10 million errors |         |

|      |      | per second. To find the injected BER, divide by the                                                     |         |

|      |      | clock frequency. For example, at a setting of 1E2                                                       |         |

|      |      | (100) errors per second, the BER will be 1E-8 at a clock rate of 10 GHz, or 8E-9 at 12.5 GHz. See       |         |

|      |      | Table 16.                                                                                               |         |

|      |      |                                                                                                         |         |

|      |      | When Display->Ø is selected from the display                                                            |         |

|      |      | selector, pressing the Adjust->Config State PLUS button will prompt the N4962A to automatically         |         |

|      |      | determine the optimum detector clock phase. This                                                        |         |

|      |      | is detailed further in Section 4.6.                                                                     |         |

|      |      | NoData 0                                                                                                |         |

|      |      | NoData U     o options: 0, 1                                                                            |         |

|      |      |                                                                                                         |         |

|      |      | NoData option helps with the initialization                                                             |         |

|      |      | sequence. When the source is used with the error                                                        |         |

|      |      | detector, this value should be set to 1. This helps with a condition when all zeros are loaded into the |         |

|      |      | error detector's input, which can erroneously cause                                                     |         |

|      |      | bad error rate numbers. This should be set to 0                                                         |         |

| Text | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                   | Default |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|      |      | when using a different manufacturer's pattern<br>generator, or a known good signal is used with the<br>N4962A source.                                                                                                                                                                                                                                                                                                         |         |

|      |      | <ul> <li>TD= 0010</li> <li>Min 0010 (1 μs), max 6500 (650 μs)</li> </ul>                                                                                                                                                                                                                                                                                                                                                      |         |

|      |      | The TD ("Training Delay") option delays the start of the error detector after the BER measurement has been initiated. This feature is used in conjunction with the NoData function. This delay, listed in 1/10th microseconds (default 1us), allows the PRBS pattern time to transition through the DUT before measurement start. This can be very important for DUTs containing a long electrical length or an optical loop. |         |

|      |      | <ul> <li>APT=0010</li> <li>Min 0001 (0.1 ms), max 5000 (500 ms)</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |         |

|      |      | The APT ("Autophase Time") option specifies the autophase search algorithm measurement time at each 2-degree phase point. This option allows the user to specify the measurement depth of the autophase algorithm.                                                                                                                                                                                                            |         |

|      |      | APT allows a tradeoff between the search time and positioning accuracy of the autophase algorithm. Because 180 phase points are measured, this option may increase the autophase time to a total of 90+ seconds.                                                                                                                                                                                                              |         |

|      |      | The confidence interval of a BER measurement, with frequency (GHz), gate time (seconds), and measurement depth (BER) is:                                                                                                                                                                                                                                                                                                      |         |

|      |      | $CI = 1 - e^{-Freq(GHz) \times time(s) \times MeasDepth(BER)}$                                                                                                                                                                                                                                                                                                                                                                |         |

|      |      | • 1234R111<br>o options: none                                                                                                                                                                                                                                                                                                                                                                                                 |         |