Agilent

M9330A Series

PXI-H Arbitrary Waveform

Generator

Option Y1176A

Synchronization Cable Kits

Installation Note

Edition, January 7, 2011 M9330-90007

NOTICE: In August 2014, Agilent Technologies' former Test and Measurement business became Keysight Technologies. This document is provided as a courtesy but is no longer kept current and thus will contain historical references to Agilent. For more information, go to **www.keysight.com.**

## **Notices**

© Agilent Technologies, Inc. 2005, 2007, 2010

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Agilent Technologies, Inc. as governed by United States and international copyright laws.

Microsoft® and Visual Studio® are trademarks or registered trademarks of Microsoft Corporation in the United States and/or other countries.

PCI-SIG®, PCI™, PCI Express®, PCIe®, EXPRESSMODULE™, PCI-X™, PCI-X™ 66, PCI-X™ 133, PCI-X™ 266, PCI-X™ 533, PCI HOT PLUG™, and MINI PCI™ are registered trademarks and/or service marks of PCI-SIG.

#### **Manual Part Number**

M9330-90007

#### **Edition**

Edition, January 7, 2011

Printed in USA

Agilent Technologies, Inc. 1400 Fountaingrove Pkwy Santa Rosa, CA 95403

#### Warranty

The material contained in this document is provided "as is," and is subject to being changed, without notice, in future editions. Further, to the maximum extent permitted by applicable law, Agilent disclaims all warranties, either express or implied, with regard to this manual and any information contained herein, including but not limited to the implied warranties of merchantability and fitness for a particular purpose. Agilent shall not be liable for errors or for incidental or consequential damages in connection with the furnishing, use, or performance of this document or of any information contained herein. Should Agilent and the user have a separate written agreement with warranty terms covering the material in this document that conflict with these terms, the warranty terms in the separate agreement shall control.

## **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### **Restricted Rights Legend**

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Agilent Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

## **Safety Notices**

#### **CAUTION**

A **CAUTION** notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a **CAUTION** notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

Internal Clock Synchronization Using Continuous Mode 8

External Clock Synchronization Using Continuous Mode 11

## 1.0 GHz Clock Rate

## **Description**

The Agilent Technologies M9330A Series AWG Module Synchronization Cable Kit is designed for use with a clock rate of 1.0 GHz. The cable kit is a set of eight cable assemblies, one adapter, and two power dividers that provide the necessary interconnection for two-M9330A Series AWG module synchronization.

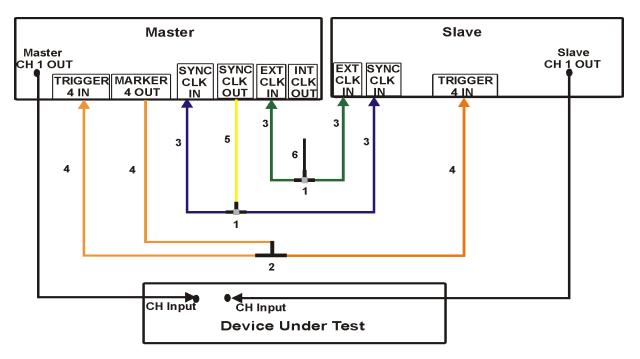

## **Cable Kit Contents**

Figure 1 Cable Kit Contents

| ltem | Quantity | Description                           | Part Number |

|------|----------|---------------------------------------|-------------|

| 1    | 2        | DC to 26.5 GHz power divider, APC 3.5 | 11636B-FG   |

| 2    | 1        | Adapter-Coax Tee                      | 1250-0670   |

| 3    | 4        | Cable Assembly 10 in SMA              | 5062-6685   |

| 4    | 3        | Cable Assembly                        | 8120-5016   |

| 5    | 1        | Cable Assembly 16 in SMA              | 5062-6689   |

# Cabling, 1.0 GHz Clock Rate

- 1- Power divider

- 2 SMB Adapter Tee

- 3 SMA Cable Assembly 10 in

- 4 SMB Cable Assembly

- 5 SMA Cable Assembly 16 in

- 6 External Clock In

Note: The CH 1 OUT customer furnished cables from the Master and Slave modules must be of equal length.

The external clock cable is also customer furnished.

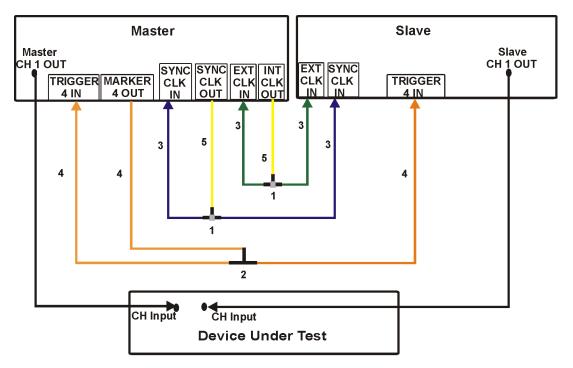

## 1.25 GHz Clock Rate

## **Description**

The Agilent Technologies M9330A Series AWG Module Synchronization Cable Kit is designed for use with internal clock rate of 1.25 GHz. The cable kit is a set of seven cable assemblies, three adapters, and two power dividers that provide the necessary interconnection for two-M9330A Series AWG module synchronization.

## **Cable Kit Contents**

| ltem | Quantity | Description                           | Part Number |

|------|----------|---------------------------------------|-------------|

| 1    | 2        | DC to 26.5 GHz power divider, APC 3.5 | 11636B-FG   |

| 2    | 1        | Adapter-Coax Tee                      | 1250-0670   |

| 3    | 4        | Cable Assembly 10 in SMA              | 5062-6685   |

| 4    | 3        | Cable Assembly                        | 8120-5016   |

| 5    | 2        | Adapter                               | 1250-1788   |

- 1- Power divider

- 2 SMB Adapter Tee

- 3 SMA Cable Assembly 10 in

- 4 SMB Cable Assembly

- 5 Adapter

Note: The CH 1 OUT customer furnished cables from the Master and Slave modules must be of equal length.

## Synchronizing Two M9330A Series AWG Modules

## **Internal Clock Synchronization Using Continuous Mode**

When synchronizing two-M9330A Series AWG modules using the internal clock, one unit is designated as the Master and the other unit is designated as the Slave. The Master unit sources the sample clock and the sync clock signals. These signals are split and fed to the synchronized modules (the Master as well as the Slave).

The internal sample clock operates at 1.25 GHz and provides the final retiming of the analog output from each M9330A Series AWG module. Any skew in the sample clock cable delays between the modules will result in the same skew in the analog outputs. The sample clock signal is split with a matched passive divider and the cable lengths are matched. The resulting skew is small and repeatable.

## **Required Equipment**

- · M9330A Series AWG module

- PXI compliant chassis

- Embedded controller or PXI interface link

- Cable Kit

#### **Customer Furnished Cables**

SMA to BNC Cable (2 each, equal length)

#### **Procedure Using a Software Marker**

- 1 Start with the system turned off.

- 2 Cable the equipment.

#### **Selecting the Master Unit**

- 1 Open an M9330A Control Utility session (double-click the M9330A icon on the desktop).

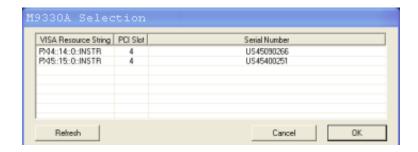

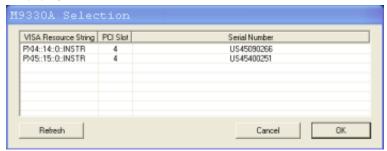

- 2 Highlight the Master unit in the **M9330A Selection** window list and click **OK**.

- 1 Select the desired signal conditioning path.

- 2 Select the desired waveform file.

- 3 Select the Clock tab.

- 4 From the SYNC CLK IN drop-down list, select Master.

Notice the following changes to the graphical user interface that are automatically configured when the Master unit is assigned:

#### Clock tab

- the internal clock is no longer driving the sample clock

- the sample clock and sync clock out are driven by the external clock in signal

- · the sync clock in signal communicates with the sequencer

#### Markers tab

Marker 4 is assigned to a Software marker and is grayed out

## Triggers tab

Start trigger is assigned to Trigger 4 and is grayed out

#### **Selecting the Slave Unit**

- 1 Open a second M9330A Control Utility session.

- 2 Highlight the unit designated as the Slave in the M9330A Selection window list and click OK.

- 3 Select the desired signal conditioning path

- 4 Select the desired waveform file.

- 5 Select the Clock tab.

- **6** From the **SYNC CLK IN** drop-down list, select **Slave**.

Notice the changes to the graphical user interface that are automatically configured when the Slave unit is assigned:

#### **Clock tab**

- · the internal clock is disabled

- the sample clock is driven by the external clock in signal

- · the sync clock out is disabled

- the sync clock in signal communicates with the sequencer

## **Triggers tab**

Start trigger is assigned to Trigger 4 and is grayed out

### **Initiating Synchronous Playback**

- 1 In the **Quick Play** area of the Slave GUI, select **Play**. This arms the waveform playback.

- 2 In the **Quick Play** area of the Master GUI, select **Play**. This initiates synchronous waveform playback.

NOTE

You can view the output on an oscilloscope by setting **Marker 1** on the **Master** module to **Waveform Start** and cabling the marker output to trigger the oscilloscope.

## **External Clock Synchronization Using Continuous Mode**

When synchronizing two modules using an external clock, one unit is designated as the Master and the other unit is designated as the Slave. The Master unit sources the sample clock and the sync clock signals. These signals are split and fed to the synchronized modules (the Master as well as the Slave).

The external sample clock provides the final retiming of the analog output from each AWG. Any skew in the sample clock cable delays between the modules will result in the same skew in the analog outputs. The sample clock signal is split with a matched passive divider and the cable lengths are matched. The resulting skew is small and repeatable.

### **Required Equipment**

- M9330A Series AWG module

- PXI compliant chassis

- Embedded controller or PXI interface link

- Cable Kit

#### **Customer Furnished Cables**

SMA to BNC Cable (2 each, equal length)

#### **Procedure Using a Software Marker**

- 1 Start with the system turned off.

- 2 Cable the equipment.

#### **Selecting the Master Unit**

- 1 Open an M9330A Control Utility session (double-click the M9330A icon on the desktop).

- Highlight the Master unit in the M9330A Selection window list and click OK.

- 3 Select the desired signal conditioning path.

- 4 Select the desired waveform file.

- 5 Select the Clock tab.

- 6 Enable EXT CLK IN.

- 7 Enter the external clock frequency.

- 8 From the SYNC CLK IN drop-down list, select Master.

Notice the following changes to the graphical user interface that are automatically configured when the Master unit is assigned:

#### Clock tab

- the internal clock is no longer driving the sample clock

- the sample clock and sync clock out are driven by the external clock in signal

- · the sync clock in signal communicates with the sequencer

#### Markers tab

· Marker 4 is assigned to a Software marker and is grayed out

## **Triggers tab**

Start trigger is assigned to Trigger 4 and is grayed out

#### **Selecting the Slave Unit**

- 1 Open a second M9330A Control Utility session.

- 2 Highlight the unit designated as the Slave in the M9330A Selection window list and click **OK**.

- 3 Select the desired signal conditioning path.

- 4 Select the desired waveform file.

- 5 Select the Clock tab.

- 6 From the **SYNC CLK IN** drop-down list, select **Slave**.

Notice the changes to the graphical user interface that are automatically configured when the Slave unit is assigned:

#### **Clock tab**

- the internal clock is disabled

- the sample clock is driven by the external clock in signal

- · the sync clock out is disabled

- the sync clock in signal communicates with the sequencer

## **Triggers tab**

Start trigger is assigned to Trigger 4 and is grayed out

#### **Initiating Synchronous Playback**

- 1 In the **Quick Play** area of the Slave GUI, select **Play**. This arms the waveform playback.

- 2 In the **Quick Play** area of the Master GUI, select **Play**. This initiates synchronous waveform playback.

You can view the output on an oscilloscope by setting **Marker 1** on the **Master** module to **Waveform Start** and cabling the marker output to trigger the oscilloscope.

Installation