# M5300A PXIe RF AWG Modules

Four CH, DC-16 GHz RF, 2 GHz IBW, 14-bits resolution

# **Notices**

# **Copyright Notice**

© Keysight Technologies 2025

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

#### **Trademarks**

UNIX is a registered trademark of UNIX System Laboratories in the U.S.A. and other countries. Target is copyrighted by Thru-Put Systems, Inc.

# **Manual Part Number**

M5300-91002

#### Edition

1.8, August 2025

Available in electronic format only

#### Published by

Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

# **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

**Declaration of Conformity**

Declarations of Conformity for this product and for other Keysight products may be downloaded from the Web. Go to <a href="http://www.keysight.com/go/conformity">http://www.keysight.com/go/conformity</a> and click on "Declarations of Conformity." You can then search by product number to find the latest Declaration of Conformity.

#### **U.S. Government Rights**

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS")

227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

#### Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANT-

ABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

# **Safety Information**

#### CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# Keysight Cybersecurity

#### **Product and Solution Cybersecurity**

Keysight is dedicated to ensuring the cybersecurity of its products and solutions. For detailed information, visit Product and Solution Cybersecurity.

#### Report a Product Cybersecurity Issue

If you encounter a cybersecurity issue with a Keysight product, report it immediately at: Product Cybersecurity Issue Reporting.

#### Responsible Disclosure Program

Keysight encourages responsible disclosure of security vulnerabilities. For more details, visit Responsible Disclosure Program.

#### **Product Software Updates**

Keysight releases periodic software updates to fix known defects, incorporate product enhancements, and address cybersecurity vulnerabilities, if any. Ensure that your product software is always up to date. To search for software updates for your product, visit the Keysight Technical Support page at: <a href="https://www.keysight.com/find/M5300A">https://www.keysight.com/find/M5300A</a>.

#### User Documentation

User documentation includes comprehensive information on features that may impact the secure deployment, use, and decommissioning of our products. This includes details on exposed network ports, the use of cryptography and authentication, and firmware security settings, if necessary.

# Safety Summary

The following general safety precautions must be observed during all phases of operation of this instrument. Failure to comply with these precautions or with specific warnings or operating instructions in the product manuals violates safety standards of design, manufacture, and intended use of the instrument. Keysight Technologies assumes no liability for the customer's failure to comply with these requirements. Product manuals are provided on the Web. Go to www.keysight.com and type in your product number in the Search field at the top of the page.

# WARNING

Do not use the device if it is damaged. Contact your Keysight sales representative for replacement of device.

# WARNING

Verify that all safety precautions are taken. Make all connections to the unit before applying power. Note the external markings described under "Safety symbols & instrument markings".

# WARNING

Do not operate the device in an explosive atmosphere or wet environments. Do not operate the instrument around flammable gases or fumes, vapor, or wet environments.

#### WARNING

Do not install substitute parts or perform any unauthorized modification to the product. Return the product to a Keysight Sales and Service Office to ensure that safety features are maintained.

### CAUTION

If the device is used in a manner not specified by the manufacturer, the protection provided by the device may be impaired.

#### CAUTION

Do not attempt to clean the device. If cleaning the card is absolutely necessary, Keysight recommends cleaning the card with a lightly dampened cloth while the module is in a de-energized condition. Do not re-energize the card until it is completely dry.

# NOTE

The safety of any system incorporating the equipment is the responsibility of the assembler of the system.

# WARNING

If this product is not used as specified, the protection provided by the equipment could be impaired. This product must be used in a normal condition (in which all means for protection are intact) only.

# **CAUTION**

The measuring terminals on this instrument are designed to be used with external signals described in Mains-isolated secondary circuits, but NOT with external signals described in Categories II, III, and IV. The input of this instrument cannot be connected to the mains.

| Measurement Category | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| II                   | Applicable to testing and measuring circuits connected directly to utilization points (socket outlets and similar points) of the low-voltage mains installation.  Example: Measurements on MAINS CIRCUITS of household appliances, portable tools and similar equipment and on the consumer side only of socket-outlets in the fixed installation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| III                  | Applicable to test and measuring circuits connection to the distribution part of the building's low-voltage mains installation. To avoid risks caused by the hazards arising from these higher short-circuit currents, additional insulation and other provisions are required. Example: Measurements on distribution boards (including secondary meters), photovoltaic panels, circuit breakers, wiring, including cables, bus-bars, junction boxes, switches, socket-outlets in the fixed installation, equipment for industrial use and some other equipment such as stationary motors with permanent connection to the fixed installation.  NOTE: For equipment that is part of a fixed installation, the fuse or circuit breaker of the installation can be considered to provide adequate protection against short-circuit currents. |

| IV                   | Applicable to test and measuring circuits connected at the source of the building's low-voltage mains installation. Due to these high short-circuit currents, which can be followed by a high energy level, measurements made within these locations are extremely dangerous. Great precautions shall be made to avoid any chance of a short circuit.  Example: Measurements on devices installed before the main fuse or circuit breaker in the building installation.                                                                                                                                                                                                                                                                                                                                                                    |

# WARNING

To ensure mandatory safety requirements are being met, the module must be installed in a chassis which has been certified and marked by a Nationally Recognized Testing Lab (such as CSA, UL, TUV, ETL, and so on) in which all the means of protection are properly implemented. Note that CE marking alone is not adequate.

# WARNING

Servicing of the modules must be performed by qualified personnel only. To avoid electrical shock, do not perform any servicing manually. Return the module to Keysight Service Center.

For safety reasons, only Keysight approved equipment and accessories should be used with the module.

# NOTE

Position chassis to ensure easy access to remove the modules.

# Environmental Conditions

This instrument is intended for "indoor use" only.

The following table shows the environmental requirements and the corresponding characteristics for the product.

| Environmental Requirements                 | General Characteristics                                                                    |

|--------------------------------------------|--------------------------------------------------------------------------------------------|

| Temperature                                | Operating condition: 0°C to 45°C<br>Storage condition: -40°C to 70°C                       |

| Maximum Relative Humidity (non-condensing) | Type tested, 95% RH up to 40°C, decreases linearly to 40% RH at 45°C                       |

| Altitude                                   | Operating condition: Up to 10,000 ft (3048m)<br>Storage condition: Up to 15,000 ft (4572m) |

| Pollution degree*                          | Pollution Degree 2                                                                         |

<sup>\*</sup> See table below for Pollution Degree definitions

| Pollution Degree | Description                                                                                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | No pollution or only dry, non-conductive pollution occurs. The pollution has no influence. Example: A clean room or climate-controlled office environment.                   |

| 2                | Normally only dry non-conductive pollution occurs. Occasionally a temporary conductivity caused by condensation may occur. Example: General indoor environment.              |

| 3                | Conductive pollution occurs, or dry, non-conductive pollution occurs which becomes conductive due to condensation which is expected. Example: Sheltered outdoor environment. |

# Safety symbols & instrument markings

| Safety Symbol / Instrument Marking | Description                                                                                                                                                                                                                                                                                                             |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | Hot surface. The metallic panels may get warm after powering on the equipment.                                                                                                                                                                                                                                          |

| $\triangle$                        | The instruction manual symbol. The product is marked with this warning symbol when it is necessary for the user to refer to the instructions in the manual.                                                                                                                                                             |

| ISM GRP 1-A                        | The CE mark is a registered trademark of the European Community.                                                                                                                                                                                                                                                        |

| UK<br>CA                           | The UK mark is a registered trademark of the European Community.                                                                                                                                                                                                                                                        |

|                                    | The RCM mark is a registered trademark of the Australian Communications and Media Authority.                                                                                                                                                                                                                            |

|                                    | The KC mark is the Korean certification mark. This equipment is Class A suitable for professional use and is for use in electromagnetic environments outside of the home.                                                                                                                                               |

|                                    | Electro Static Discharge. Attach ESD protective wrist strap to avoid damage by direct contact with the equipment.                                                                                                                                                                                                       |

| 40                                 | China Restricted Substance Product Label. The EPUP (environmental protection use period) number in the center indicates the time period during which no hazardous or toxic substances or elements are expected to leak or deteriorate during normal use and generally reflects the expected useful life of the product. |

| ccr.keysight@keysight.com          | This is the Keysight email address required by EU directives applicable to our product.                                                                                                                                                                                                                                 |

# Compliance and Environmental Information

Table 1 Compliance and Environmental Information

# The crossed out wheeled bin symbol indicates that separate collection for waste electric and electronic equipment (WEEE) is required, as obligated by the EU DIRECTIVE and other National legislation. Refer to keysight.com/go/takeback to understand your Trade in options with Keysight in addition to product takeback instructions.

# Declaration of Conformity

Declarations of Conformity for this product and for the Keysight products may be downloaded from the Web. Go to <a href="http://www.keysight.com/go/conformity">http://www.keysight.com/go/conformity</a>.

You can then search by product number to find the latest Declaration of Conformity.

# References to other documents

| Document name                      | Location on installed machine                                                                 |

|------------------------------------|-----------------------------------------------------------------------------------------------|

| M5300x C++ API Help                | <root-dir>\Program Files\Keysight\M5300x\Help\html\index.html</root-dir>                      |

| M5300x HVI Add-on Help             | <pre><root-dir>\Program Files\Keysight\M5300x\Help\Keysight_KtM5300xHvi_Fx45</root-dir></pre> |

| M5300x IVI.Net Help                | <root-dir>\Program Files\Keysight\M5300x\Help\Keysight_KtM5300x_Fx45</root-dir>               |

| M5300x IVI-C Help                  | <root-dir>\Program Files\Keysight\M5300x\Help\KtM5300x</root-dir>                             |

| M5300x Python API Help             | <root-dir>\Program Files\Keysight\M5300x\python\html\index.html</root-dir>                    |

| M5300A PXIe Hi-Speed AWGs BSP Help | Accessible within the KF9000B PathWave FPGA environment                                       |

| Document name                                       | K.com URL                                                                        |

|-----------------------------------------------------|----------------------------------------------------------------------------------|

| M5300A PXIe RF AWG Modules Startup Guide            | https://www.keysight.com/find/M5300A-TechSupport/                                |

| M5200A PXIe Digitizer Modules User Guide            | https://www.keysight.com/find/M5200A-TechSupport/                                |

| M5201A PXIe Downconverter Modules User Guide        | https://www.keysight.com/find/M5201A-TechSupport/                                |

| KS2201A PathWave Test Sync Executive User<br>Manual | https://www.keysight.com/in/en/support/KS2201A/pathwave-test-sync-executive.html |

| KF9000B PathWave FPGA User Documentation            | https://www.keysight.com/in/en/support/KF9000B/pathwave-fpga.html                |

# Contents

Keysight Cybersecurity / 3

```

Safety Summary / 4

Safety symbols & instrument markings / 7

Compliance and Environmental Information / 8

Declaration of Conformity / 8

References to other documents / 9

1 Overview on M5300A High-Speed AWG Modules

About M5300A AWG modules / 18

About M5300A module's timebase / 21

System Clock Architecture 21

Procedure for System Clock Initialization 22

Procedure for Module Clock Initialization 22

Clock Configuration 22

Inter-Module Phase Alignment 23

Procedure for Initial Clock Alignment 23

Procedure for Clock Re-Alignment 26

List of products required / supported with M5300A modules / 29

About M5300x software features / 31

Waveform formats in the M5300x SW / 31

Binary Floating Point Data 32

Binary Digital Data 32

Invalid Values 33

CSV Data (CSV Floating Point Data) 33

CSV Digital Data 33

Creating Waveform files in M5300x SW drivers / 35

Data transfer speed in M5300x SW / 36

Normal APIs 36

Remote APIs 36

Measured values in M5300x SW / 37

About PathWave FPGA and BSP / 38

Using PathWave FPGA / 38

Using BSP with PathWave FPGA / 38

About KS2201A PathWave Test Sync Executive software / 40

About HVI Technology / 40

M5300A Firmware version requirements for HVI / 40

About HVI Application Programming Interface / 40

```

# 2 Using the KS2201A PathWave Test Sync Executive software

```

Licensing for KS2201A PathWave Test Sync Executive software / 44

Understanding operation flow in KS2201A HVI API / 45

Working with KS2201A PathWave Test Sync Executive software / 46

Overview on HVI technology / 46

Understanding the HVI elements used in M5300x API / 47

Description of various HVI elements / 47

HVI Engine 47

HVI Actions 47

HVI Events 47

HVI Trigger 47

HVI Registers 48

HVI Instructions 48

FPGA Sandbox registers and Memory maps 48

Resources available in PathWave Test Sync Executive 49

Module initialization and execution procedures with HVI / 52

Start up and Calibration operations / 52

Initialization steps 52

Test Execution operations / 54

Execution steps 54

Timing to be added to HVI commands / 55

HVI timings in M5300A modules / 56

HVI-Engine Clock / 56

HVI Sync Resources Timing / 56

HVI Sync and Flow control statement timing / 56

HVI Triggers Timing / 57

Trigger groups 57

TriggerWrite instruction timing 57

HVI Actions Timing / 58

Action groups for M5300A modules 58

ActionExecute instruction timing 58

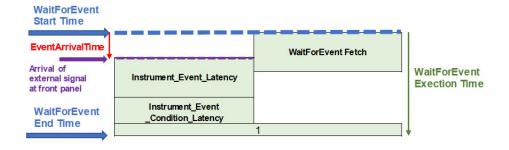

HVI Event Timing / 60

Local Wait-for-event Statement timing 60

HVI FPGA User Sandbox Instructions Timing / 62

Instruction-specific parameter 62

HVI Local Instructions Timing / 63

Other HVI timings / 63

FPGA-Instruction Statement Timing 63

M5300A-specific HVI Instructions 64

Sync FPGA Data sharing 64

```

# 3 Using the PathWave FPGA Board Support Package (BSP)

Licensing for PathWave FPGA BSP support / 66 Features in PathWave FPGA / 67

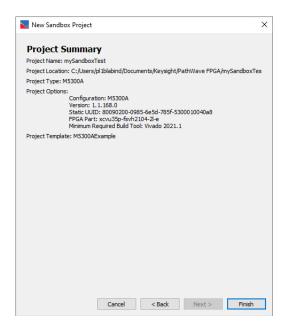

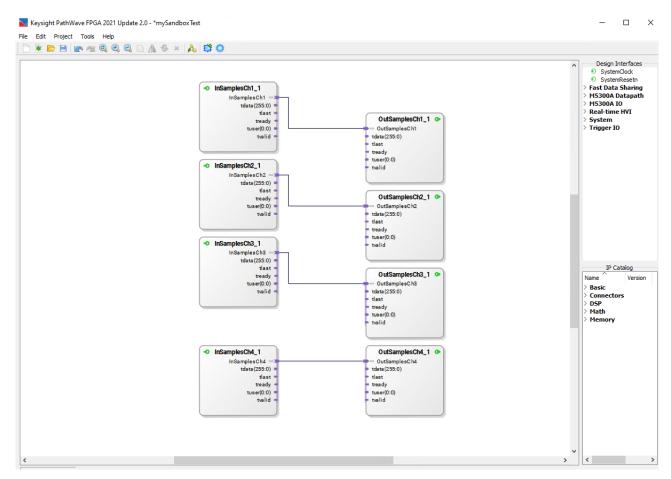

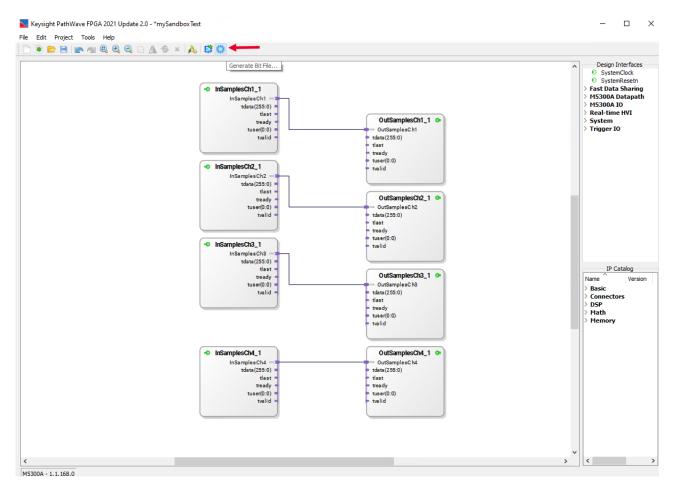

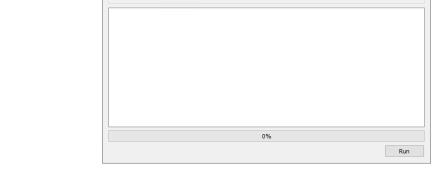

Working with PathWave FPGA software / 68

Understanding Partial Configuration (PR) / 69

Using BSP with PathWave FPGA software / 71

Understanding BSP composition / 71

Generating a k7z file using PathWave FPGA BSP / 73 Loading k7z file onto modules / 80

# 4 Using Keysight Distributed Infrastructure (KDI)

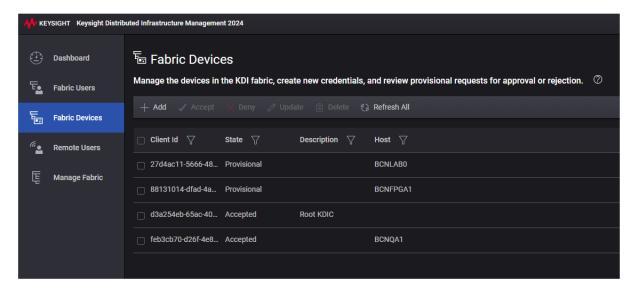

Overview / 82

About KDI Authentication Service (KDIS) / 82

About KDI Clients (KDIC) / 83

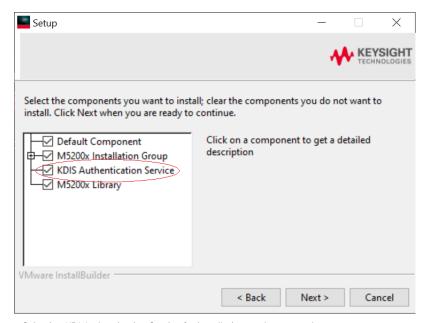

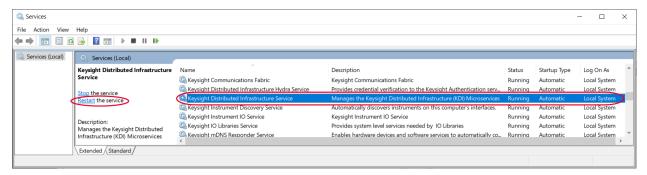

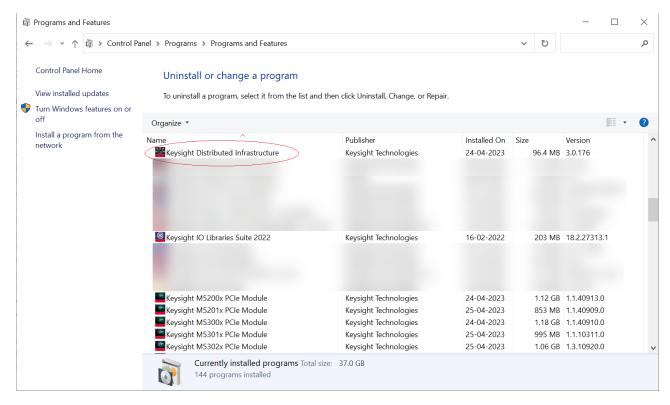

Installing KDI on the root node / 84

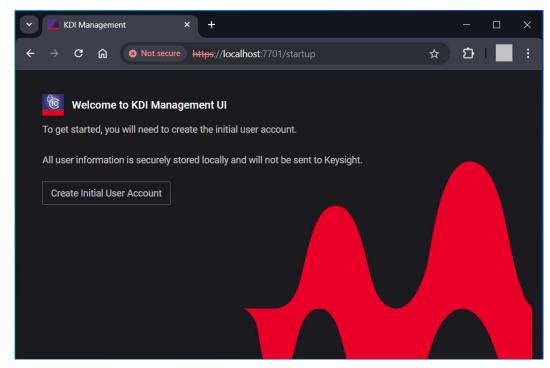

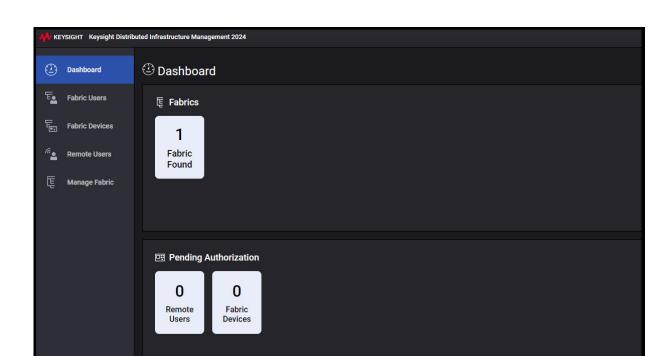

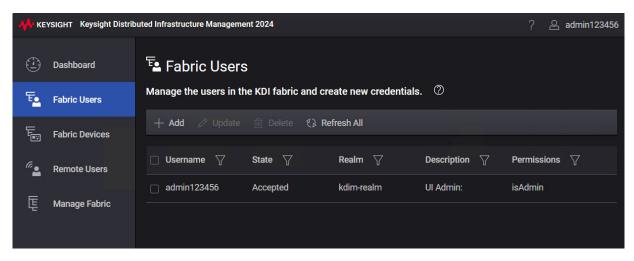

Configuring KDI and KDIS on root node / 85

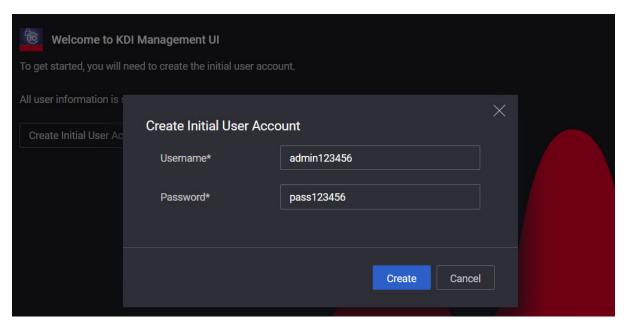

Configuring admin credentials in KDIS / 85

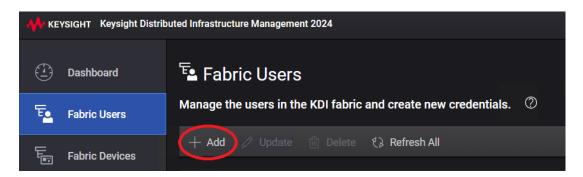

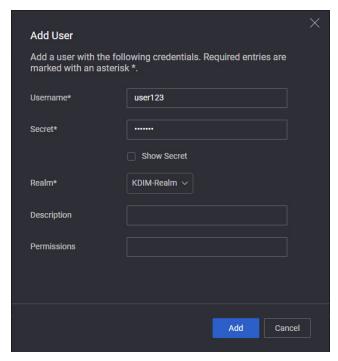

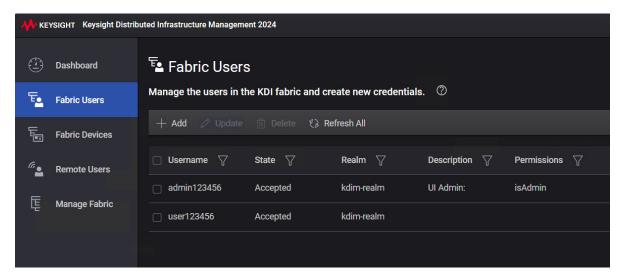

Adding additional users in KDIS / 89

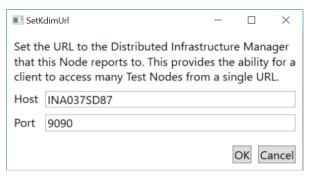

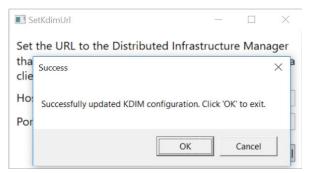

Configuring KDI Clients to find KDIS / 92

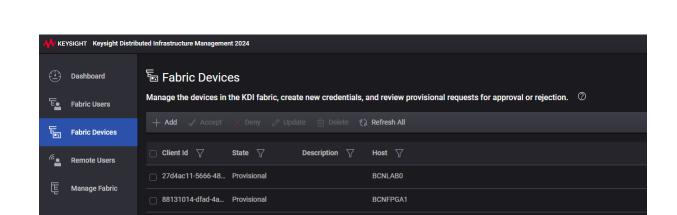

Accepting leaf nodes (KDI clients) in KDIS / 93

Using KDI on root node / 95

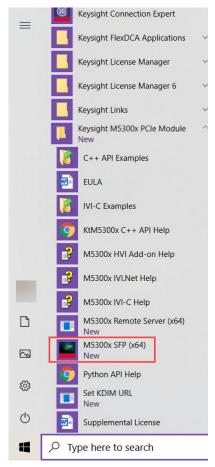

Method 1: Including KDI in SW API scripts 95 Method 2: Including KDI in M5200x SFP 95

Removing KDI from the root node / 97

# 5 Using M5300A High-Speed AWG Modules SFP

Launching the M5300A PXIe Module SFP software / 100

Familiarizing with the SFP software / 102 Menus / 102

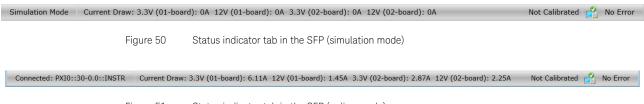

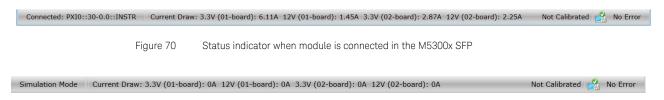

Status Indicators / 102

Understanding Menu options / 103

File menu options / 103

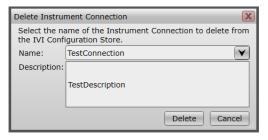

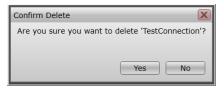

To save a connection: 103

To delete a connection: 103

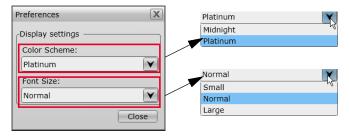

View menu options / 104

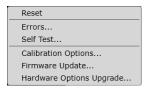

Utilities menu options / 105

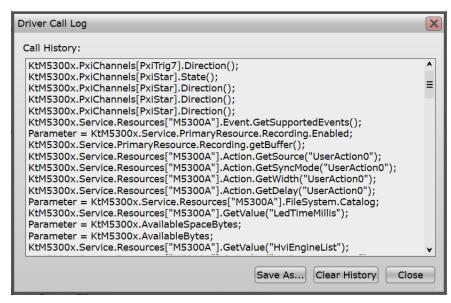

Tools menu options / 106

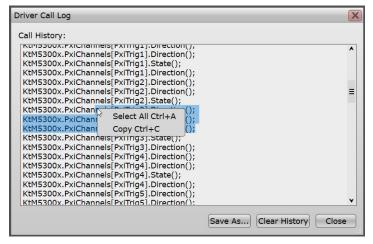

To clear the driver call logs: 107

To copy and paste call history from the driver call log: 107 To save a copy of the Driver Call Log to a file: 108

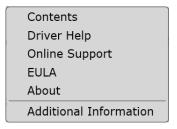

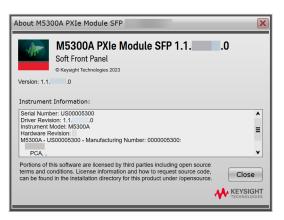

Help menu options / 108

Performing specific tasks in the M5300x SFP Software / 110

Connecting to Modules / 110

Connecting via PXI VISA address 111

Connecting via Simulation mode 111

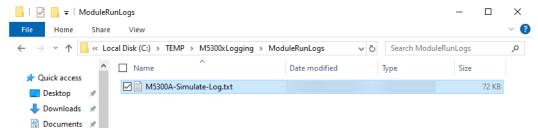

Managing Module Run Logs / 112

Checking Instrument Status / 114

Configuring the SFP features / 114

Read-only data 115

Auto-Refresh 115

Configuring Clock source and alignment settings 116

Configuring Waveform External Trigger Setup 117

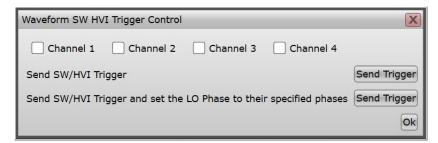

Configuring SW/HVI Trigger Control 119

Configuring Channel and Output 120

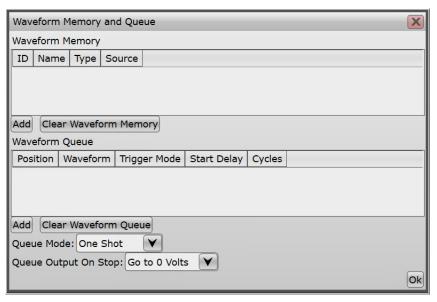

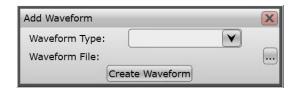

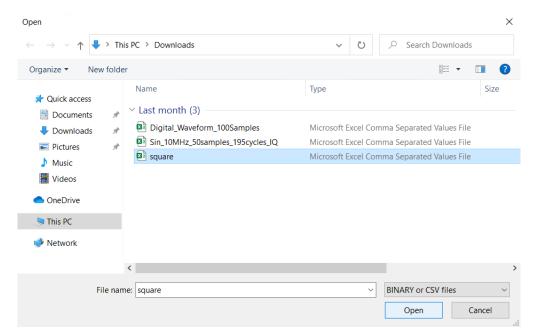

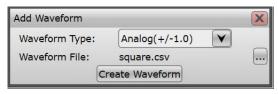

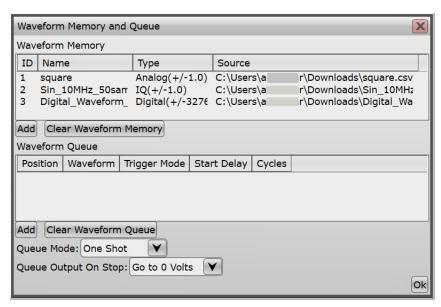

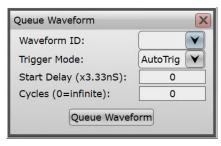

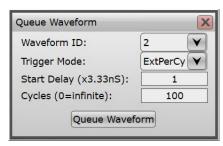

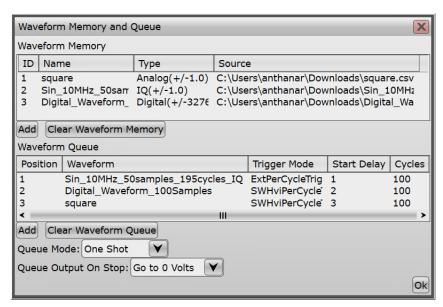

Configuring Waveform Memory and Queue 121

Configuring Waveform Play 126

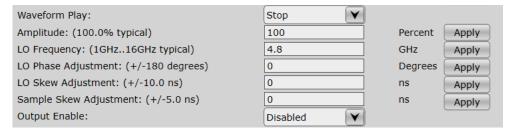

Configuring the Amplitude & Local Oscillator (LO) parameters 127

Configuring Output Enable 128

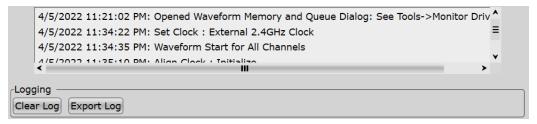

Configuring Logs 128

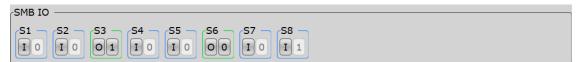

Configuring the 'SMB IO' bank 129

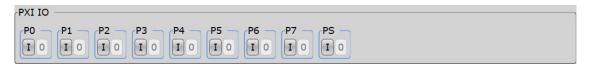

Configuring the 'PXI IO' bank 130

Update / Auto-Update 131

Resetting to Default Factory Settings / 131

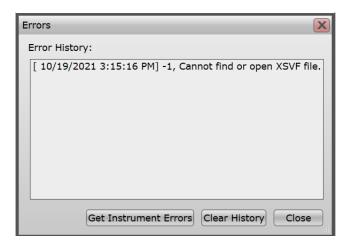

Viewing Errors log / 131

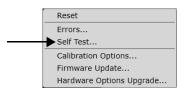

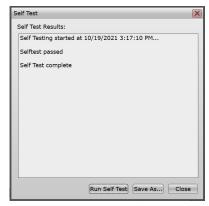

Conducting a Self Test / 133

Performing Self Test using the Soft Front Panel 133

Performing Self Test using IVI Drivers 134

Self Test Errors 135

Setting Calibration Options / 136

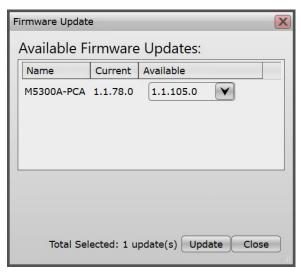

Updating Firmware / 136

# 6 Configuring waveforms using the M5300x SFP

Mechanism of waveform generation / 138

Understanding Waveform formats / 139

Waveform formats in the M5300x SW / 139

Conditions to create Waveform files in M5300x SW drivers / 139

Data transfer speed in M5300x SW / 139

Measured values in M5300x SW / 139

Configuring M5300x SFP for waveform generation / 140

# 7 Using Peer-to-Peer Streaming for data transfers

```

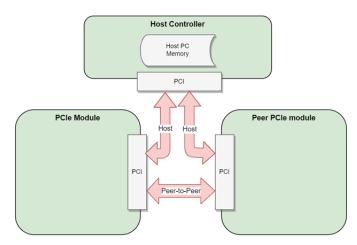

P2P Streaming - Overview / 142

About PDTI / 142

Common terminologies in P2P streaming / 142

Data flow in P2P streaming / 144

Data Format & Transfer in P2P streaming / 144

Prerequisites to P2P Streaming / 146

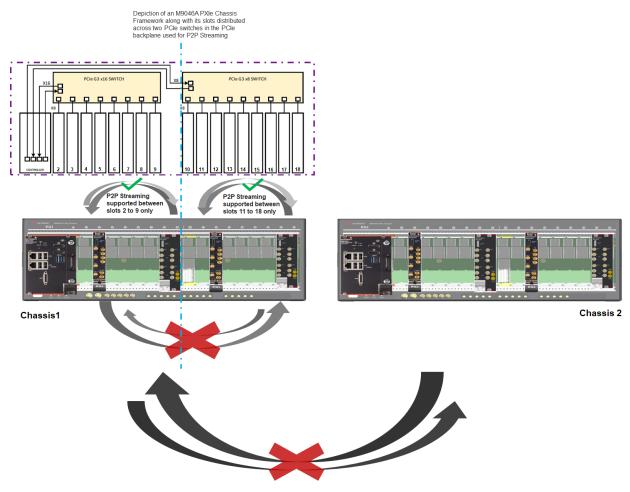

Hardware prerequisites / 146

Positioning of modules in the PXIe Chassis 146

Software requirements / 147

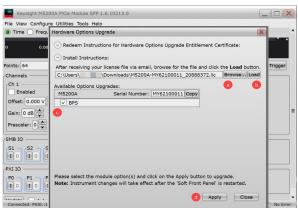

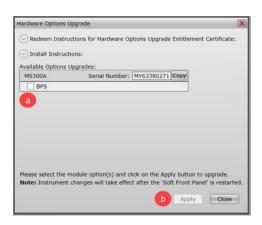

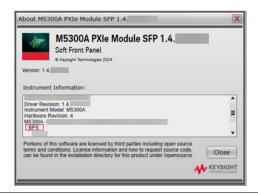

Licensing requirements / 147

Performing P2P data streaming between modules / 150

Supported APIs / 150

```

# 8 Using M5300x API functions in sample programs

```

Implementing M5300x API functions — Sample Programs / 154

Sample program to perform & check toggling on SMB IO Channels / 154

Output 156

Sample program to load a Sandbox design onto an M5300A module / 157

Output 159

Sample program to create an HVI sequence for an SMB trigger / 160

Output 163

Sample program to configure waveform settings on the module / 163

Output 165

Sample program to adjust phase using HVI / 165

Output 168

Sample program to perform P2P streaming / 169

Sample program using HVI to perform P2P streaming / 175

```

# 9 Exceptions/Errors/Warnings

Description of messages returned by the SW / 184

Index

# 1. Overview on M5300A High-Speed AWG Modules

About M5300A AWG modules 18

About M5300x software features 31

About PathWave FPGA and BSP 38

About KS2201A PathWave Test Sync Executive software 40

#### 1

# Section 1.1: About M5300A AWG modules

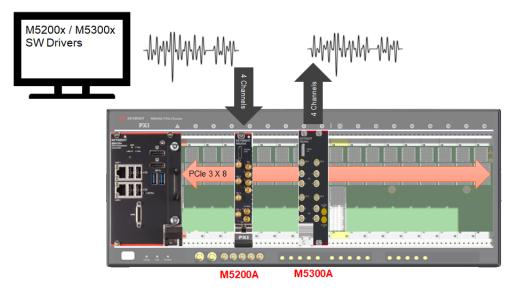

The M5300A RF AWG module supports four directly synthesized RF channels in 2 PXIe slots with up to 18 GHz of RF and 2 GHz of instantaneous bandwidth. The channels are fully coherent across the module and across the entire system for applications in quantum computing and aerospace applications. The module supports the ability to load data into the module directly over the PCIe backplane. You can also create custom IP and processing algorithms in the FPGA. The module supports the PathWave FPGA and PathWave Test Sync Executive platforms for developing and configuring IP blocks and synchronous system event control.

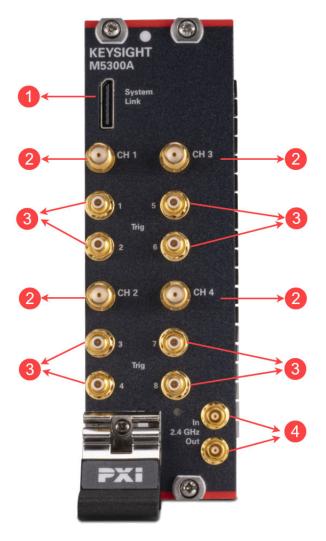

Figure 1 Front Panel view of the M5300A High Speed AWG module

The M5300A is a two-slot PXIe module with four high-speed (0 to 18 GHz) AWG outputs along with clock input-output, and eight triggers. Figure 1 shows the front panel of an M5300A High Speed AWG module, which comprises of the following connectors:

#### 1 SystemLink Connector (1)

The top connector is a x4 System Link connection. It has eight bi-directional LVDS pairs (1.2 Gbps), unused RX and TX SERDES pairs (6 Gbps), four single-ended control lines, and a power supply (+5 V at 0.5 A). System Link also has two handshaking signals called TX\_DISABLE\_OUT and TX\_DISABLE\_IN. If these signals are not properly driven, the data signals in connector are forced to be inputs (tri-state). This connector can be used to connect to a system timing module, other cards, or to a breakout board.

#### 2 AWG outputs

The analog outputs are created with a DAC clocked in GHz, with a special double-data rate mechanism inside the DAC doubles the effective sampling rate, thereby providing a Nyquist bandwidth of 19.2 GHz. The 19.2 GHz sample clock is derived from either the 100 MHz PXI clock, DSTARA, or an external 2.4 GHz clock using onboard clock multipliers.

#### 3 Bi-directional SMB Triggers

The module allows you to control eight single-ended signals on the SMB connectors. These signals swing 0-3.3 V and can drive 50-ohm loads (dividing the voltage in half). The signals toggle up to 100 MHz with 3.3 ns edge alignment.

#### 4 2.4 GHz Analog Reference Clock (In & Out)

There are two connectors for 2.4 GHz clkout and 2.4 GHz clkin - these are used for sharing a coherent frequency reference across multiple cards in one or more chassis.

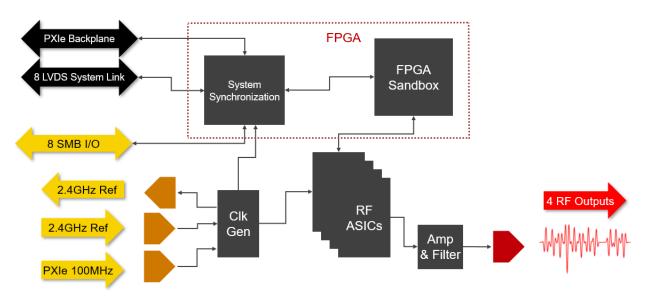

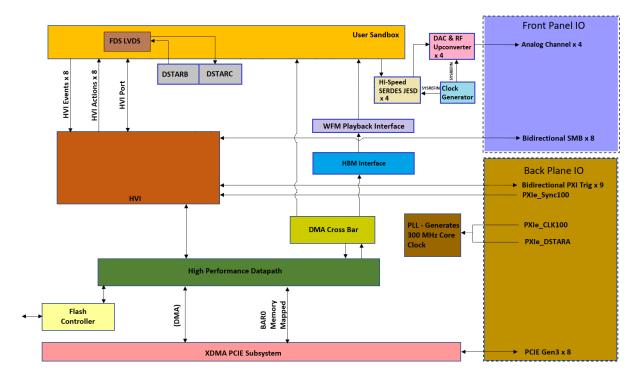

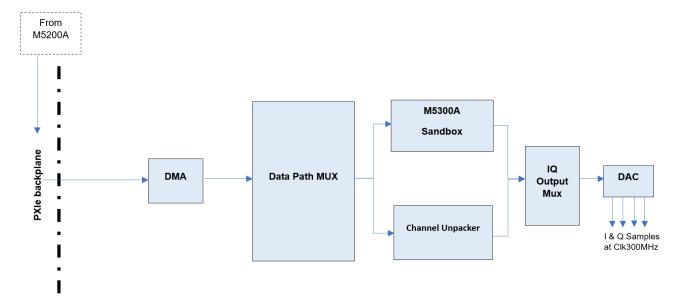

The block diagram shown in Figure 2 depicts the various elements in the M5300A modules that help in generating high-speed RF waveforms.

Figure 2 Block diagram representation of the M5300A High Speed AWG module

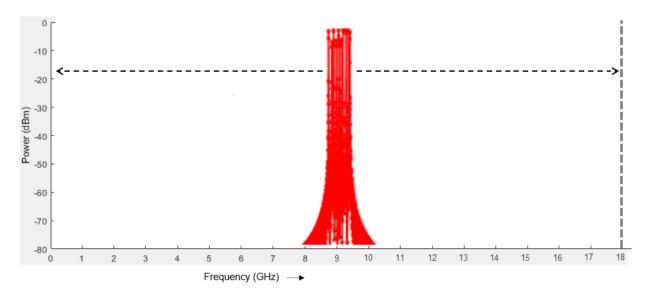

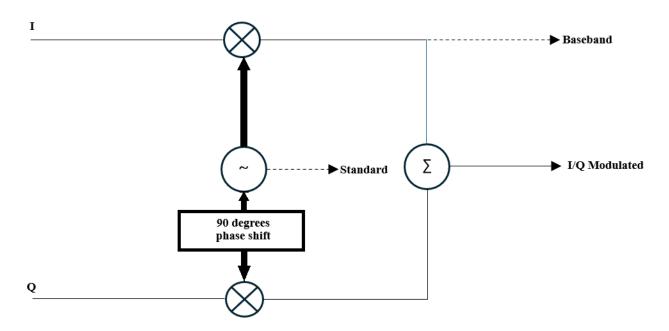

The M5300A generates three output waveform types, namely Standard, Baseband and Modulated. Figure 3 shows an example of how the M5300A RF AWG can use IQ modulation to create a 2.4 GHz signal anywhere within the frequency range of 0 to 18 GHz.

Figure 3 Example of using IQ modulation in M5300A RF AWG module

While the Front Panel connectors have been described above, the M5300A plugs into two slots of the High-performance PXIe chassis (M9046A) with two connectors (per slot). The PXI backplane provides eight bus trigger lines (PXI\_TRIG[7:0]) and one point-point trigger line (PXI\_STAR). These lines allow communication between cards. The PXI\_TRIG lines operate at low MHz with open-drain outputs pulled up to 5 V. These lines can be controlled using either the SFP or the APIs. See "Configuring the 'PXI IO' bank" on page 130 for more information.

Other than level-shifting to the PXI triggers and generating/distributing clocks, the FPGA handles all communication to onboard chips and to the PXIe backplane. The main FPGA interfaces are x8 PCIe to the backplane, SERDES and LVDS links to the four DACs, controls for the clocks, and many small peripherals (power sequencers, temp sensors, and so on).

The Digital to Analog Converters within the M5300A modules allows 2 GHz of IF (signal) bandwidth upconverted to a frequency between 0-18 GHz. Each upconverter includes an amplifier with differential input and differential output to help level the output frequency response to 16 GHz.

Table 2 lists certain specifications for the M5300A module.

Table 2 Specifications for the M5300A module

| Characteristic           | Value                       |

|--------------------------|-----------------------------|

| Operating Voltage        | +3.3 V and +12 V            |

| Operating current (max.) | 6.3 A (3.3 V), 2.4 A (12 V) |

| Total Power dissipation  | 50 W                        |

| Measurement Category     | Non-CAT                     |

# CAUTION

The measuring terminals on this instrument are designed to be used with external signals described in Mains-isolated secondary circuits, but NOT with external signals described in Categories II, III, and IV. The input of this instrument cannot be connected to the mains.

Table 3 Description of Measurement Category II, III and IV

| Measurement Category | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| II                   | Applicable to testing and measuring circuits connected directly to utilization points (socket outlets and similar points) of the low-voltage mains installation.  Example: Measurements on MAINS CIRCUITS of household appliances, portable tools and similar equipment and on the consumer side only of socket-outlets in the fixed installation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| III                  | Applicable to test and measuring circuits connection to the distribution part of the building's low-voltage mains installation. To avoid risks caused by the hazards arising from these higher short-circuit currents, additional insulation and other provisions are required. Example: Measurements on distribution boards (including secondary meters), photovoltaic panels, circuit breakers, wiring, including cables, bus-bars, junction boxes, switches, socket-outlets in the fixed installation, equipment for industrial use and some other equipment such as stationary motors with permanent connection to the fixed installation.  NOTE: For equipment that is part of a fixed installation, the fuse or circuit breaker of the installation can be considered to provide adequate protection against short-circuit currents. |

| IV                   | Applicable to test and measuring circuits connected at the source of the building's low-voltage mains installation. Due to these high short-circuit currents, which can be followed by a high energy level, measurements made within these locations are extremely dangerous. Great precautions shall be made to avoid any chance of a short circuit.  Example: Measurements on devices installed before the main fuse or circuit breaker in the building installation.                                                                                                                                                                                                                                                                                                                                                                    |

To know about the functionality of the M5300A SFP, refer to "Using M5300A High-Speed AWG Modules SFP" on page 99.

# 1.1.1: About M5300A module's timebase

The M5300A module generates an independent internal LO for each of the four channels. The time reference for the LO is selectable and can be sourced from either an internal 2.4 GHz Analog Reference Clock derived from the PXI chassis 100 MHz System Reference Clock or from an external 2.4 GHz Analog Reference Clock. The internal Analog Clock is easier to use than the external Analog Clock because it does not require external clock generation and distribution. However, the best absolute phase noise and coherency between modules is achieved when using the external Analog Clock.

# System Clock Architecture

The M5300A modules are used in Keysight PXI-based systems that employ a variety of clock configuration options that trade off phase coherency and system complexity. Those different clock configurations are described in "Clock Configuration" on page 22.

Regardless of the system clock configuration used, the clock generation and distribution must be configured and aligned. Some of this configuration and alignment takes place within the PXI chassis and System Synchronization Modules (M9032A) and some of it takes place within each peripheral module (such as the M3202A AWG 1G module). In general, all clock configuration and alignment procedures must be performed at the system level before they are performed at the peripheral module level.

NOTE

Re-configuring the system-level clocks can cause disruptions and glitches in the both the 100 MHz System Clock and 2.4 GHz Analog Clock. Disruptions in these system-level clocks while a peripheral module is performing certain operations can cause the module to become unstable or unresponsive. System clock re-configuration should only be performed immediately after system power on or after all peripheral modules have been reset. Modules can be reset through the SFP or API.

For description on instructions for resetting modules, refer to "Resetting to Default Factory Settings" on page 131.

When either the SFP or API connects to a module driver for the first time after a power cycle, the module's Analog Clock source is defaulted to internal, and all the module clocks are aligned. Subsequent disconnections and re-connections to the module driver do not interfere with the module's clock configuration or alignments unless explicitly forced to do so using the "Reset" driver connection option.

# Procedure for System Clock Initialization

The system-level clock initialization procedure comprises configuring and aligning the system clocks, which are external to the M5300A module. Depending on which clock configuration option you use, this procedure can range from very simple to extremely complex. Except for the simplest configurations, system clock initialization is performed using automated procedures provided by the PathWave Test Synchronization Executive. You can find more detail about using those automated system clock initialization procedures in the KS2201A PathWave Test Sync Executive User Manual.

#### Procedure for Module Clock Initialization

The module-level clock initialization procedure comprises configuring and aligning the clocks which are internal to the M5300A module. The module initialization procedure you need to perform depends on; 1) which system clock configuration option you use and 2) whether you care about the precise relative phase alignment between the M5300A module you are initializing and other peripheral modules.

The module clock initialization procedures are relatively simple and can be performed either through the module SFP interface, automated by the PathWave Test Synchronization Executive or automated yourself using the module API commands.

# **Clock Configuration**

The various clock configuration options configure the module to use either the internal 2.4 GHz Analog Clock or the external 2.4 GHz Analog Clock. The procedure to select the Analog Clock source using the SFP interface is described in "Configuring Clock source and alignment settings" on page 116. The details to select the Analog Clock source using the PathWave Test Synchronization Executive is described in the KS2201A PathWave Test Sync Executive User Manual. The module API command to select the Analog Clock source using the API interface is described in the IVI-Help files and M5300x Python Help file.

NOTE

When configuring the Analog Clock source using either the GUI or API for multi-module systems that daisy-chain the external Analog Clock through one of the modules, the order in which you configure each module is important. Upstream modules in daisy-chained configuration must be configured before downstream modules to prevent disruption or glitching of downstream clocks.

# Inter-Module Phase Alignment

Single-module applications that do not require precise inter-module phase alignment do not require use of HVI synchronization or any additional clock alignment actions beyond simply selecting the desired Analog Clock source. However, multi-module applications that depend on synchronized LO phase between modules require both HVI and additional clock alignment and de-skew procedures.

Every time the M5300A powers on, it needs to perform a module clock alignment. The first time the module clock alignment is performed (an Initial Clock Alignment), the LO's residual random skew error (phase error) can be up to  $\pm 52$  ps relative to the System Time Reference provided by the PathWave Test Sync Executive. You may correct this skew error as part of the normal User De-skew procedure, which corrects for your application's other cable and fixture skew errors.

Each time the module performs an Initial Clock Alignment, it could result in a residual skew error of  $\pm 52$  ps, which would then need to be corrected with a User Skew adjustment.

You could choose to perform an Initial Clock Alignment after each power cycle, but that can be a time-consuming process. Alternatively, you can perform a Clock Re-Alignment, provided that you have performed an Initial Clock Alignment at least once before with the same exact system hardware and clock configuration. Performing a Clock Re-Alignment does not result in a random residual skew error and does not require an adjustment to the User Skew settings.

NOTE

The Clock Re-Alignment procedure is very sensitive to the propagation delays of all the system and module clocks. Any change in the hardware or clock configuration will require a new Initial Clock Alignment. Simply replacing a defective MCX Analog Clock cable or moving a module to different chassis slot will require a new Initial Clock Alignment, as would a significant change to the system's ambient temperature.

Module clock alignment can be performed using the PathWave Test Synchronization Executive, the module's API or module's SFP. Module alignment of large systems is only practical using the PathWave Test Synchronization Executive software. For small systems of only a few modules, following procedures can be used.

# Procedure for Initial Clock Alignment

Must be performed after any hardware or clock configuration change.

- 1 Open all module GUI or API driver connections.

- GUI controls

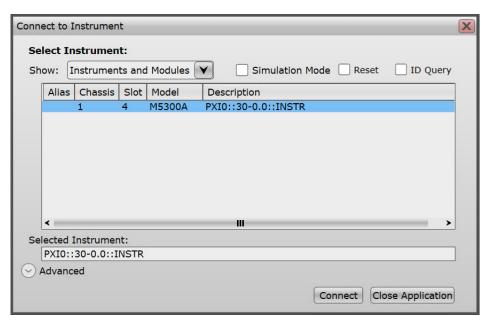

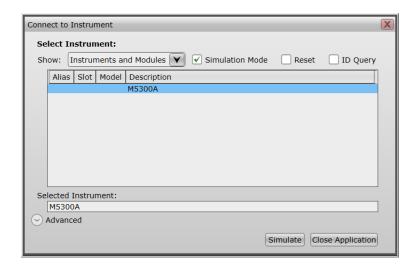

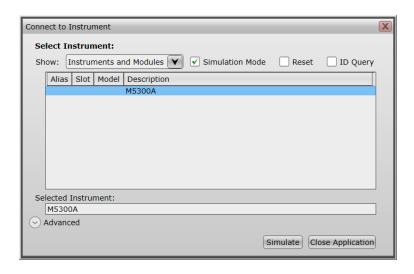

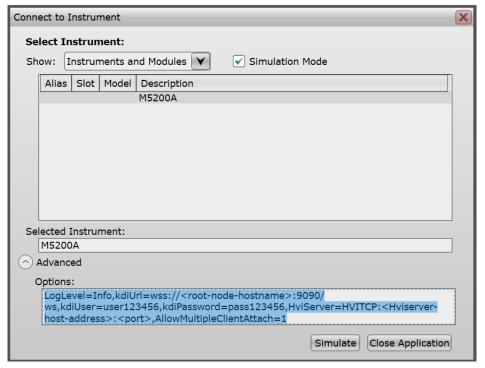

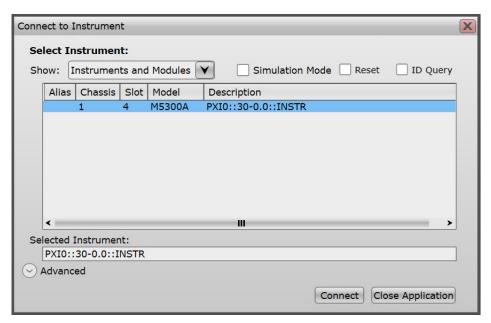

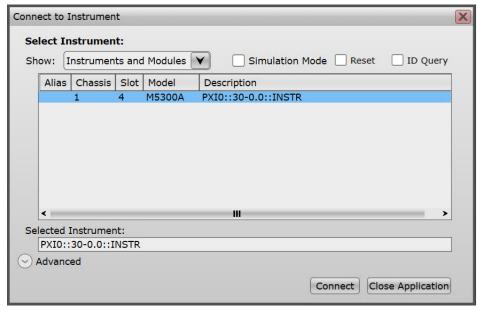

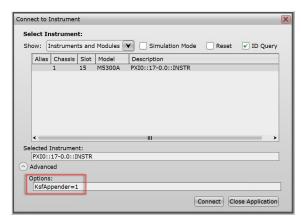

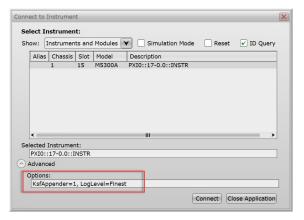

Figure 4 M5300x SFP software Connect to Instrument window (with one or more modules connected)

Figure 5 M5300x SFP software Connect to Instrument window (Simulation Mode)

· API commands

# driver = keysight\_ktm5300x.KtM5300x(resource, query, reset, options)

- 2 Configure module to use the desired Analog Clock.

- · GUI controls

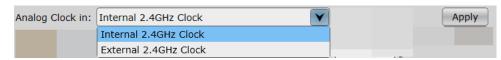

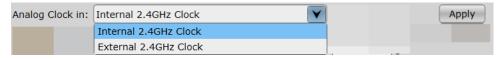

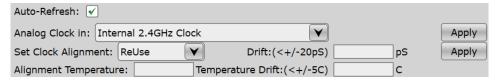

- i From the main window of the M5300x SFP, select a reference clock source from the **Analog Clock in** drop-down field:

Figure 6 Configuring the desired analog clock in the M5300x SFP

- Internal 2.4GHz Clock (default option)

- External 2.4GHz Clock

- ii Click Apply.

- · API commands

driver.clock.clock\_source = keysight\_ktm5300x.ClockSource.INTERNAL

driver.clock.clock\_source = keysight\_ktm5300x.ClockSource.EXTERNAL

Modules in Daisy-chained clock configurations must be configured in a specific order to prevent disruption of downstream clocks.

3 Wait for system temperature to stabilize.

This could take up 30 minutes, depending on the complexity of the system and how recent the power distribution of the system has changed. You may skip this waiting step if you can tolerate the potential 26 ps inter-channel skew errors.

- 4 Perform an Initial Clock Alignment.

- · GUI controls

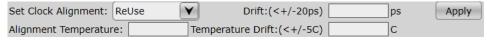

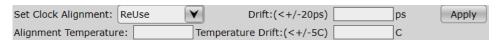

- i From the main window of the M5300x SFP, select **Initialize** from the **Set Clock Alignment** drop-down options to perform clock alignment configuration.

Figure 7 Configuring the desired clock alignment configuration in the M5300x SFP

ii Click Apply.

NOTE

Select **Initialize** if you have not previously performed an alignment using this option for the current hardware & clock configuration. This option may introduce small random skew errors, where you must perform de-skew manually.

Notice that the **Drift**, **Alignment Temperature** and **Temperature Drift** values are auto-populated when you click **Apply** to set the Clock Alignment option. For more information about these properties, see "Configuring Clock source and alignment settings" on page 116.

API commands

driver.clock.invalidate\_current\_alignment()

The driver.clock.invalidate\_current\_alignment() method must be run to either reset the clock alignment settings or if the Clock Alignment is being set to Initialize using the SFP controls. This way, a new alignment point is set, which could be different than the last alignment point. Consequently, you are required to perform once again the deskew of the outputs and inputs of the system.

driver.clock.align()

The driver.clock.align() method performs the clock alignment. In this case, since the current alignment is made invalid using the driver.clock.invalidate\_current\_alignment() method or has never been done, this method automatically performs an "initialize" alignment.

driver.clock.alignment\_temperature(float)

#### 1

driver.clock.drift\_temperature(float)

driver.clock.drift\_time(str)

Note that the order in which the modules are aligned is important. Modules should be deskewed in an order where the modules that are receiving an external clock from another module should be deskewed after the module that is sourcing the 2.4 GHz analog clock. That is, all sources of the 2.4 GHz analog clock should be deskewed before receivers of the 2.4 GHz analog clock.

- 5 De-skew residual skew error from and Initial Clock Alignment and application's unique cable and fixture skew errors.

- 6 Record User Skew values for future reference.

# Procedure for Clock Re-Alignment

May be performed after any power cycle for which now hardware or clock configuration changes have occurred since the previous Initial Clock Alignment was performed.

- 1 Open all module GUI or API driver connections.

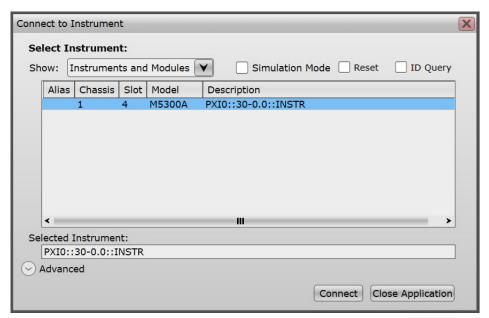

- GUI controls

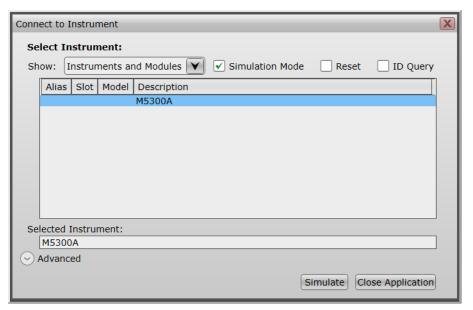

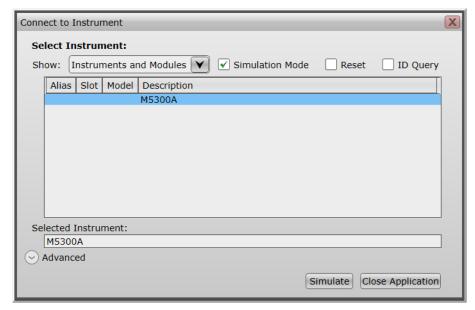

Figure 8 M5300x SFP software Connect to Instrument window (with one or more modules connected)

Figure 9 M5300x SFP software Connect to Instrument window (Simulation Mode)

API commands

# driver = keysight\_ktm5300x.KtM5300x(resource, query, reset, options)

- 2 Configure module to use the desired Analog Clock.

- · GUI controls

- i From the main window of the M5300x SFP, select a reference clock source from the **Analog Clock in** drop-down field:

Figure 10 Configuring the desired analog clock in the M5300x SFP

- Internal 2.4GHz Clock (default option)

- External 2.4GHz Clock

- ii Click Apply.

- · API commands

driver.clock.clock\_source = keysight\_ktm5300x.ClockSource.INTERNAL

#### driver.clock.clock\_source = keysight\_ktm5300x.ClockSource.EXTERNAL

Modules in Daisy-chained clock configurations must be configured in a specific order to prevent disruption of downstream clocks.;

3 Wait for system temperature to stabilize.

This could take up 30 minutes, depending on the complexity of the system and how recent the power distribution of the system has changed. You may skip this waiting step if you can tolerate the potential 52 ps inter-channel skew errors.

4 Perform an Initial Clock Alignment.

#### GUI controls

i From the main window of the M5300x SFP, select **ReUse** from the **Set Clock Alignment** drop-down options to perform clock alignment configuration.

Figure 11 Configuring the desired clock alignment configuration in the M5300x SFP

ii Click Apply.

Select this option if you previously performed an alignment using the **Initialize** option for the current hardware and clock configuration. This option preserves the inter-channel skews set by the prior alignment where the **Initialize** option was used.

Notice that the **Drift**, **Alignment Temperature** and **Temperature Drift** values are auto-populated when you click **Apply** to set the Clock Alignment option. For more information about these properties, see "Configuring Clock source and alignment settings" on page 116.

· API commands

driver.clock.align()

The driver.clock.align() method performs the clock alignment wherein, the previous alignment setting is used and by default, a "Reuse" alignment is performed. In this scenario, do not use the driver.clock.invalidate\_current\_alignment() method to perform clock re-alignment.

```

driver.clock.alignment_temperature(float)

driver.clock.drift_temperature(float)

driver.clock.drift_time(str)

```

Note that the order in which the modules are aligned is important. Modules should be deskewed in an order where the modules that are receiving an external clock from another module should be deskewed after the module that is sourcing the 2.4 GHz analog clock. That is, all sources of the 2.4 GHz analog clock should be deskewed before receivers of the 2.4 GHz analog clock.

5 Apply User Skew values that were recorded after the previous Initial Clock Alignment was performed.

# 1.1.2: List of products required / supported with M5300A modules

You require the following (recommended) Keysight products to achieve precision and control when performing measurements. Visit the corresponding product pages on <a href="https://www.keysight.com">www.keysight.com</a> to procure and refer to the respective documentation to understand how to use these modules/products.

Table 4 List of supported equipment

| Required equipment                                                              | Recommended Model / Part number(s)                                     |  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| PXIe Digitizer modules                                                          | M5200A                                                                 |  |

| PXIe Downconverter modules                                                      | M5201A                                                                 |  |

| PXIe Baseband AWG modules                                                       | M5301A                                                                 |  |

| PXIe LVDS Digital IO modules                                                    | M5302A                                                                 |  |

| System Sync modules                                                             | M9032A / M9033A                                                        |  |

| PXIe Chassis: High power, 18 slots, 24 GB/s, requires option -QS2               | M9046A                                                                 |  |

| Controller options (use one of the following options)                           |                                                                        |  |

| PXIe High-Performance Embedded Controller                                       | M9037A                                                                 |  |

| External Controller*                                                            | Refer to http://www.keysight.com/find/PXIAXIePCBIOSandWindowsSettings. |  |

| Other accessories                                                               |                                                                        |  |

| PXIe 5-channel Source / Measure Unit, 100 pA                                    | M9614A                                                                 |  |

| PXIe 5-channel Precision Source/Measure Unit,<br>500 kSa/s, 10 pA, 30 V, 500 mA | M9615A                                                                 |  |

| PXIe System Modules and Cable Interface                                         | M902xA                                                                 |  |

| PCle High-Performance Host Adapter                                              | M9049A                                                                 |  |

| Streamline Vector Network Analyzer, 9 kHz to 4.5 GHz, 2-port                    | P5000B                                                                 |  |

| Infiniium UXR-Series Oscilloscope: 16 GHz, 4 Channels                           | UXR0164A                                                               |  |

<sup>\*</sup> You may use any External Controller of your choice. Keysight recommends using the HP Z8 G4 Workstation to scale up your system for multi-chassis operations.

For information about the recommended BIOS and Windows system settings in the External Controller being used along with one or more M5000-series modules, refer to

http://www.keysight.com/find/PXIAXIePCBIOS and Windows Settings.

To connect the HP Z8 G4 workstation as an external controller to the M9046A PXIe chassis, you require the following additional products:

- · M9049A PCIe High Performance Host Adapter

- M9023A PXIe High Performance System Module

#### · Y1201A PCIe cable

The M5000-series modules require specific Keysight cables that have been customized for connectivity with the M9032x SSM modules and M9046A PXIe high-performance chassis. Table 5 lists the cables that you may procure for the configuration of a single/multi-chassis multi-system setup.

Table 5 Customized cables for use with M5300A PXIe RF AWGs

| Cable type       | Specification                              | Model number |  |

|------------------|--------------------------------------------|--------------|--|

| System Sync/Link | x4-x4, 0.5M                                | Y1320A       |  |

|                  | x4-x4, 1.0M                                | Y1321A       |  |

|                  | x8-2, x4, 0.5M                             | Y1323A       |  |

|                  | x8-2, x4, 1.0M                             | Y1324A       |  |

|                  | x8-x8, 0.5M                                | Y1326A       |  |

|                  | x8-x8, 1.0M                                | Y1327A       |  |

|                  | x8-x8, 2.0M                                | Y1329A       |  |

| MCX(m) to MCX(m) | phase stable, 0.3m                         | Y1330A       |  |

|                  | phase stable, 1.0m                         | Y1331A       |  |

|                  | phase stable, 2.0m                         | Y1332A       |  |

| SMA(m)-SMP(f)    | 0.3m                                       | Y1333A       |  |

| Cat-5            | RJ-45 connectors (to interconnect chassis) |              |  |

NOTE

Optimum phase coherency and stability between analog channels is achieved by distributing the external Analog Clock over the MCX to MCX cables and power dividers in a balanced star configuration. You may use cables with different lengths, but the total propagation delay of the Analog clock from its common source (usually the Leader chassis) to each module Ext. Ref. clock input should be equal.

The complexity of your quantum computing system shall determine the quantity of modules and cables that should be procured.

For more information about the cables that you wish to procure, contact Keysight Support.

# Section 1.2: About M5300x software features

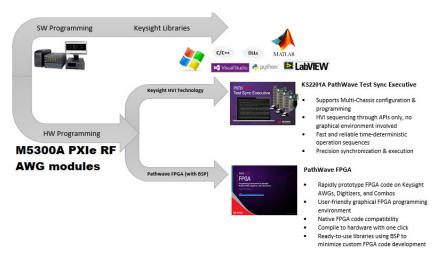

The Keysight M5300x software, which comprises of drivers, programming libraries and Software Front Panel for the M5300A module, provides a comprehensive platform to perform the basic operations pertaining to the High-Speed AWG modules. The M5300x software also supports the Hardware FPGA reprogramming, which is done using the PathWave FPGA Board Support Package. Moreover, the M5300x software API is powered by the KS2201A PathWave Test Sync Executive software for performing real-time operations and HVI sequencing.

Figure 12 Model depicting the M5300x software capabilities

# 1.2.1: Waveform formats in the M5300x SW

You may load waveform files using the M5300x SFP or API.

To load waveform files using the SFP, see "Configuring Waveform Memory and Queue" on page 121.

The createFromFile (file\_path, waveform\_id, type) method in the M5300x SW API for loading a file from the disk is shown below, along with the waveformType enumeration that tells the API how to handle the waveform.

#### C#

ArbitraryWaveform.createFromFile(string filePath, int waveformId, WaveformFileTypeEnum waveformType)

#### Python

arbitrary\_waveform.create\_from\_file(filePath, waveformId, waveformType)

Table 6 Enum value to handle data

| Value for waveformType enum | Data handling                                                          |

|-----------------------------|------------------------------------------------------------------------|

| Analog                      | The file is treated as real value only csv or binary file.             |

| IQ                          | The file is treated as having IQ data in csv, binary or wfm format.    |

| Digital                     | The file is treated as having integer IQ data in csv or binary format. |

1

NOTE

The Signal Studio waveform file (WFM format) only supports the IQ waveform type. The waveform file is generated using the following software licenses - N7631APPC and N7631RAWC.

The M5300A module requires that data be presented in 16 sample increments. If the waveform presented to the driver is not an integer multiple of 16 samples, the driver 'pads 0s' to the waveform and returns a warning in the error queue that the waveform has been 'zero padded'.

# Binary Floating Point Data

Values are stored in IEEE 754 double precision (64 bit) floating point values normalized between -1 and 1. On loading these values are converted to the nearest sample value. The floating point values are laid out in an array. For IQ waveforms the first value in the pair is the I value followed by the Q value.

#### Real values (ANALOG)

Point 0

Point 1

Point 2

• •

Point N-1

#### IQ Data (IQ)

Point 0 I

Point 0 Q

Point 1 I

Point 1 Q

Point 2 I

Point 2 Q

. . .

Point N-1 I

Point N-1 Q

# Binary Digital Data

This format contains the IQ pairs of data to be sent to the DAC. The data is interpreted as being stored as 16 bit signed integers (ranging from -32768 to 32767).

#### Integer Data (DIGITAL)

Point 0 I

Point 0 0

Point 1 I

Point 1 Q

Point 2 I

Point 2 Q

```

Point N-1 I

```

### **Invalid Values**

The following values are considered invalid and if encountered, the driver will throw an exception.

- Infinity

- NaN

- · Values out of the range (-1, 1)

# CSV Data (CSV Floating Point Data)

For real valued waveforms, the format is simply a list of floating point values between -1 and 1.

#### Real Values (ANALOG)

```

Point 0

Point 1

Point 2

...

Point N - 1

```

For IQ waveforms, the format is:

#### IQ Data (IQ)

```

Point 0 I, Point 0 Q

Point 1 I, Point 1 Q

Point 2 I, Point 2 Q

...

Point N-1 I, Point N-1 Q

```

Note that the CSV format has the same rules about invalid values as the binary format.

# **CSV** Digital Data

The CSV digital format follows the same rules as the floating point data except that data must be in the form of 16 bit signed integers (ranging from -32768 to 32767). Values that are above or below the possible values of samples will cause an exception to be thrown.

#### Integer Data (DIGITAL)

```

Point 0 I, Point 0 Q

Point 1 I, Point 1 Q

Point 2 I, Point 2 Q

...

Point N-1 I, Point N-1 Q

```

1

NOTE

The CSV formats support single line comments in starting with '!', '%' or '#' and ignoring any characters after that character until the end of the line. Valid CSV data can occur prior to the comment character and will be parsed normally by the SW.

# 1.2.2: Creating Waveform files in M5300x SW drivers

Table 7 lists the conditions to create a waveform file that is recognized and processed by the M5300x SW drivers.

Table 7 Conditions for creating the Waveform types in M5300x SW

| Waveform type | Waveform creation method using     | Value range in the array / file | M5300x API to use             |

|---------------|------------------------------------|---------------------------------|-------------------------------|

|               | With numpy array (one dimensional) | between -1.0 to 1.0             | create()                      |

| Analog        | With .bin File (single column)     |                                 | <pre>create_from_file()</pre> |

|               | With .csv File (single column)     |                                 | <pre>create_from_file()</pre> |

| Digital       | With numpy array (one dimensional) |                                 | create_int16()                |

|               | With .bin File (single column)     | between -32768 to 32767         | <pre>create_from_file()</pre> |

|               | With .csv file (two columns)       |                                 | <pre>create_from_file()</pre> |

NOTE

When you load an analog waveform using the <code>create\_from\_file()</code> API, the original values from the .bin file are inserted at even rows, while zeroes are padded at odd rows - effectively doubling the data size to convert into IQ format.

The doubling of data size doesn't occur in case of a digital waveform.

#### •

# 1.2.3: Data transfer speed in M5300x SW

# Normal APIs

Table 8 Average time and data transfer rate measured per waveform using the create() API in Python

| Number of Points (per Waveform) | Average Time (ms) | Average Data Transfer Rate (MB/s) |

|---------------------------------|-------------------|-----------------------------------|

| 64                              | 0.18              | 0.6                               |

| 500                             | 0.2               | 4.9                               |

| 1000                            | 0.2               | 9.69                              |

| 5000                            | 0.31              | 31.57                             |

| 10000                           | 0.41              | 48.23                             |

| 100000                          | 2.59              | 73.5                              |

| 500000                          | 15.9              | 59.8                              |

| 1000000                         | 35.8              | 53.2                              |

# Remote APIs

Table 9 Average time and data transfer rate measured per waveform using the create() API in Python

| Number of Points (per Waveform) | Average Time (ms) | Average Data Transfer Rate (MB/s) |

|---------------------------------|-------------------|-----------------------------------|

| 64                              | 0.39              | 0.32                              |

| 500                             | 0.42              | 2.35                              |

| 1000                            | 0.47              | 4.4                               |

| 5000                            | 0.8               | 12.39                             |

| 10000                           | 1.24              | 16.1                              |

| 100000                          | 10.18             | 18.7                              |

| 500000                          | 61.2              | 15.5                              |

| 1000000                         | 122.3             | 15.58                             |

# 1.2.4: Measured values in M5300x SW

Table 10 Minimum and maximum values of parameters used in M5300x SW

| Parameter                                                        | Minimum value                     | Typical value | Maximum value                                     | Description                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------|-----------------------------------|---------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Waveform Size per channel                                        | 64 Samples (I+Q)                  | -             | 1G Samples (I+Q) =<br>1,073,741,824 Samples (I+Q) | Min/Max number of samples in a waveform.                                                                                                                                                                                                                                                            |

| Waveform length in time                                          | 64 Samples / 4.8 GSa/s = 13.33 ns | -             | 1,073,741,824 Samples / 4.8 GSa/s = 223.69 ms     | Min and Max waveform length in time.                                                                                                                                                                                                                                                                |

| Waveform Granularity                                             | 16 Samples (I+Q)                  | -             | -                                                 | Number of samples in a waveform should be integral multiple of 16 (I+Q).                                                                                                                                                                                                                            |

| start_delay                                                      | 0                                 | 0             | ((2^24) - 1)*3.33 ns<br>= 55868.125 μs            | Amount of time a waveform start can be additionally delayed.                                                                                                                                                                                                                                        |

| Skew value                                                       | -24                               | 0             | +24                                               | Skew adjustment range in number of Samples (I+Q).                                                                                                                                                                                                                                                   |

| Number of Waveforms per<br>channel                               | 1                                 | -             | 4096                                              | Min/Max number of different waveforms that can be programmed in memory per channel. Note that total space in memory is 1G Samples per channel.                                                                                                                                                      |

| Number of entries in request queue                               | 1                                 | -             | 4096                                              | Number of Waveform<br>Requests that can be<br>programmed per channel.                                                                                                                                                                                                                               |

| Number of cycles per request queue entry                         | 1                                 | 1             | ((2^16) - 1) =<br>65535                           | Number of times a waveform request should be played. 0 = infinite cycles.                                                                                                                                                                                                                           |

| Minimum sample size for<br>gapless cyclic play with cycle =<br>1 | 12,000 samples                    | -             | -                                                 | To play continuous waveform in cyclic mode, our estimate is minimum 12000 sample sized waveform with cycle = 1. If you have are playing more than 1 cycle, then the minimum sample size requirement for gapless play will be less, because cycles will allow more time to buffer the next waveform. |

#### Section 1.3: About PathWave FPGA and BSP

#### 1.3.1: Using PathWave FPGA

The M5300x software supports the KF9000B PathWave FPGA Programming Environment (commonly known as PathWave FPGA) to program custom logic into the instrument FPGA.

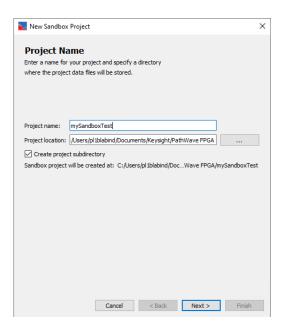

PathWave FPGA provides a complete FPGA design flow from design creation to simulation to GateWare deployment to Hardware/Gateware verification. This environment provides an easy-to-use GUI, where you may create bitstream images targeted to a sandbox in the Keysight FPGA.

Refer to "Downloading required software" on page 42 for information about Keysight's landing page for PathWave FPGA software installer. For more information regarding the PathWave FPGA software, refer to the embedded help file or the KF9000B PathWave FPGA Programming Environment Document Library.

NOTE

The PathWave FPGA is a licensed software. Contact Keysight Support for more information on procuring the respective licenses.

#### 1.3.2: Using BSP with PathWave FPGA

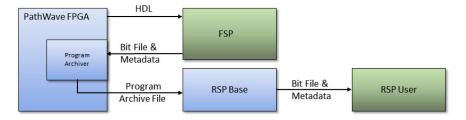

PathWave FPGA, by itself, does not provide access to any of the controls, which are associated with the Keysight M5300A PXIe modules. You must install the Board Support Package (BSP) to leverage the features within the PathWave FPGA software for your design.

The Board Support Package (BSP) comprises of two parts—an FPGA Support Package (FSP) and a Runtime Support Package (RSP). These are installed separately from PathWave FPGA.

The FSP is that portion of the BSP that allows you to build a bit file for the target FPGA. It is consumed by PathWave FPGA to support design creation and sandbox compilation; everything that is performed without the physical hardware.

The RSP is that portion of the BSP that allows you to control your target FPGA. It provides an API that you can use to download and verify your FPGA bit image. You may use the RSP to load design images onto the hardware and perform simple register and streaming accesses to one or more sandboxes.

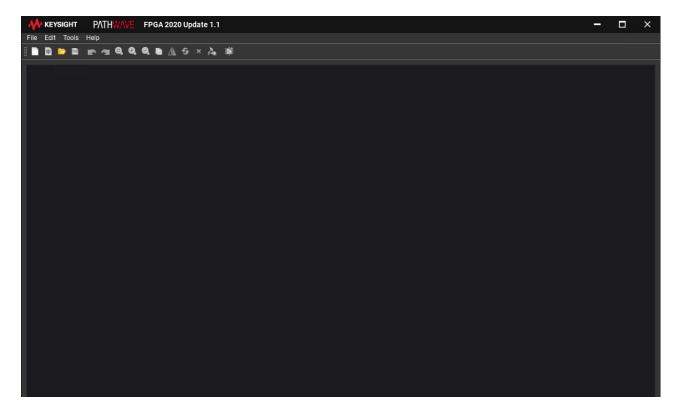

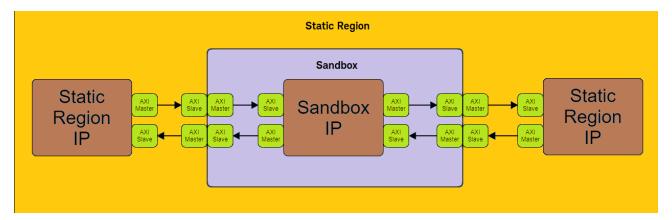

The FPGA design consists of two regions: the static region and the sandbox region. The static region for each supported module is defined within BSP and cannot be modified. This region defines the implementation of the FPGA interfaces to external resources, and defines the interfaces to the sandbox. A static region implementation can define one or more sandbox regions in an FPGA design. The sandbox region contains the user specific FPGA design. The interface of the sandbox depends on the static region implementation. A specific design flow is promoted by PathWave FPGA, called Partial Reconfiguration (PR). In a PR flow, a full FPGA reconfiguration is only necessary once for a given static region version. The sandboxes can be reconfigured anytime, without a full reconfiguration, and without stopping the current operation of the FPGA.

To perform FPGA designing, the BSP must be installed on the same machine as the PathWave FPGA software. Both PathWave FPGA software and the BSP function together and cannot be used individually.

To control the front panel IO on the M5300A modules, the M5300x API allows you to control the hardware.

For installation instructions regarding the PathWave FPGA Board Support Package, see "Installing required software" on page 43.

For more information regarding the PathWave FPGA interface available for the Board Support Package corresponding to the M5300A module, refer to the respective help file embedded in the PathWave FPGA software.

#### 1

# Section 1.4: About KS2201A PathWave Test Sync Executive software

The KS2201A PathWave Test Sync Executive software is a programming environment based on Keysight's Hard Virtual Instrument (HVI) technology, that enables you to develop and execute synchronous real-time operations across multiple instruments. The real-time sequencing and synchronization capabilities of the PathWave Test Sync Executive software make it a powerful tool for *Multi-Input Multi-Output (MIMO)* applications that require tight synchronization and real-time control and feedback in areas such as Quantum Computing.

#### 1.4.1: About HVI Technology

HVI technology enables you to program one or multiple instruments to execute time-deterministic sequences of operations and execute them with precise synchronization. It achieves this by deploying an executable code into each instrument's HW to be executed by the HVI engine or processor integrated into the instrument. The code executes on these engines in parallel, across multiple instruments. The new user-defined HW operation of the group of instruments is called a Hard Virtual Instrument or just HVI. The sequences of operations or instructions executed by the HVI engines are called HVI sequences. On top of the advantages inherent of the new use model, several other features have been added, such as extended multi-chassis capabilities and expanded product support.