# **D9040EDPV eDP Test Application**

METHODS OF IMPLEMENTATION

# Notices

### © Keysight Technologies 2023

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

# Trademarks

UNIX is a registered trademark of UNIX System Laboratories in the U.S.A. and other countries. Target is copyrighted by Thru-Put Systems, Inc.

### Version

Version 1.30.0.0

Edition

July 2023

Available in electronic format only

### Keysight Technologies, Inc. 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

# Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE

# TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

# U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no

greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

# Safety Notices

# CAUTION

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

# WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

# Contents

# 1 Overview

eDP Automated Testing-At a Glance / 8 Licensing Information / 9 Required Equipment and Software / 10 Hardware / 10 Software / 11 In This Book / 12 See Also / 12

# 2 Installing the Test Application and Licenses

Installing the Test Application / 14 Installing the License Key / 15 Using Keysight License Manager 5 / 15 Using Keysight License Manager 6 / 16

## 3 Preparing to Take Measurements

Calibrating the Oscilloscope / 20 Starting the eDP Test Application / 21 Setting Up the Transmission Path Test Point / 22 Overview on Connection Points for Source Tests / 23

# 4 eDP Automated Source Differential Tests

Eye Diagram Test / 26 Test Overview / 26 Test Conditions / 26 Test Procedure / 26 Viewing Test Results / 27 Non ISI Jitter Test / 29 Test Overview / 29 Test Conditions / 29 Test Procedure / 29 Viewing Test Results / 30 Total Jitter Test / 31 Test Overview / 31 Test Conditions / 31 Test Procedure / 31 Viewing Test Results / 32 Deterministic Jitter Test / 33 Test Overview / 33 Test Conditions / 33 Test Procedure / 33 Viewing Test Results / 33 Random Jitter Test / 35 Test Overview / 35 Test Conditions / 35 Test Procedure / 35 Viewing Test Results / 35 Peak to Peak Differential Voltage Test / 37 Test Overview / 37 Test Conditions / 38 Test Procedure / 39 Viewing Test Results / 39 Differential Voltage Level Test / 43 Test Overview / 43 Test Conditions / 44 Test Procedure / 45 Viewing Test Results / 45 Differential Voltage Level Ratio Test / 48 Test Overview / 48 Test Conditions / 50 Test Procedure / 51 Viewing Test Results / 51 Pre-Emphasis Level Test / 55 Test Overview / 55 Test Conditions / 57 Test Procedure / 57 Viewing Test Results / 58

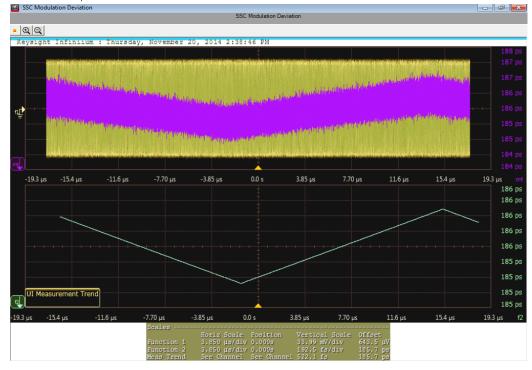

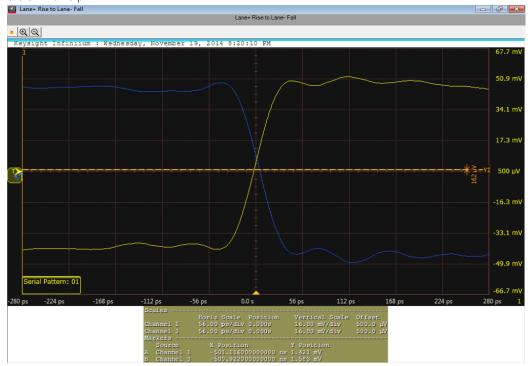

Pre-Emphasis Level Delta Test / 61 Test Overview / 61 Test Conditions / 63 Test Procedure / 64 Viewing Test Results / 64 Rise/Fall Time Test / 70 Test Overview / 70 Test Conditions / 70 Test Procedure / 70 Viewing Test Results / 70 Inter Pair Skew Test / 73 Test Overview / 73 Test Conditions / 73 Test Procedure / 74 Viewing Test Results / 74 Main Link Frequency Compliance Test / 75 Test Overview / 75 Test Conditions / 75 Test Procedure / 75 Viewing Test Results / 76 SSC Modulation Frequency Test / 78 Test Overview / 78 Test Conditions / 78 Test Procedure / 78 Viewing Test Results / 78 SSC Modulation Deviation Test / 80 Test Overview / 80 Test Conditions / 80 Test Procedure / 80

## 5 eDP Automated Source Single-Ended Tests

Intra Pair Skew Test / 84 Test Overview / 84 Test Conditions / 84 Test Procedure / 85 Viewing Test Results / 85

Viewing Test Results / 81

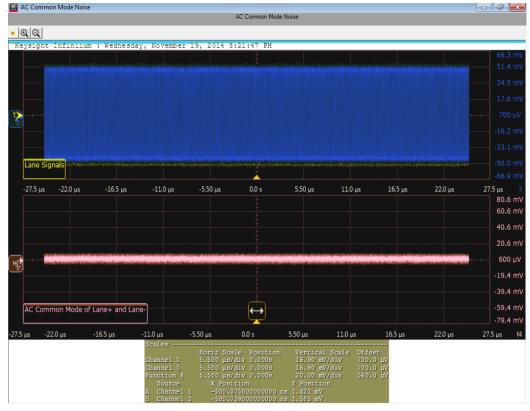

AC Common Mode Noise Test / 87 Test Overview / 87 Test Conditions / 87 Test Procedure / 87 Viewing Test Results / 88 Single-Ended Rise and Fall Time Mismatch Test / 89 Test Overview / 89 Test Conditions / 89 Test Procedure / 89 Viewing Test Results / 90

### 6 eDP Automated Source AUX Channel Physical Layer Tests

Connection Setup for AUX Channel Tests / 92 AUX Channel Unit Interval Test / 93 Test Overview / 93 Test Conditions / 93 Test Procedure / 93 PASS Condition / 93 AUX Channel Eye Test / 94 Test Overview / 94 Test Conditions / 94 Test Procedure / 94 PASS Condition / 95 AUX Channel Peak to Peak Voltage Test / 96 Test Overview / 96 Test Conditions / 96 Test Procedure / 96 PASS Condition / 97 AUX Channel Eye Sensitivity Calibration / 98 Test Overview / 98 Test Conditions / 98 Test Procedure / 98 PASS Condition / 98 AUX Channel Eye Sensitivity Test / 99 Test Overview / 99 Test Conditions / 99 Test Procedure / 99 PASS Condition / 99

Keysight D9040EDPV eDP Test Application Methods of Implementation

# 1 Overview

eDP Automated Testing—At a Glance 8 Required Equipment and Software 10 In This Book 12

# eDP Automated Testing-At a Glance

The Keysight D9040EDPV eDP Test Application for Embedded DisplayPort (eDP) standard provides a framework to use the Keysight Infiniium DSOs or UXRs to perform compliance testing on an Embedded DisplayPort Source device.

The Keysight D9040EDPV eDP Test Application:

- Lets you select individual or multiple tests to run.

- Lets you identify the device being tested and its configuration.

- · Shows you how to make oscilloscope connections to the device under test.

- Automatically checks for proper oscilloscope configuration.

- Automatically sets up the oscilloscope for each test.

- Provides detailed information for each test that has been run and lets you specify the thresholds at which marginal or critical warnings appear.

- · Creates a printable HTML report of the tests that have been run.

The eDP Test Application allows you to choose the eDP standard (either eDP 1.5 or eDP 1.4b) that is implemented on the DUT, based on which you may run compliance tests. Depending on the standard you select, the application provides the following tests:

| Test Name                         | References                                             | References                                                                |

|-----------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------|

|                                   | eDP 1.4b                                               | eDP 1.5                                                                   |

| Eye Diagram                       | eDP Standard Version 1.4, Section 4.6                  | RBR, HBR, HBR2 (CTLE):<br>eDP 1.5, Section 4.7.1, Table 4-22              |

|                                   |                                                        | HBR3 (CTLE Only):<br>eDP 1.5, Section 4.7.1, Table 4-23                   |

|                                   |                                                        | HBR3 (CTLE + DFE):<br>eDP 1.5, Section 4.7.1, Table 4-24                  |

| Non ISI Jitter                    | DisplayPort Standard Version 1. Revision 2, Table 3-23 | RBR, HBR, HBR2 (CTLE):<br>DP CTS 1.4a, Rev 1.0, Section 3.9.5, Table 3-45 |

|                                   |                                                        | HBR3 (CTLE Only):<br>eDP 1.5, Section 4.6.3, Table 4-15                   |

|                                   |                                                        | HBR3 (CTLE + DFE):<br>eDP 1.5, Section 4.6.3, Table 4-15                  |

| Total Jitter                      | DisplayPort Standard Version 1. Revision 2, Table 3-23 | eDP 1.5, Section 4.6.2, Table 4-14                                        |

| Deterministic Jitter              | DisplayPort Standard Version 1. Revision 2, Table 3-23 | eDP 1.5, Section 4.6.2, Table 4-14                                        |

| Random Jitter                     | DisplayPort Standard Version 1. Revision 2, Table 3-23 | DisplayPort Standard Version 1. Revision 2,<br>Table 3-23                 |

| Peak to Peak Differential Voltage | eDP Standard Version 1.4b (Section 4.4,<br>Table 4-9)  | eDP 1.5, Section 4.5, Table 4-11                                          |

| Differential Voltage Level        | eDP Standard Version 1.4, Section 4.3                  | eDP 1.5, Section 4.5, Table 4-11                                          |

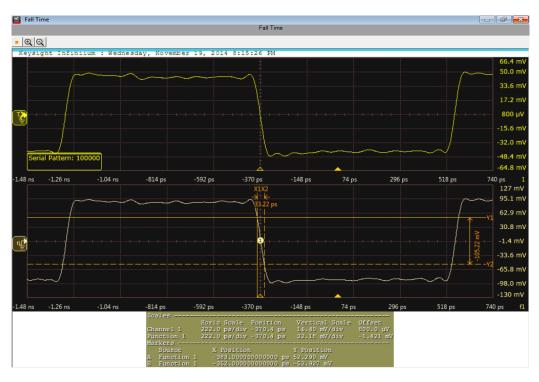

| Pre-Emphasis Level                | eDP Standard Version 1.4, Section 4.3                  | eDP 1.4, Section 4.3                                                      |

#### Table 1 Source Electrical Specification (Differential and Single-Ended) Tests by Standard Reference

| Test Name                                  | References                                                             | References                                                             |

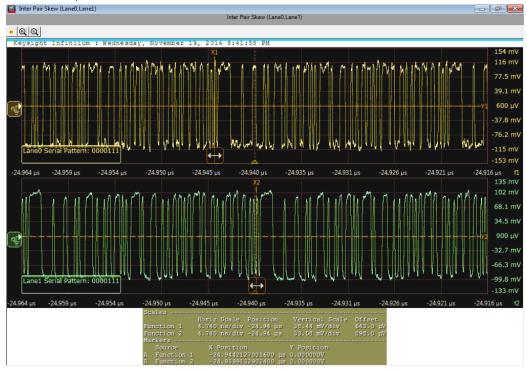

|--------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|

| Rise/Fall Time                             | eDP Standard Version 1.4, Section 4                                    | DP 1.1 CTS, Section 3.6                                                |

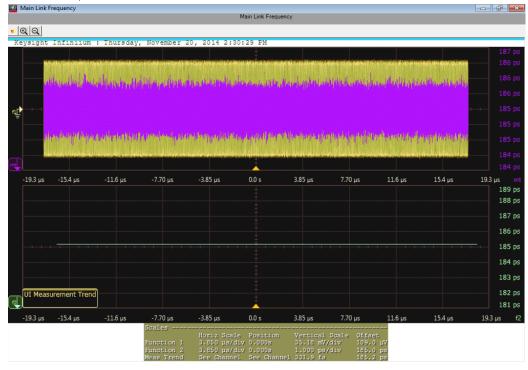

| Inter Pair Skew                            | eDP Standard Version 1.4, Section 4                                    | RBR, HBR, HBR2:<br>eDP CTG Version 1.0, Section 3.2.5                  |

|                                            |                                                                        | HBR3:<br>DP 1.4a CTS Version 1.1, Section 3.6, Table 3-33              |

| Main Link Frequency Compliance             | eDP Standard Version 1.4, Section 4.4,<br>Table 4-9                    | eDP 1.5, Section 4.5, Table 4-11                                       |

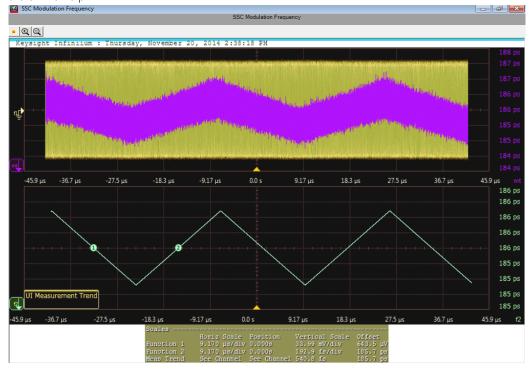

| SSC Modulation Frequency                   | eDP Standard Version 1.4, Section 4.4                                  | DP 2.0, Section 3.5.4, Table 3-38                                      |

| SSC Modulation Deviation                   | eDP Standard Version 1.4, Section 4.4                                  | DP 2.0, Section 3.5.4, Table 3-38                                      |

| Intra Pair Skew                            | eDP Standard Version 1.4, Section 4                                    | eDP 1.5, Section 4.5, Table 4-12                                       |

| AC Common Mode Noise                       | eDP Standard Version 1.4, Section 4                                    | RBR, HBR:<br>DP 2.0, Section D.2, Table D-3                            |

|                                            |                                                                        | HBR2:<br>DP 2.0, Section D.2, Table D-3                                |

|                                            |                                                                        | HBR3:<br>DP 2.0, Section D.2, Table D-3                                |

| Rise and Fall Time Mismatch                | DisplayPort Compliance Test Standard<br>Version 1, Section 3.7         | DP 1.1 CTS, Section 3.7                                                |

| AUX Channel Unit Interval                  | DisplayPort Standard 1.3, Section 3.4.2,<br>Table 3-4                  | DisplayPort Standard 1.3, Section 3.4.2, Table 3-4                     |

| AUX Channel Eye                            | DisplayPort Compliance Test<br>Specification Version 1.2b, Section 8.1 | DisplayPort Compliance Test Specification<br>Version 1.2b, Section 8.1 |

| AUX Channel Peak to Peak<br>Voltage        | eDP Standard Version 1.4b (Section 4.7.1,<br>Table 4-20)               | eDP Standard Version 1.5 Section 4.7.1, Table 4-20                     |

| AUX Channel Eye Sensitivity<br>Calibration | DisplayPort Compliance Test<br>Specification Version 1.2b, Section 8.2 | DisplayPort Compliance Test Specification<br>Version 1.2b, Section 8.2 |

| AUX Channel Eye Sensitivity                | DisplayPort Compliance Test<br>Specification Version 1.2b, Section 8.2 | DisplayPort Compliance Test Specification<br>Version 1.2b, Section 8.2 |

Licensing Information

Refer to the *Data Sheet* pertaining to eDP Test Application to know about the licenses you must install along with other optional licenses. Visit "http://www.keysight.com/find/D9040EDPV" and in the web page's **Document Library** tab, you may view the associated Data Sheet.

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

The licensing format for Keysight License Manager 6 differs from its predecessors. See "Installing the License Key" on page 15 to see the difference in installing a license key using either of the applications on your machine.

# Required Equipment and Software

Hardware

- Use one of the following Oscilloscope models:

- Digital Storage Oscilloscopes: All 90000A/90000X/90000Q/V-Series/Z-Series/Q-Series Infinitum scopes with a bandwidth of 16 GHz and above for eDP 1.4b and eDP 1.5.

- Keysight UXR Oscilloscopes

- Keyboard, qty=1, (provided with Keysight Infiniium Oscilloscope)

- Mouse, qty=1, (provided with Keysight Infiniium Oscilloscope)

Following fixtures and accessories are required to run the Keysight D9040EDPV eDP Test Application.

| Table 2 | Required fixtures and accessories |

|---------|-----------------------------------|

|---------|-----------------------------------|

| Required Equipment                                                                 | Quantity | Recommended Oscilloscope                                                          |

|------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------|

| Embedded DisplayPort Test Point Adapter<br>(Recommended: Wilder eDP TPA 30/40/50)* | 1        | Infiniium Series                                                                  |

| E2655A/B/C Probe De-Skew and Performance<br>Verification Kit                       | 1        | Infiniium Series                                                                  |

| BNC to SMA Converter                                                               | 4        | For Infiniium 90000A Series                                                       |

| SMA (male) to SMA (male) Converter                                                 | 4        | For Infiniium 90000X, 90000 Q Series, V-Series, Z-Series, Q-Series and UXR Series |

\* All Wilder Technologies Test Point Adapters require the Wilder Technologies DP-TPA-A Aux Control Board

### Table 3 InfiniiMax Series Probe Amplifiers with minimum 12 GHz bandwidth

| Required Equipment                                   | Quantity | Recommended Oscilloscope |

|------------------------------------------------------|----------|--------------------------|

| 1169A 12 GHz InfiniiMax II Series Probe Amplifier    |          |                          |

| N2832A 13 GHz InfiniiMax III+ Series Probe Amplifier | 5        | Infiniium Series         |

| N2800A 16 GHz InfiniiMax III Series Probe Amplifier  | Ū        |                          |

| MX0023A 25 GHz InfiniiMax RC Probe Amplifier         |          |                          |

### Table 4 InfiniiMax Series Probe Head with minimum 12 GHz bandwidth

| Required Equipment                                                               | Quantity | Recommended Oscilloscope |

|----------------------------------------------------------------------------------|----------|--------------------------|

| Physical Layer Tests                                                             |          |                          |

| N5380A InfiniiMax II 12 GHz Differential SMA Adapter                             |          |                          |

| N5444A InfiniiMax III 28 GHz SMA Probe Head                                      | 3        | Infiniium Series         |

| MX0105A InfiniiMax 20 GHz Differential SMA Probe<br>Head                         |          |                          |

| AUX Channel Physical Layer Tests                                                 |          |                          |

| E2677A InfiniiMax 12 GHz Differential Solder-In                                  |          |                          |

| E2678A/B InfiniiMax 12 GHz<br>Single-Ended/Differential Probe Head & Accessories | 2        | Infiniium Series         |

### Table 5 Automation Controllers (Optional)

| Required Equipment                                                                  | Quantity | Recommended Oscilloscope |

|-------------------------------------------------------------------------------------|----------|--------------------------|

| For Source DUT testing, Unigraf DPR-100 Compact<br>Sized DisplayPort Reference Sink | 4        | Infiniium Series         |

### Software

- The minimum version of Infiniium Oscilloscope Software (see the D9040EDPV eDP Test Application Release Notes)

- D9040EDPV eDP Test Application software

# In This Book

This manual describes the tests that are performed by the Keysight D9040EDPV eDP Test Application in more detail; it contains information from (and refers to) the eDP specification and it describes how the tests are performed.

- Chapter 1, "Overview" shows how to install and license the automated test application (if it was purchased separately).

- Chapter 2, "Installing the Test Application and Licenses" explains how to obtain the installer for

the automated test application and install the associated licenses (if it was purchased separately).

- Chapter 3, "Preparing to Take Measurements" describes how to launch the Keysight D9040EDPV eDP Test Application and gives a brief overview of how it is used.

- Chapter 4, "eDP Automated Source Differential Tests" describes the differential tests for interoperability verification of eDP sources.

- Chapter 5, "eDP Automated Source Single-Ended Tests" describes the single-ended tests for interoperability verification of eDP sources.

- Chapter 6, "eDP Automated Source AUX Channel Physical Layer Tests" describes the Auxiliary Channel Physical Layer tests for interoperability verification of both eDP source and sink devices along with an optional reference sink / reference source device, respectively.

### See Also

The Keysight D9040EDPV eDP Test Application's Online Help, which describes:

- Starting the eDP Test Application

- · Creating or Opening a Test Project

- Setting Up the Test Environment

- Selecting Tests

- Configuring Tests

- Verifying Physical Connections

- Running Tests

- Configuring Automation in the Test Application

- Viewing Results

- · Viewing HTML Test Report

- Exiting the Test Application

- Additional Settings in the Test App

Keysight D9040EDPV eDP Test Application Methods of Implementation

# 2 Installing the Test Application and Licenses

Installing the Test Application 14 Installing the License Key 15

If you purchased the D9040EDPV eDP Test Application separate from your Infiniium oscilloscope, you must install the software and license key.

# Installing the Test Application

- 1 Make sure you have the minimum version of Infiniium Oscilloscope software (see the Keysight D9040EDPV eDP Test Application release notes). To ensure that you have the minimum version, select **Help > About Infiniium...** from the main menu.

- 2 To obtain the eDP Test Application, go to Keysight website: "http://www.keysight.com/find/D9040EDPV".

- 3 In the web page's **Trials & Licenses** tab, click the **Details and Download** button to view instructions for downloading and installing the application software.

You must make sure to accept the installation of the *.NET framework* software, which is required to run the eDP Test Application.

## Installing the License Key

To procure a license, you require the Host ID information that is displayed in the Keysight License Manager application installed on the same machine where you wish to install the license.

Using Keysight License Manager 5

To view and copy the Host ID from Keysight License Manager 5:

- 1 Launch Keysight License Manager on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID that appears on the top pane of the application. Note that x indicates numeric values.

|       | Keysig | nt License Manager                        |

|-------|--------|-------------------------------------------|

| •     |        | Licenses on <b>Example (</b> localhost) Ċ |

| Conn  |        | Full computer name: .msr.is.keysight.com  |

| ectio |        | Host ID: PCSERNO, JBXXXXXXX               |

| ions  |        |                                           |

Figure 1 Viewing the Host ID information in Keysight License Manager 5

To install one of the procured licenses using Keysight License Manager 5 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager.

- 3 From the configuration menu, use one of the options to install each license file.

| 3 2 - □ ×                      |        |

|--------------------------------|--------|

| Why do I need these tools?     |        |

| Install License File           | Ctrl+I |

| Install License from Text      | Ctrl+T |

| View License Alerts            | Ctrl+L |

| Explore Transport URLs         |        |

| About Keysight License Manager |        |

Figure 2 Configuration menu options to install licenses on Keysight License Manager 5

For more information regarding installation of procured licenses on Keysight License Manager 5, refer to Keysight License Manager 5 Supporting Documentation.

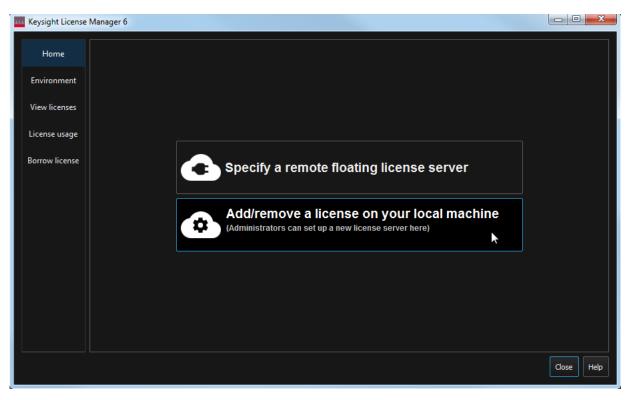

Using Keysight License Manager 6

To view and copy the Host ID from Keysight License Manager 6:

- 1 Launch Keysight License Manager 6 on your machine, where you wish to run the Test Application and its features.

- 2 Copy the Host ID, which is the first set of alphanumeric value (as highlighted in Figure 3) that appears in the Environment tab of the application. Note that x indicates numeric values.

| Keysight License | Manager 6                 |                                                                            |

|------------------|---------------------------|----------------------------------------------------------------------------|

| Home             | Licensing Version         | = Keysight License Manager Ver: 6.0.3 Date: Nov 9 2018                     |

|                  | Copyright                 | = © Keysight Technologies 2000-2018                                        |

| Environment      |                           |                                                                            |

|                  | AGILEESOFD_SERVER_CONFIG  |                                                                            |

| View licenses    | AGILEESOFD_SERVER_LOGFILE | = <u>C:\ProgramData\Keysight\Licensing\Log\server_log.txt</u>              |

|                  | SERVER_LICENSE_FILE       |                                                                            |

| License usage    | AGILEESOFD_LICENSE_FILE   | = C:\ProgramData\Keysight\Licensing\Licenses\Other;C:\ProgramData\Keysight |

|                  | FLO_LICENSE_FILE          | = C:\ProgramData\Keysight\Licensing\Licenses\Other;C:\ProgramData\Keysight |

| Borrow license   | KAL_LICENSE_FILE          | = C:\ProgramData\Keysight\Licensing\Licenses\Other;C:\ProgramData\Keysight |

|                  | AGILEESOFD_DEBUG_MODE     |                                                                            |

|                  | FLEXLM_TIMEOUT            |                                                                            |

|                  | Default Hostid            |                                                                            |

|                  | Ethernet Address          | = XXXXadXXXXbe XXbaXeaceXee<br>= XXXXadXXXXbe XXbaXeaceXee                 |

|                  | UUID                      | - AAAAdAAAAAde AAdaAeaceaee                                                |

|                  | Physical MAC Address      | -<br>= XXXXadXXXXbe PHY ETHER=XXbaXeaceXee                                 |

|                  | IP Address                | = 127.0.0.1                                                                |

|                  | Computer/Hostname         |                                                                            |

|                  | Username                  |                                                                            |

|                  |                           |                                                                            |

|                  | PATH                      | = C:\Program Files (x86)\Common Files\Intel\Shared Libraries\redist\intel6 |

|                  |                           |                                                                            |

|                  | •                         | •                                                                          |

|                  | Compact View              |                                                                            |

|                  |                           | Refresh Glose Help                                                         |

|                  |                           |                                                                            |

|                  |                           |                                                                            |

Figure 3 Viewing the Host ID information in Keysight License Manager 6

To install one of the procured licenses using Keysight License Manager 6 application,

- 1 Save the license files on the machine, where you wish to run the Test Application and its features.

- 2 Launch Keysight License Manager 6.

- 3 From the Home tab, use one of the options to install each license file.

Figure 4 Home menu options to install licenses on Keysight License Manager 6

For more information regarding installation of procured licenses on Keysight License Manager 6, refer to Keysight License Manager 6 Supporting Documentation.

### 2 Installing the Test Application and Licenses

Keysight D9040EDPV eDP Test Application Methods of Implementation

# 3

# Preparing to Take Measurements

Calibrating the Oscilloscope 20 Starting the eDP Test Application 21

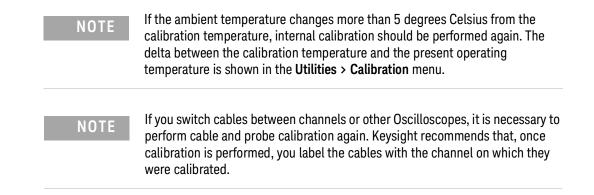

Before running the automated tests, you should calibrate the oscilloscope and probe. No test fixture is required for this application. After the oscilloscope and probe have been calibrated, you are ready to start the eDP Test Application and perform the measurements.

# Calibrating the Oscilloscope

If you have not already calibrated the oscilloscope, refer to the *User Guide* for the respective Oscilloscope you are using.

# Starting the eDP Test Application

1 Ensure that the eDP Device Under Test (DUT) is operating and set to desired test modes. To start the eDP Test Application: From the Infiniium Oscilloscope's main menu, select Analyze > Automated Test Apps > D9040EDPV eDP Test App.

| Z Embedded DisplayPort Test Application eDP Device 1                                          |          |

|-----------------------------------------------------------------------------------------------|----------|

| File View Tools Help                                                                          |          |

| Set Up Select Tests Configure Connect Run Automate Results HTML Report                        | <b>-</b> |

| Embedded DisplayPort Test Application Test Environment Setup                                  |          |

| Test Specification                                                                            |          |

| eDP 1.5 Y Physical Layer Tests                                                                | ] ]      |

| Test Environment Setup                                                                        |          |

| Device Definition Setup Test Setup                                                            |          |

| Device Definition Setup Completed. Test Setup Incomplete                                      |          |

| Show Normative Tests Only                                                                     |          |

| Test Controller Setup                                                                         |          |

| Test Controller UnigrafDPTC 🔽 Enable Automation Configure                                     |          |

| Script File C:\Program Files\Keysight\Infiniiur Browse Test Controller Dialog                 |          |

|                                                                                               |          |

|                                                                                               |          |

| Messages                                                                                      |          |

| Summaries (click for details) Details                                                         |          |

| G 2019-08-22 01:50:31:451 PM HTML Report Refreshed Application initialized and ready for use. |          |

| 2019-08-22 01:50:45:170 PM Ready                                                              |          |

|                                                                                               | ¥        |

| 0 Tests                                                                                       |          |

Figure 5 eDP Test Application Main Window

To understand the functionality of the various features in the user interface of the Test Application, refer to the *Keysight D9040EDPV eDP Test Application Online Help* available in the Help menu.

| HTML Report  | Shows a compliance test report that can be printed.                                                                                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Results      | Contains more detailed information about the tests that have been run. You can change the<br>thresholds at which marginal or critical warnings appear.                                                                                                                     |

| Automate     | Lets you construct scripts of commands that drive execution of the application.                                                                                                                                                                                            |

| Run          | Starts the automated tests. If the connections to the device under test need to be changed while multiple tests are running, the tests pause, show you how to change the connection, and wait for you to confirm that the connections have been changed before continuing. |

| Connect      | Shows you how to connect the oscilloscope to the device under test for the tests that are to be run                                                                                                                                                                        |

| Configure    | Lets you configure test parameters (for example, channels used in test, voltage levels, etc.).                                                                                                                                                                             |

| Select Tests | Lets you select the tests you want to run. The tests are organized hierarchically so you can select al tests in a group. After tests are run, status indicators show which tests have passed, failed, or not been run, and there are indicators for the test groups.       |

| Set Up       | Lets you identify and set up the test environment, including information about the device under test. The Test App includes relevant information in the final HTML report.                                                                                                 |

The task flow pane and the tabs in the main pane show the steps you take in running the automated tests:

NOTE

In the **Configure** tab, the values for all such Configuration parameters that are Oscilloscope-dependent, will correspond to the Oscilloscope Model (DSOs or UXRs), where you are running the Test Application.

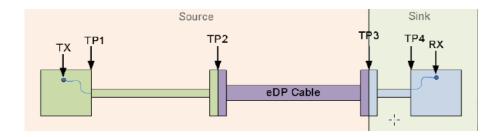

Setting Up the Transmission Path Test Point

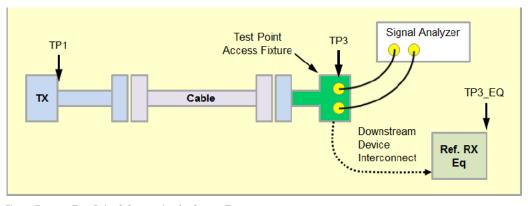

Figure 6 Embedded Link Test Point

The links in an Embedded DisplayPort (eDP) contain a Transmitter (TX) and a Receiver (RX), where the transmitter is connected to the Source device and the receiver to the Sink device. You may optionally set up connectors anywhere along the embedded channel. Taking into account various embedded topologies, eDP provides measurement of the physical layer attributes.

Figure 6 shows a pictorial representation of the embedded link transmission path test points to measure signal voltage and jitter on an embedded channel, which are:

| TP1 | eDP transmitter package pins            |

|-----|-----------------------------------------|

| TP2 | Source device eDP Cable Connector       |

| TP3 | Sink device (panel) eDP Cable Connector |

| TP4 | eDP receiver package pins               |

### Overview on Connection Points for Source Tests

This section describes the tests for interoperability verification of eDP sources. Sources must be tested either at point TP3 or point TP3\_EQ, where the latter is placed after the Reference Receiver Equalizer, as shown below in Figure 7. You must also include the actual eDP cable, which the system integrator intends to use (or a properly correlated model of this cable) for source test measurements. The analyzer and test point access fixtures from each test solution provider are identified in this document. Unless specifically stated under the test conditions, all supported lanes for the DUT must be evaluated.

Figure 7 Test Point 3 Connection for Source Tests

The Source Tests broadly include three categories namely:

- Source Differential Tests

- Source Single-Ended Tests

- Source AUX Channel Physical Layer Tests

### NOTE

All tests performed on the Source DUT are Normative tests only.

### 3 Preparing to Take Measurements

Keysight D9040EDPV eDP Test Application Methods of Implementation

# 4 eDP Automated Source Differential Tests

This section describes the differential tests for interoperability verification of eDP sources.

# Eye Diagram Test

#### Test Overview

The Eye Diagram Test evaluates the waveform to ensure that the timing variables and amplitude trajectories support the overall eDP system objective of Bit Error Rate in data transmission.

The source eye diagram performance provides the best visual aid to assess the interoperability potential by showing the amplitude and timing attributes of the signal and also provides an intuitive understanding of design margin.

### **Test Conditions**

| Specification                           | eDP Version 1.4b                                                                                                                                                               | eDP Version 1.5 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Test Point                              | TP3 and TP3_EQ                                                                                                                                                                 |                 |

| Bit Rate                                | All bit rates are supported.                                                                                                                                                   |                 |

| Voltage Level and<br>Pre-emphasis Level | The Source device sets the Voltage level and Pre-emphasis level for each supported data rate, such that it meets the Pass/Fail criteria as specified in the CTG Specification. |                 |

| SSC                                     | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions.                                                             |                 |

| Test Lane                               | All test lanes must generate a test pattern to induce crosstalk.                                                                                                               |                 |

| Test Pattern                            | Any of the supported test patterns                                                                                                                                             |                 |

Test Procedure

- 1 Validate and acquire the signal.

- 2 If equalizer is enabled, please set up the equalizer for TP3\_EQ, else please skip this step.

- 3 Determine the threshold of the signal by measuring  $V_{Top}$  and  $V_{Base}$ .

- 4 Measure the data rate and validate the test pattern.

- 5 If random noise is included, use "EZJIT Complete" to perform jitter separation base on the Time Interval Error (TIE) measurement of the signal.

- 6 Set up the clock recovery base on the clock recovery setting of the configuration variable.

- 7 Create eye diagram at the middle of the screen. The range of the eye diagram must be more than one Unit Interval (UI) but less than 2.5 UI.

- 8 To obtain the optimum eye height, compute the eye height at different passing points.

- 9 Load the eye mask and position it centrally at the middle of the eye diagram.

- a To measure with the "Dynamic" eye mask height location, note the center eye mask perimeter value and if required, modify the eye mask height vertices to the optimum eye height location.

- Note the center eye mask and compute the eye mask height and width. The eye mask supports only four vertices point center mask.

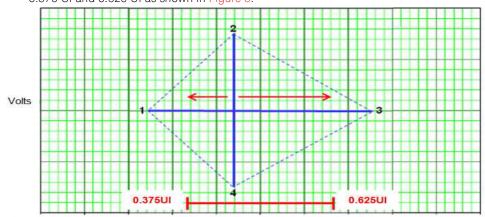

• To modify the eye mask height point, shift the eye mask height vertices horizontally between 0.375 UI and 0.625 UI as shown in Figure 8.

Figure 8 eDP TP3\_EQ Eye Mask for eDP 1.4b

- *b* To measure with the "Fixed" eye mask height location, load the eye mask directly without any modification.

- 10 Run the eye mask until you achieve the required number of Uls.

- 11 Check for any signal trajectories that may have entered into the eye mask.

### Viewing Test Results

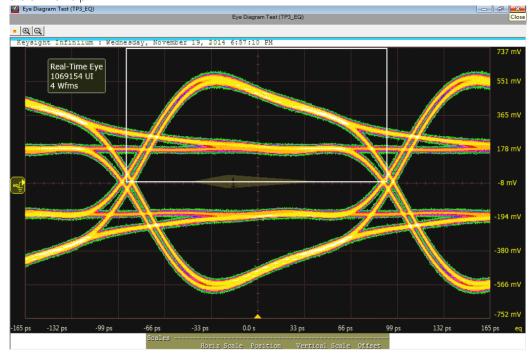

The measured eye diagram for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

For each test trial, click the **Results** tab to view the results. Click the desired test to view its result. The lower pane contains the displays the detailed description of the test results. A sample reference image based on the measured values is captured by the oscilloscope. Click the sample reference image to view the details. For information about viewing the test results, refer to **Viewing Results** in the online help.

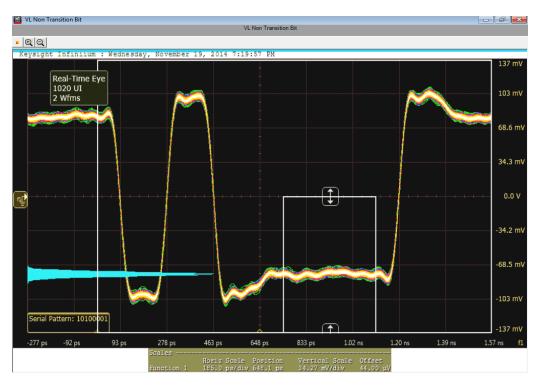

Figure 9 Reference Image for Eye Diagram Test

# Non ISI Jitter Test

#### Test Overview

The Non ISI (Inter Symbol Interference) Jitter Test evaluates the amount of Non ISI jitter accompanying the data transmission.

The overall system jitter budget defines the point of compliance for the Non ISI Jitter Test and the different amounts of jitter allocation that each system component is allowed to contribute. Exceeding any of these limits violates the component level jitter budget. Non ISI jitter must be limited in magnitude because the receiver is unable to compensate any higher amount of jitter.

### Test Conditions

| Specification                           | eDP Version 1.4b                                                                                                   | eDP Version 1.5                                                                           |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Test Point                              | TP3 and TP3_EQ                                                                                                     |                                                                                           |

| Bit Rate                                | All bit rates are supported.                                                                                       |                                                                                           |

| Voltage Level and<br>Pre-emphasis Level | 5                                                                                                                  | and Pre-emphasis level for each supported criteria as specified in the CTG Specification. |

| SSC                                     | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions. |                                                                                           |

| Test Lane                               | All test lanes must generate a test pattern to induce crosstalk.                                                   |                                                                                           |

| Test Pattern                            | Any of the supported test patterns                                                                                 |                                                                                           |

Test Procedure

- 1 Validate and acquire the signal.

- 2 Determine the threshold of the signal by measuring  $V_{Top}$  and  $V_{Base}$ .

- 3 Measure the data rate and validate the test pattern.

- 4 Set up the clock recovery base on the clock recovery setting in configuration variable.

- 5 Use "EZJIT Complete" to perform jitter separation base on the Time Interval Error (TIE) measurement of the signal.

- 6 Compute the Non ISI Jitter using the following equation:

### Non ISI Jitter = Total Jitter – Jitter<sub>ISI</sub>

where,  $Jitter_{ISI}$  is the ISI Jitter component induced by ISI, which is the peak-to-peak value of the histogram of rising edges or of the histogram of the falling edges, whichever is greater.

# NOTE

DFE will be enabled by default for HBR3 bit rate.

### Viewing Test Results

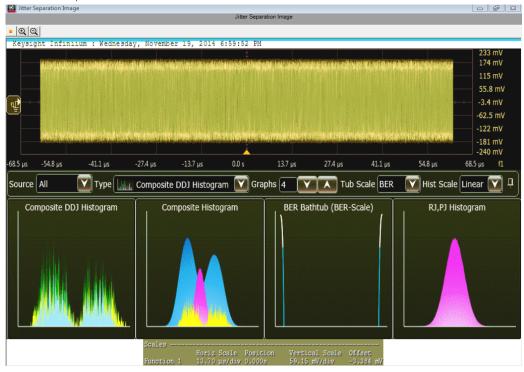

The measured Non ISI Jitter value for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

For each test trial, click the **Results** tab to view the results. Click the desired test to view its result. The lower pane contains the displays the detailed description of the test results. A sample reference image based on the measured values is captured by the oscilloscope. Click the sample reference image to view the details. For information about viewing the test results, refer to **Viewing Results** in the online help.

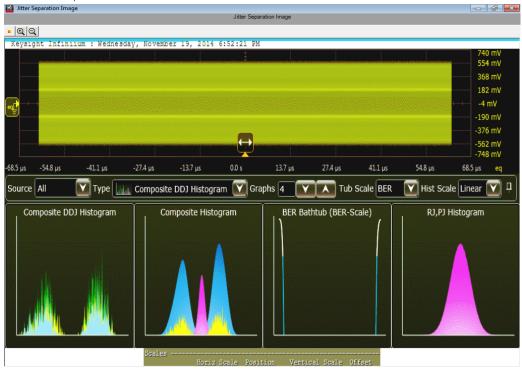

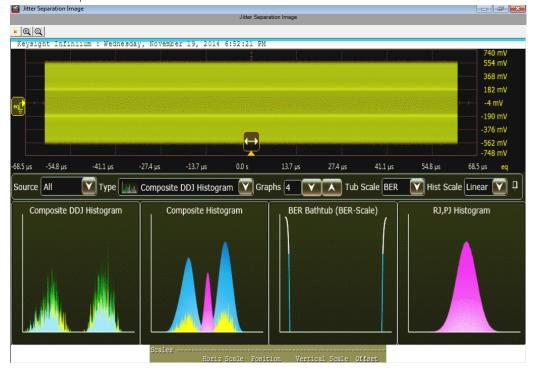

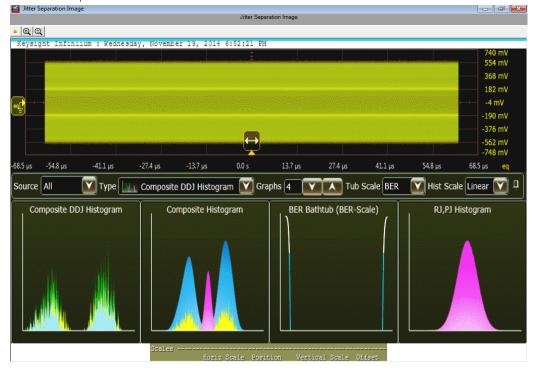

Figure 10 Reference Image for Non ISI Jitter Test

# Total Jitter Test

#### Test Overview

The Total Jitter Test evaluates the total jitter, which is a form of data time interval error (Data-TIE) jitter measurement, which accompanies data transmission at either an explicit bit error rate of 10<sup>-9</sup> or through an approved estimation technique.

Similar to Non ISI jitter, the overall system jitter budget defines the point of compliance for the Total Jitter Test and allocates different amounts of jitter that each system component is allowed to contribute. Exceeding any of these limits violates the component level jitter budget.

### Test Conditions

| Specification                           | eDP Version 1.4b                                                                                                   | eDP Version 1.5 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| Test Point                              | TP3 and TP3_EQ                                                                                                     |                 |

| Bit Rate                                | All bit rates ar                                                                                                   | e supported     |

| Voltage Level and<br>Pre-emphasis Level | Voltage level and Pre-emphasis level as set for the Eye Diagram test.                                              |                 |

| SSC                                     | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions. |                 |

| Test Lane                               | All test lanes must generate a test pattern to induce crosstalk.                                                   |                 |

| Test Pattern                            | Any of the supported test patterns                                                                                 |                 |

**Test Procedure**

- 1 Validate and acquire the signal.

- 2 If equalizer is enabled, please set up the equalizer for TP3\_EQ, else please skip this step.

- 3 Determine the threshold of the signal by measuring  $V_{\text{Top}}$  and  $V_{\text{Base}}$

- 4 Measure the data rate and validate the test pattern.

- 5 Set up the clock recovery base on the clock recovery setting of the configuration variable.

- 6 Use "EZJIT Complete" to perform jitter separation base on the Time Interval Error (TIE) measurement of the signal.

- 7 Use the Dual Dirac Technique to estimate the Total Jitter for bit error rate of 10<sup>-9</sup> using the following equation:

Total Jitter = Deterministic Jitter<sub>dd</sub> + n \* Random Jitter

where, Deterministic Jitter<sub>dd</sub> is the deterministic jitter, Random Jitter is the random jitter, which is a standard deviation value of an idealized pure noise process and n is the multiplier that is determined by the bit error ratio (n = 12.0 for bit error ratio of  $1 * 10^{-9}$ ).

## \_\_NOTE

DFE will be enabled by default for HBR3 bit rate.

### Viewing Test Results

The measured value of Total Jitter for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

For each test trial, click the **Results** tab to view the results. Click the desired test to view its result. The lower pane contains the displays the detailed description of the test results. A sample reference image based on the measured values is captured by the oscilloscope. Click the sample reference image to view the details. For information about viewing the test results, refer to **Viewing Results** in the online help.

Figure 11 Reference Image for Total Jitter Test

### Deterministic Jitter Test

### Test Overview

The Deterministic Jitter Test evaluates the deterministic jitter, which is also a form of Data-TIE jitter measurement, accompanying the data transmission.

Similar to the previous types of jitter, the overall system jitter budget defines the point of compliance for the Deterministic Jitter Test and allocates different amounts of jitter that each system component is allowed to contribute. Exceeding any of these limits violates the component level jitter budget.

### Test Conditions

| Specification                           | eDP Version 1.4b                                                                                                   | eDP Version 1.5 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| Test Point                              | TP3 and TP3_EQ                                                                                                     |                 |

| Bit Rate                                | All bit rates are supported                                                                                        |                 |

| Voltage Level and<br>Pre-emphasis Level | Voltage level and Pre-emphasis level as set for the Eye Diagram test.                                              |                 |

| SSC                                     | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions. |                 |

| Test Lane                               | All test lanes must generate a test pattern to induce crosstalk.                                                   |                 |

| Test Pattern                            | Any of the supported test patterns                                                                                 |                 |

Test Procedure

- 1 Validate and acquire the signal.

- 2 If equalizer is enabled, please set up the equalizer for TP3\_EQ, else please skip this step.

- 3 Determine the threshold of the signal by measuring  $V_{Top}$  and  $V_{Base}$ .

- 4 Measure the data rate and validate the test pattern.

- 5 Set up the clock recovery base on the clock recovery setting of the configuration variable.

- 6 Use "EZJIT Complete" to perform jitter separation base on the Time Interval Error (TIE) measurement of the signal.

DFE will be enabled by default for HBR3 bit rate.

Viewing Test Results

The measured Deterministic Jitter value for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

For each test trial, click the **Results** tab to view the results. Click the desired test to view its result. The lower pane contains the displays the detailed description of the test results. A sample reference image based on the measured values is captured by the oscilloscope. Click the sample reference image to view the details. For information about viewing the test results, refer to **Viewing Results** in the online help.

Figure 12 Reference Image for Deterministic Jitter Test

## Random Jitter Test

### Test Overview

The Random Jitter Test evaluates the random jitter, which is also a form of Data-TIE jitter measurement, accompanying the data transmission.

Similar to the previous types of jitter, the overall system jitter budget defines the point of compliance for the Random Jitter Test and allocates different amounts of jitter that each system component is allowed to contribute. Exceeding any of these limits violates the component level jitter budget.

### Test Conditions

| Specification                           | eDP Version 1.4b                                                                                                   | eDP Version 1.5 |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| Test Point                              | TP3 and TP3_EQ                                                                                                     |                 |

| Bit Rate                                | All bit rates are supported.                                                                                       |                 |

| Voltage Level and<br>Pre-emphasis Level | Voltage level and Pre-emphasis level as set for the Eye Diagram test.                                              |                 |

| SSC                                     | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions. |                 |

| Test Lane                               | All test lanes must generate a test pattern to induce crosstalk.                                                   |                 |

| Test Pattern                            | Any of the supported test patterns                                                                                 |                 |

Test Procedure

- 1 Validate and acquire the signal.

- 2 If equalizer is enabled, please set up the equalizer for TP3\_EQ, else please skip this step.

- 3 Determine the threshold of the signal by measuring  $V_{\text{Top}}$  and  $V_{\text{Base}}$

- 4 Measure the data rate and validate the test pattern.

- 5 Set up the clock recovery base on the clock recovery setting of the configuration variable.

- 6 Use "EZJIT Complete" to perform jitter separation base on the Time Interval Error (TIE) measurement of the signal.

DFE will be enabled by default for HBR3 bit rate.

Viewing Test Results

The measured random jitter value for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

For each test trial, click the **Results** tab to view the results. Click the desired test to view its result. The lower pane contains the displays the detailed description of the test results. A sample reference image based on the measured values is captured by the oscilloscope. Click the sample reference image to view the details. For information about viewing the test results, refer to **Viewing Results** in the online help.

Figure 13 Reference Image for Random Jitter Test

# Peak to Peak Differential Voltage Test

Test Overview

The Peak to Peak Differential Voltage Test evaluates the peak to peak voltage accompanying the data transmission.

You can measure the transition and non-transition voltage swings for each supported voltage level and pre-emphasis setting. To obtain the peak to peak voltage, you must combine the High and Low voltage measurements formed within each transition and non-transition voltage swing.

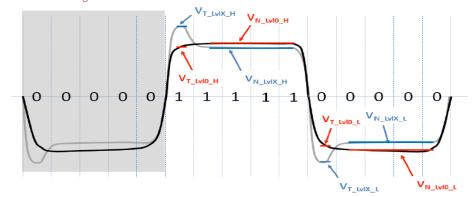

Compute the peak to peak voltages for transition and non-transition voltage swing for a given voltage level and pre-emphasis level (LvIX) using the following equations:

$$V_{T\_LvIX\_PP} = V_{T\_LvIX\_H} - V_{T\_LvIX\_L}$$

$$V_{N_{LVIX}PP} = V_{N_{LVIX}H} - V_{N_{LVIX}L}$$

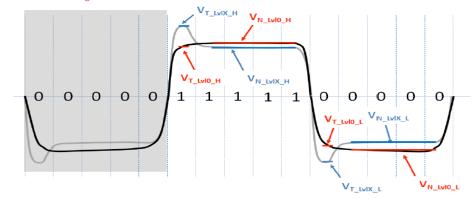

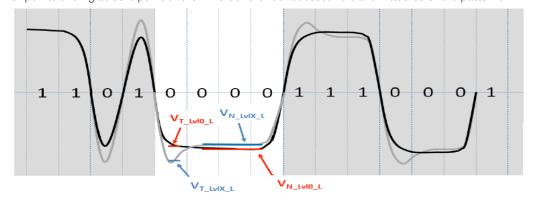

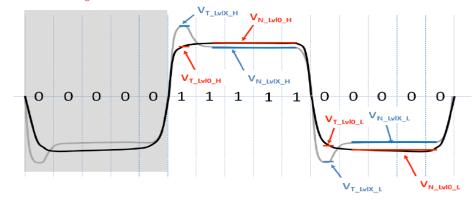

where  $V_{T\_LvIX\_PP}$  is the peak to peak voltage at the transition bit and  $V_{N\_LvIX\_PP}$  is the peak to peak voltage at the non transition bit. The constituent voltages  $V_{T\_LvIX\_H}$ ,  $V_{T\_LvIX\_L}$ ,  $V_{N\_LvIX\_H}$  and  $V_{N\_LvIX\_L}$  are identified in the following figures showing generalized pre-emphasis and non pre-emphasized waveforms.

The condition for Level 0 pre-emphasis is identified separately in the following figures but is merely a special case. The measurement of high and low voltage values is an average value derived from a specific number of UI obtained over a certain number of required test patterns.

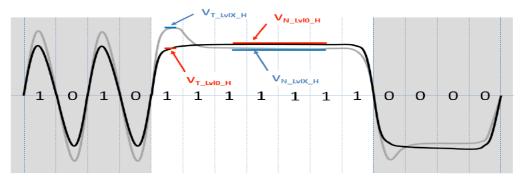

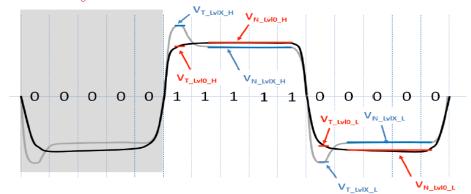

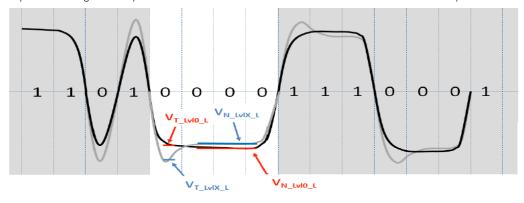

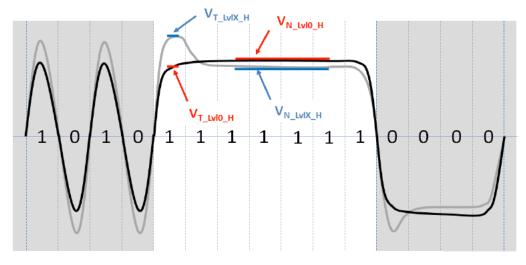

## For PLTPAT

There are specific qualifying patterns in the 80-Bit Custom pattern (PLTPAT) for 'High' and 'Low' voltage level measurements. These measurements require a 1-1-1-1-0-0-0-0-0 balanced pattern and no preconditioning is required on this pattern. The transition voltage measurements,  $V_{T_LvIX_H}$  and  $V_{T_LvIX_L}$  is the average value over the 40% to 70% UI points in the transition bit. The non-transition voltage measurement,  $V_{N_LvIX_H}$  and  $V_{N_LvIX_L}$  is the average value over three UI points ending at the 50% point of the 5<sup>th</sup> bit of the five successive transmitted 1s or 0s of the patterns. Refer to Figure 14.

Figure 14 High and Low Voltage Measurement for PLTPAT

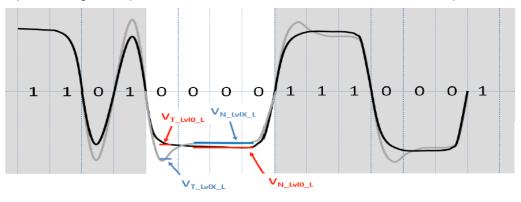

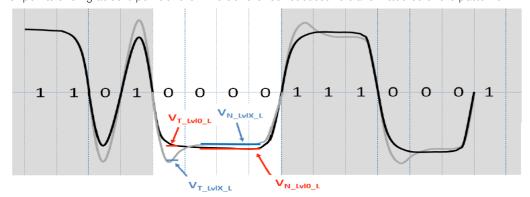

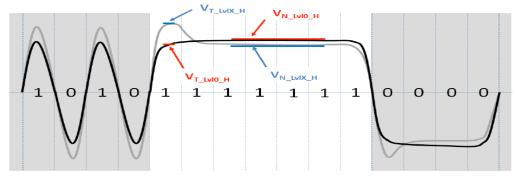

For PRBS7

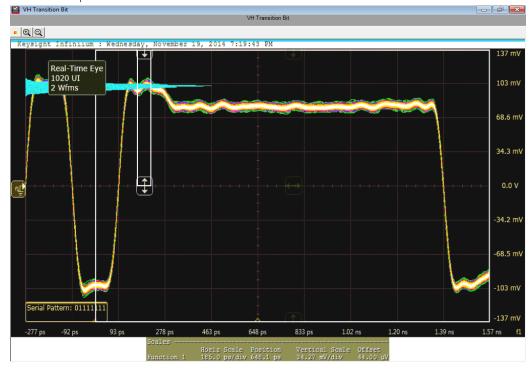

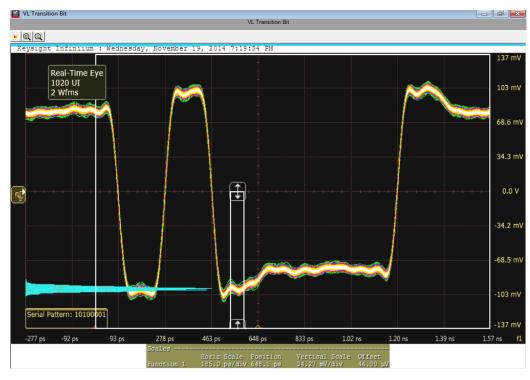

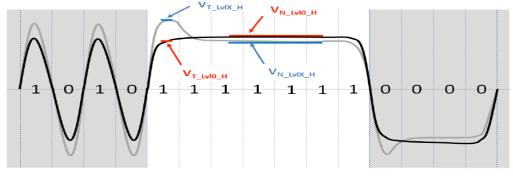

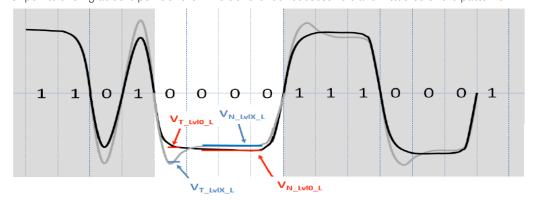

There are specific qualifying patterns in PRBS7 and other sequence for 'High' and 'Low' voltage level measurements. The 'High' level measurements require a 0-1-0-1-1-1-1-1-1 pattern and the 'Low' level measurements require a 1-0-1-0-0-0-1 pattern. Refer to Figure 15 and Figure 16. The first 3-bits in these patterns are a precondition to the transition measurements. The precondition bits for a transition to high level voltage measurement, are 0-1-0 and for a transition to low level voltage measurement are 1-0-1.

Figure 15 High Voltage Measurement for PRBS7

The transition voltage measurements,  $V_{T\_LvIX\_H}$  and  $V_{T\_LvIX\_L}$  are the average value over the 40% to 70% UI points in the transition bit. The non-transition voltage measurement,  $V_{N\_LvIX\_H}$  is the average value over three UI points ending at the 50% point of the 6<sup>th</sup> bit of the seven successive transmitted 1s of the patterns. The non-transition voltage measurement,  $V_{N\_LvIX\_L}$  is the average value over two UI points ending at 50% point of the 4<sup>th</sup> bit of the four successive transmitted 0s of the patterns.

Figure 16 Low Voltage Measurement for PRBS7

### Test Conditions

| Specification                           | eDP Version 1.4b                                                                                      | eDP Version 1.5 |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------|

| Test Point                              | TP                                                                                                    | 3               |

| Bit Rate                                | All bit rates are supported.                                                                          |                 |

| Voltage Level and Pre-emphasis<br>Level | Any Voltage level and Pre-Emphasis level that are compliant to all normative tests run on the Source. |                 |

| Specification | eDP Version 1.4b                                                                                                   | eDP Version 1.5 |

|---------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| SSC           | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions. |                 |

| Test Lane     | All test lanes must generate a test pattern to induce crosstalk.                                                   |                 |

| Test Pattern  | Any of the supported test patterns                                                                                 |                 |

#### **Test Procedure**

- 1 Validate and acquire the signal.

- 2 Determine the threshold of the signal by measuring  $V_{Top}$  and  $V_{Base}$ .

- 3 Measure the data rate and validate the test pattern.

- 4 Acquire the qualifying test pattern over the specific number of required patterns to measure the high voltage level.

- 5 Set up the Histogram to measure the average value of high voltage level for both transition and non-transition voltage levels.

- 6 Acquire the qualifying test pattern over the specific number of required patterns to measure the low voltage level.

- 7 Set up the Histogram to measure the average value of low voltage level for both transition and non-transition voltage levels.

- 8 Compute the peak to peak voltage for both transition and non-transition voltage levels using the following equations:

$$V_{T\_LvIX\_PP} = V_{T\_LvIX\_H} - V_{T\_LvIX\_L}$$

$$V_{N_{LVIX_{PP}}} = V_{N_{LVIX_{H}}} - V_{N_{LVIX_{L}}}$$

9 Obtain the value of the peak to peak differential voltage from the worst case of both transition and non-transition voltage measurements using the following equation:

$$V_{PP} = Worst Case (V_T LVIX PP, V_N LVIX PP)$$

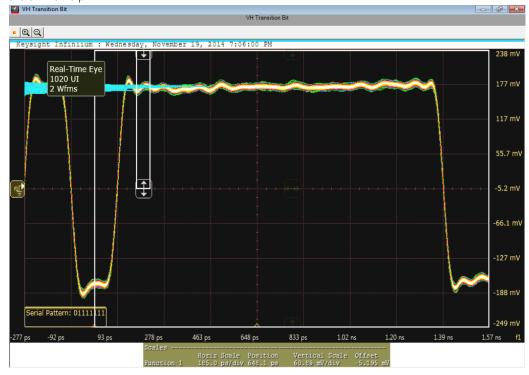

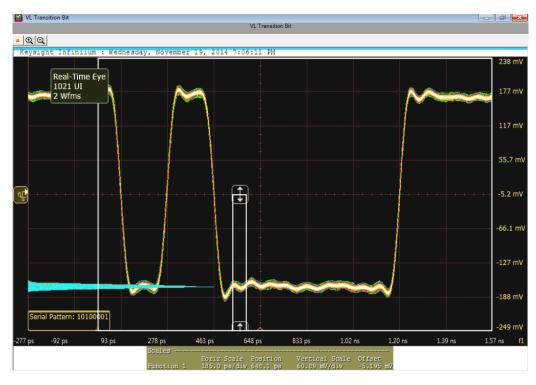

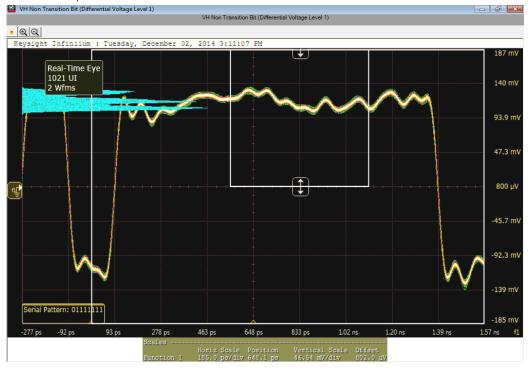

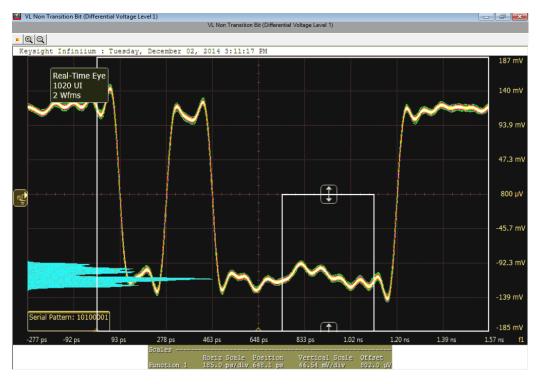

### Viewing Test Results

The measured value of the peak to peak differential voltage for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

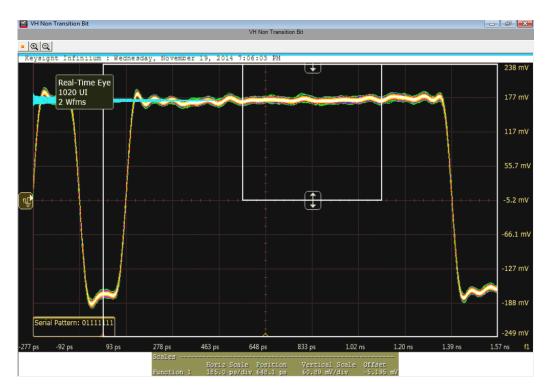

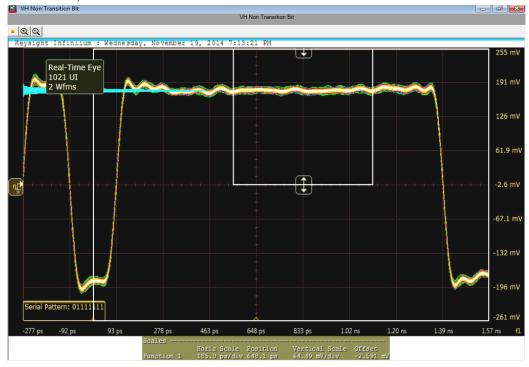

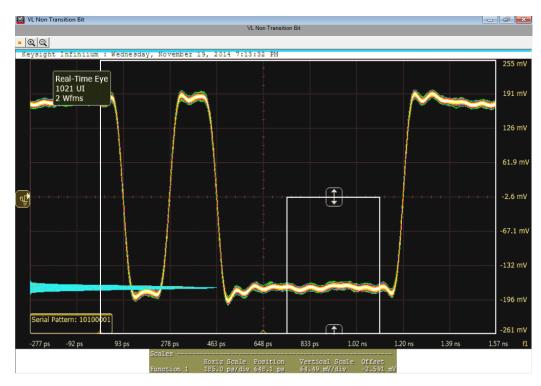

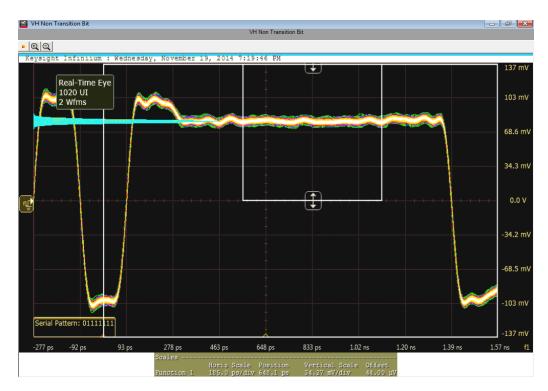

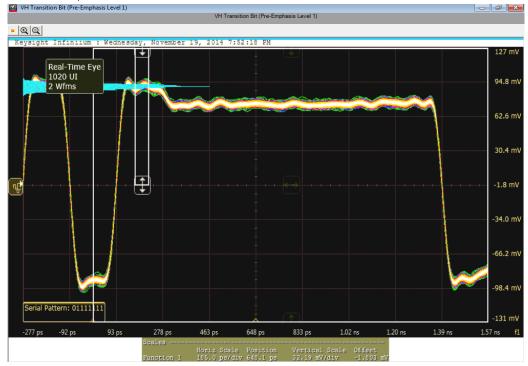

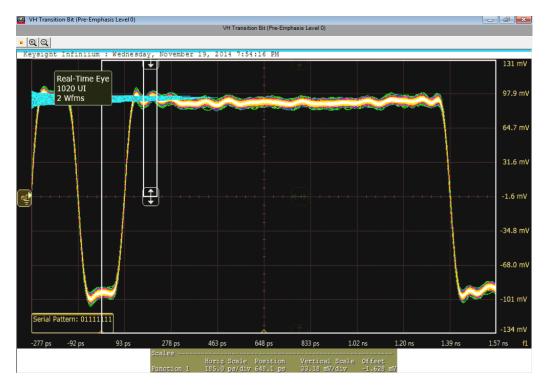

Figure 17 Reference Image for Peak to Peak Differential Voltage Test – V<sub>H</sub> Transition Bit

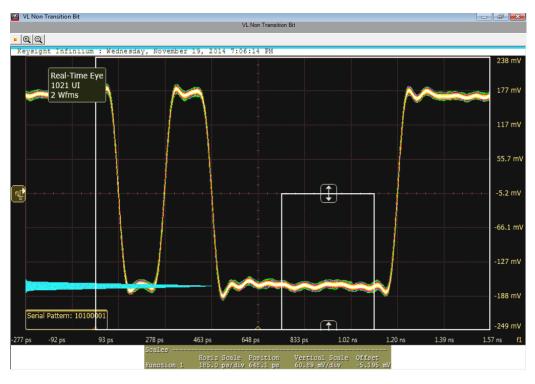

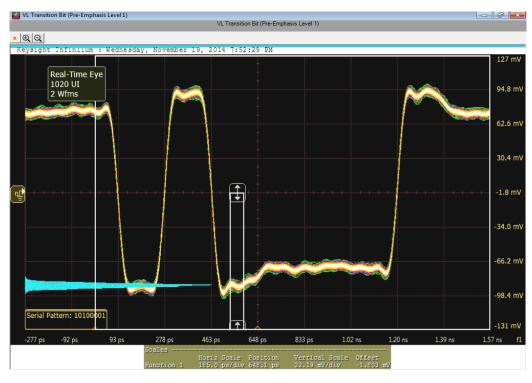

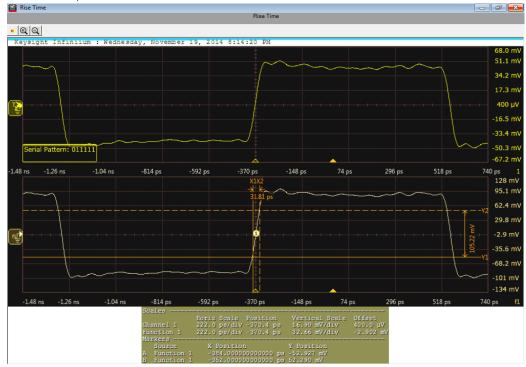

Figure 18 Reference Image for Peak to Peak Differential Voltage Test –  $V_L$  Transition Bit

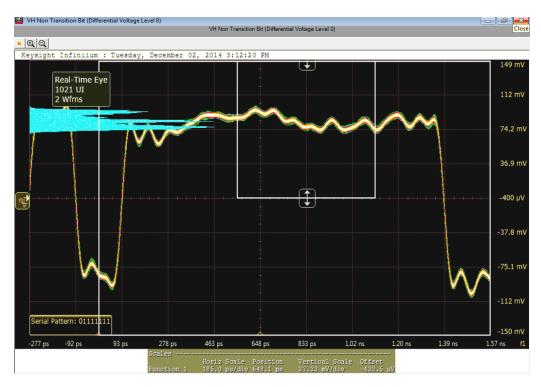

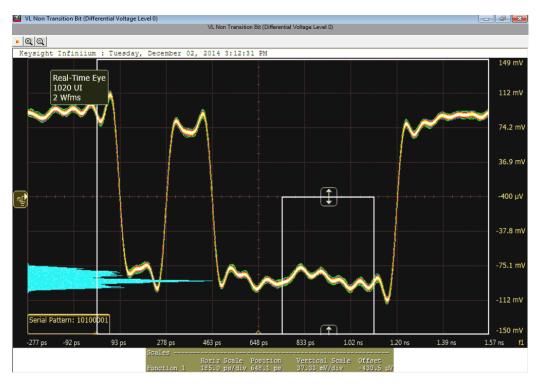

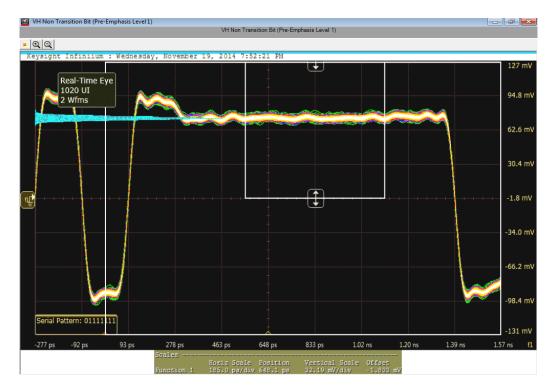

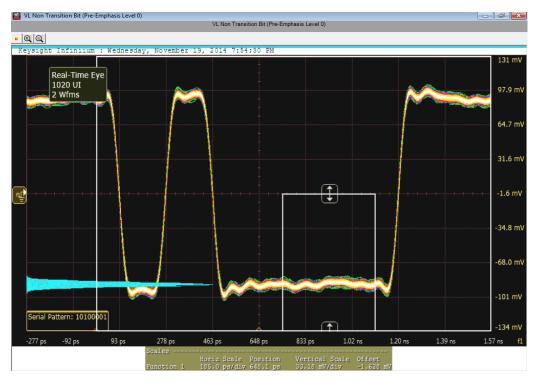

Figure 19 Reference Image for Peak to Peak Differential Voltage Test – V<sub>H</sub> Non Transition Bit

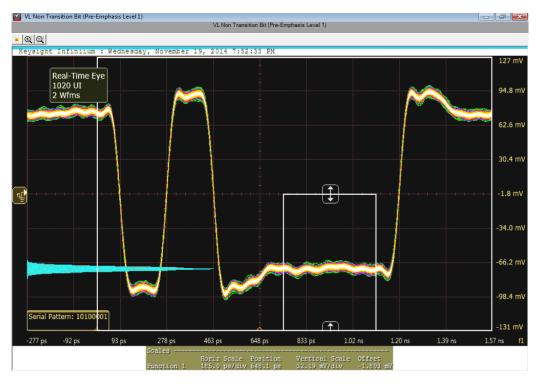

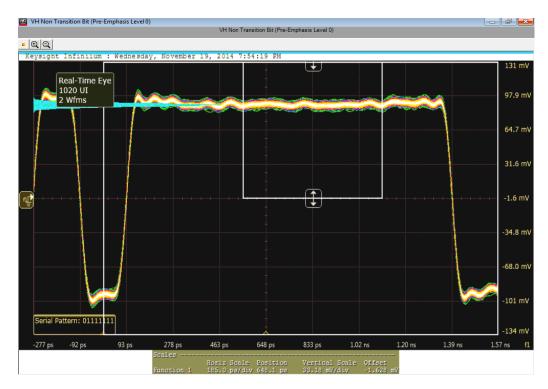

Figure 20 Reference Image for Peak to Peak Differential Voltage Test – V<sub>L</sub> Non Transition Bit

# Differential Voltage Level Test

Test Overview

The Differential Voltage Level Test evaluates the differential voltage level accompanying the data transmission.

You can define the expected output for each setting of voltage level on the source, such that the output correlates with the system budget elements such as cable loss, receiver EYE minimum/maximum values and PC board transmission line loss. Furthermore, it must be kept in mind that the link must benefit when you increase level settings.

You can measure the transition and non-transition voltage swings for each supported voltage level and pre-emphasis setting. To obtain the peak to peak voltage, you must combine the High and Low voltage measurements formed within each transition and non-transition voltage swing.

Compute the peak to peak voltages for transition and non-transition voltage swing for a given voltage level and pre-emphasis level (LvIX) using the following equations:

$$V_{T_{VX_{PP}}} = V_{T_{VX_{H}}} - V_{T_{VX_{L}}}$$

$$V_{N_{VX_{PP}}} = V_{N_{VX_{H}}} - V_{N_{VX_{L}}}$$

where  $V_{T\_LvIX\_PP}$  is the peak to peak voltage at the transition bit and  $V_{N\_LvIX\_PP}$  is the peak to peak voltage at the non-transition bit. The constituent voltages  $V_{T\_LvIX\_H}$ ,  $V_{T\_LvIX\_L}$ ,  $V_{N\_LvIX\_H}$  and  $V_{N\_LvIX\_L}$  are identified in the following figures showing generalized pre-emphasis and non pre-emphasized waveforms.

The condition for Level 0 pre-emphasis is identified separately in the following figures but is merely a special case. The measurement of high and low voltage values is an average value derived from a specific number of UI obtained over a certain number of required test patterns.

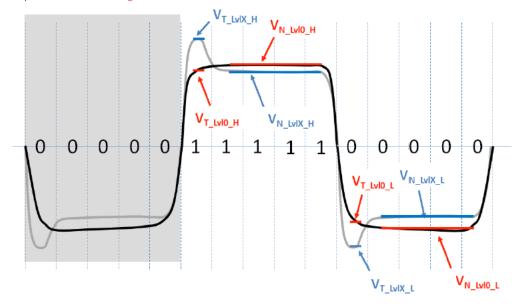

## For PLTPAT:

There are specific qualifying patterns in the 80-Bit Custom pattern (PLTPAT) for 'High' and 'Low' voltage level measurements. These measurements require a 1-1-1-1-0-0-0-0 balanced pattern and no preconditioning is required on this pattern. The transition voltage measurements,  $V_{T_LvIX_H}$  and  $V_{T_LvIX_L}$  is the average value over the 40% to 70% UI points in the transition bit. The non-transition voltage measurement,  $V_{N_LvIX_H}$  and  $V_{N_LvIX_L}$  is the average value over three UI points ending at the 50% point of the 5<sup>th</sup> bit of the five successive transmitted 1s or 0s of the patterns. Refer to Figure 21.

Figure 21 High and Low Voltage Measurement for PLTPAT

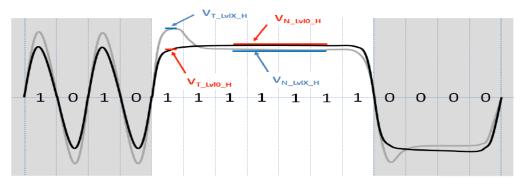

#### For PRBS7:

There are specific qualifying patterns in PRBS7 and other sequence for 'High' and 'Low' voltage level measurements. The 'High' level measurements require a 0-1-0-1-1-1-1-1-1 pattern and the 'Low' level measurements require a 1-0-1-0-0-0-1 pattern. Refer to Figure 22 and Figure 23. The first 3-bits in these patterns are a precondition to the transition measurements. The precondition bits for a transition to high level voltage measurement, are 0-1-0 and for a transition to low level voltage measurement are 1-0-1.

Figure 22 High Voltage Measurement for PRBS7

The transition voltage measurements,  $V_{T\_LvIX\_H}$  and  $V_{T\_LvIX\_L}$  are the average value over the 40% to 70% UI points in the transition bit. The non-transition voltage measurement,  $V_{N\_LvIX\_H}$  is the average value over three UI points ending at the 50% point of the 6<sup>th</sup> bit of the seven successive transmitted 1s of the patterns. The non-transition voltage measurement,  $V_{N\_LvIX\_L}$  is the average value over two UI points ending at 50% point of the 4<sup>th</sup> bit of the four successive transmitted 0s of the patterns.

Figure 23 Low Voltage Measurement for PRBS7

#### **Test Conditions**

| Specification                           | eDP Version 1.4b                                                                                      | eDP Version 1.5 |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------|

| Test Point                              | TP3                                                                                                   |                 |

| Bit Rate                                | All bit rates are supported.                                                                          |                 |

| Voltage Level and<br>Pre-emphasis Level | Any Voltage level and Pre-Emphasis level that are compliant to all normative tests run on the Source. |                 |

| Specification | eDP Version 1.4b                                                                                                   | eDP Version 1.5 |

|---------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

| SSC           | If the DUT can operate in either the SSC-enabled or the SSC-disabled state, it shall be tested in both conditions. |                 |

| Test Lane     | All test lanes must generate a test pattern to induce crosstalk.                                                   |                 |

| Test Pattern  | Any of the supported test patterns                                                                                 |                 |

### Test Procedure

- 1 Validate and acquire the signal.

- 2 Determine the threshold of the signal by measuring  $V_{Top}$  and  $V_{Base}$ .

- 3 Measure the data rate and validate the test pattern.

- 4 Acquire the qualifying test pattern over the specific number of required patterns to measure the high voltage level.

- 5 Set up the Histogram to measure the average value of high voltage level for both transition and non-transition voltage levels.

- 6 Acquire the qualifying test pattern over the specific number of required patterns to measure the low voltage level.

- 7 Set up the Histogram to measure the average value of low voltage level for both transition and non-transition voltage levels.

- 8 Compute the value of differential voltage level from the peak to peak voltage for non-transition voltage measurement using the following equation:

Differential Voltage Level  $(V_{N_{LVIX_{PP}}}) = V_{N_{LVIX_{H}}} - V_{N_{LVIX_{L}}}$

Viewing Test Results

The measured value of the differential voltage level for the test signal must fall within the conformance limit of the specifications for the CTG Test mentioned under the "References" column of Table 1.

Figure 24 Reference Image for Differential Voltage Level Test – V<sub>H</sub> Non Transition Bit

Figure 25 Reference Image for Differential Voltage Level Test –  $V_L$  Non Transition Bit

# Differential Voltage Level Ratio Test

Test Overview

The Differential Voltage Level Ratio Test evaluates the differential voltage level accompanying the data transmission and ensures that differential voltage level settings are monotonic so that the sink device relies on the source device to incrementally increase upon request by the sink.

You can define the expected output for each setting of voltage level on the source, such that the output correlates with the system budget elements such as cable loss, receiver EYE minimum/maximum values and PC board transmission line loss. Furthermore, it must be kept in mind that the link must benefit when you increase level settings.

You can measure the transition and non-transition voltage swings for each supported voltage level and pre-emphasis setting. To obtain the peak to peak voltage, you must combine the High and Low voltage measurements formed within each transition and non-transition voltage swing.

Compute the peak to peak voltages for transition and non-transition voltage swing for a given voltage level and pre-emphasis level (LvIX) using the following equations:

$$V_{T\_LVIX\_PP} = V_{T\_LVIX\_H} - V_{T\_LVIX\_L}$$

$$V_{N\_LVIX\_PP} = V_{N\_LVIX\_H} - V_{N\_LVIX\_L}$$

where  $V_{T\_LvIX\_PP}$  is the peak to peak voltage at the transition bit and  $V_{N\_LvIX\_PP}$  is the peak to peak voltage at the non-transition bit. The constituent voltages  $V_{T\_LvIX\_H}$ ,  $V_{T\_LvIX\_L}$ ,  $V_{N\_LvIX\_H}$  and  $V_{N\_LvIX\_L}$  are identified in the following figures showing generalized pre-emphasis and non pre-emphasized waveforms.

# NOTE

The condition for Level 0 pre-emphasis is identified separately in the following figures but is merely a special case. The measurement of high and low voltage values is an average value derived from a specific number of UI obtained over a certain number of required test patterns.

## For PLTPAT:

There are specific qualifying patterns in the 80-Bit Custom pattern (PLTPAT) for 'High' and 'Low' voltage level measurements. These measurements require a 1-1-1-1-0-0-0-0-0 balanced pattern and no preconditioning is required on this pattern. The transition voltage measurements,  $V_{T_LvIX_H}$  and  $V_{T_LvIX_L}$  is the average value over the 40% to 70% UI points in the transition bit. The

non-transition voltage measurement,  $V_{N\_LvIX\_H}$  and  $V_{N\_LvIX\_L}$  is the average value over three UI points ending at the 50% point of the 5<sup>th</sup> bit of the five successive transmitted 1s or 0s of the patterns. Refer to Figure 26.

Figure 26 High and Low Voltage Measurement for PLTPAT

# For PRBS7:

There are specific qualifying patterns in PRBS7 and other sequence for 'High' and 'Low' voltage level measurements. The 'High' level measurements require a 0-1-0-1-1-1-1-1-1 pattern and the 'Low' level measurements require a 1-0-1-0-0-0-1 pattern. Refer to Figure 27 and Figure 28. The first 3-bits in these patterns are a precondition to the transition measurements. The precondition bits for a transition to high level voltage measurement, are 0-1-0 and for a transition to low level voltage measurement are 1-0-1.

Figure 27 High Voltage Measurement for PRBS7

The transition voltage measurements,  $V_{T\_LvIX\_H}$  and  $V_{T\_LvIX\_L}$  are the average value over the 40% to 70% UI points in the transition bit. The non-transition voltage measurement,  $V_{N\_LvIX\_H}$  is the average value over three UI points ending at the 50% point of the 6<sup>th</sup> bit of the seven successive transmitted 1s of the patterns. The non-transition voltage measurement,  $V_{N\_LvIX\_L}$  is the average value over two UI points ending at 50% point of the 4<sup>th</sup> bit of the four successive transmitted 0s of the patterns.

Figure 28 Low Voltage Measurement for PRBS7

For each voltage level and pre-emphasis level setting that you use to run tests, use the following equation to compute Differential Voltage Level Ratio:

Differential Voltage Level Ratio = 20 \* Log<sub>10</sub>[V<sub>PP LevelA</sub> / V<sub>PP LevelB</sub>]

The following table identifies the peak to peak voltage level A and peak to peak voltage level B used in the calculation of the Differential Voltage Level Ratio.

| Measurement | Peak to Peak Voltage Level A | Peak to Peak Voltage Level B |

|-------------|------------------------------|------------------------------|

| 1           | Level 1                      | Level 0                      |

| 2           | Level 2                      | Level 1                      |

| 3           | Level 3                      | Level 2                      |

**Test Conditions**

| Specification                           | eDP Version 1.4b                                               | eDP Version 1.5                  |

|-----------------------------------------|----------------------------------------------------------------|----------------------------------|

| Test Point                              | TP3                                                            |                                  |

| Bit Rate                                | All bit rates are                                              | e supported.                     |

| Voltage Level and<br>Pre-emphasis Level | Any Voltage level and Pre-Emphasis level th<br>on the S        | •                                |

| SSC                                     | If the DUT can operate in either the SSC-ena<br>tested in both | ,                                |

| Test Lane                               | All test lanes must generate a te                              | est pattern to induce crosstalk. |

| Test Pattern                            | Any of the support                                             | ted test patterns                |

Test Procedure

- 1 Validate and acquire the signal for Level A.

- 2 Determine the threshold of the signal by measuring  $V_{Top}$  and  $V_{Base}$ .

- 3 Measure the data rate and validate the test pattern.

- 4 Acquire the qualifying test pattern over the specific number of required patterns to measure the high voltage level.

- 5 Set up the Histogram to measure the average value of high voltage level for both transition and non-transition voltage levels.

- 6 Acquire the qualifying test pattern over the specific number of required patterns to measure the low voltage level.

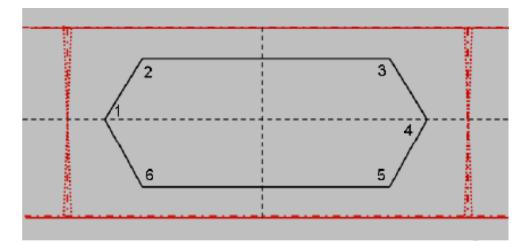

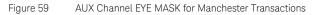

- 7 Set up the Histogram to measure the average value of low voltage level for both transition and non-transition voltage levels.