# PathWave FPGA 2022

Update 1.0

## **Notices**

## Copyright Notice

© Keysight Technologies 2018-2022

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies, Inc. as governed by United States and international copyright laws.

#### Manual Part Number

## Published By

Keysight Technologies 1400 Fountaingrove Pkwy Santa Rosa, CA 95403-1738. United States

#### Edition

Edition 3.0, February, 2023 Printed in USA

## Regulatory Compliance

This product has been designed and tested in accordance with accepted industry standards, and has been supplied in a safe condition. To review the Declaration of Conformity, go to http://www.keysight.com/go/conformity.

Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED. WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW. KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED, WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR OF ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS. THE WARRANTY TERMS IN THE SEPARATE AGREEMENT SHALL CONTROL.

KEYSIGHT TECHNOLOGIES DOES NOT WARRANT THIRD-PARTY SYSTEM-LEVEL (COMBINATION OF CHASSIS. CONTROLLERS, MODULES, ETC.) PERFORMANCE, SAFETY, OR REGULATORY COMPLIANCE, UNLESS SPECIFICALLY STATED.

## Technology Licenses

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in

the EULA represents the exclusive authority

by which the U.S. government may use, modify, distribute, or disclose the Software. The EULA and the license set forth therein. does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinquish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce, release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

## Safety Notices

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

#### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

The following safety precautions should be observed before using this product and any associated instrumentation.

This product is intended for use by qualified personnel who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read and follow all installation, operation, and maintenance information carefully before using the product.

#### WARNING

If this product is not used as specified, the protection provided by the equipment could be impaired. This product must be used in a normal condition (in which all means for protection are intact) only.

The types of product users are:

- Responsible body is the individual or group responsible for the use and maintenance of equipment, for ensuring that the equipment is operated within its specifications and operating limits, and for ensuring operators are adequately trained.

- Operators use the product for its intended function. They must be trained in

electrical safety procedures and proper

use of the instrument. They must be protected from electric shock and contact

with hazardous live circuits.

- Maintenance personnel perform routine procedures on the product to keep it operating properly (for example, setting the line voltage or replacing consumable materials). Maintenance procedures are described in the user documentation. The procedures explicitly state if the operator may perform them. Otherwise,

- they should be performed only by service personnel.

- Service personnel are trained to work on live circuits, perform safe installations, and repair products. Only properly trained service personnel may perform installation and service procedures.

#### WARNING

Operator is responsible to maintain safe operating conditions. To ensure safe operating conditions, modules should not be operated beyond the full temperature range specified in the Environmental and physical specification. Exceeding safe operating conditions can result in shorter lifespans, improper module performance and user safety issues. When the modules are in use and operation within the specified full temperature range is not maintained, module surface temperatures may exceed safe handling conditions which can cause discomfort or burns if touched. In the event of a module exceeding the full temperature range, always allow the module to cool before touching or removing modules from chassis. Keysight products are designed for use with electrical signals that are rated Measurement Category I and Measurement Category II, as described in the International **Electrotechnical Commission (IEC) Standard** IEC 60664. Most measurement, control, and data I/O signals are Measurement Category I and must not be directly connected to mains voltage or to voltage sources with high transient over-voltages. Measurement Category II connections require protection for high transient over-voltages often associated with local AC mains connections. Assume all measurement, control, and data I/O connections are for connection to Category I sources unless otherwise marked or described in the user documentation.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cable connector jacks or test fixtures. The American National Standards Institute (ANSI) states that a shock hazard exists when voltage levels greater than 30V RMS, 42.4V peak, or 60VDC are present. A good safety practice is to expect that hazardous voltage is present in any unknown circuit before measuring.

Operators of this product must be protected from electric shock at all times. The responsible body must ensure that operators are prevented access and/or insulated from every connection point. In some cases, connections must be exposed to potential human contact. Product operators in these circumstances must be trained to protect themselves from the risk of electric shock. If the circuit is capable of operating at or above 1000V, no conductive part of the circuit may be exposed.

Do not connect switching cards directly to unlimited power circuits. They are intended to be used with impedance-limited sources. NEVER connect switching cards directly to AC mains. When connecting sources to switching cards, install protective devices to limit fault current and voltage to the card.

Before operating an instrument, ensure that the line cord is connected to a properly-grounded power receptacle. Inspect the connecting cables, test leads, and jumpers for possible wear, cracks, or breaks before each use.

When installing equipment where access to the main power cord is restricted, such as rack mounting, a separate main input power disconnect device must be provided in close proximity to the equipment and within easy reach of the operator.

For maximum safety, do not touch the product, test cables, or any other

instruments while power is applied to the circuit under test. ALWAYS remove power from the entire test system and discharge any capacitors before: connecting or disconnecting cables or jumpers, installing or removing switching cards, or making internal changes, such as installing or removing jumpers.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always make measurements with dry hands while standing on a dry, insulated surface capable of withstanding the voltage being measured.

The instrument and accessories must be used in accordance with its specifications and operating instructions, or the safety of the equipment may be impaired.

Do not exceed the maximum signal levels of the instruments and accessories, as defined in the specifications and operating information, and as shown on the instrument or test fixture panels, or switching card.

When fuses are used in a product, replace with the same type and rating for continued protection against fire hazard.

Chassis connections must only be used as shield connections for measuring circuits, NOT as safety earth ground connections.

If you are using a test fixture, keep the lid closed while power is applied to the device under test. Safe operation requires the use of a lid interlock.

Instrumentation and accessories shall not be connected to humans.

Before performing any maintenance, disconnect the line cord and all test cables.

To maintain protection from electric shock and fire, replacement components in mains circuits – including the power transformer,

test leads, and input jacks – must be purchased from Keysight. Standard fuses with applicable national safety approvals may be used if the rating and type are the same.

Other components that are not safety-related may be purchased from other suppliers as long as they are equivalent to the original component (note that selected parts should be purchased only through Keysight to maintain accuracy and functionality of the product). If you are unsure about the applicability of a replacement component, call an Keysight office for information.

#### WARNING

No operator serviceable parts inside. Refer servicing to qualified personnel. To prevent electrical shock do not remove covers. For continued protection against fire hazard, replace fuse with same type and rating.

#### PRODUCT MARKINGS:

The CE mark is a registered trademark of the European Community.

Australian Communication and Media

Authority mark to indicate regulatory compliance as a registered supplier.

#### ICES/NMB-001 ISM GRP.1 CLASS A

This symbol indicates product compliance with the Canadian Interference-Causing Equipment Standard (ICES-001). It also identifies the product is an Industrial Scientific and Medical Group 1 Class A product (CISPR 11, Clause 4).

South Korean Class A EMC Declaration. This equipment is Class A suitable for professional use and is for use in electromagnetic environments outside of the home. A 급 기기 (업무용 방송통신기자재)이 기기는 업무용 (A 급 ) 전자파적합기기로서 판 매자 또는 사용자는 이 점을 주 의하시기 바라 며, 가정외의 지역에서 사용하는 것을 목적으로 합니다.

This product complies with the WEEE Directive marketing requirement. The affixed product label (above) indicates that you must not discard this electrical/electronic

product in domestic household waste.

Product Category: With reference to the equipment types in the WEEE directive

Annex 1, this product is classified as "Monitoring and Control instrumentation" product. Do not dispose in domestic household waste. To return unwanted products, contact your local Keysight office, or for more information see http://-

about.key-

sight.-

com/en/companyinfo/environment/takeback.shtml.

This symbol indicates the instrument is sensitive to electrostatic discharge (ESD). ESD can damage the highly sensitive components in your instrument. ESD damage is most likely to occur as the module is being installed or when cables are connected or disconnected. Protect the circuits from ESD damage by wearing a grounding strap that provides a high resistance path to ground. Alternatively, ground yourself to discharge any built-up static charge by touching the outer shell of any grounded instrument chassis before touching the port connectors.

This symbol on an instrument means caution, risk of danger. You should refer to the operating instructions located in the user documentation in all cases where the symbol is marked on the instrument.

This symbol indicates the time period during which no hazardous or toxic substance elements are expected to leak or deteriorate during normal use. Forty years is the expected useful life of the product.

# Contents

| Getting Started                            | 11  |

|--------------------------------------------|-----|

| System Requirements                        | 12  |

| Installation                               | 14  |

| Licensing                                  | 16  |

| User Guide                                 | 18  |

| Overview                                   | 19  |

| GUI Overview                               | 23  |

| Keyboard and Mouse Shortcuts               | 25  |

| Basic Controls                             | 25  |

| Adding Blocks                              | 27  |

| Connecting Ports and Interfaces            | 29  |

| Connection Rules                           | 35  |

| Adding and Editing Comments                | 37  |

| Configuring PathWave FPGA                  | 40  |

| Designing your FPGA Logic                  | 42  |

| Creating a New Sandbox Project             | 42  |

| Creating a New Submodule Project           | 46  |

| Project Settings Dialog                    | 46  |

| Design Interfaces                          | 48  |

| Keysight Standard Interfaces               | 50  |

| Adding a Memory Map                        | 59  |

| Adding a Register Bank                     | 60  |

| Configuring Submodule Interfaces           | 64  |

| Deciding the Address Width of an Interface | 67  |

| Registering Sandbox Interfaces             | 72  |

| Symbol Names                               | 73  |

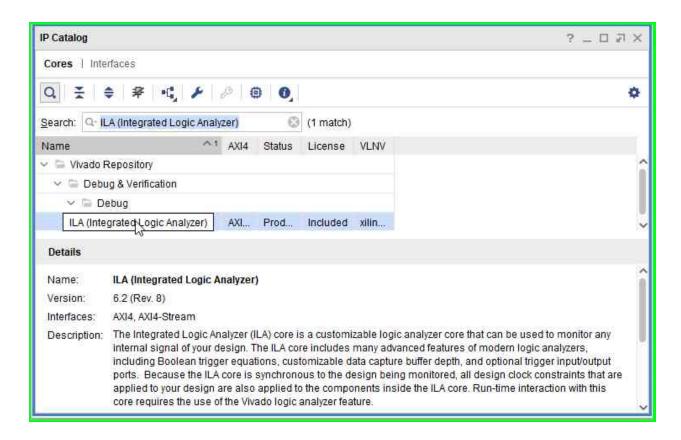

| IP Catalog                                 | 75  |

| PathWave FPGA IP Repository                | 80  |

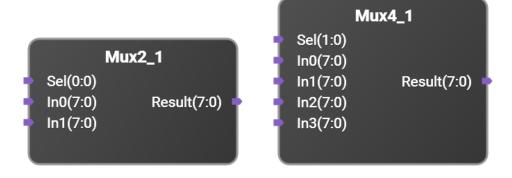

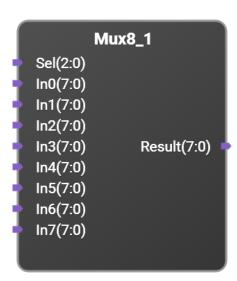

| Basic IP Blocks                            | 80  |

| Connector Blocks                           | 110 |

| Math Blocks                                | 115 |

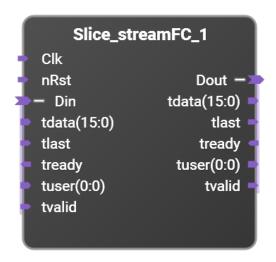

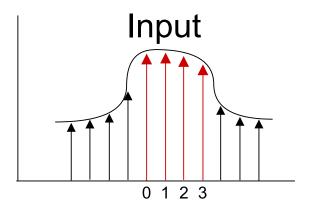

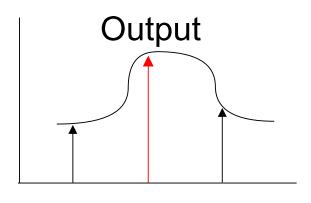

| DSP Blocks                                 | 132 |

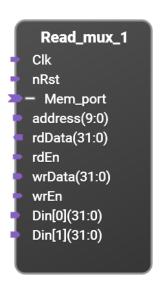

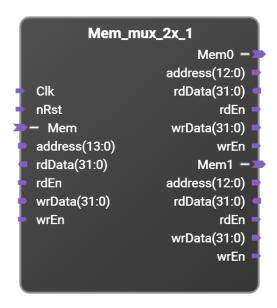

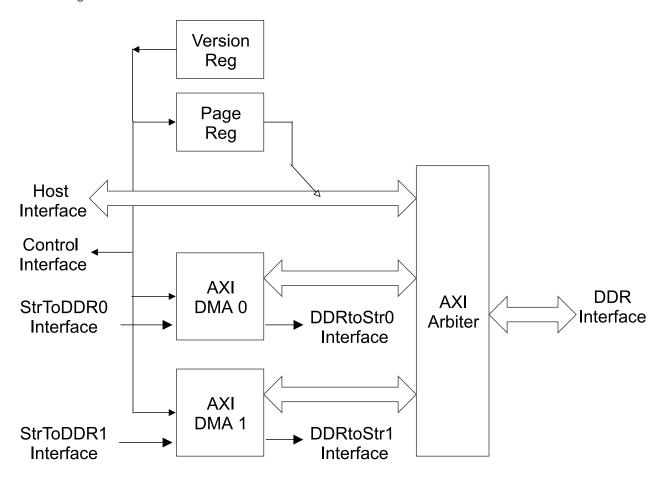

| Memory Blocks                              | 159 |

| DSP Library IP Blocks                      | 168 |

| IP Repositories                            | 214 |

| Imported User IP                           | 215 |

| Vivado XCI (Xilinx Core Instance)          | 220 |

| PathWave FPGA Submodule                    | 223 |

| Naming Conventions                                    | 224 |

|-------------------------------------------------------|-----|

| Name Collisions                                       | 225 |

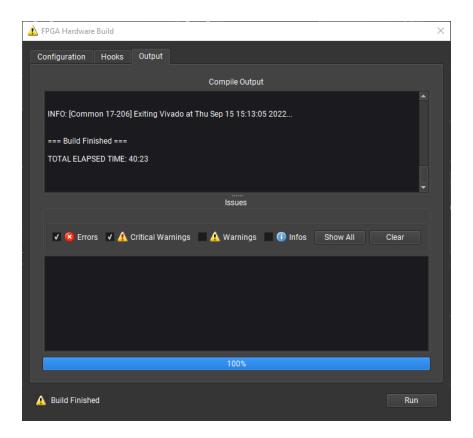

| Building your FPGA Logic                              |     |

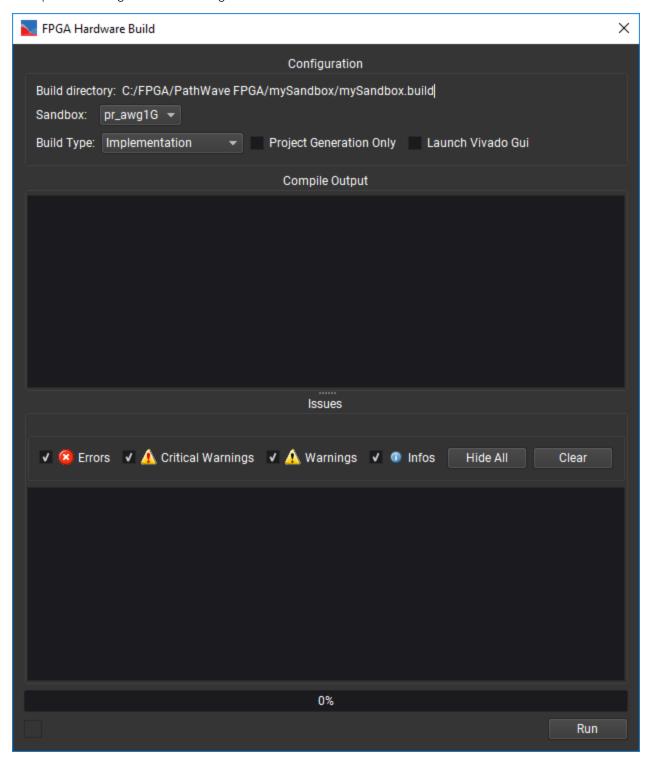

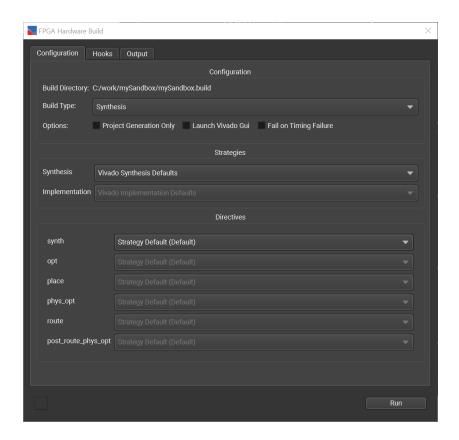

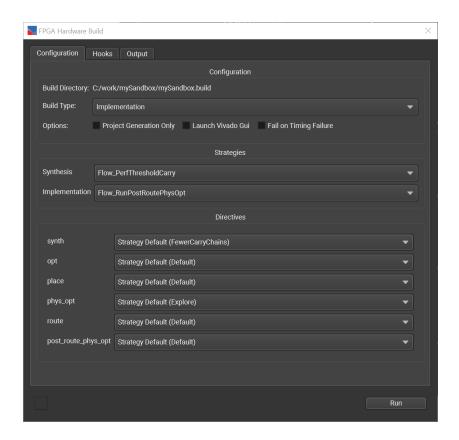

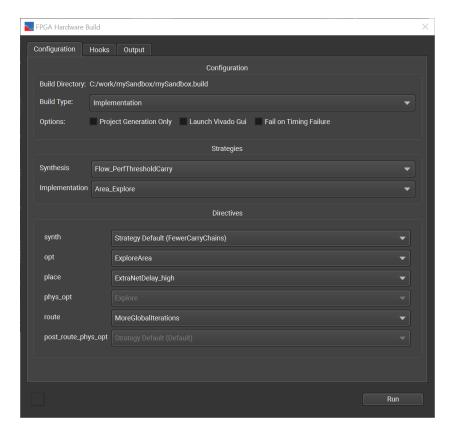

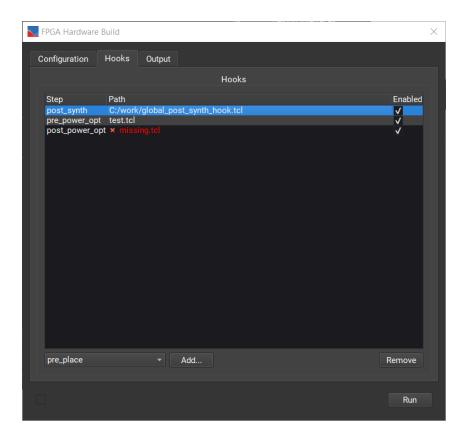

| Generating the Bit File                               | 227 |

| Simulating your FPGA Logic                            | 237 |

| Simulation Testbench Design                           | 237 |

| Test Bench Address Mapping                            | 253 |

| Advanced Features                                     | 258 |

| Command Line Arguments                                | 258 |

| Migrating a design to a new BSP                       | 260 |

| Changing a Submodule Project Target Hardware          | 261 |

| Debugging in Hardware                                 | 261 |

| User Constraint Files                                 | 271 |

| Glossary                                              | 273 |

| IP Developers Guide                                   | 275 |

| Overview: IP Developers Guide                         | 276 |

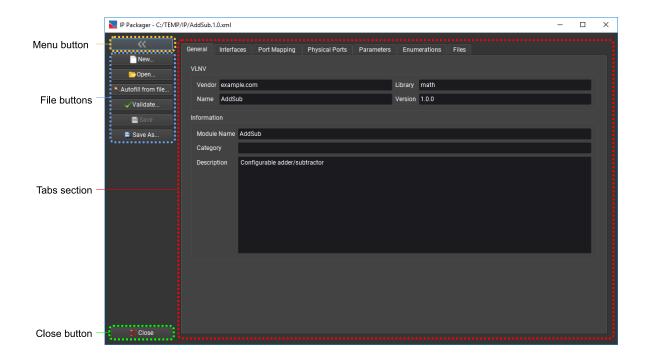

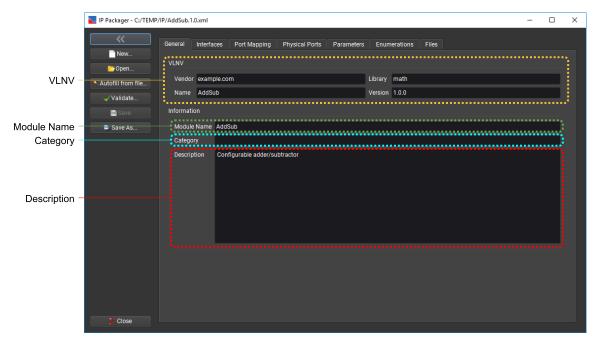

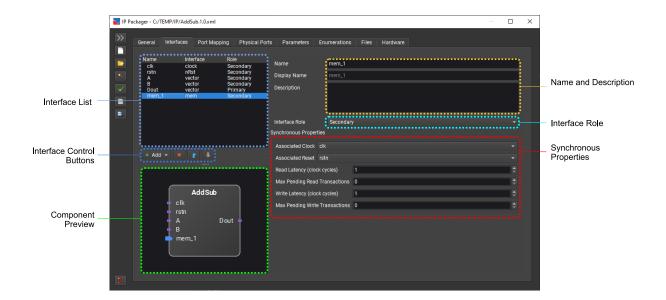

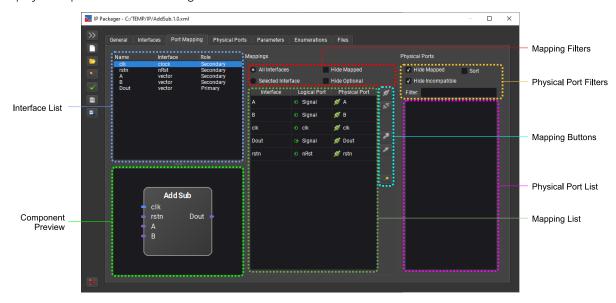

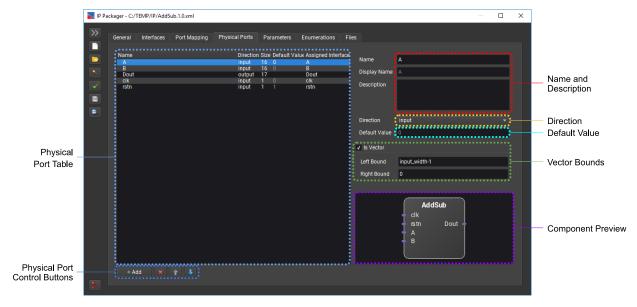

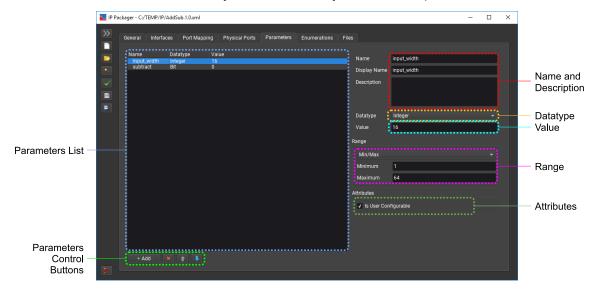

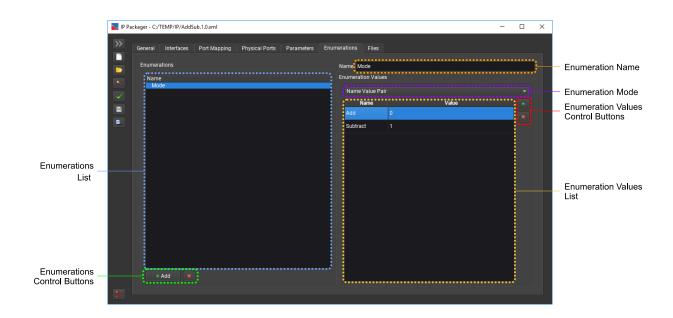

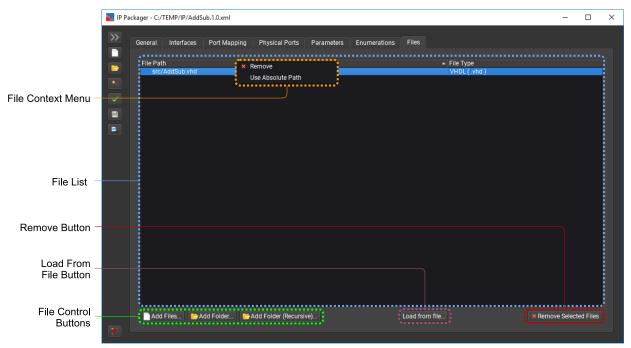

| IP Packager                                           | 277 |

| Additional Interface Properties                       | 292 |

| IP Repository Manifest                                | 296 |

| Tutorials                                             | 297 |

| IP Packager Tutorial                                  | 298 |

| Simple HDL done manually                              | 299 |

| Simple HDL done automatically                         | 325 |

| Parameterized HDL                                     | 336 |

| Advanced IP Packaging                                 | 354 |

| HVI Example                                           | 380 |

| Import Vivado High-Level Synthesis (HLS) generated IP | 386 |

| Power of Two Decimation Tutorial                      | 395 |

| Xilinx System Generator for DSP™ Tutorial             | 404 |

| Appendix                                              | 417 |

| Infer Interface Reference                             | 418 |

| Importing IP with Invalid IP-XACT                     | 424 |

| VHDL Support                                          | 425 |

| Verilog Support                                       | 427 |

| Legal                                                 | 429 |

| 3rd Party Licenses                                    | 430 |

| Apache License v2.0                                   | 436 |

| GNU GPLv3                                             | 440 |

| GNU LGPLv3                                            | 452 |

# **Getting Started**

# Contents

- System Requirements

- Installation

- Licensing

Getting Started System Requirements

# System Requirements

You must ensure that your system meets the following requirements before installing PathWave FPGA.

- Administrator privileges

- Operating system that has the most recent updates and Service Packs

- License File (or Authorization Codes, or token if evaluating) or internet access

## **Recommended Hardware Configurations**

| Category                  | Practical Minimums | Recommended                |

|---------------------------|--------------------|----------------------------|

| Operating System          | Windows 10, 64-bit | Windows 10, 64-bit         |

| Hard disk                 | 10 GB free space   | 100 GB free space          |

| RAM                       | 4 GB RAM           | 16 GB RAM and above        |

| Display                   | 1280 x 720         | 1920 x 1200                |

| Software Security         | USB hardware key   | Wired LAN, or Wireless LAN |

| Test Instrument Interface | Not required       | LAN                        |

| Touch User<br>Interface   | N/A                | Not supported              |

## Software Compatibility with PathWave FPGA

The following table summarizes PathWave FPGA compatibility with various versions of other software applications. However, for the latest vendor information, licensing, and downloads, please contact each vendor directly.

| Vendor    | Software / Feature                                                    | Release<br>Officially<br>Supported | May work, but not supported                                               | Release<br>Explicitly not-<br>supported |

|-----------|-----------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|-----------------------------------------|

| Xilinx    | Vivado, debugging, compilation of bit images.                         | Vivado<br>2017.3                   |                                                                           | prior to Vivado<br>2017.3               |

| CMake     | CMake to support to enable FPGA bit file verification                 | 3.9 or later                       |                                                                           | prior to 3.9                            |

| Kactus2   | We recommend using the PathWave FPGA IP Packager instead of Kactus 2. | 3.6 or later                       | 3.5 (note, there is a workaround documented when using parameterized HDL) | 3.4                                     |

| Microsoft | Visual Studio C++ to enable FPGA bit file verification                | 2017                               | Other versions                                                            |                                         |

Getting Started System Requirements

## **Summary of HDL Language Support**

| Standard | Release Officially Supported       | May work, but not supported | Release Explicitly not-<br>supported |

|----------|------------------------------------|-----------------------------|--------------------------------------|

| IP-XACT  | IEEE 1685-2014, IEEE 1685-<br>2009 |                             |                                      |

| Verilog  | IEEE 1364-2005                     |                             |                                      |

| VHDL     | IEEE 1076-2002 (VHDL 2002)         |                             | IEEE 1076-2008 (VHDL 2008)           |

NOTE

Newer versions of Xilinx Vivado might be required for Keysight Instruments (BSPs). Consult the instrument product manual for specific requirements.

Getting Started Installation

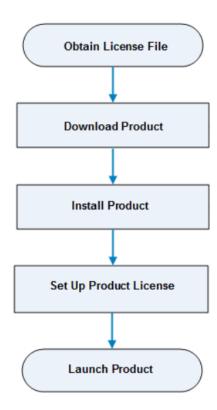

## Installation

PathWave FPGA can be installed on a computer running Windows by downloading the PathWave FPGA install file from http://www.keysight.com/find/pathwave-fpga. For the system requirement details, refer to System Requirements.

#### Obtain PathWave FPGA License File

PathWave FPGA requires a license to run. You can either apply for an Evaluation or a Purchased license. Once the license request is approved, a license file (with .lic extension) is sent as an email attachment. Save this file on your computer, it will be used when you run the Keysight PathWave License Manager.

#### Download PathWave FPGA Installer

Click https://www.keysight.com/find/pathwave-fpga to download the installer.

#### Install PathWave FPGA

To install PathWave FPGA, you must have system administrator privileges. Run the downloaded installer and follow the guided tour to complete the installation. If you want to do a silent install, run

Getting Started Installation

the installer executable from the command line as **Administrator** and use the "--mode unattended" command line option.

## Setup PathWave FPGA License

At the end of installation, the License Setup Wizard starts automatically after detecting that you do not have a valid license to start PathWave FPGA. If you choose to skip the license setup, you can complete the process later by clicking Start > Programs > Keysight PathWave License Manager > Keysight PathWave License Manager.

#### Node-locked License

To setup a counted license, select the **Add a License File** option and follow the guided tour to complete the license setup process. In case of a USB dongle, attach the dongle to the USB port and invoke the **PathWave License Manager** to complete the setup process.

#### Floating License

To setup a floating license, select the **Specify a Remote License Server** option and follow the guided tour to complete the license setup process. Consult your license administrator for the network path of the license server.

#### Launch PathWave FPGA

To run PathWave FPGA, go to the **Start** menu and choose **Programs > Keysight PathWave FPGA** <*release\_number> > Keysight PathWave FPGA <release\_number> >*.

Getting Started Licensing

## Licensing

This chapter explains in more detail how to install PathWave FPGA licenses. It contains the following sections:

- About PathWave FPGA Licenses

- The Licensing Process

- Troubleshooting

#### About PathWave FPGA Licenses

PathWave FPGA requires one license per desktop client. PathWave FPGA releases 2021 and newer require a different license than PathWave FPGA 2020 Update 1.1, or older.

NOTE

Option -FP1 was previously required to be purchased for an instrument to be used with PathWave FPGA. Option -FP1 is now deprecated, but existing instruments that used the -FP1 option, such as Keysight M3xxxA PXI Instruments, are still supported.

#### Supported licensing modes

The following types of licenses are supported:

#### Commercial licenses:

- Node-Locked, perpetual and 6, 12, 24, and 36 months, subscription.

- USB Portable, perpetual and 6, 12, 24, and 36 months, subscription.

- Floating/Networking, perpetual and 6, 12, 24, and 36 months, subscription.

- Transportable, perpetual and 6, 12, 24, and 36 months, subscription.

#### Trial licenses:

• 30 days Node-locked.

#### The Licensing Process

The Keysight licensing process uses the following steps:

#### 1. Purchase and fulfillment

For most Keysight licensed product options, your entitlement certificate is sent to you as a PDF attachment via email immediately after your purchase. In some cases, you receive a paper copy of your certificate with your purchased product. The licensed product options may be software products or upgraded features of an instrument.

## 2. Getting a license

Getting Started Licensing

Using the entitlement certificate you received when you ordered, you can request your licenses on the Keysight Software Manager web site. To do this, you'll need to choose a host instrument or PC, and provide its identifying information (the Host ID) when you request your licenses. Once you begin the process, Keysight Software Manager will guide you step by step through requesting your licenses and you will receive the license files via email.

You might need to create a *myKeysight* login when you first go to the Keysight Software Manager site, and you will need to log in anytime you go to the site.

## 3. Installing your license

To enable the licensed software, after you receive a license file from Keysight Software Manager, you must install it on your instrument or computer or on a central licensing server accessible from your instrument or computer.

To install the license:

- 1. Install PathWave FPGA.

- 2. Use Keysight PathWave License Manager to install your license. PathWave License Manager is installed with PathWave FPGA, if not already installed. The installation process is described in the email that comes with your license. Previous versions of PathWave FPGA used a different Keysight license manager. Keysight recommends that you do not uninstall any previous Keysight license manager so that your previous Keysight products continue to function. After installing a PathWave FPGA license, it will appear in the PathWave License Manager status tab, with a Feature name of KF9000B.

Detailed documentation for administrators is available at <a href="http://www.keysight.com/find/licensingdoc">http://www.keysight.com/find/licensingdoc</a>.

## **Troubleshooting**

By default, PathWave License Manager 2.3 saves its log files in C:\ProgramData\Keysight\Licensing\Log

# User Guide

## Contents

- Overview

- GUI Overview

- Configuring PathWave FPGA

- Designing your FPGA Logic

- Building your FPGA Logic

- Simulating your FPGA Logic

- Advanced Features

- Glossary

## Overview

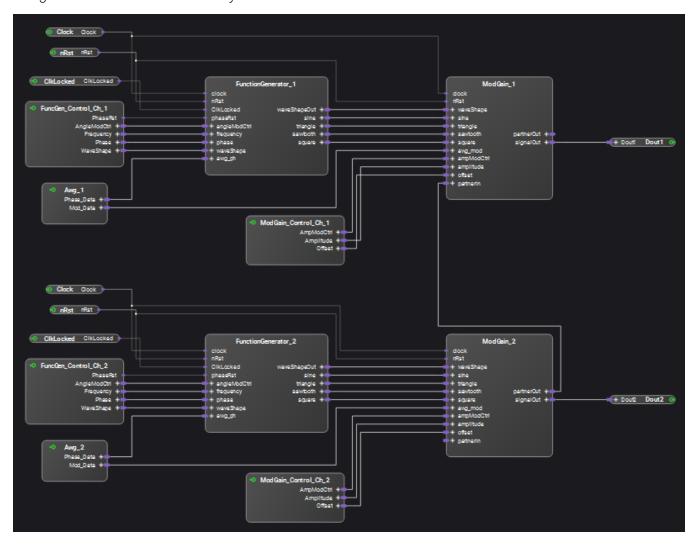

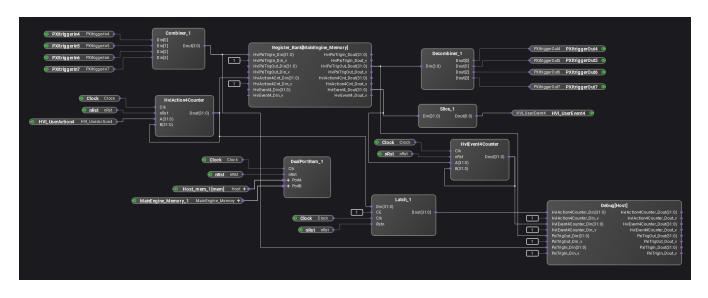

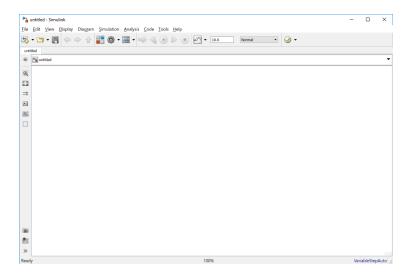

PathWave FPGA is Keysight's "Open FPGA" development environment. PathWave FPGA provides a complete FPGA design flow from design creation to gateware deployment to HW/gateware verification.

PathWave FPGA includes a graphical environment that provides a way to rapidly develop FPGA designs on Keysight Open FPGA hardware. An IP library is provided which includes Logic/Math, Memory, and DSP blocks that can be included in an FPGA design. Vivado IP blocks or custom HDL IP can also be imported and the port interfaces described using IP-XACT 2014. PathWave FPGA provides a design flow from schematic to bitfile generation with the press of a button.

To get started, follow the PathWave FPGA design flow:

- 1. Start PathWave FPGA

- 2. Create a new project with the PathWave FPGA New Project Wizard

3. Modify the default FPGA template design by importing Vivado IP, HDL IP, or by using the PathWave FPGA IP library.

4. Compile the design into a bit image

5. Deploy your design using the instrument driver

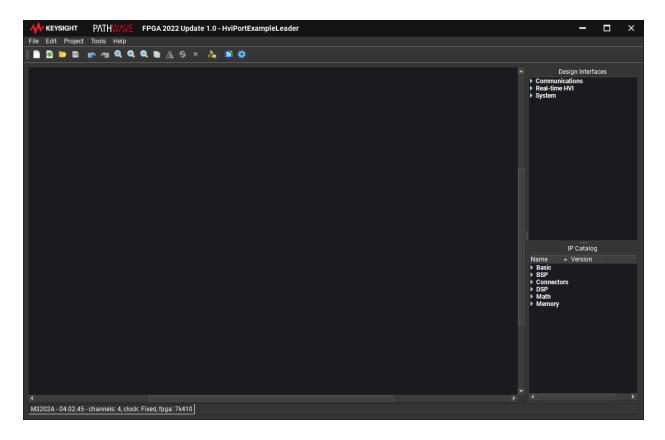

# **GUI** Overview

| Menu/Icon/Pane | Description                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File           | Includes options to create a new project, open an existing project, save a project, close a project, and exit.                                                      |

|                | WARNING When doing a <b>Save As</b> of an existing project, only the project file and files in the <b>.data</b> directory will be copied to the new project folder. |

| Edit           | Includes actions to manipulate the design canvas such as undo, redo, select all, and copy.                                                                          |

| Project        | Includes an option to generate FPGA firmware and to import external blocks.                                                                                         |

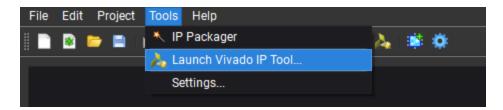

| Tools          | Includes the IP Packager, Vivado IP tool and configure settings.                                                                                                    |

| Help           | Includes link to product documentation, license, and product related information.                                                                                   |

|                | Create a new sandbox project.                                                                                                                                       |

| *              | Create a new submodule project.                                                                                                                                     |

|                | Open an existing project.                                                                                                                                           |

|                | Save the project.                                                                                                                                                   |

|                | Undo the last operation.                                                                                                                                            |

| <b>5</b>       | Redo the last operation that was undone.                                                                                                                            |

|                | Fit schematic in window.                                                                                                                                            |

| •              | Zoom in.                                                                                                                                                            |

| Q              | Zoom out.                                                                                                                                                           |

|                | Сору.                                                                                                                                                               |

|                | Flip.                                                                                                                                                               |

| <b>3</b>       | Redraw connections.                                                                                                                                                 |

| ×              | Remove.                                                                                                                                                             |

| <b>1</b>       | Launch the Vivado IP tool.                                                                                                                                          |

|                | Add external block.                                                                                                                                                 |

|                      | Generate the firmware for the project.                                                                                                                                       |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design<br>Interfaces | Design Interfaces are responsible for communication between the internally configurable FPGA part (the FPGA customizable space, which a user can edit) and the rest of FPGA. |

| IIILEITACES          | FPGA part (the FPGA customizable space, which a user carredit) and the rest of FPGA.                                                                                         |

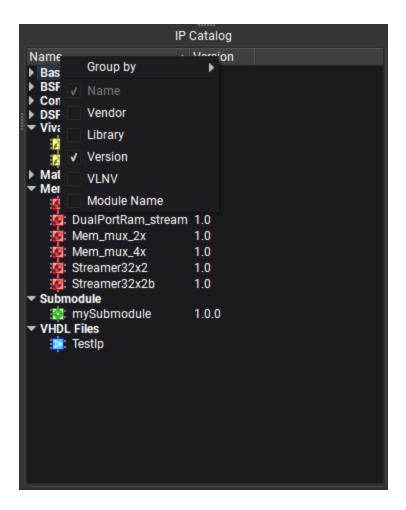

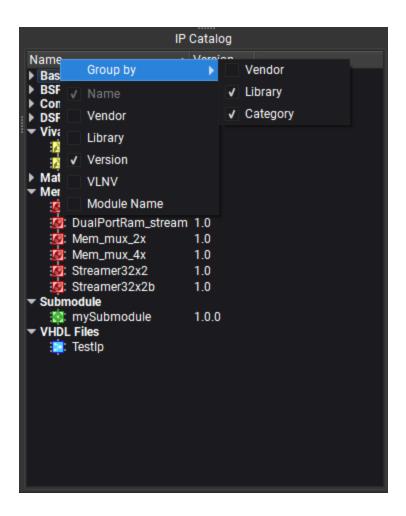

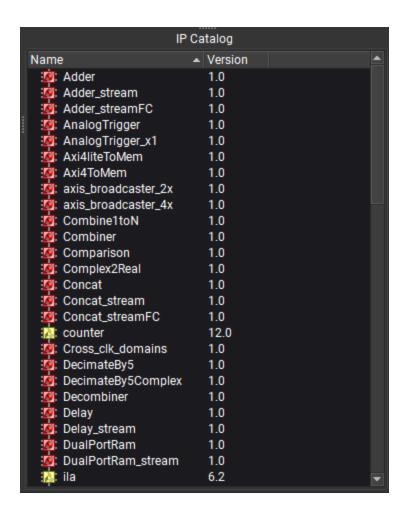

| IP Catalog           | IP Catalog contains the building blocks, built-in or custom, for the design canvas.                                                                                          |

## See Also

- Keyboard and Mouse Shortcuts

- Basic Controls

- Adding Blocks

- Connecting Ports and Interfaces

- Adding and Editing Comments

# **Keyboard and Mouse Shortcuts**

This topic lists the operations that can be performed using keyboard and mouse shortcuts.

| Function                       | Key Code              |

|--------------------------------|-----------------------|

| Add/remove item from selection | Ctrl + Left click     |

| Select all connected nets      | Double click on a net |

| Abort current action           | Esc                   |

| Remove selected items          | Delete                |

| Redraw connections             | Ctrl + R              |

| Zoom fit                       | Ctrl + F              |

| Copy selection                 | Ctrl + C              |

| Select all                     | Ctrl + A              |

| Undo                           | Ctrl + Z              |

| Redo                           | Ctrl + Y              |

| New project                    | Ctrl + N              |

| Open project                   | Ctrl + O              |

| Save project                   | Ctrl + S              |

| Close project                  | Ctrl + F4             |

| Exit                           | Alt + F4              |

## **Basic Controls**

#### Adjusting the View

| Operation | Keyboard | Mouse                      |

|-----------|----------|----------------------------|

| Zoom      | Ctrl++   | Ctrl - Mauga whool up      |

| In        | CIII++   | Ctrl + Mouse wheel up      |

| Zoom      | Ctrl+-   | Ctrl + Mouse wheel down    |

| Out       | CIII+-   | Ctrt + Mouse wheet down    |

| Zoom      | Ctrl+F   |                            |

| Fit       | GHI+F    |                            |

| Pan       |          | Alt + Mouse click and drag |

#### Manipulating Items

To move an item, left-click on the item and drag it to a different location. Connections are routed automatically and can't be moved manually.

To select an item, left-click on the item. To select multiple items, left-click on an empty space and drag to select all items in a rectangle. To add or remove individual items from the selection, hold the **Ctrl** key and left-click an item. To select all items, press **Ctrl+A** or choose **Select All** from the **Edit** menu.

To copy a block or a selection, right-click the block or an item in the selection and choose Copy, then left-click to place the copy in the design. You can also press **Ctrl+C**, choose **Copy** from the **Edit** menu,

or click the Copy button on the toolbar.

#### Undo and Redo

To **Undo** an action, press **Ctrl+Z**, or choose **Undo** from the **Edit** menu, or click the **Undo** button on the toolbar.

To **Redo** an action, press **Ctrl+Y**, or choose **Redo** from the **Edit** menu, or click the **Redo** button on the toolbar.

Undo is disabled after certain actions:

- Adding or removing external blocks from the IP panes. Adding or removing instances does not disable Undo.

- Adding or removing Vivado IP from the IP panes. Adding or removing instances does not disable Undo.

- Creating or removing a submodule project from the Submodules pane. Adding or removing instances does not disable Undo.

- · Reloading a block

- · Changing a blocks file

## **Adding Blocks**

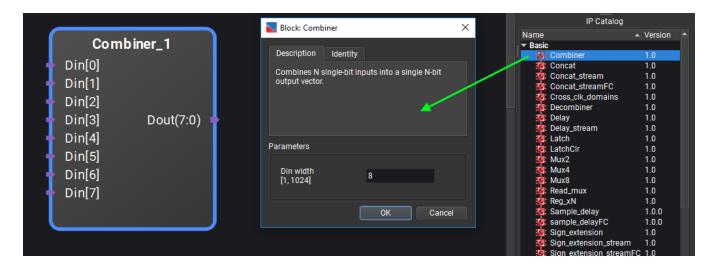

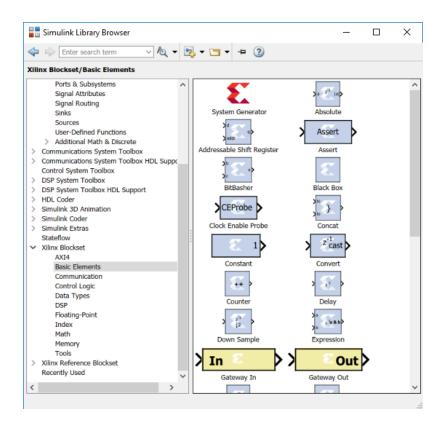

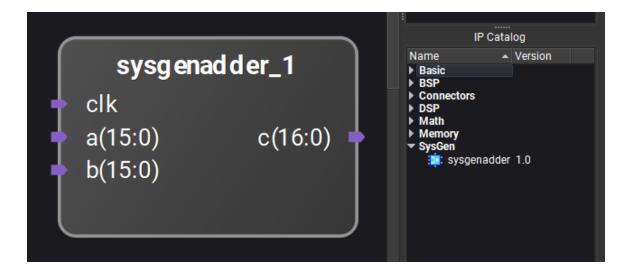

A hardware project is created by combining blocks from the IP Catalog on the right side of the user interface. The blocks can be selected, dragged into the project, configured, and connected to other blocks in the project.

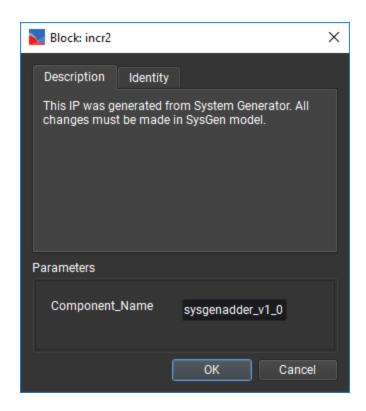

To add a block, either double-click the entry or drag it onto the Design Canvas. In the properties dialog, you can review the description and change the values of parameters.

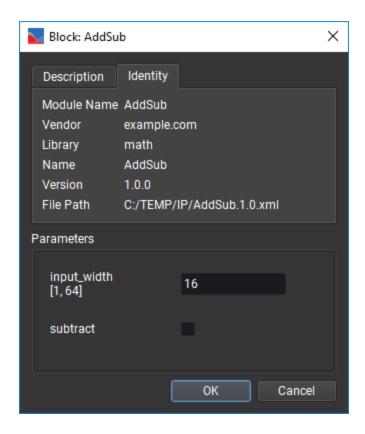

The Identity tab shows the identifying information about the IP.

- Module/Entity Name is the name of the Verilog module or VHDL entity that contains the IP.

- Vendor, Library, Name, and Version are the unique identifier for the IP-XACT file. If the IP was imported directly from VHDL or Verilog, these fields are not shown.

- File Path is the location on disk of the IP-XACT or HDL file. This is not shown for IP that comes with PathWave FPGA.

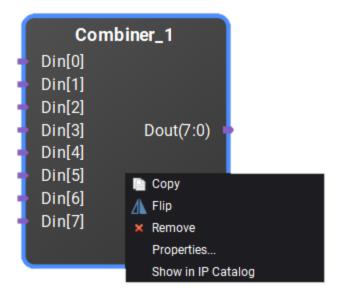

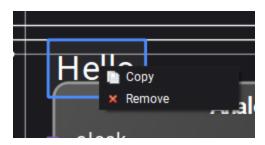

Right-click a block on the Design Canvas to open the context menu.

- Copy creates a duplicate of the selected block.

- Flip swaps the ports, so that inputs are on the right and outputs are on the left.

- Remove deletes the block from the project.

- Properties... opens the configuration dialog box shown above.

- Show in IP Catalog selects the IP for this block in the IP Catalog.

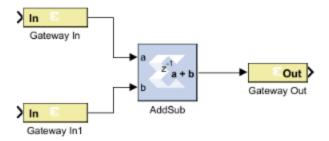

## **Connecting Ports and Interfaces**

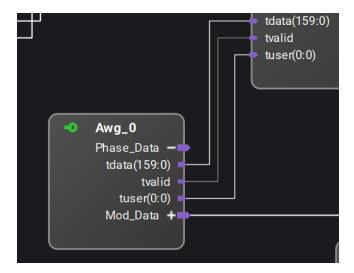

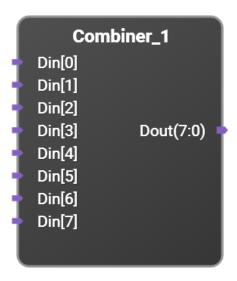

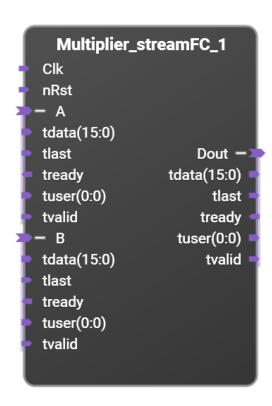

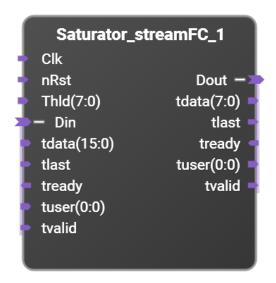

Blocks can be connected together by their ports and interfaces. An interface is defined to be a set of ports.

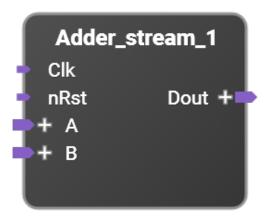

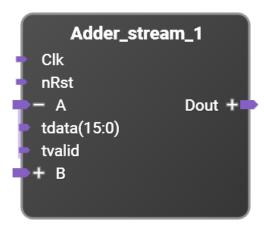

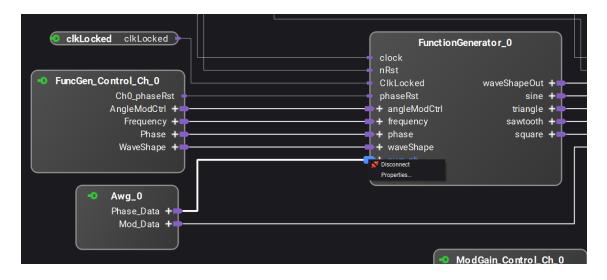

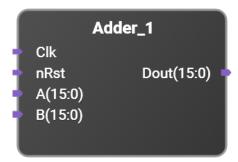

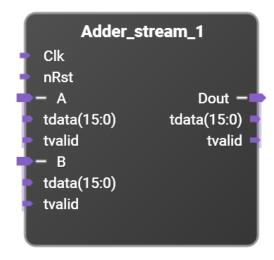

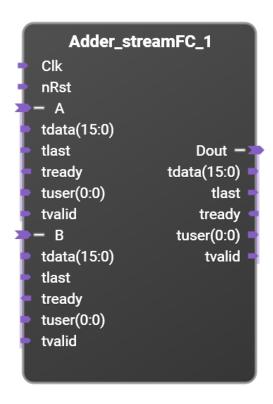

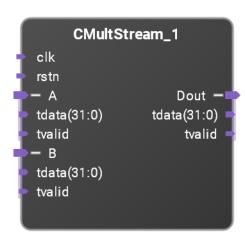

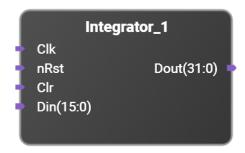

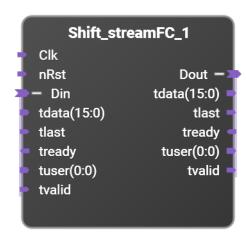

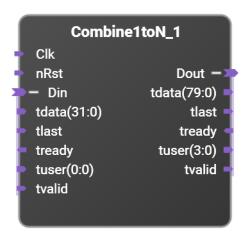

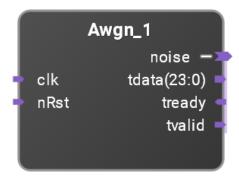

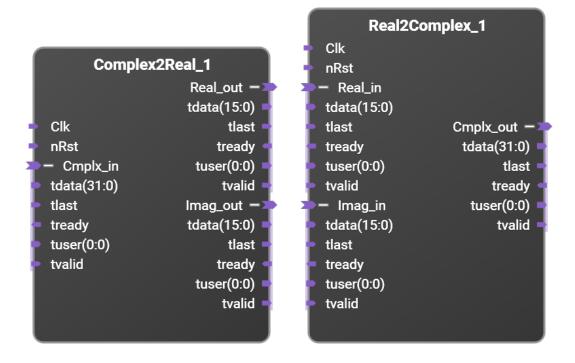

In the example above, this block has inputs to the left (input connectors point into the block), and outputs to the right side of the block (output connectors point out of the block).

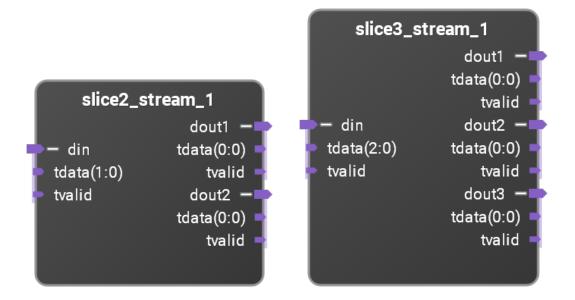

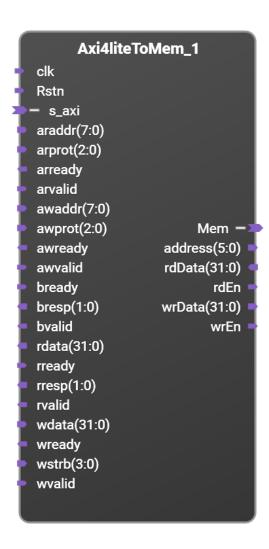

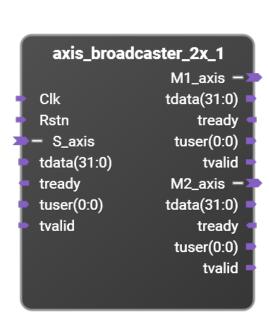

This block has two ports (small connectors), and the other connectors are interfaces (larger connectors). The ports can represent one bit of data or a vector of bits. If the port represents a vector of bits, the size can be identified next to its name.

When clicking on the "+" sign of an interface, such as "A" in the above image, the internal ports of the interface appear shown below. Notice also that the "+" sign has changed to a "-" sign. Clicking on the "-" sign hides the ports again.

When the "A" interface is connected to the output of a compatible interface, all individual signals between the two interfaces are connected. If the design requires connecting an interface to an incompatible interface or individual ports on another block, the ports within the interface may be connected instead.

#### Connecting an Output Port to an Input Port

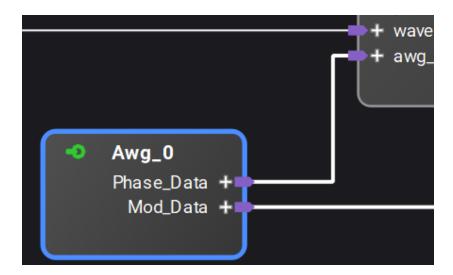

In the image below, connections are made by clicking on one port and then dragging the line from it to another suitable port. This can be done by dragging a line from an output port to an input port or by dragging a line from an input port to an output port. It may also be done by dragging a line from an input port to an existing compatible connection.

Connections can be created according to connection rules. For more information, refer Connection Rules.

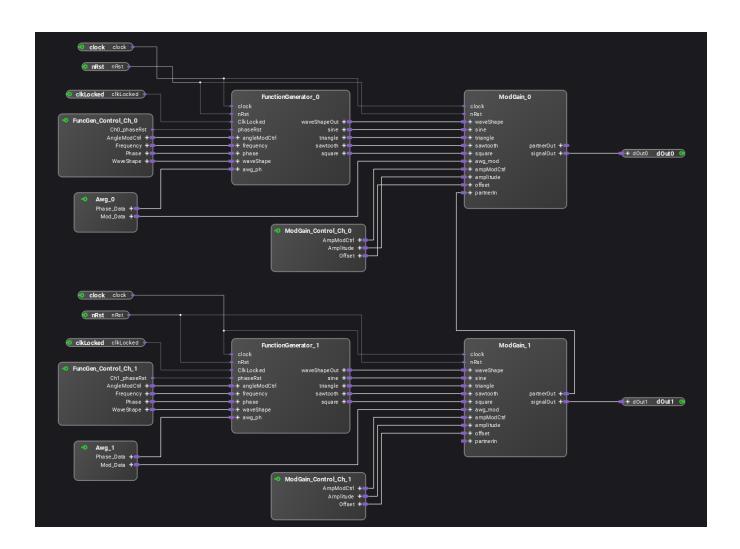

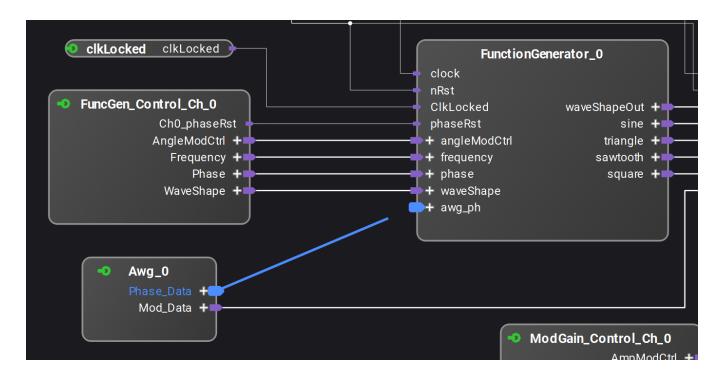

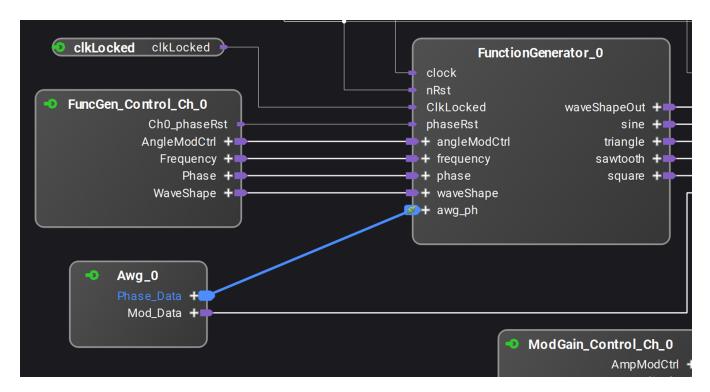

If a connection can be made from a connector, a new line appears from this connector to mouse and the mouse cursor changes to the axis icon as shown below. Furthermore, the possible target connectors are highlighted in blue for showing the different connection possibilities. See the input ports on the lower block "Awg\_0" shown below.

For finishing the connection, the end of the connection line is dragged by the mouse to a compatible target connector. In this case, the mouse icon changes to the green connection icon.

When the mouse button is released, the new connection is created.

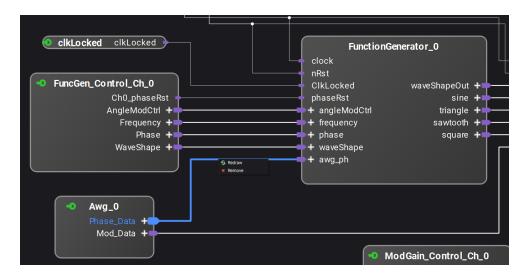

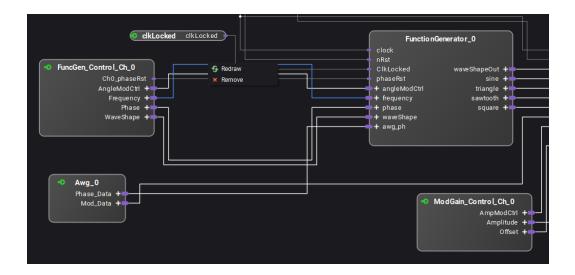

## Remove and Redraw operations

Right-click the line connecting the two ports to see two options: **Remove** and **Redraw**. Remove will delete the connecting line.

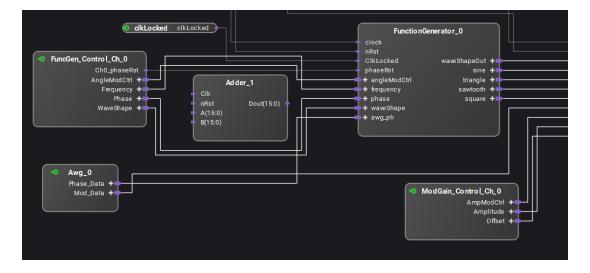

For example, add a block between the two ports. Notice the line connecting the ports is no longer straight.

Delete the block that was just added and notice that the connecting line stays unchanged. Right-click the line and select **Redraw**. The line will be straight again.

## Disconnecting a Connection

Once a connection is created, the connection can be disconnected by right-clicking on the connector, which displays the **Disconnect** option.

#### Connecting Input Ports to a Literal Constant

If you want to connect a input port to a constant numeric value, you should connect the port to a literal. Literals set 64-bit value constants at input ports. To insert a literal, right-click the port and select the 'Connect to literal' command. You can set the value to an integer, hexadecimal, or binary value:

Integer: A integer number, negative numbers set a two's complement format. The range for valid inputs is from -9,223,372,036,854,775,808 to 9,223,372,036,854,775,807, or from -(2^63) to 2^63 - 1

• **Hexadecimal**: A hexadecimal number using the characters 0 - F can be entered, followed by an h; for example, Ah. The range for valid inputs is from 0h to FFFFFFFFFFFFF.

• Binary: Binary numbers can be added followed by a b, for example, 1010b.

#### **Connection Rules**

#### **Ports**

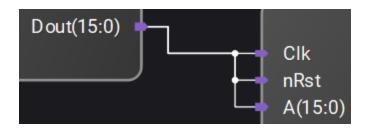

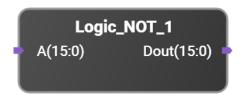

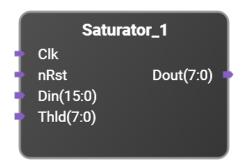

There are input ports and output ports. The input ports can have only one connection to an output port. In this example, Din(15:0) has one connection.

The output ports can be connected to multiple input ports. In this example, Dout(15:0) output is connected to three inputs.

#### Port Size Mismatches

If a wider output port is connected to a narrower input port, then the LSBs of the output port are used to make the connection.

If a narrow output port is connected to a wider input port, the output port connects to the LSBs of the input port. The remaining bits of the input port are set to zero.

In general, if the smaller of the two ports has N bits, then bits N-1...0 of the output port are connected to bits N-1...0 of the input port. Any remaining output port bits are ignored, and any remaining input port bits are set to zero.

In the second example shown above, both clk and rst will be connected to Dout(0).

#### Interfaces

Interfaces with the same type can be connected together as long as their data ports have the same width. Therefore, interfaces of similar protocols can be put together with a single connection. By connecting one interface to another interface, as shown below, all the corresponding ports shown are connected. This removes the chore of having to connect each interface port as shown below.

Clicking on the "+" sign for either interface will expand the interface to show the underlying ports. When an interface is expanded, clicking the "-" sign will collapse the port back to showing just the interface name.

Connection between interface ports that have mismatched width, apart from data ports, is handled the same way as it is described in section Port Size Mismatches.

User Guide GUI Overview

## Connecting Keysight interfaces to Xilinx interfaces

Keysight standard interfaces can be connected to Xilinx standard interfaces when appropriate mappings exist. i.e. a Keysight AXI4 can connect to a Xilinx AXI4. If no appropriate mapping is available, you cannot connect the interfaces.

## Unconnected interface input ports

Input ports of an interface that are left without connection, either explicitly (by no connecting anything to those) or implicitly (in the case of an interface connection, where the respecting output port from the other interface is optional and not defined), will be initialized with the default value specified in the interface's specification. If a value other than the standard default value should be used for any of these ports, a literal with the desired value should be connected to that port.

#### **Special Cases**

In some cases it is not possible to define the default value as per spec definition inside PathWave FPGA. For example, the AXI4MM interface has some default values to depend on the width of the data bus.

In the following table you can find the default values that PathWave FPGA is using:

| Interface<br>Name | Port   | Default value from spec.                                                           | Default value in<br>PathWave |

|-------------------|--------|------------------------------------------------------------------------------------|------------------------------|

| AXI4MM            | awsize | width of data bus in bytes as a power of 2, default assumes a bus width of 32-bits | 2                            |

| AXI4MM            | arsize | width of data bus in bytes as a power of 2, default assumes a bus width of 32-bits | 2                            |

Another Special case for AXI4MM is the ID ports. If the ID port is present on a secondary AXI4MM, the matching primary port must have a width less than or equal to the size of the secondary ID port.

This rule is enforced so that no subtle bugs are introduced into your schematic logic.

If this does not match your expectations and the interface primary does not include this port, you have to explicitly connect the unconnected input port to a literal with the desired default value.

# **Adding and Editing Comments**

Adding and Editing Comments

To add a comment:

User Guide GUI Overview

1. Position the cursor within the project where the comment is to be inserted.

2. Right-click on a blank part of the canvas and select Insert Comment....

3. Add text to the comment text box.

4. The comment can be moved by dragging it with the mouse. Notice the comment is in the foreground and appears above the project elements.

5. On right-clicking the comment, the option to copy or remove is provided.

User Guide GUI Overview

6. Choose **Copy**, to create a duplicate comment.

7. Choose **Remove**, to delete the comment.

# Configuring PathWave FPGA

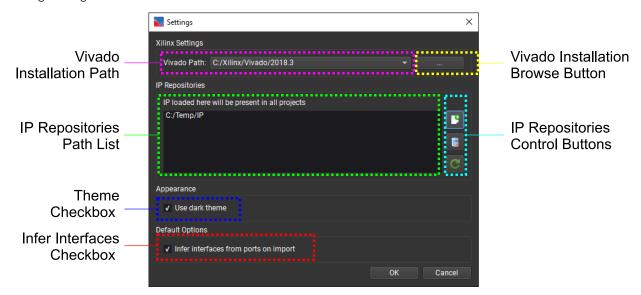

The Settings dialog provides options for configuring *PathWave FPGA*. You can specify the Vivado path, IP repositories, and the appearance of the interface. Select **Tools > Settings** to open the following dialog:

#### Vivado Installation Path

This drop-down list displays the installation path of the Xilinx Vivado version to be used by PathWave FPGA for the bit file generation flow as well as the Xilinx IP Import. At start-up, PathWave FPGA populates the drop-down list with the Xilinx Vivado installations found on the local system. By default, the latest one is selected. The drop-down list may be used to select a different Vivado version. If the desired version is not located, the Browse Button can be used to locate a specific installation.

Vivado IP interfaces are only reloaded on a restart of PathWave FPGA.

NOTE

Changing the Vivado version takes about 10 seconds. A label will show up informing you about this when you are about to change version.

## Vivado Installation Browse Button

Opens a browse dialog for the user to locate a Xilinx Vivado installation that was not found automatically.

# **IP Repositories Path List**

Displays a list of directory paths, where PathWave FPGA will look for IP. To learn more information on how to create an IP repository, you can review the IP Developers Guide.

The actual IP discovery process takes place either when the user clicks the button explicitly, or when the list is updated and the settings dialog is accepted. If a project is open at the time of loading, the discovered IP will be loaded to the open project.

Currently, PathWave FPGA does not support having multiple IP with the same name. If more that one IP with the same name is encountered during a project load, PathWave FPGA will only load the first one and report an error for the others. To workaround this limitation, you can create a wrapper for your IP with name that does not conflict with any other in the project library.

The IP repositories specified here will be available to all projects. To specify IP repositories that will be available to a specific project, see Project Settings Dialog.

# **IP Repositories Control Buttons**

The button opens a browse dialog for selecting an IP Repository location. If a location is selected, it is added to the IP Repositories Path List.

The button searches for IP inside the directories defined in the list. When IP repositories loading is completed, an informational message is displayed. In case of errors or warnings, the errors will be logged into a temporary file. The temporary file will exist until the closing of PathWave FPGA process. To regenerate the log file, repeat the loading procedure.

#### Theme Checkbox

To use the dark theme, check the *Use dark theme* check box.

#### Infer Interfaces Checkbox

When importing VHDL or Verilog User IP, interfaces can be deduced from the naming convention of the ports. Each time a new IP file is added, the user has the option to infer interfaces from the ports. The default choice is controlled by this checkbox.

# Designing your FPGA Logic

### **Contents**

- Creating a New Sandbox Project

- Creating a New Submodule Project

- Project Settings Dialog

- Design Interfaces

- IP Catalog

- Naming Conventions

- Name Collisions

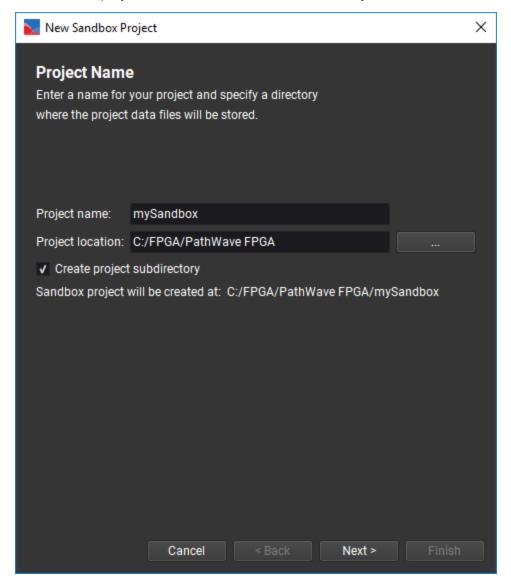

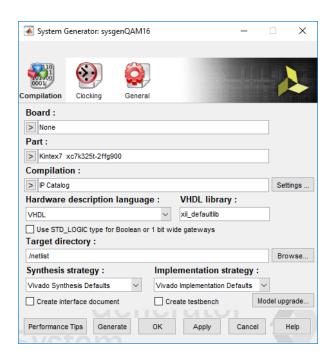

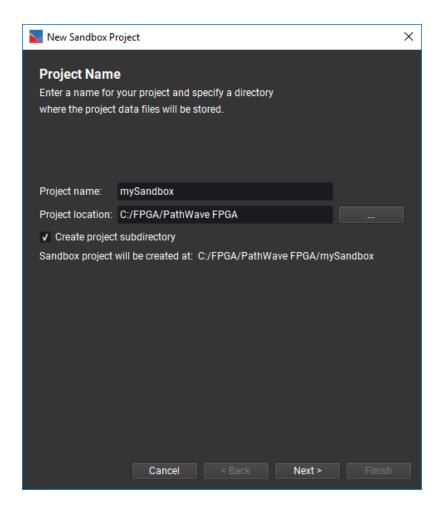

# **Creating a New Sandbox Project**

A sandbox project contains the customizable resources of the programmable FPGA of a PathWave FPGA hardware module. When selecting a target module, the project is opened with the factory settings of a standard module. The custom on-board solution is developed within this hardware project and is saved, compiled and loaded into the hardware module (the binary can be loaded into multiple identical modules).

Below are the steps to create a new sandbox project.

- 1. Select File > New... > New Sandbox Project.

- 2. Enter the project name.

- 3. Browse to select the project location.

- To place the project in a subdirectory by the same name, select the **Create project subdirectory** check box.

- 4. Click **Next**. If a project with the same name exists, a prompt to overwrite the project is displayed. Click **Yes** to overwrite the project.

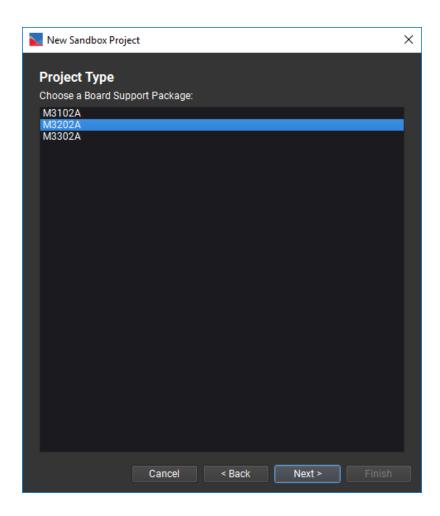

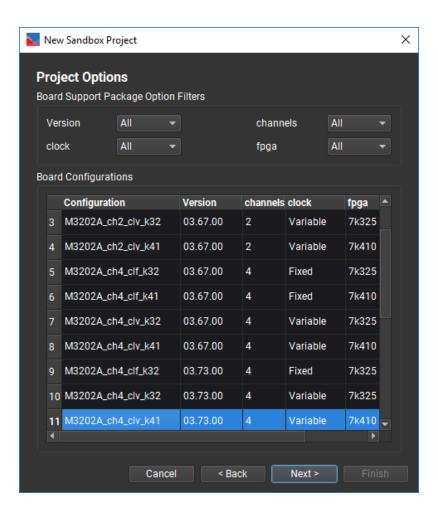

- 5. Choose the **Board Support Package** for the target hardware module and click **Next**.

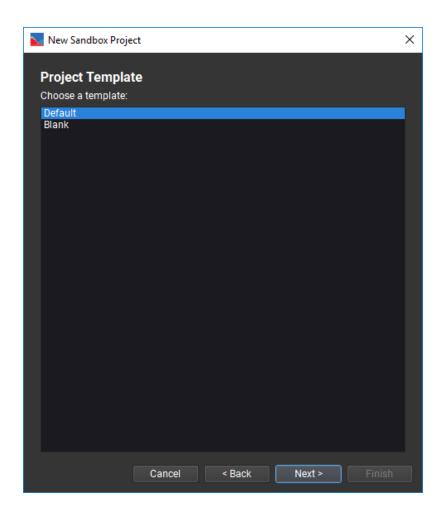

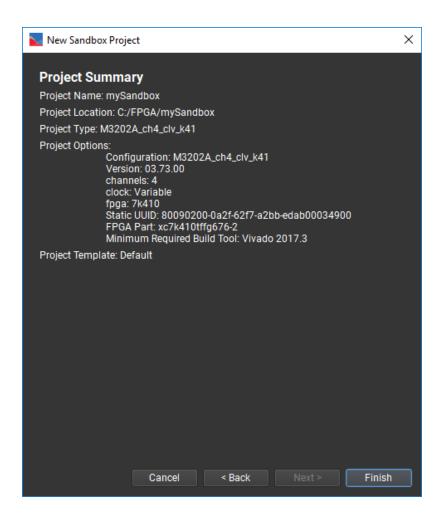

- 6. Choose a Project Template and click **Next**. A summary of the project details is displayed. Click **Finish**.

- 7. To save any changes you made to the project, click the **Save** icon or use the menu option.

Using the shortcut menu (right-click a block), you can perform the following operations:

NOTE

- To duplicate a block, select Copy.

- To flip a block horizontally, so inputs are on the right and outputs on the left, select Flip.

- To redraw the connections to the block, select Redraw connections.

- To remove the block, select **Remove**.

- To view the description/properties, select Properties.

## Sandbox Project Directory Structure

When a new project is created, a project folder with a corresponding project design file is created. This project folder will contain build output and any Vivado XCI (Xilinx Core Instance) IP that you have configured using PathWave FPGA. In the following example, the project created is named *myProject*. The directory structure is shown below:

- myProject Project folder

- myProject.kfdk Project design file

- myProject.build Folder containing intermediate build output

- myProject.data Folder containing final build output and Vivado XCI IP

- o bin Folder with the final build output

- myProject\_<timestamp> Folder containing build output

- bitgen.log Vivado build log file

- myProject.k7z Program archive that can be downloaded into your FPGA

- myProject.spb Program FPGA bit file that is an older format, to supported existing instrument software for M3102A, M3202A, M3302A and associated instruments. Newer Keysight hardware will not produce this file output.

- VivadoIP Folder to contain output for Vivado XCI IP that was configured using PathWave FPGA

- <imported Vivado XCI> Folder for each Vivado XCI IP configured using PathWave FPGA

- submodules Folder to contain submodule projects. The directory structure that is created

is an IP Repository of the submodules defined in the project

- mySubmodule Submodule with default name

- mySubmodule.data Folder containing Vivado XCI IP

### Source Control

This section will describe best practices for using a version system for tracking changes in your PathWave FPGA project.

PathWave FPGA takes some steps to work well with source control of its project files, such as using plain text and maintaining a consistent order of elements. If more than one person is making changes to a PathWave FPGA project, the changes may need to be merged. However, automated merging of significant changes should not be considered reliable. Always check for problems by opening the project and running a synthesis build after a merge. When in doubt, manually "merge" the changes by repeating them using the PathWave FPGA GUI.

If your project includes software source code, follow the best practices as for any other software source control. The example projects that come with PathWave FPGA use CMake. In this case, CMake will place the Visual Studio solution or Unix makefiles and all build artifacts in a directory, usually with the word "build" in the name. This directory should be excluded, and most other files should be included.

# Which files should be tracked

| File path                                                                                   | Track? |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|---------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| projectName.kfdk                                                                            | Yes    | The project design file should be tracked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| projectName<br>.kfdk.bak                                                                    | No     | Backup project files are created when a project is upgraded to a newer version of PathWave FPGA, or when a project is retargeted to a different BSP. If you are tracking the project file with source control, you already have a backup and don't need these files.                                                                                                                                                                                                                                                                                  |  |  |

| projectName.build/                                                                          | No     | This directory contains intermediate build files which don't usually need to be stored.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| projectName<br>.data/submodules/                                                            |        | Each submodule is contained within a directory in submodules. Its directory structure mirrors that of the main project. There will never be a <i>submoduleName</i> .build directory, but there may be a <i>submoduleName</i> .data directory containing any Vivado IP used by the submodule. The same guidelines for the sandbox project directory apply for the submodule directory. In the provided .gitignore file, some patterns use ** so that they apply to both the sandbox and the submodule.                                                 |  |  |

| projectName<br>.data/bin/                                                                   |        | Each successful sandbox build creates a directory in bin with the .k7z file, and sometimes other BSP-specific files. These files can be included or excluded depending on your requirements.                                                                                                                                                                                                                                                                                                                                                          |  |  |

| projectName .data/VivadoIP/ip_ No user_files/                                               |        | This directory contains files generated by Vivado when configuring IP. These files are only created if you click Generate after configuring the IP. PathWave FPGA does not use these files because it always regenerates Vivado IP at the start of the build.                                                                                                                                                                                                                                                                                         |  |  |

| projectName .data/VivadoIP/ ipName/ipName.xml projectName .data/VivadoIP/ ipName/ipName.xci | Yes    | Each configured Vivado IP is contained in a directory inside VivadoIP. Two files in this directory are important: the .xci and the .xml. All other files should be excluded from version control.  You may see critical warnings from Vivado during the sandbox build if the other files are missing, but the build will still complete correctly. To remove the critical warnings, launch the Vivado IP tool from within your project, select all of your IP, right click and select "Reset Output Products". This will remove all extraneous files. |  |  |

# Sample .gitignore file

The following file will make git ignore the files that shouldn't be tracked. Place this file in the same directory as the project file.

- \*.kfdk.bak\*

- \*.build/

- \*.data/bin

- \*\*/\*.data/VivadoIP/ip\_user\_files/

- \*\*/\*.data/VivadoIP/\*/\*

- !\*\*/\*.data/VivadoIP/\*/\*.xml

- !\*\*/\*.data/VivadoIP/\*/\*.xci

# Creating a New Submodule Project

A submodule project allows you to organize your design hierarchically and reuse these designs in multiple projects.

Below are the steps to create a new submodule project.

- 1. Select File > New... > New Submodule Project, from the menu of an open sandbox project.

- 2. In the New Submodule Project dialog, enter the submodule project name and click **Next**.

- 3. Define the vendor, library, name and version (VLNV) and other properties of the submodule. This information can be modified later by selecting **Project > Properties...**

- 4. Click **Next**. A summary of the project details is displayed. Click **Prev** to make changes or **Finish** to save the new submodule project. See **Sandbox Project Directory Structure** for information about how submodule projects are saved.

- 5. A new instance of PathWave FPGA will be started where you can edit your new submodule.

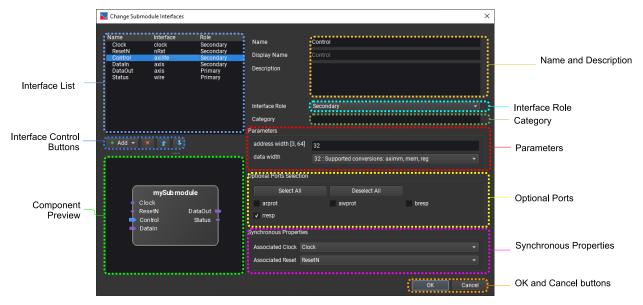

- 6. In the Change Submodule Interfaces dialog, define the interfaces into and out of the submodule. See Configuring Submodule Interfaces for more information. The interfaces can be modified later by selecting Project > Change Submodule Interfaces...

- 7. Click **OK** to close the Change Submodule Interfaces dialog.

- 8. To save any changes you made to the project, click the **Save** icon or use the menu option.

# **Project Settings Dialog**

The project settings dialog provides some options for configuring *your PathWave FPGA project* by adding IP repositories and constraints. Select **Project > Project Settings** to open the following dialog:

## IP Repositories Path List

Displays a list of directory paths specific to the loaded project; PathWave FPGA will search for IP in these directories. To learn more creating an IP repository, see the IP Developers Guide.

The actual IP discovery process takes place either when the button is clicked, or when the list is modified and the OK button is clicked. If a project is open at the time of loading, the discovered IP will

be loaded in the open project. After the IP discovery process, a dialog will report how many IP have been found, and any warnings or errors that occurred.

An IP repository path may be converted to a relative path by right-clicking on the path and selecting 'Use Relative Path' in the context menu. You may convert back to an absolute path by selecting 'Use Absolute Path'.

## IP Repositories Control Buttons

The button opens a browse dialog for selecting an IP Repository location. If a location is selected, it is added to the IP Repositories Path List.

The button removes the selected directories from the list.

The button searches for IP inside the directories defined in the list. When IP repositories loading is completed, an informational message is displayed. In case of errors or warnings, the errors will be logged into a temporary file. The temporary file will exist until PathWave FPGA is closed. To regenerate the log file, repeat the loading procedure.

NOTE

To specify IP repositories that will be available to all projects, specify the repositories in the PathWave FPGA Settings dialog (see Configuring PathWave FPGA).

#### **Constraints**

Constraints are used to control timing, placement, or some other properties of the FPGA build. This section of the Project Settings dialog lets you add constraints to the build. Press the Add button to browse for a constraint file, which must have the file extension ".sdc" or ".xdc". Constraints may be enabled for Synthesis or Implementation, or both, or neither. Note that constraints applied to Synthesis may be propagated to Implementation automatically.

Constraints may be added with an absolute path or a relative path to the project file. When a file is added, it will use a relative path if it is inside the project directory. Otherwise it will use an absolute path. Right-click a constraint to switch it between absolute and relative path manually. You can also right-click a constraint to show the file in Explorer.

If a constraint file is not found, it will be displayed in red. The FPGA build may still be run, but that constraint file will not be used.

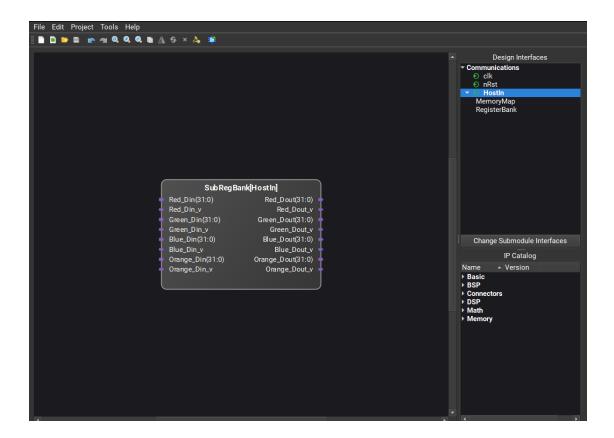

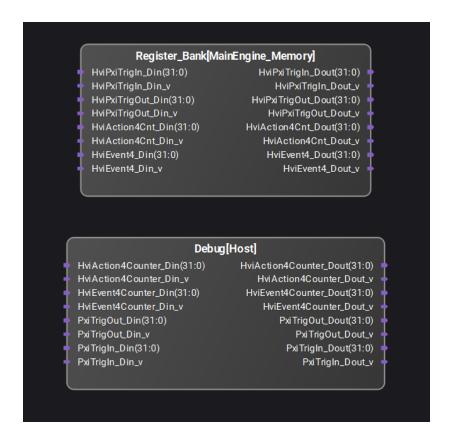

# **Design Interfaces**

To communicate between the design and what lies outside the design, i.e. the static region for sand-box designs, or some other design for submodules, you need to instantiate a design interface block

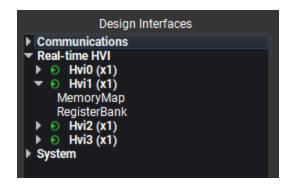

from the design interfaces pane. Each board support package provides a unique set of design interface blocks that are specific for the instrument. The design interface blocks are grouped based on the function of their connections to the "outside world". The interfaces of a design are collapsed, in order to show the different categories of design interfaces:

Apart from categorizing, some design interface blocks can be instantiated with different types of interfaces. For example, the interface "Hvi1" can be inserted to the schematic as a MemoryMap or connected directly to a RegisterBank.

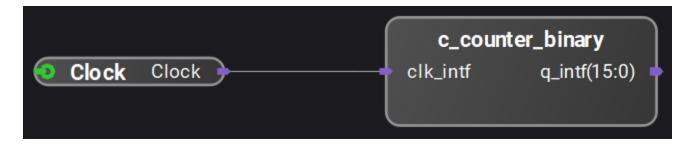

Finally, it is possible that an interface is comprised only by one port (e.g. a clock). In that case, the interface instance will only show the slot, like in the picture below:

#### See Also

- Keysight Standard Interfaces

- Adding a Memory Map

- Adding a Register Bank

- Configuring Submodule Interfaces

- Deciding the Address Width of an Interface

- Registering Sandbox Interfaces

- Symbol Names

# **Keysight Standard Interfaces**

### Contents

- Introduction

- Interface Descriptions

- clock

- nRst

- AXIMM

- AXILite

- AXIS

- mem

- vector

- wire

- · Addressing scheme

- Signal Types

- Data Types

- · Data Packing/Extending

- Polarity

- Signal Interfaces

- Example Usage

- Discussion of Example

- Associated Files

### Introduction

To facilitate connectivity between IP blocks and Design Interfaces, PathWave FPGA has standardized on a number of interfaces. IP blocks using these interfaces will be easier to interconnect and to connect to PathWave FPGA library blocks and Design Interfaces.

# Interface Descriptions

The following is a brief description of the standard interfaces PathWave FPGA supports. Note that this is only a brief description of each interface and is not meant to be a complete description. Some interfaces (e.g. the AXI family) include optional signals that can be included or omitted in particular implementations depending on the design requirements. This allows the user to tailor the complexity and size of the interface while maintaining compatibility.

#### clock

A free running clock. Data is both sampled and changed on the rising edge of a clock.

#### nRst

An active low reset signal.

#### **AXIMM**

The industry standard AXI4-Memory Mapped high performance bus architecture.

- Includes address information. This is a byte-addressable interface, meaning that each address unit addresses 8-bits of data.

- Supports data widths: 32, 64, 128, 256, 512, 1024 bits.

- Supports burst (high performance) transfers.

- Supports bi-directional flow control.

#### **AXILite**

The AXI4-Lite bus, a lightweight version of AXIMM for simpler interfaces that don't require the performance/features of full AXI4.

- Limited data width: 32 (preferred) or 64 (if needed).

- Only single transactions supported no data bursting.

- Supports bi-directional flow control.

#### **AXIS**

The AXI4-Streaming interface is for streaming arbitrarily long sequences of data.

- Point-to-point streams this interface does not include address data, though optional TID, and TDEST signals allow some routing (addressing) information.

- Data width is any multiple of 8 bits. Unlike AXIMM and AXILite, AXIS can support, for example, 24 bit data.

- The standard allows no data (TDATA is optional). An AXIS interface without data just has the control signals.

- PathWave FPGA will allow the data width to be non-multiples-of-8, although this is non-stand- ard.

- Supports optional TUSER data signals. These are extra signals that are logically attached to data samples that could be used to include auxiliary data such as triggers or data marks or timing information.

- Supports merging/packing multiple data items into wider stream.

- Supports bi-directional flow control.

#### mem

A very light weight Keysight proprietary interface.

- · Can be bi-directional.

- Includes addressing. This is a word-addressable interface, meaning that each address unit addresses 32-bits of data.

- Does not include back-pressure all transactions take place in one clock cycle and can not be held off.

- Has deterministic timing.

- Used for HVI register access. Please see the Keysight KS2201A Test Sync Executive documentation for more information on HVI.

#### vector

A multi-bit vector of signals without any signaling protocol. This might be used to connect a control register to an IP block.

#### wire

A single bit signal. This might be used for a trigger signal.

## Addressing scheme

By addressing scheme, we refer to the number of data bits each address unit is addressing.

For example, in a byte-addressing scheme, each address unit addresses 8-bits of data. That means that if we store a 32-bit data value '0xabcd0123', in a little-endian memory structure, at address b'11110000, then the memory will look like this:

| address            | data (8-bit)              |

|--------------------|---------------------------|

| b'111011 <b>11</b> | <other_data></other_data> |

| b'111100 <b>00</b> | 0x23                      |

| b'111100 <b>01</b> | 0x01                      |

| b'111100 <b>10</b> | 0xcd                      |

| b'111100 <b>11</b> | Oxab                      |

| b'111101 <b>00</b> | <other_data></other_data> |

On the other hand, for a word-addressing scheme, each address unit addresses 32-bits of data. That means that for the same example as before, the memory will look like this:

| address            | data (32-bit)             |

|--------------------|---------------------------|

| b'111011 <b>11</b> | <other_data></other_data> |

| b'111100 <b>00</b> | 0xabcd0123                |

| b'111100 <b>01</b> | <other_data></other_data> |

In the context of PathWave FPGA, there are currently three interfaces that are using addressing: AXI4MM, AXI4Lite and MEM. The first two (AXI4MM, AXI4Lite) use a byte-addressing scheme while the MEM interface uses a word-addressing scheme.

# Signal Types

There are a number of different types of signals used in a typical design. These can roughly be categorized into control signals (typically used to setup, control, and monitor a measurement), and data flow signals (the data being processed - this could be a continuous stream of data or one or more blocks of data).

The following are the various types of signals that PathWave FPGA supports:

- 1. Control Bus Secondary. Typically these would be register control/status blocks where the driver could read and write status and control data.

- 2. Control Bus Primary. This is for the case where the user IP wants to communicate with external devices via the PCIe (or other host control) bus, e.g. write to other modules to control multi-module measurements.

- 3. Continuous Streaming Data. This is an arbitrarily long stream of continuous data, e.g. from an ADC. Since the data may not be one sample per clock, flow control is required. Alongside the data, there may optionally be some amount of sideband data. This is auxiliary data that flows along with the main signal data. It could include triggers or marker info or be used to timestamp data.

- 4. Block Mode Stream Data. This would be an arbitrarily long stream of discontinuous blocks of data. Each block may represent the result of some measurement or calculation, e.g. the output of an FFT. To properly interpret this data, the boundaries of each block would need to be delineated.

- 5. Memory Read / Write Data. Typically the FPGA will have access to off chip memory. There needs to be a way for the user IP to read and write to this memory. This interface will need to include both address and data flow, and probably needs to support burst transfers for efficiency.

- 6. Supersampled Data. This is a variation of #3 and #4 above where more than one sample per clock needs to be transferred.

- 7. HVI. HVI needs an efficient, time deterministic mechanism to access control register.

- 8. Clock. One or more clocks. Signals change on and are sampled on the rising edge of clock.

- 9. Reset. One or more active low reset signals.

## **Data Types**

Most of the data that PathWave FPGA will be processing is likely to be fixed point (scaled ints) of varying bit widths. To facilitate interconnection of IP, limit the amount of data width conversion, and allow the use of standard interfaces, PathWave FPGA standardizes on data widths that are an integral number of bytes (i.e. multiples of 8 bits). Data that is natively a different size should be padded up to the next multiple of 8 bits by padding MSBs. Unsigned quantities are zero-extended, and signed quantities are sign extended. Thus a 12 bit unsigned number would place those 12 bits as the 12 LSBs of the interface with the 4 MSBs being zero. So if the data was X[11:0], the interface used would be TDATA[15:0] = {4'b0000,X[11:0]}.

The preferred format for floating point numbers in PathWave FPGA will be IEEE-754 compliant. The two supported (preferred) sizes will be binary16 (16 bits with 11 bit fraction and 5 bit exponent) and binary32 (32 bits with 24 bit fraction and 8 bit exponent). Note that the number of fractional bits includes the implied leading "1" bit. The number of physical mantissa bits is one less than the number of fractional bits, and there is also sign bit. Physically, the binary32 format would have 1 sign bit, 8 exponent bits, and 23 mantissa bits.

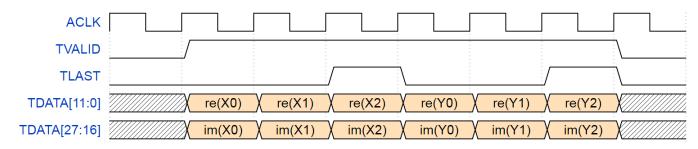

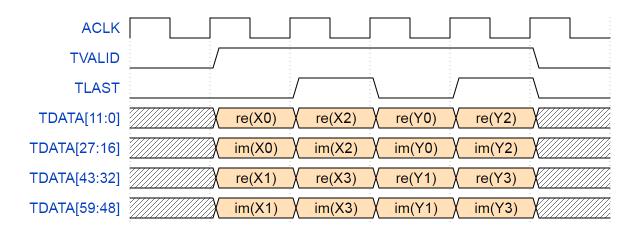

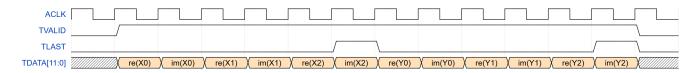

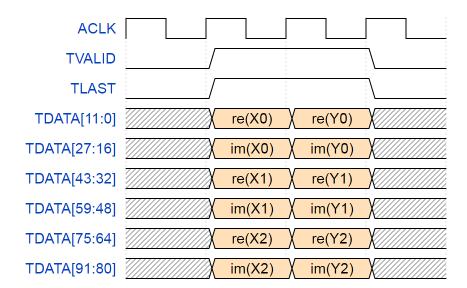

It is not uncommon to process complex data (that is, data consisting of a real and an imaginary component). If complex data is being sent over a single stream, the real and imaginary parts will be sent in parallel over a wider stream with the real part will go in the least significant word. For Serial data, the real part will come first (earlier in time).

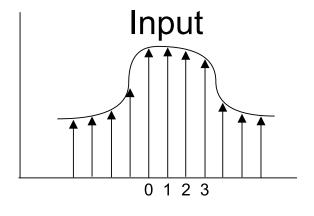

Above are examples of parallel complex data (one sample per clock and two samples per clock). Below is an example of serial complex data.

For performance reasons (and the limited clock rate available in FPGAs), it is sometimes desired to transfer more than one sample per clock. This is called *supersampled* data. In this case, each sample (or component of the sample for complex data) is first extended to an integral number of bytes, and then these are packed together with the earlier in time samples occupying the lesser significant position:

## Data Packing/Extending

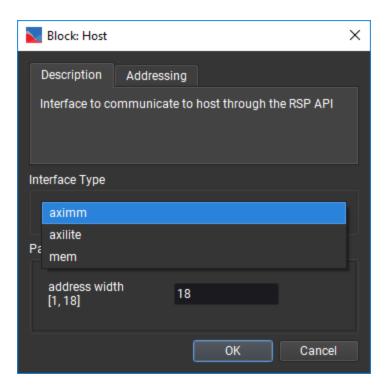

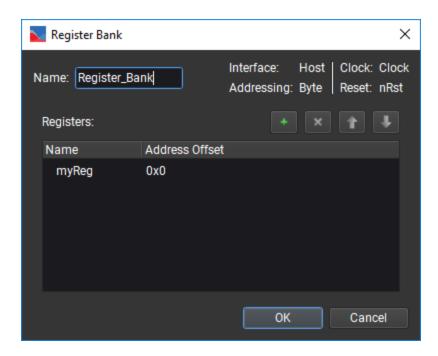

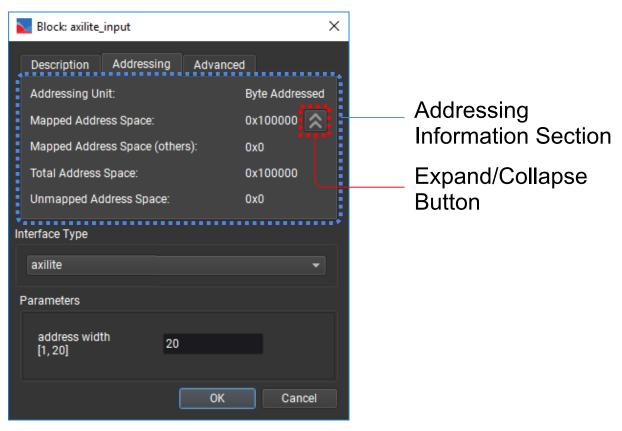

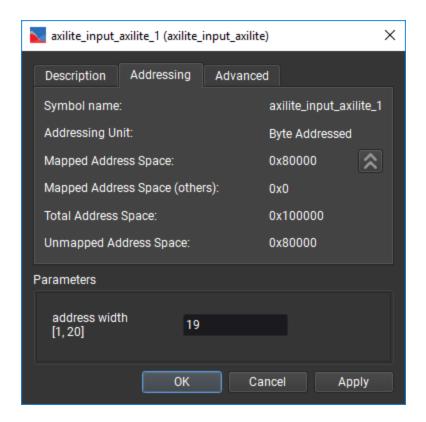

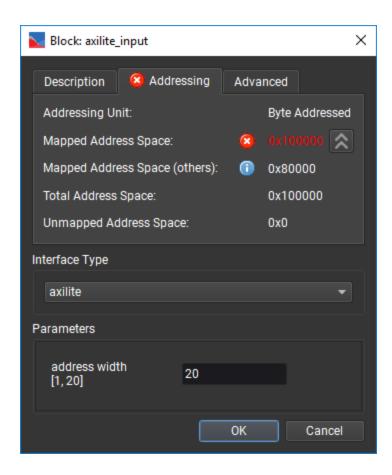

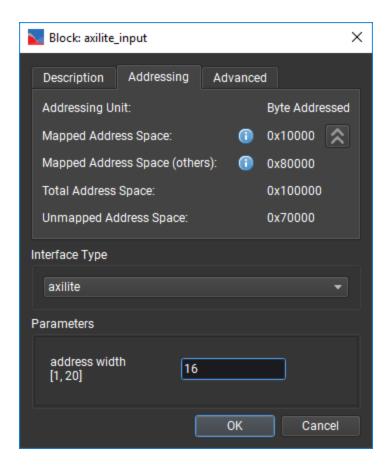

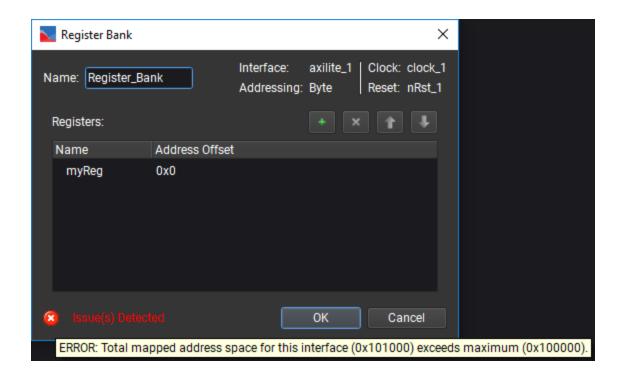

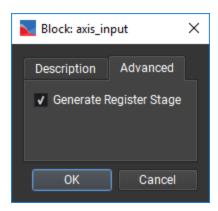

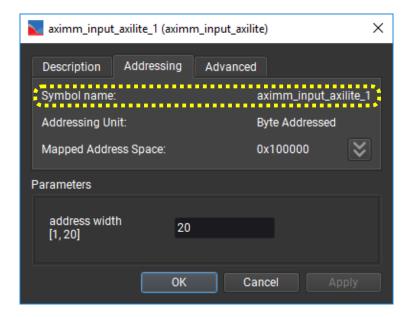

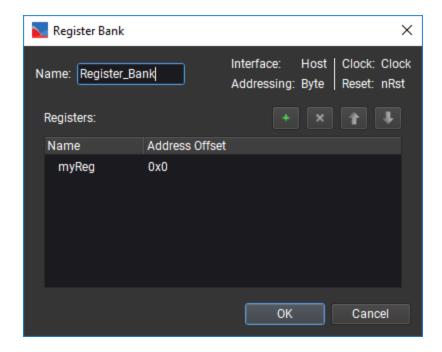

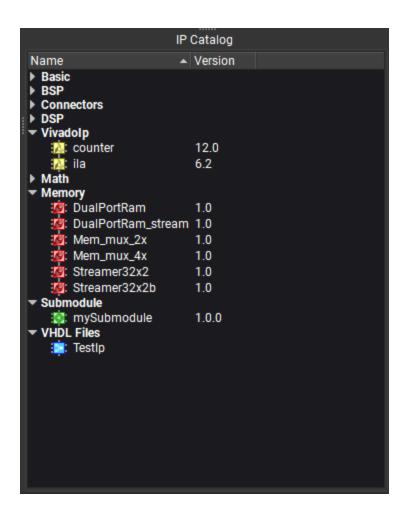

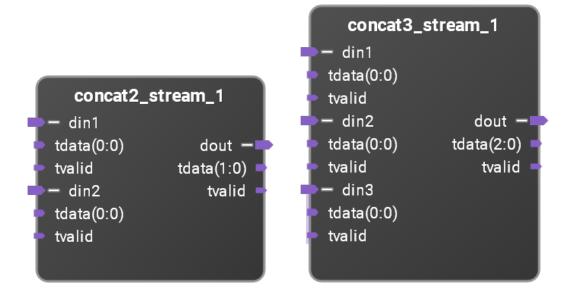

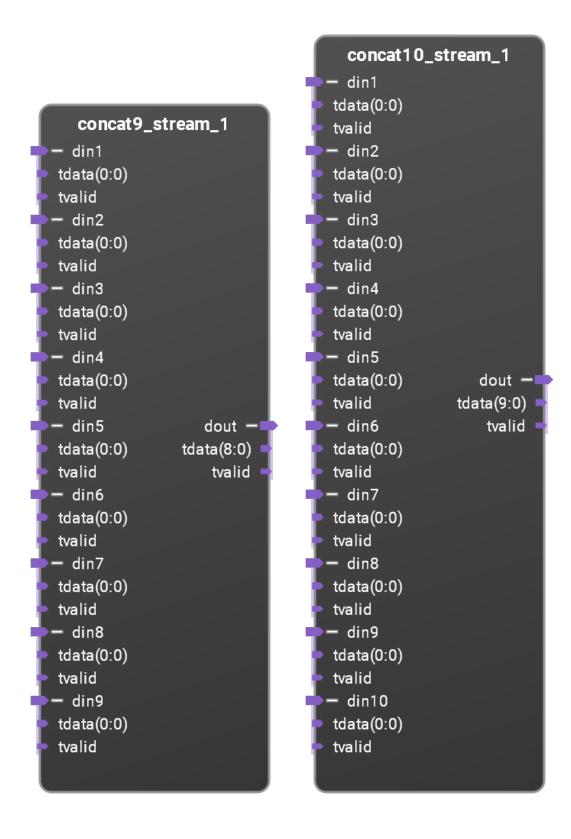

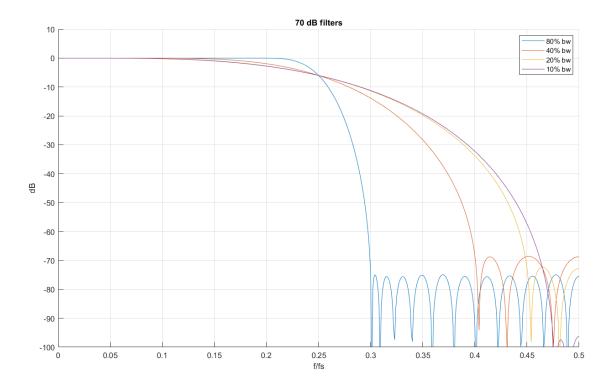

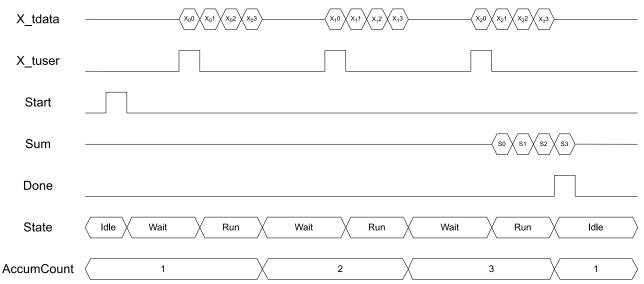

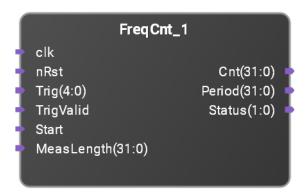

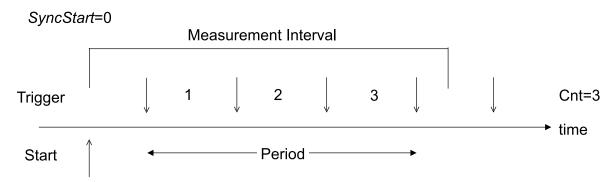

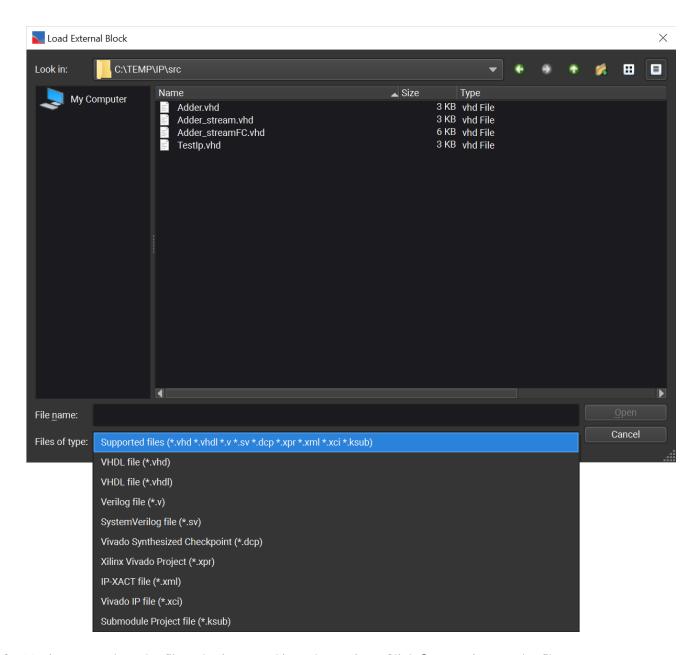

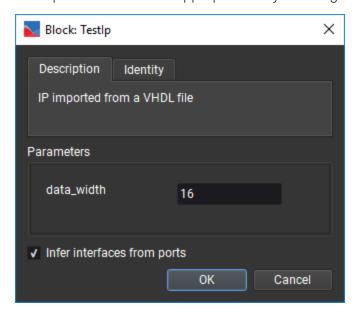

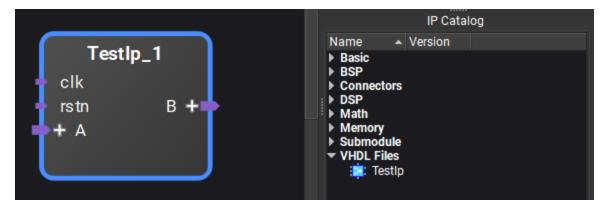

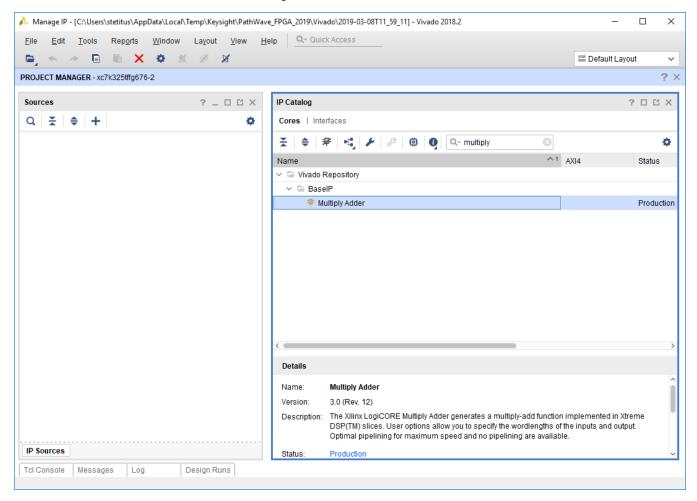

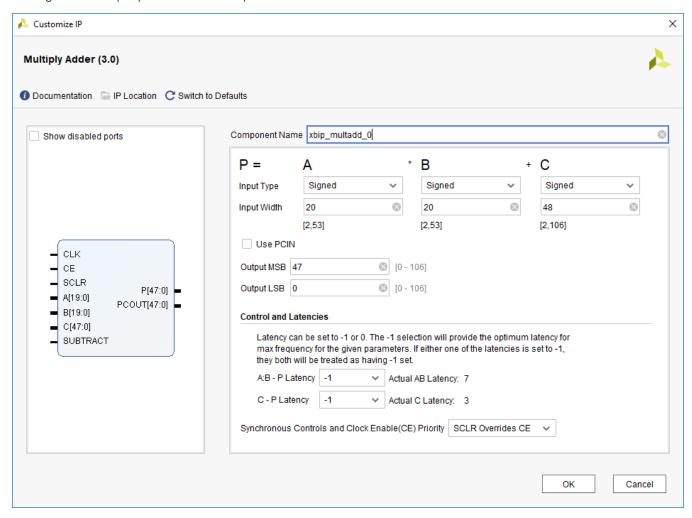

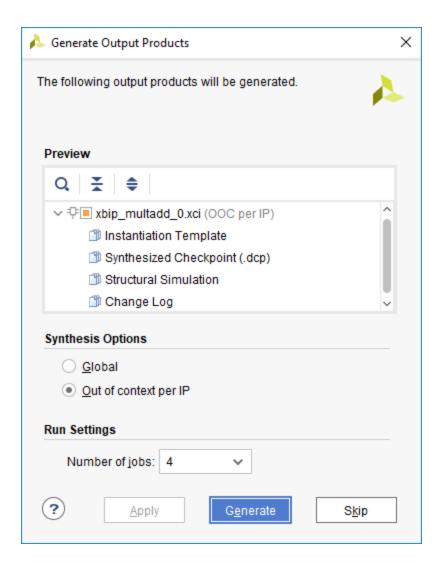

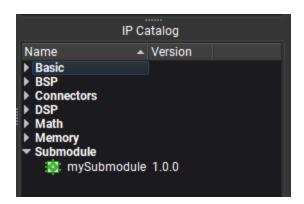

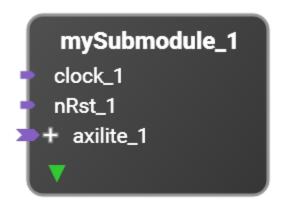

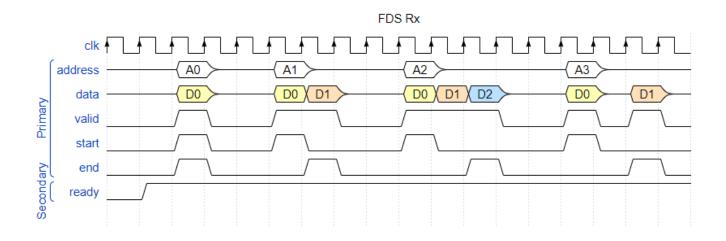

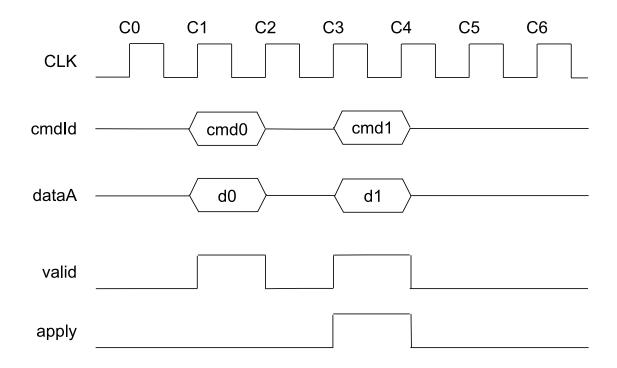

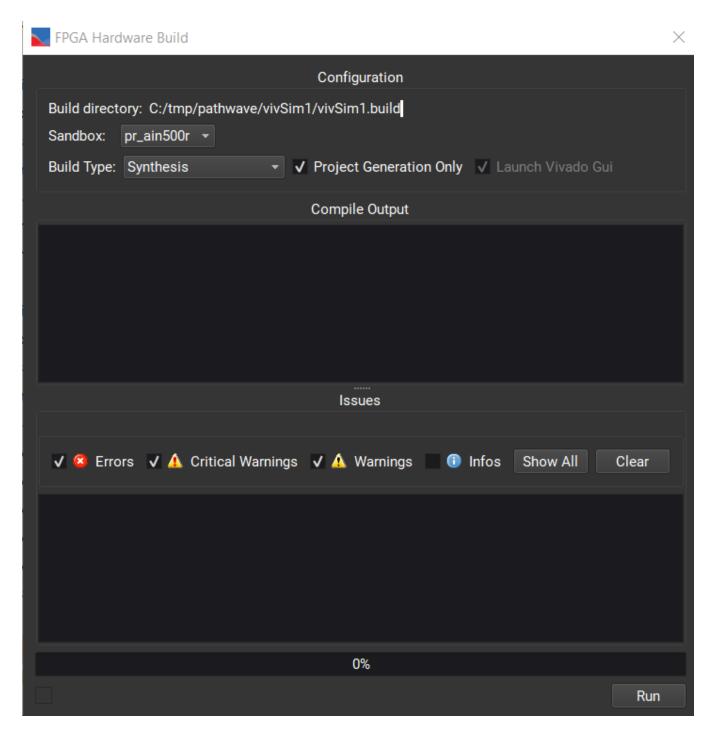

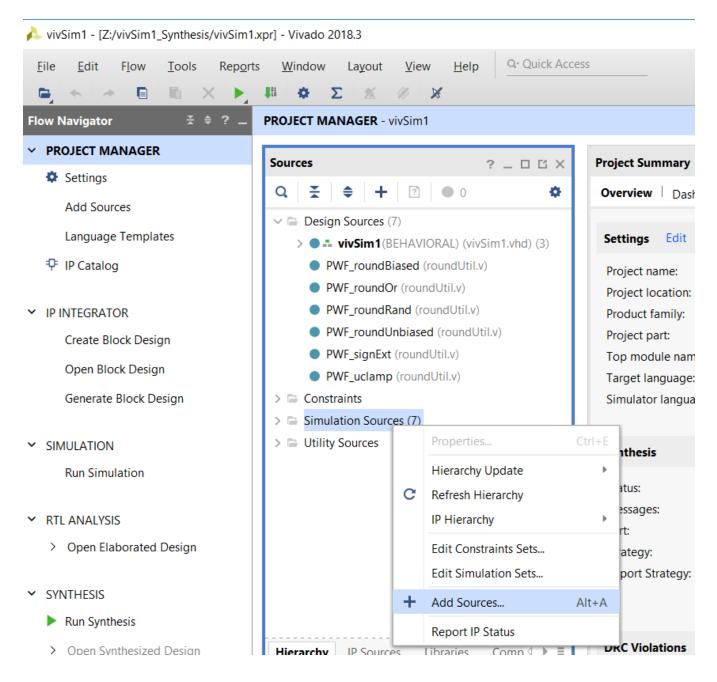

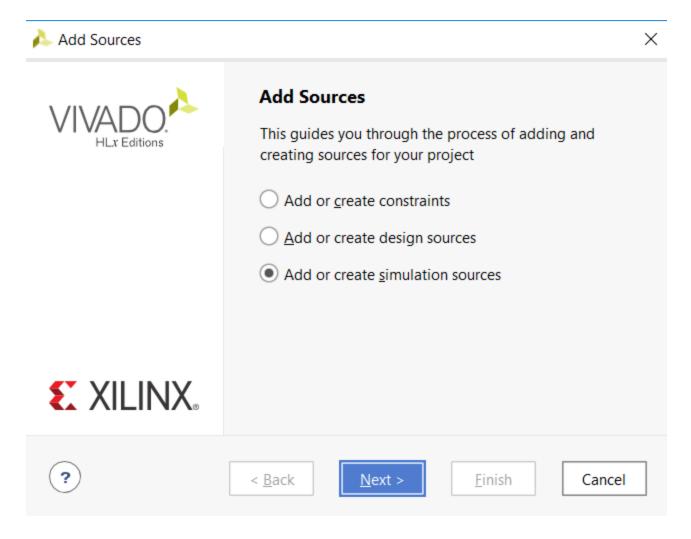

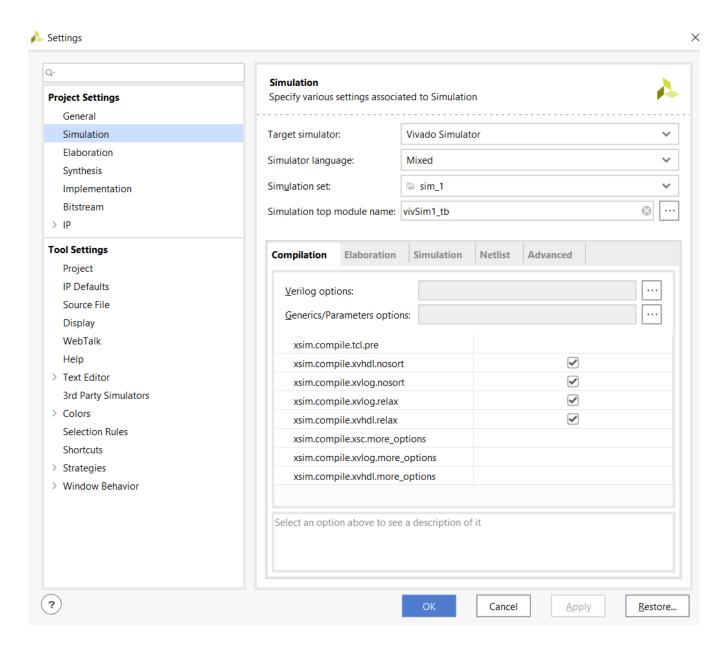

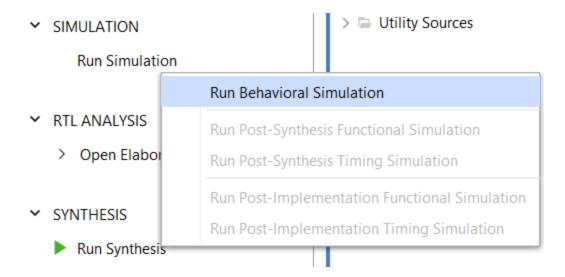

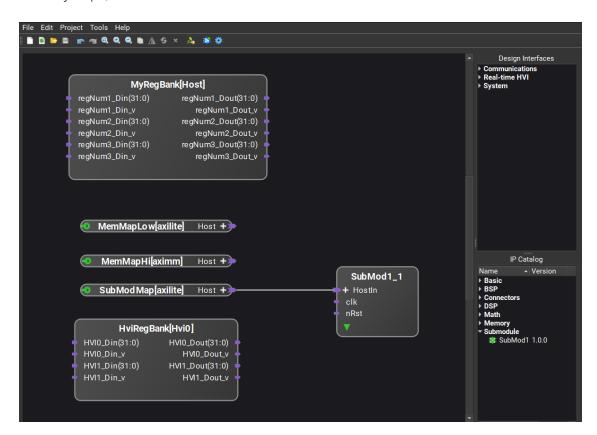

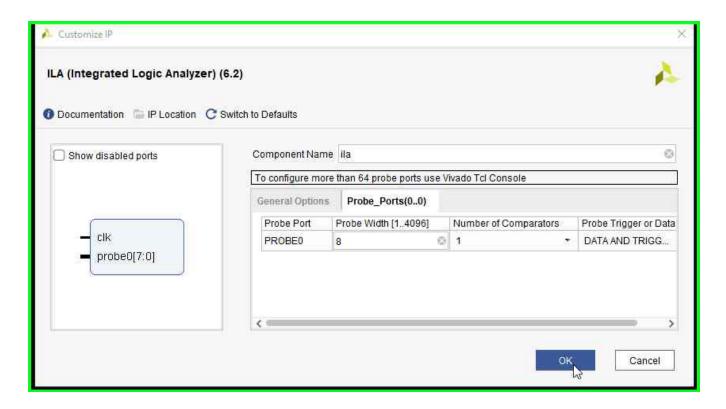

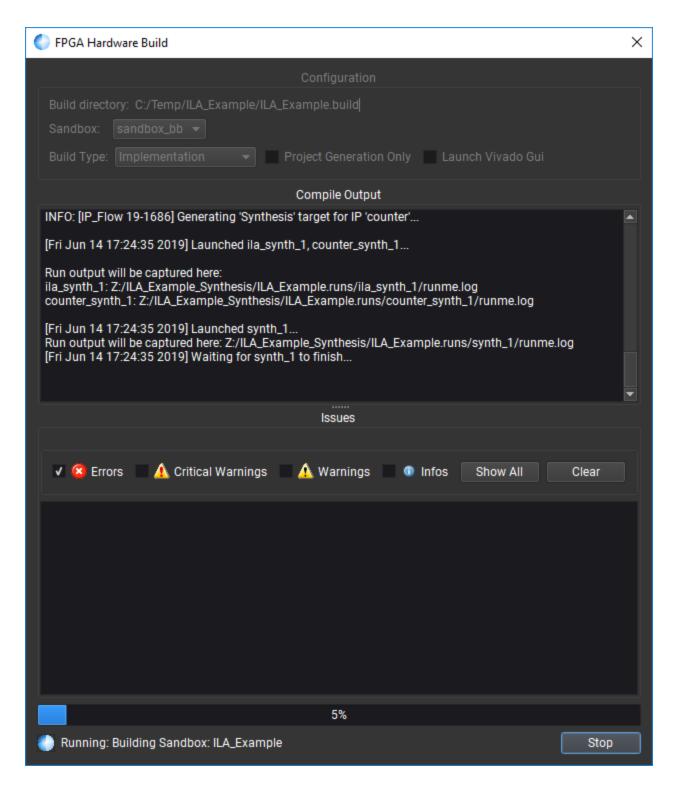

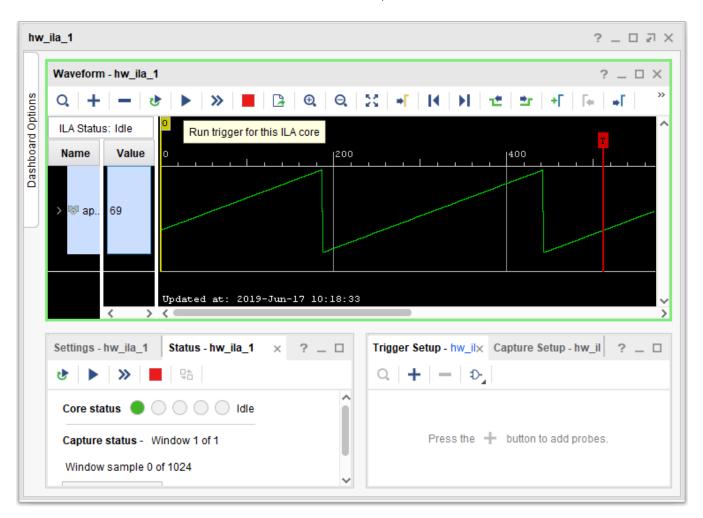

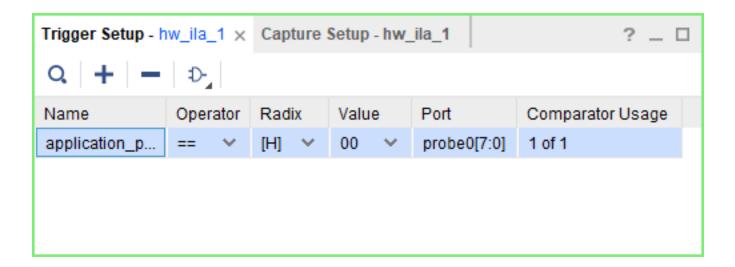

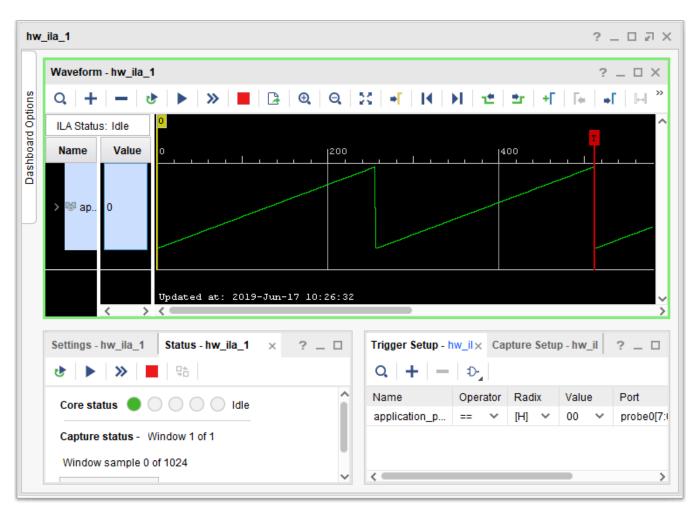

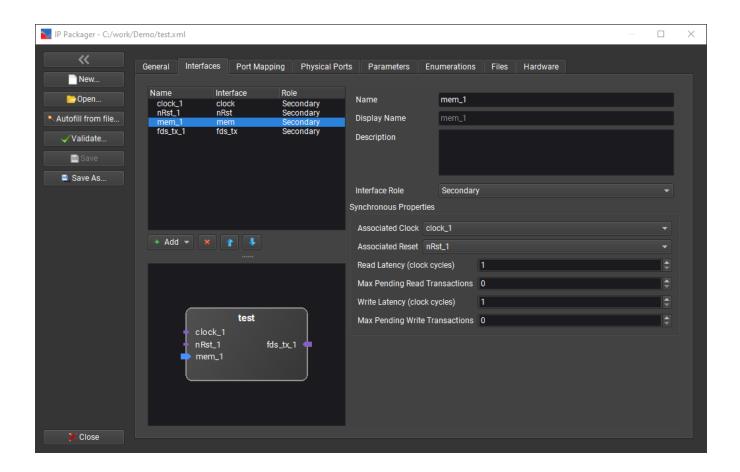

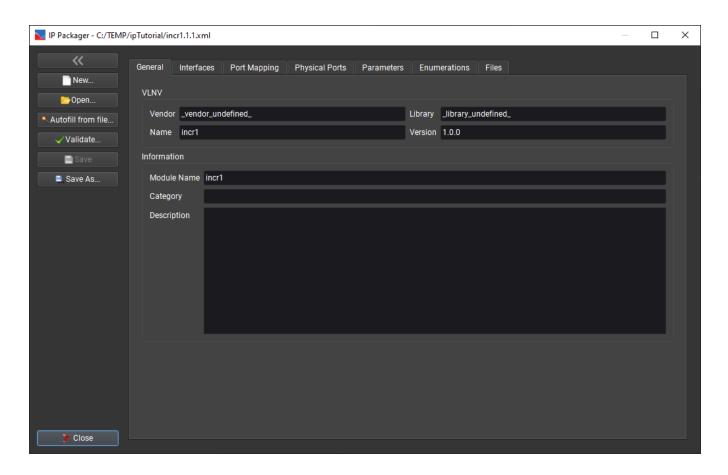

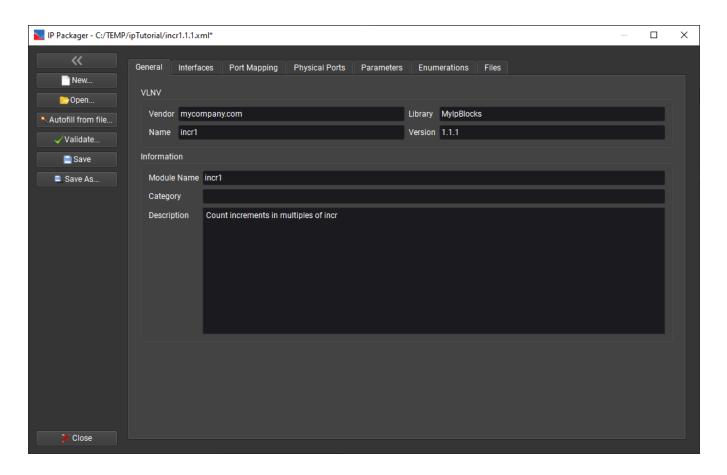

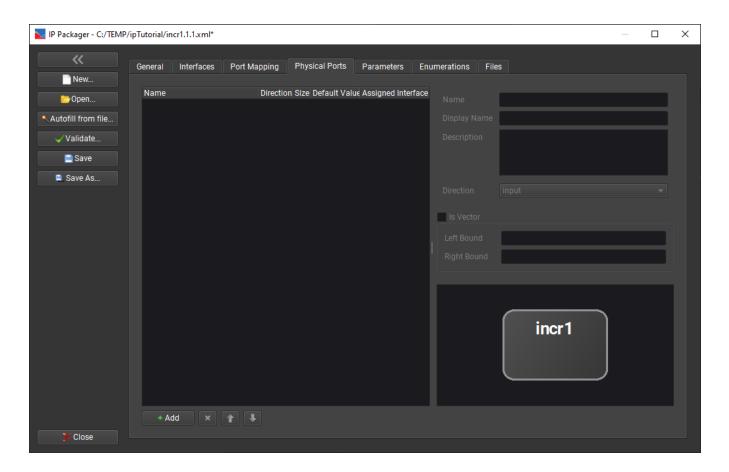

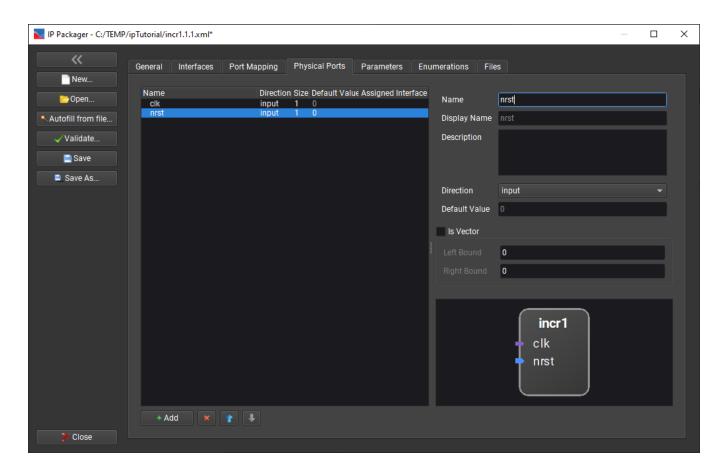

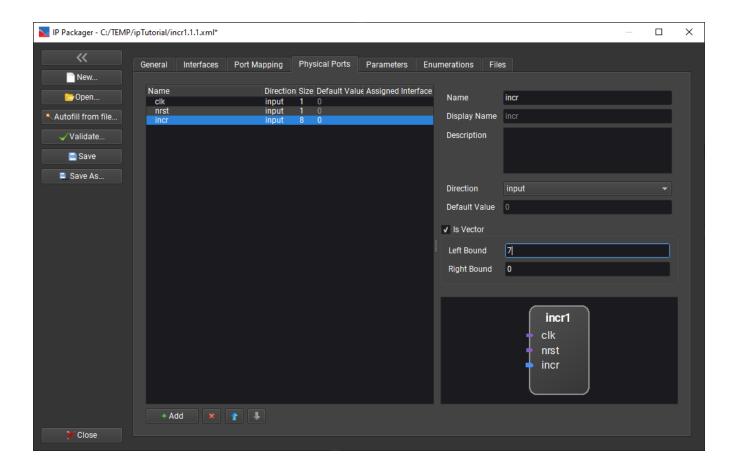

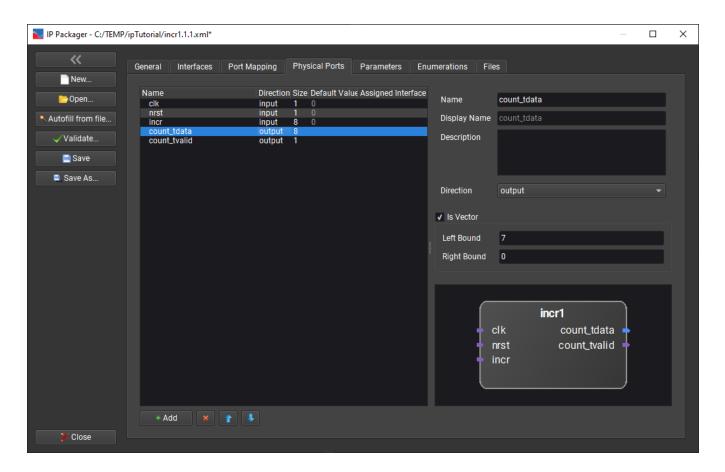

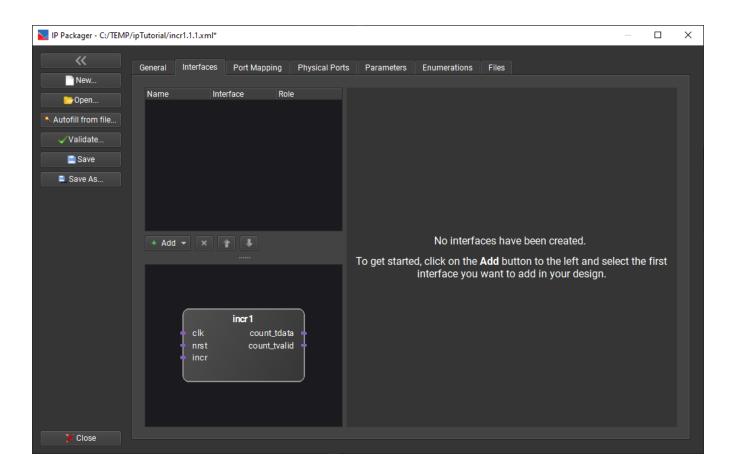

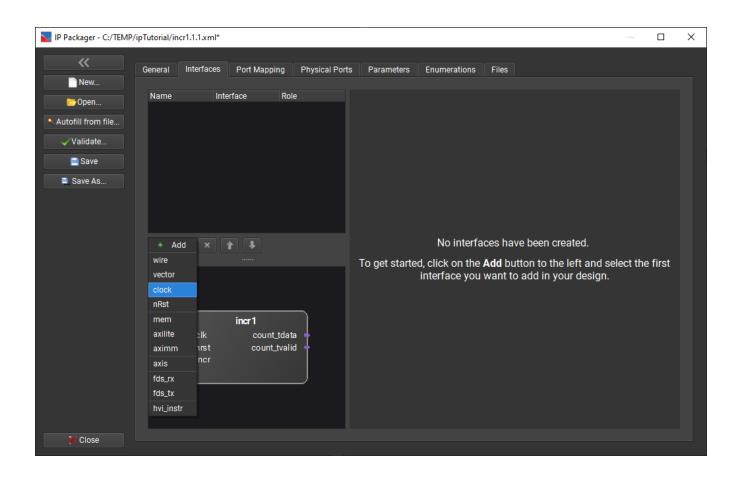

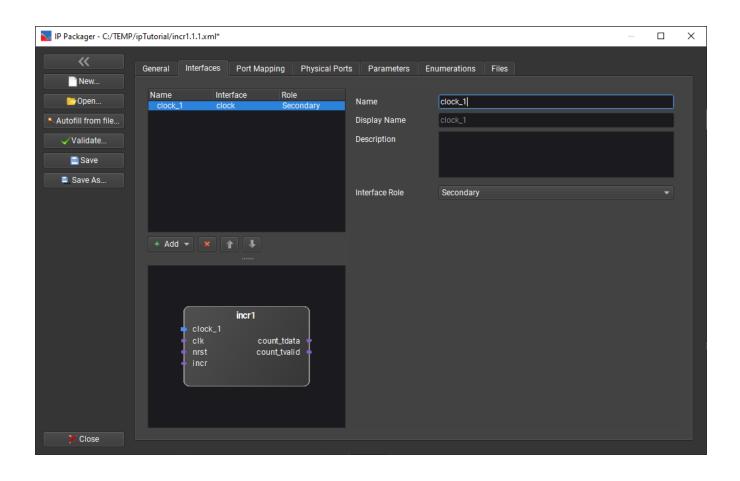

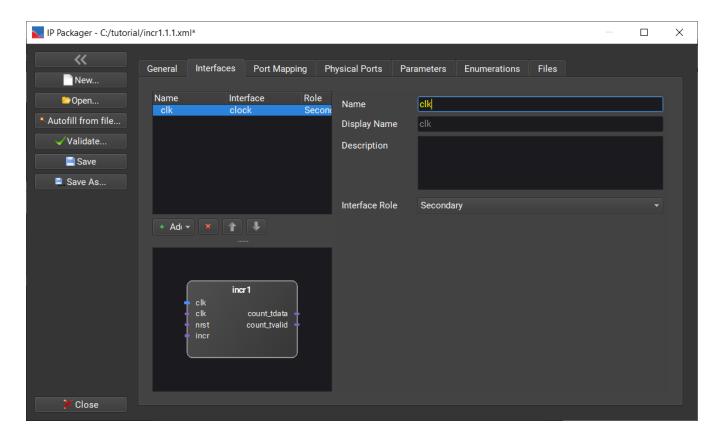

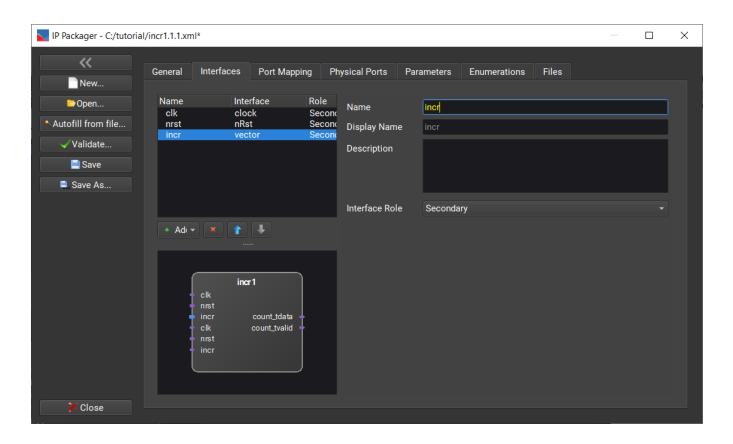

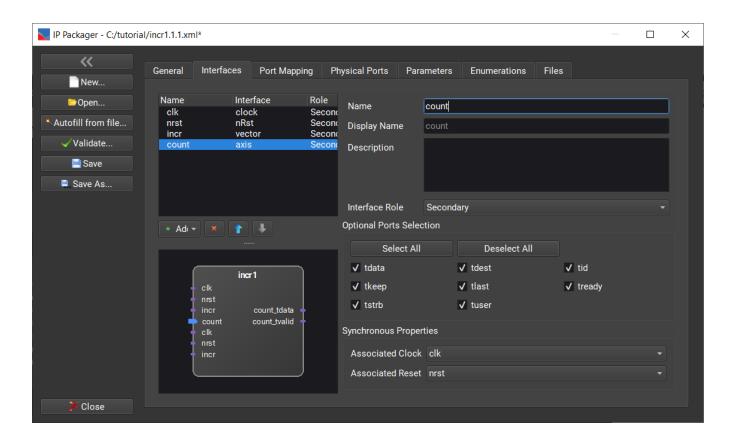

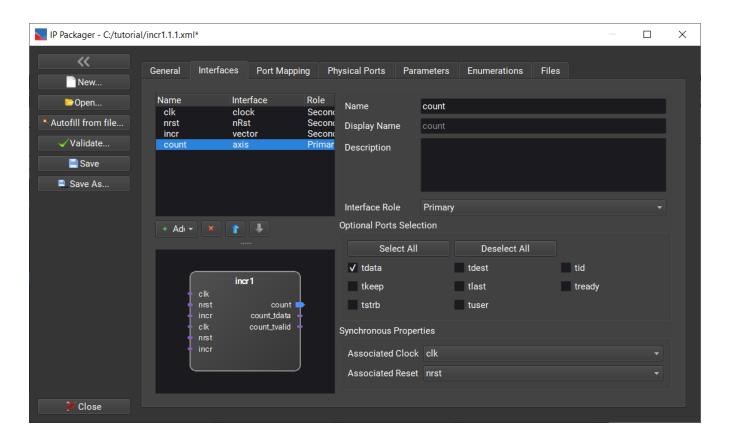

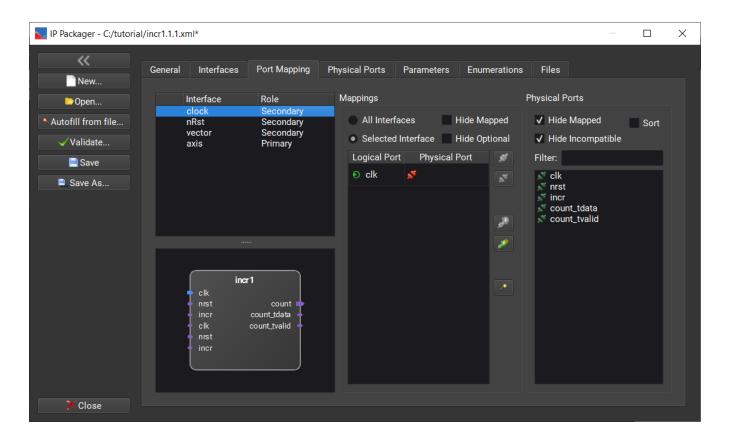

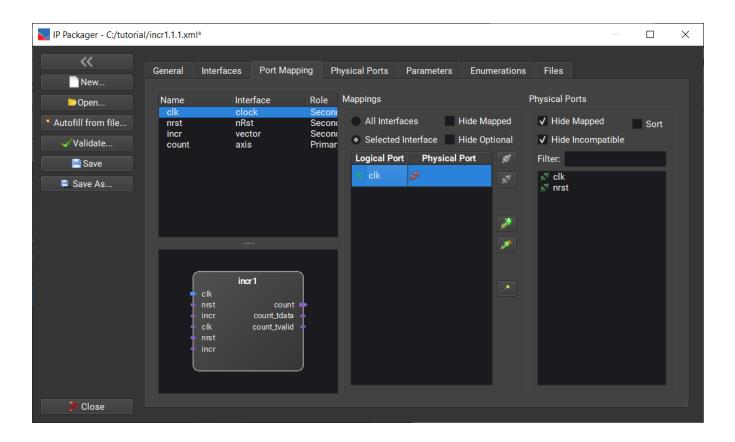

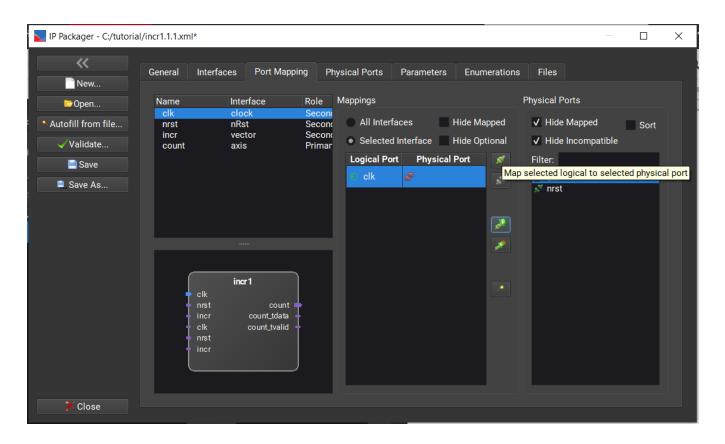

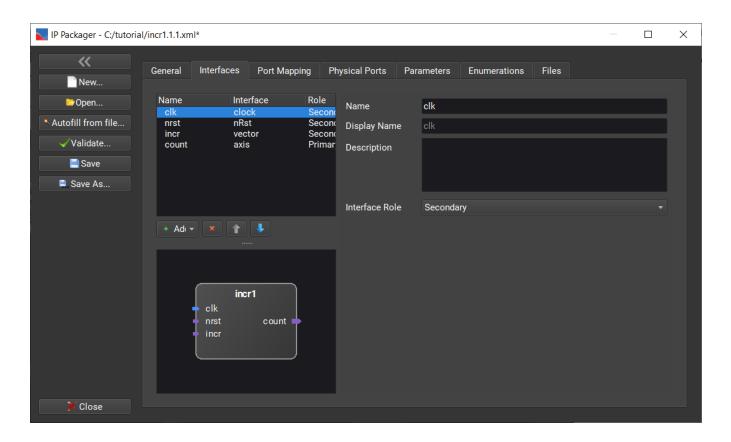

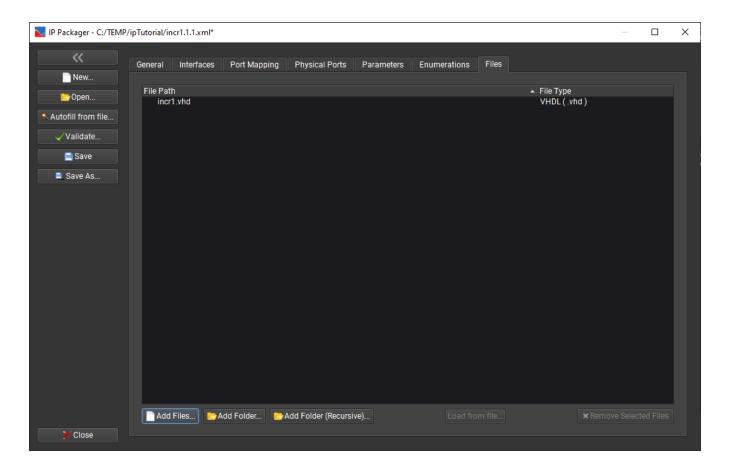

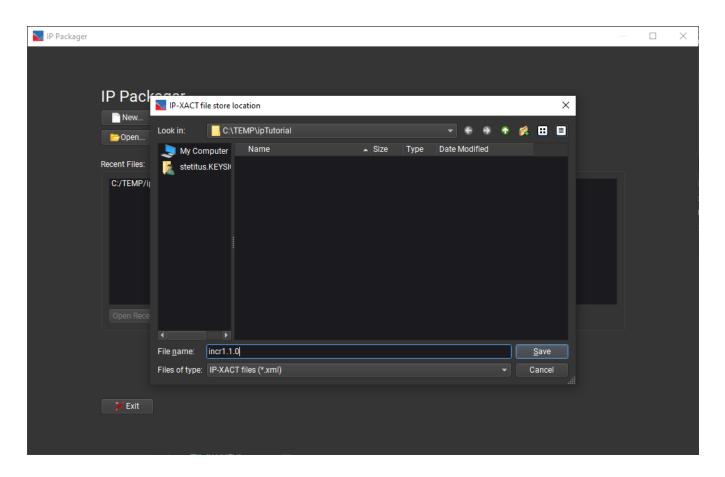

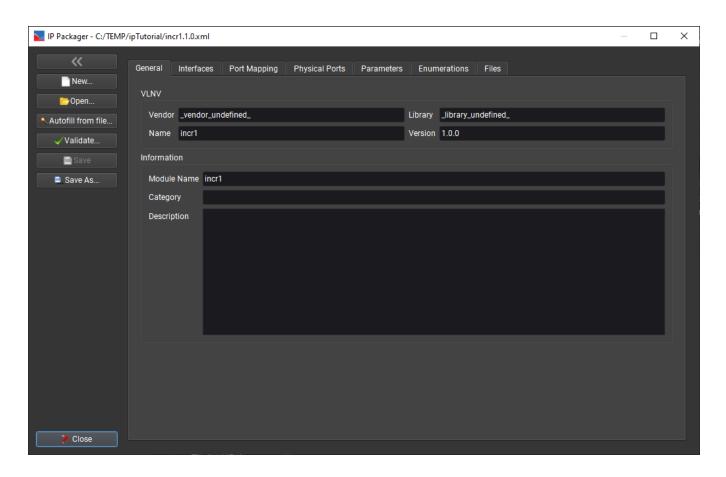

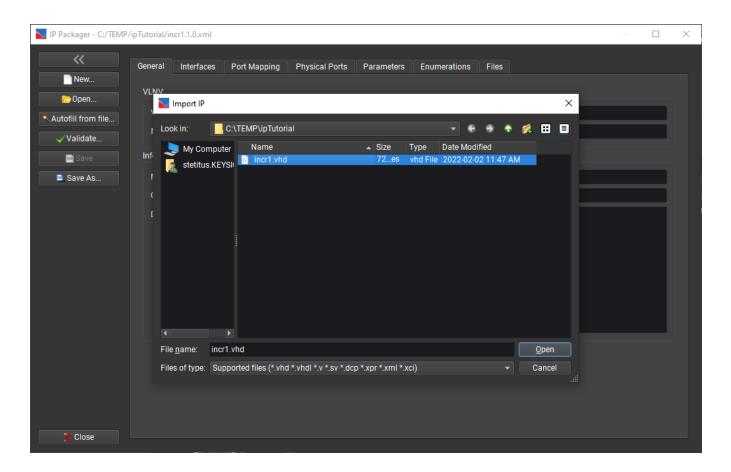

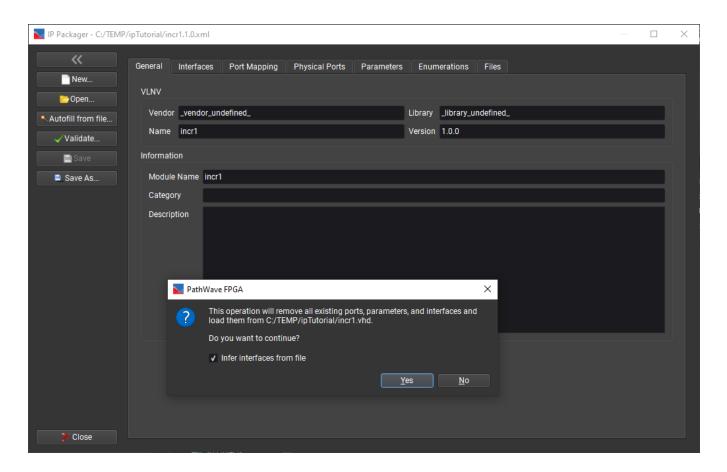

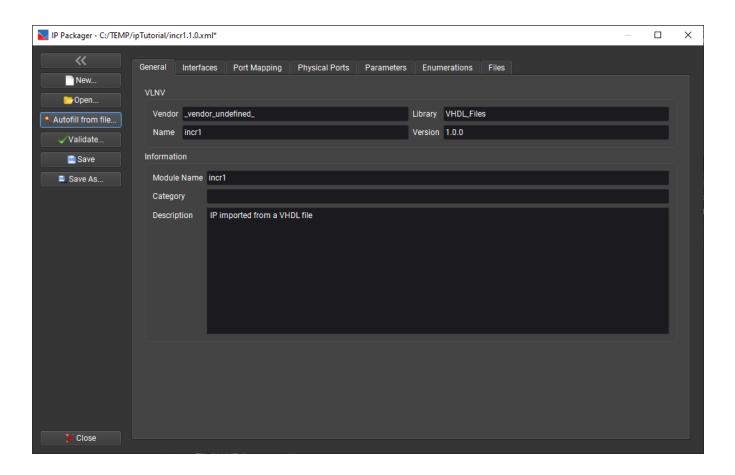

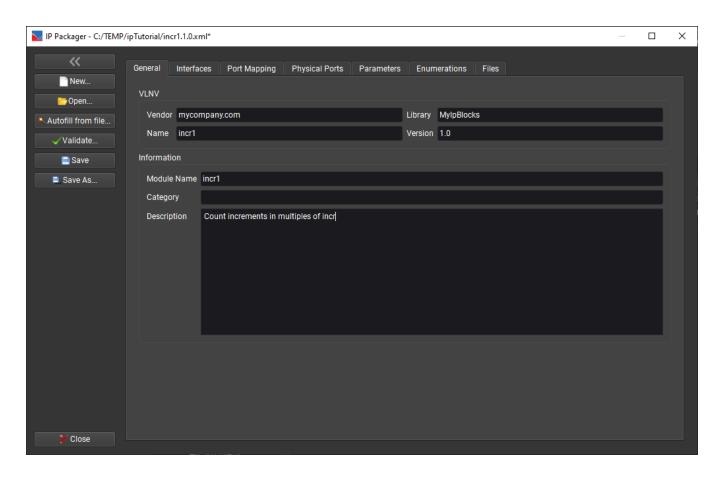

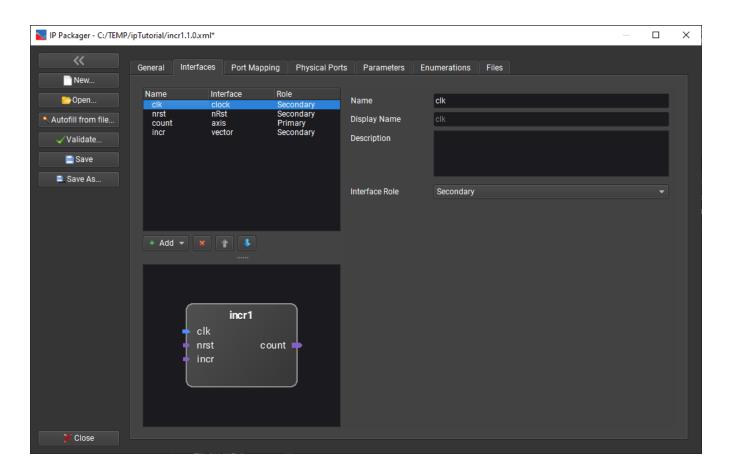

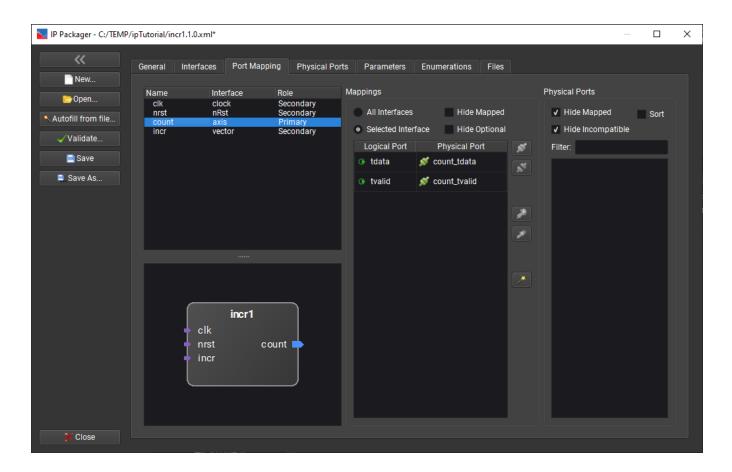

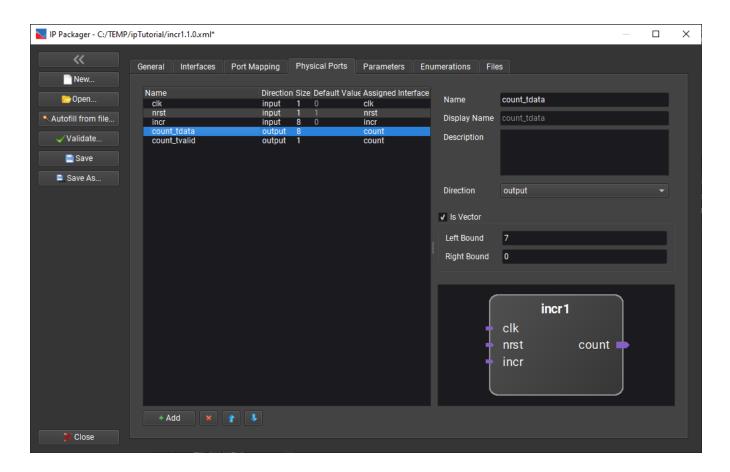

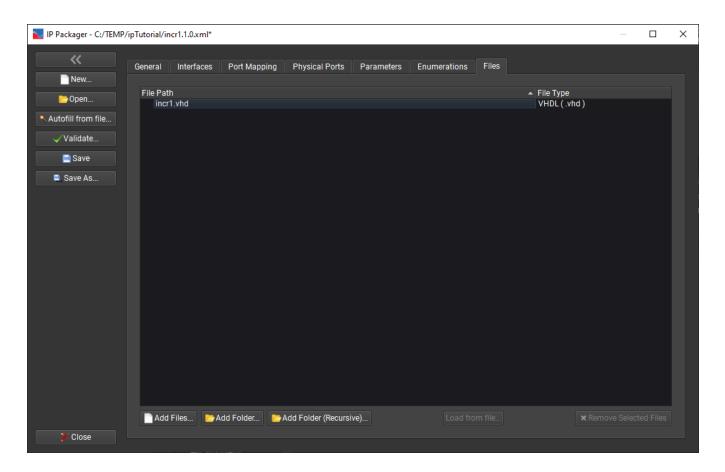

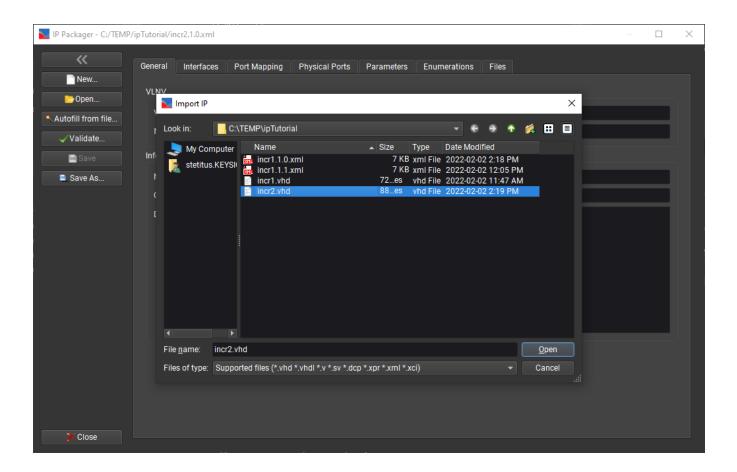

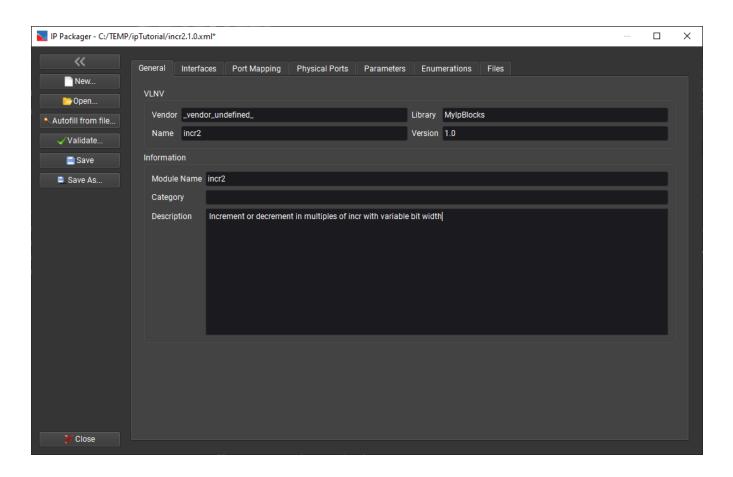

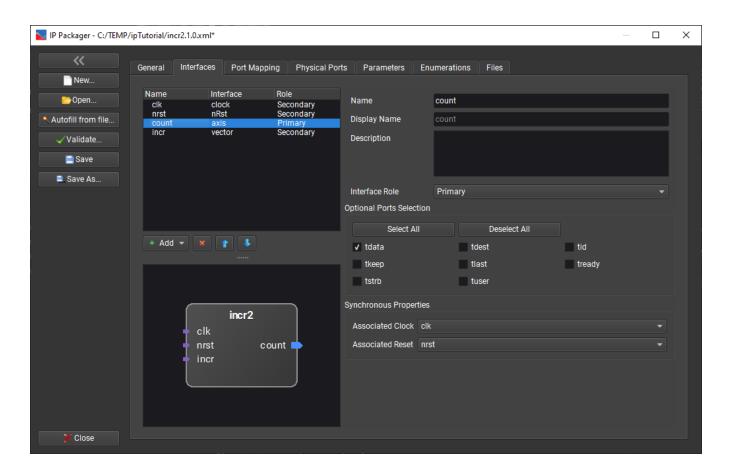

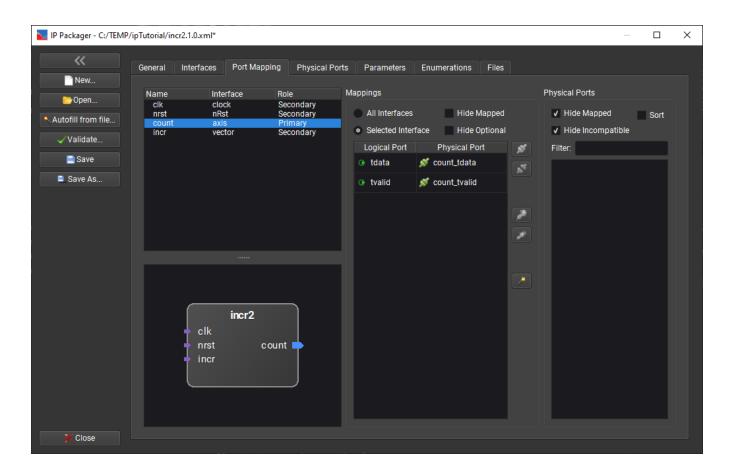

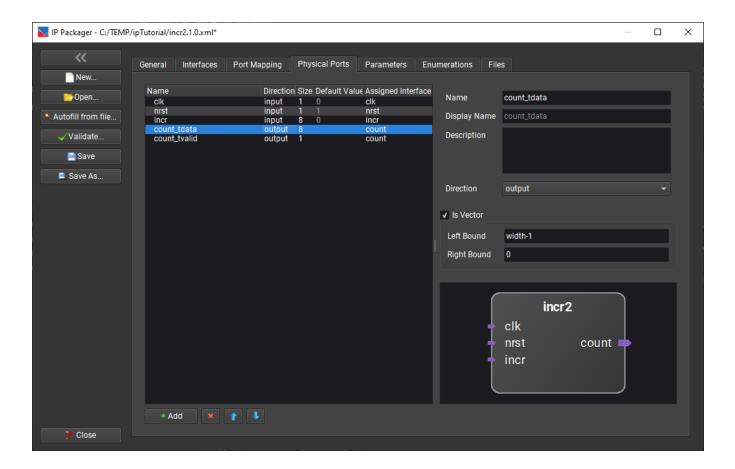

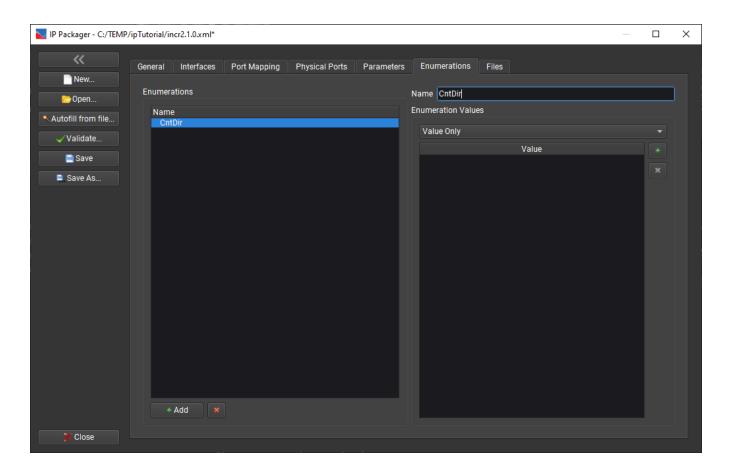

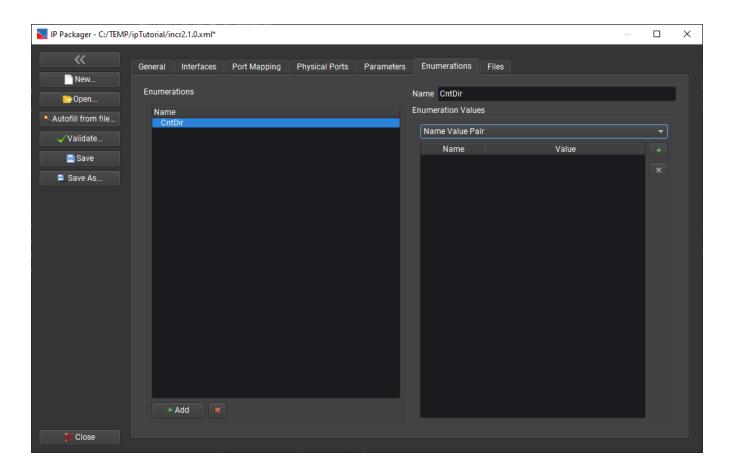

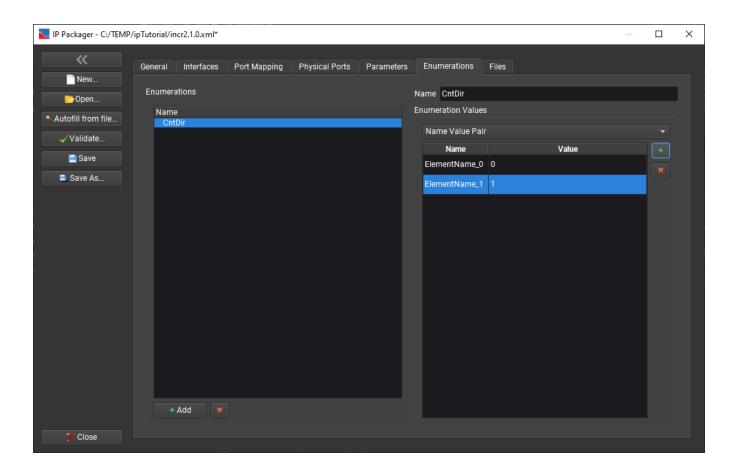

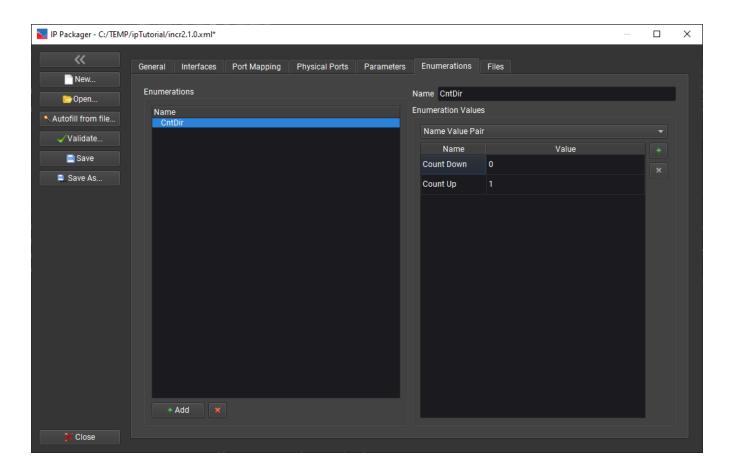

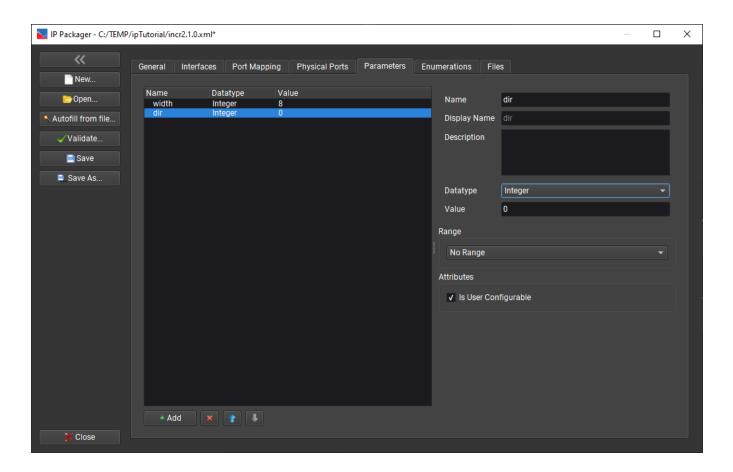

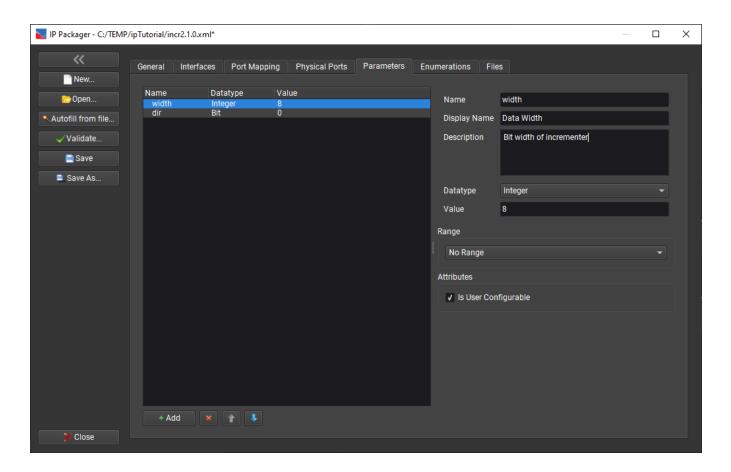

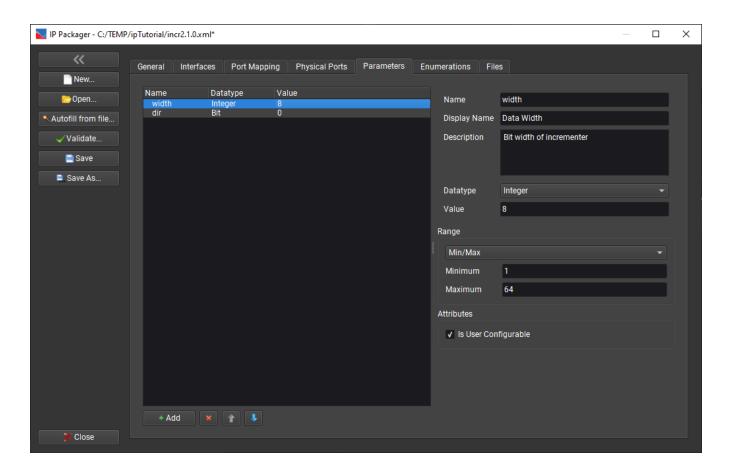

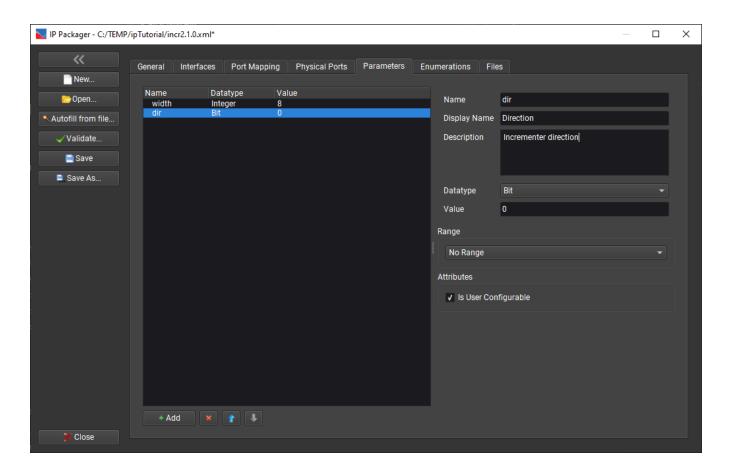

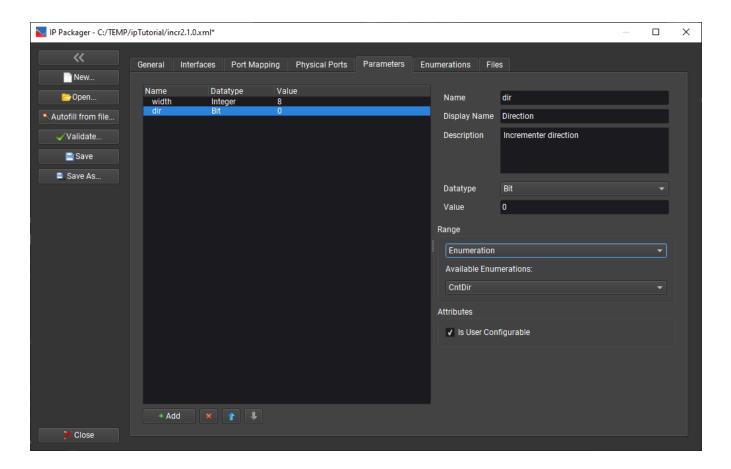

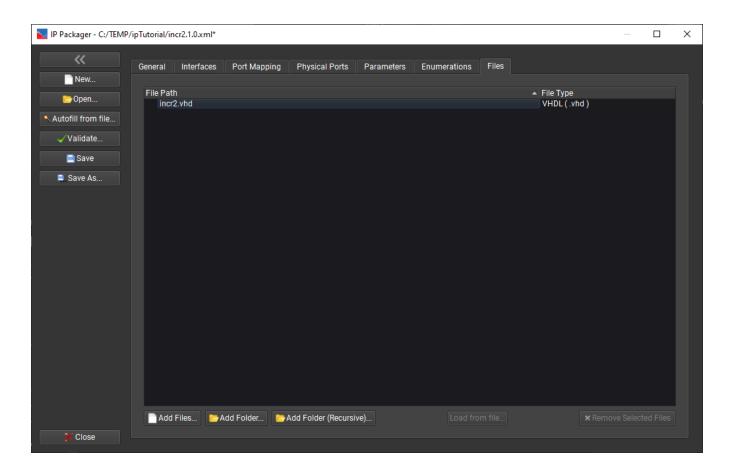

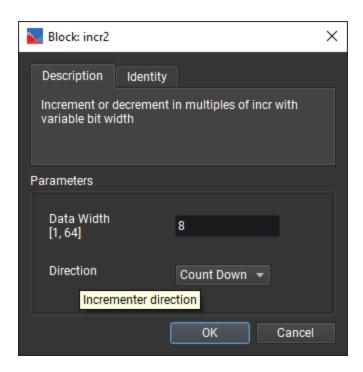

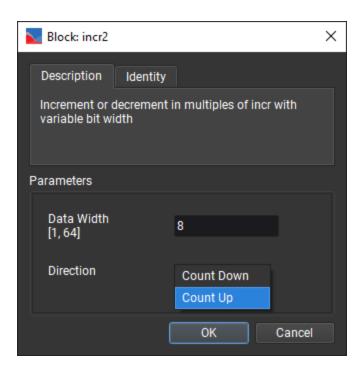

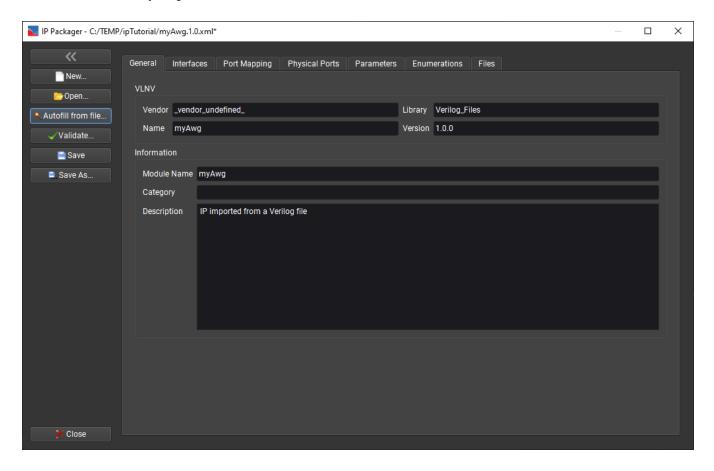

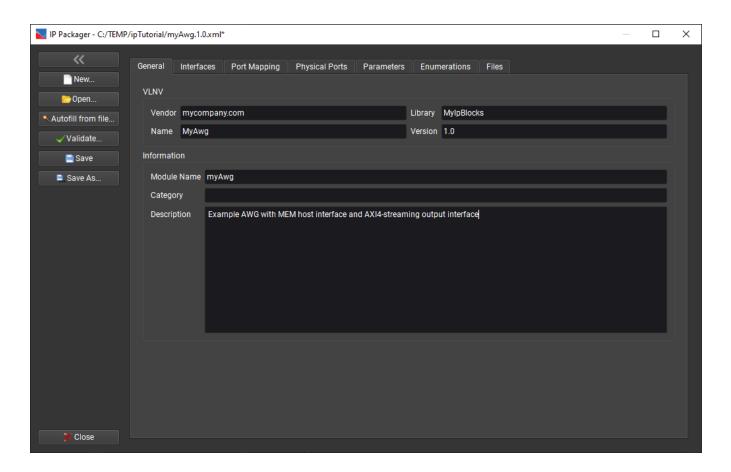

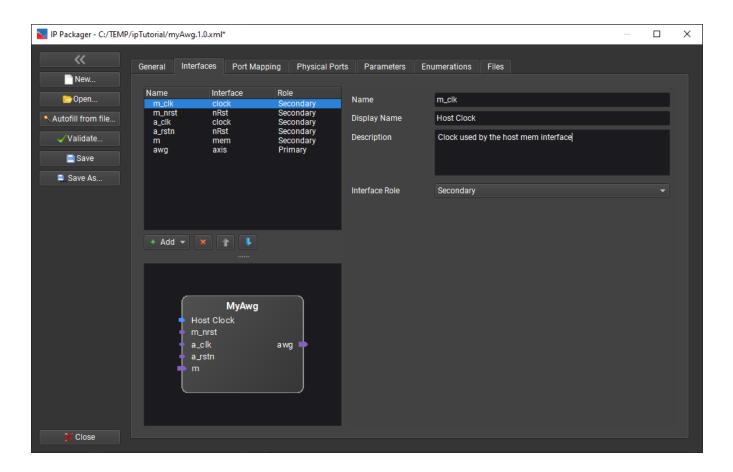

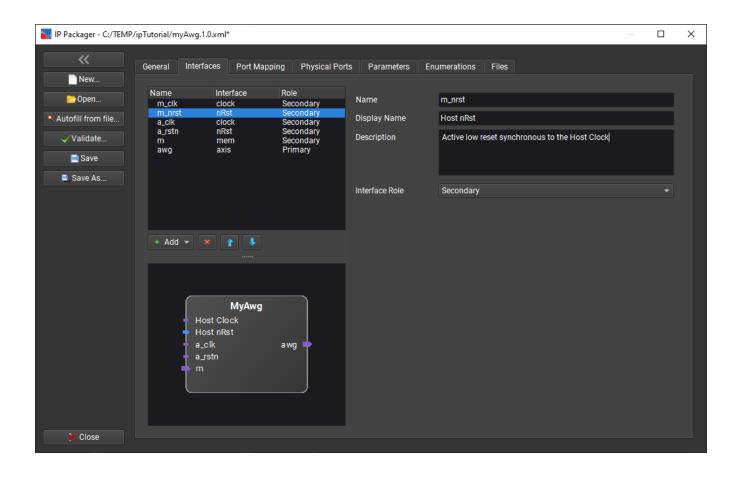

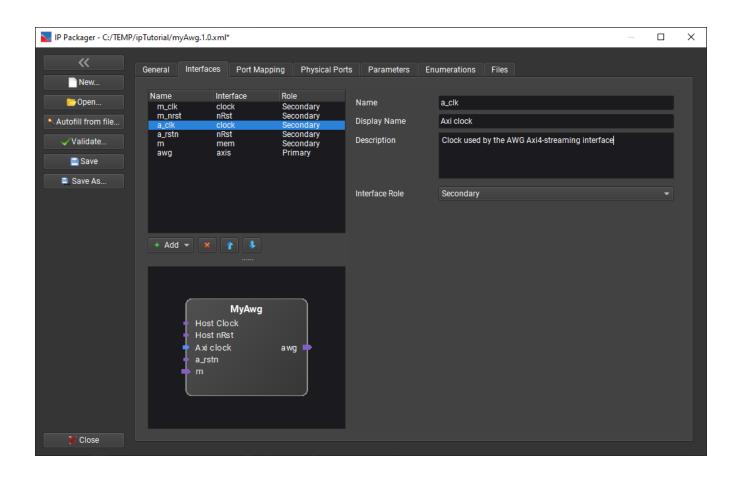

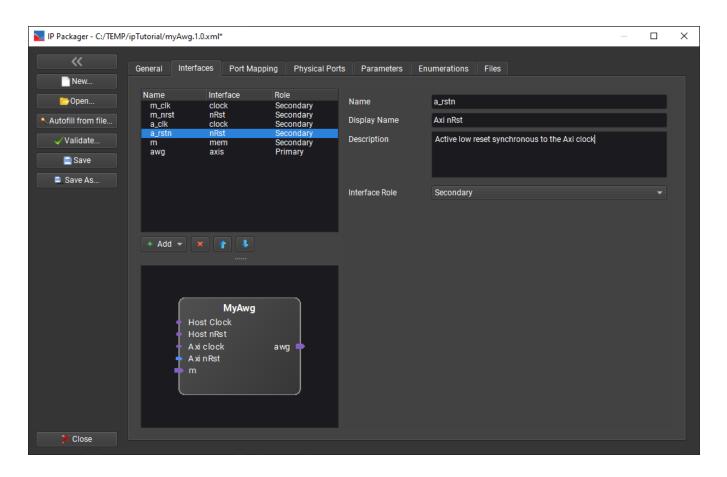

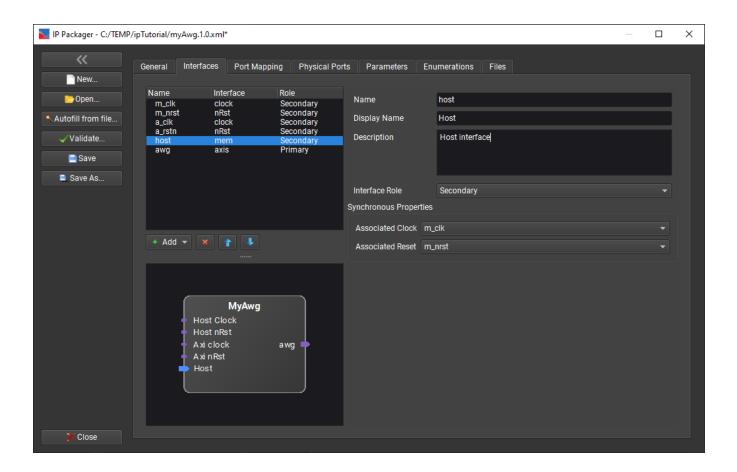

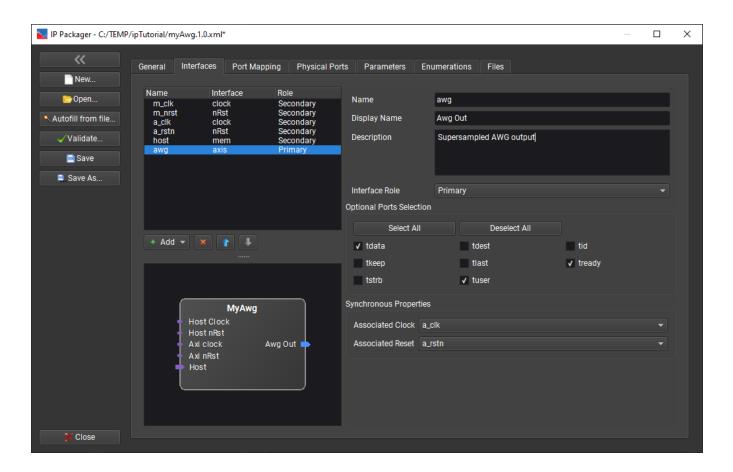

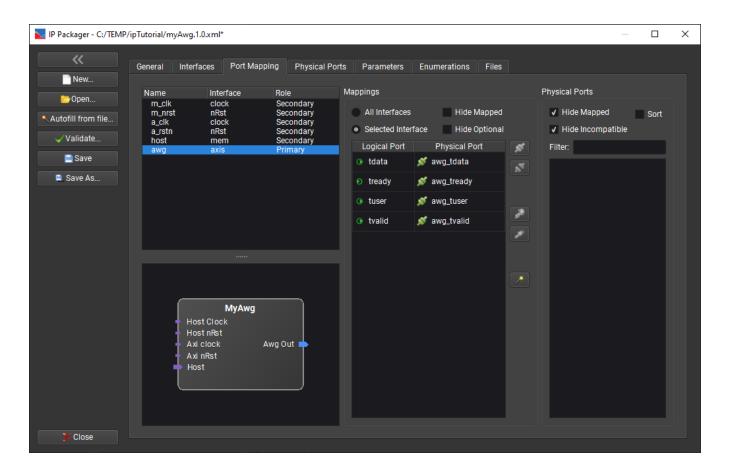

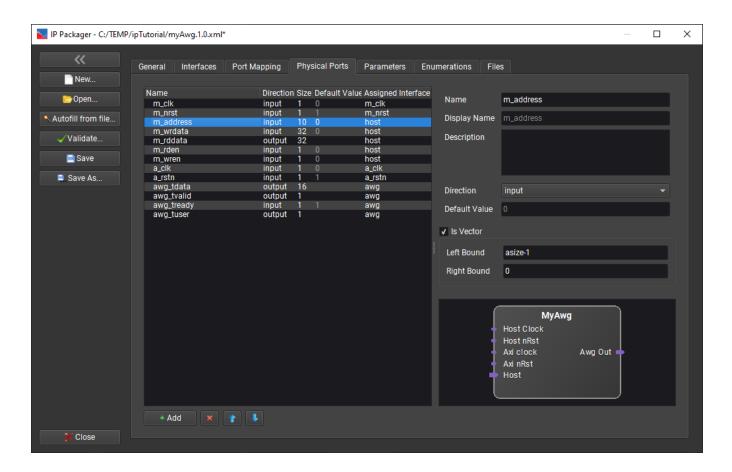

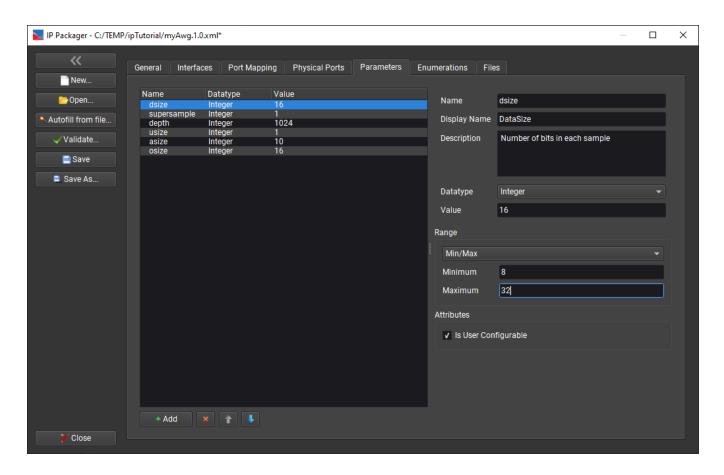

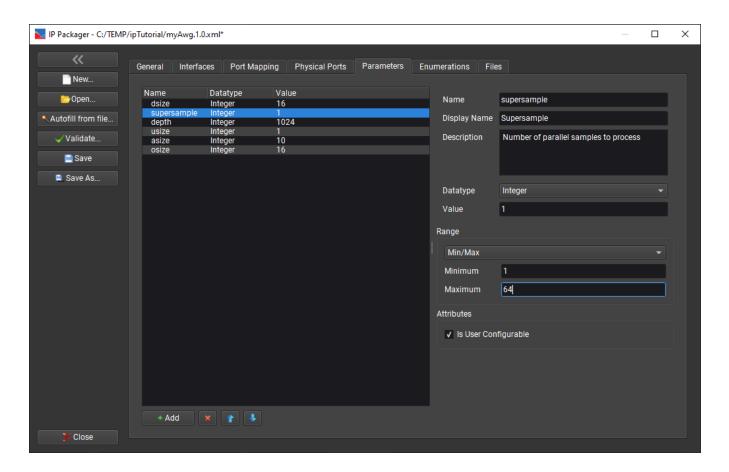

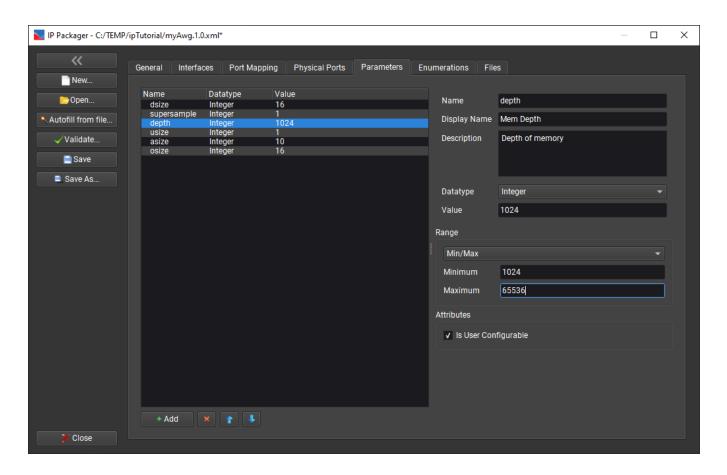

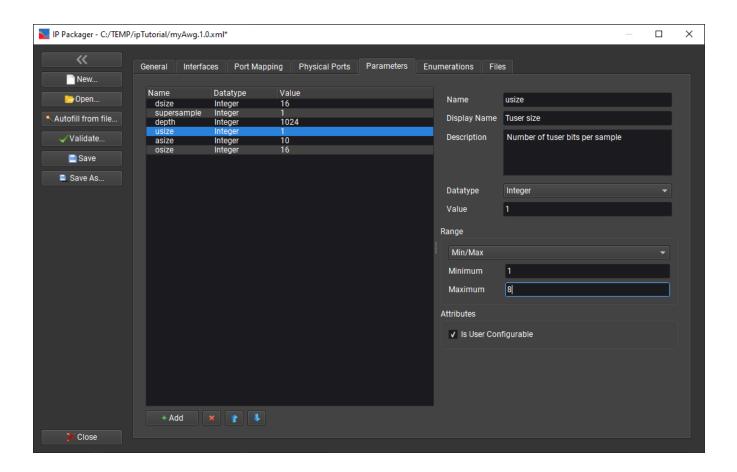

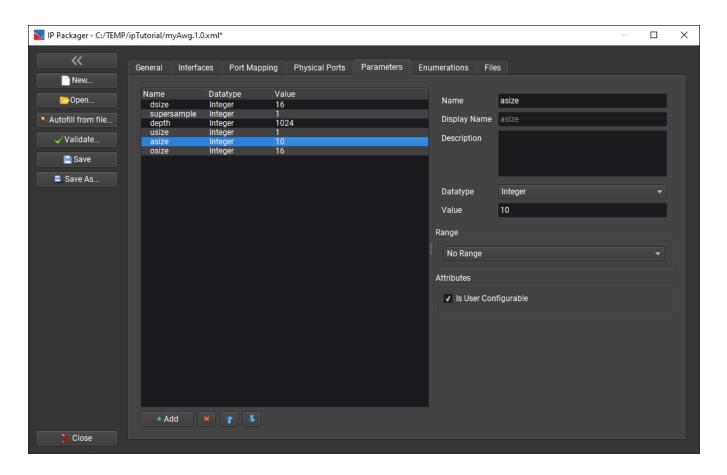

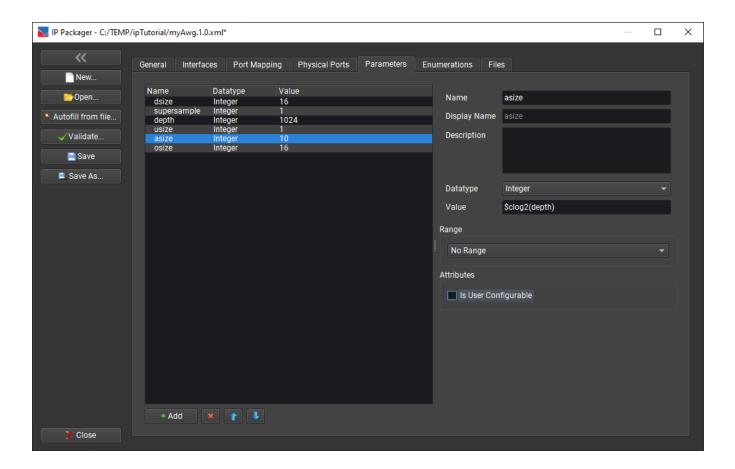

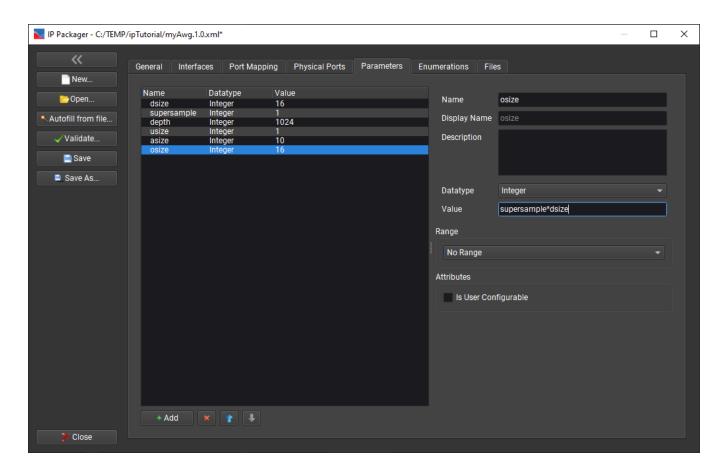

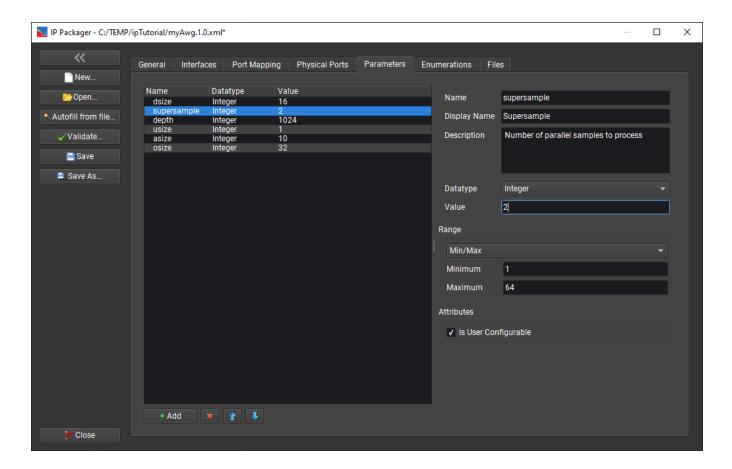

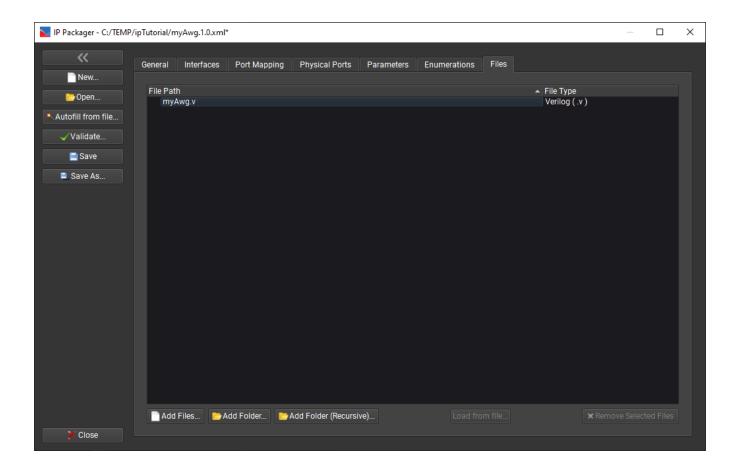

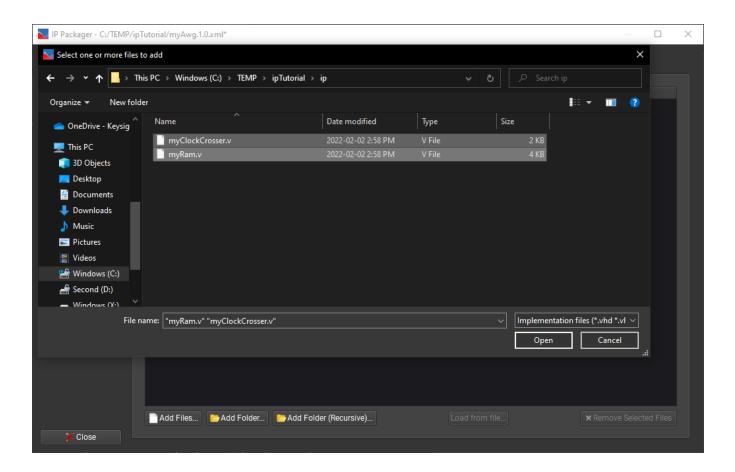

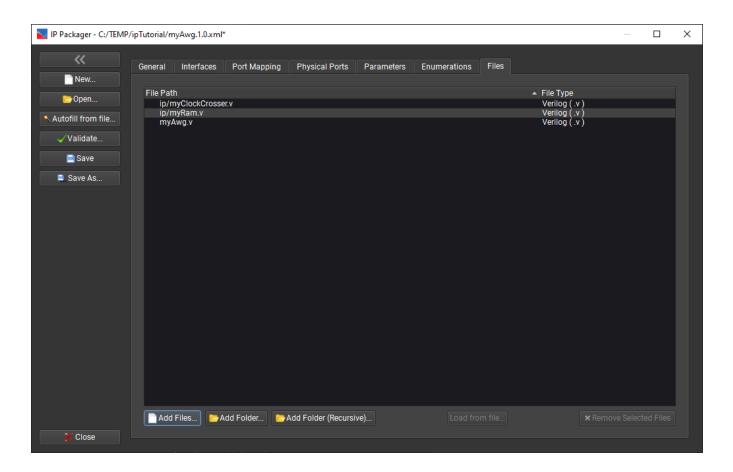

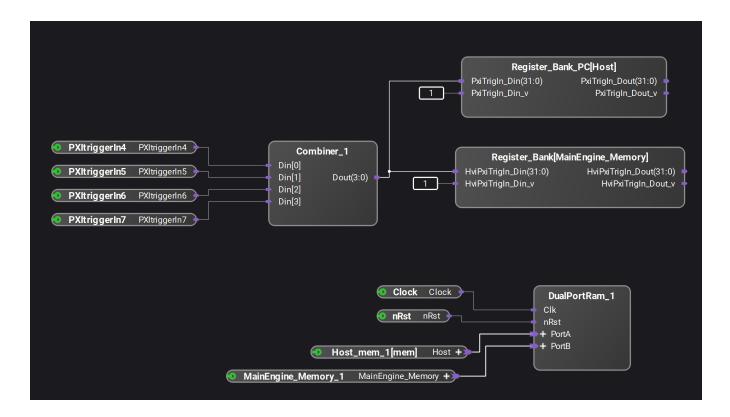

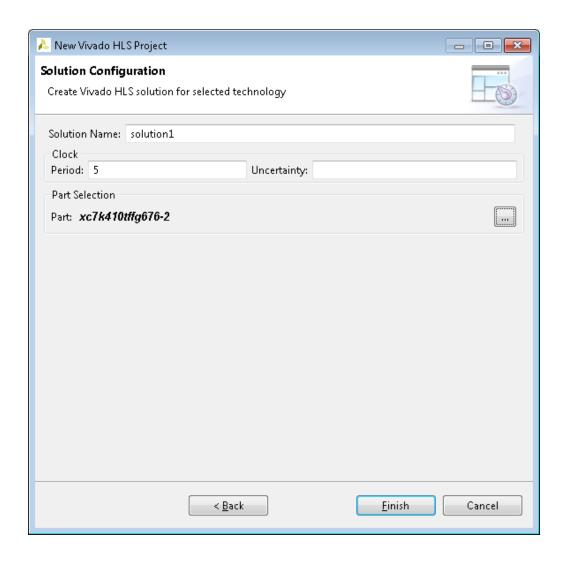

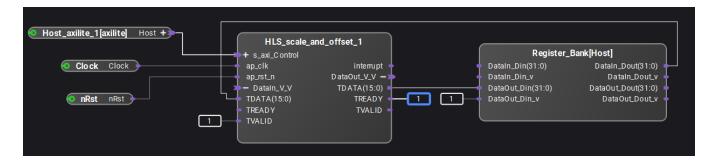

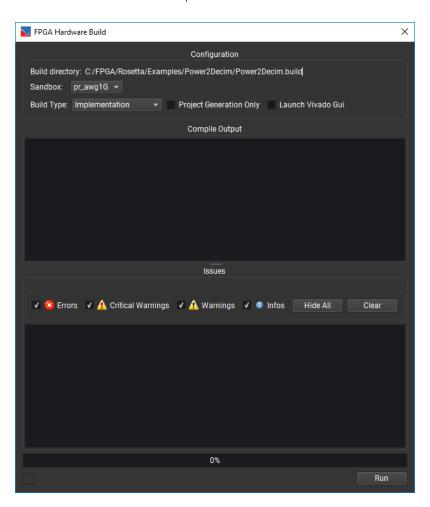

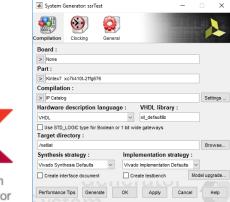

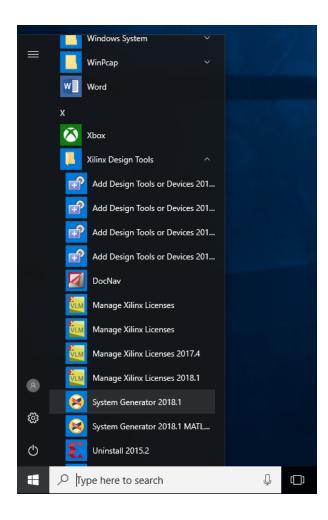

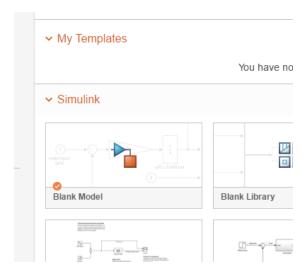

When connecting two blocks with different data widths, there are two different ways of converting the signals. The AXI standard views data as a stream of bytes without explicit meaning. Going from a narrow to a wider interface will cause the bytes to be packed. For example, going from a 16 bit interface to a 32 bit interface will pack two 16 bit words into each 32 bit word. Likewise going from a wide to a narrow interface will retain all the data bytes with the output running at a higher rate than the input. This is desired behavior when interfacing to a memory, for example.